工作方法、控制芯片及控制系统与流程

本技术属于电子电路设计,尤其涉及一种工作方法、控制芯片及控制系统。

背景技术:

1、进入5g和毫米波时代后,随着通信的吞吐量和可靠性的提升,所使用的天线数量显著增大,阵列越密集,实现准确、实时、高效的数字波控信号接口难度越高。

2、传统的天线阵列控制采用串行外设接口 (serial peripheral interface,spi)进行控制器和射频前端芯片的通信,其结构简单、功能单一,支持的相控阵应用受限。随着相控阵架构的多样化和可重构化,相应的波束控制芯片也需要支持相控阵架构的演进。因此,设计一种支持多种控制逻辑和不同架构的控制芯片具有很重要的现实价值。

技术实现思路

1、本技术提供一种工作方法、控制芯片及控制系统,旨在使得波束控制芯片实现相控阵架构的多样化功能和可重构化功能。

2、为解决上述技术问题,本技术实施例提供以下技术方案:

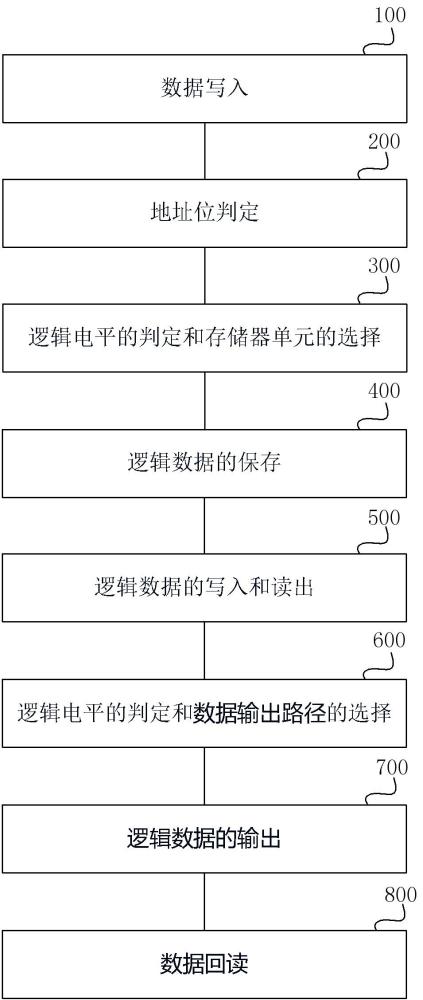

3、第一方面,本技术提供了一种工作方法,所述工作方法包括:

4、数据写入,spi输入模块中m位移位寄存器的前n位写入第二地址位,后(m-n)位写入逻辑数据;

5、地址位判定,判定spi输入模块中前n位的第二地址位与芯片地址电路的n位第一地址位是否相同;若相同,则进行下一步骤;若不同,则进入待机状态;

6、逻辑电平的判定和存储器单元的选择,控制第一存储选择开关进行逻辑电平的判定和存储器单元的选择;

7、逻辑数据的保存,控制输入的逻辑数据一级一级分别保存在存储器模块的存储器单元中;

8、逻辑数据的写入和读出,存储器模块中的第四寄存器组、第五寄存器组和第六寄存器组写入和读出存储器单元中的逻辑数据;

9、逻辑电平的判定和数据输出路径的选择,控制第二存储选择开关进行逻辑电平的判定和数据输出路径的选择;

10、逻辑数据的输出,第一输出驱动输出从第四寄存器组或第五寄存器组中读出的逻辑数据,第二输出驱动输出从第六寄存器组中读出的逻辑数据;

11、数据回读,spi输出模块输出从第四寄存器组或第五寄存器组或第六寄存器组中读出的逻辑数据和第二地址位;

12、读写使能端wr为第一存储选择开关或第二存储选择开关的读写使能端;

13、其中,m、n均为正整数且m大于n。

14、在其中一个实施例中,所述存储器单元包括第一寄存器单元、第二寄存器单元和第三寄存器单元,所述第一寄存器单元包括k1个第一寄存器组,所述第二寄存器单元包括k1个第二寄存器组,所述第三寄存器单元包括k2个第三寄存器组;

15、其中,k1、k2均为大于1的整数。

16、在其中一个实施例中,所述spi输入模块包括sclk、ncs和sdi三个端口;其中,sclk为时钟信号端,ncs为有效高电平或有效低电平的片选同步信号端,sdi为数据输入端。

17、在其中一个实施例中,所述spi输入模块中m位移位寄存器的前n位写入第二地址位,后(m-n)位写入逻辑数据包括:

18、ncs输入有效高电平或有效低电平时,n位第二地址位和(m-n)位逻辑数据串行写入所述spi输入模块中;

19、其中,m、n均为正整数且m大于n。

20、在其中一个实施例中,所述读写使能端wr为第一存储选择开关或第二存储选择开关的读写使能端包括:

21、读写使能端wr用于控制第一存储选择开关写入数据或者第二存储选择开关读出数据;

22、读写使能端wr输入有效高电平时,第一存储选择开关写入数据;读写使能端wr输入有效低电平时,第二存储选择开关读出数据;

23、或者读写使能端wr输入有效低电平时,第一存储选择开关写入数据;读写使能端wr输入有效高电平时,第二存储选择开关读出数据。

24、在其中一个实施例中,所述控制第一存储选择开关进行逻辑电平的判定和存储器单元的选择包括:

25、控制第一存储选择开关判定第一逻辑电平端sel0和第二逻辑电平端sel1输入逻辑电平的高低进行存储器单元的选择;第一逻辑电平端sel0输入有效低电平时选择第一寄存器单元或者第二寄存器单元,第一逻辑电平端sel0输入有效高电平时选择第三寄存器单元。

26、在其中一个实施例中,所述控制第一存储选择开关进行逻辑电平的判定和存储器单元的选择包括:

27、控制第一存储选择开关判定第一逻辑电平端sel0和第二逻辑电平端sel1输入逻辑电平的高低进行存储器单元的选择;第一逻辑电平端sel0输入有效高电平时选择第一寄存器单元或者第二寄存器单元,第一逻辑电平端sel0输入有效低电平时选择第三寄存器单元。

28、在其中一个实施例中,所述第一逻辑电平端sel0输入有效低电平时选择第一寄存器单元或者第二寄存器单元包括:

29、第一逻辑电平端sel0输入有效低电平且第二逻辑电平端sel1输入有效低电平时选择第一寄存器单元,第一逻辑电平端sel0输入有效低电平且第二逻辑电平端sel1输入有效高电平时选择第二寄存器单元;

30、或者第一逻辑电平端sel0输入有效低电平且第二逻辑电平端sel1输入有效高电平时选择第一寄存器单元,第一逻辑电平端sel0输入有效低电平且第二逻辑电平端sel1输入有效低电平时选择第二寄存器单元。

31、在其中一个实施例中,所述第一逻辑电平端sel0输入有效高电平时选择第一寄存器单元或者第二寄存器单元包括:

32、第一逻辑电平端sel0输入有效高电平且第二逻辑电平端sel1输入有效低电平时选择第一寄存器单元,第一逻辑电平端sel0输入有效高电平且第二逻辑电平端sel1输入有效高电平时选择第二寄存器单元;

33、或者第一逻辑电平端sel0输入有效高电平且第二逻辑电平端sel1输入有效高电平时选择第一寄存器单元,第一逻辑电平端sel0输入有效高电平且第二逻辑电平端sel1输入有效低电平时选择第二寄存器单元。

34、在其中一个实施例中,所述控制输入的逻辑数据一级一级分别保存在存储器模块的存储器单元中包括:

35、ncs进行电平切换产生上升沿或者下降沿时,逻辑数据存入存储器单元中,存储器单元中的每个寄存器组均分别保存通过spi输入模块写入的每组逻辑数据,每个寄存器组均分别保存(m-n)位数据;

36、其中,m、n均为正整数且m大于n。

37、在其中一个实施例中,所述存储器模块中的第四寄存器组、第五寄存器组和第六寄存器组写入和读出存储器单元中的逻辑数据包括:

38、第一寄存器单元中的k1个第一寄存器组的数据全部存满后写入第四寄存器组中,第四寄存器组并行读出保存的k1(m-n)位逻辑数据;第二寄存器单元中的k1个第二寄存器组的数据全部存满后写入第五寄存器组中,第五寄存器组并行读出保存的k1(m-n)位逻辑数据;第三寄存器单元中的k2个第三寄存器组的数据全部存满后写入第六寄存器组中,第六寄存器组并行读出保存的k2(m-n)位逻辑数据;

39、其中,m、n均为正整数且m大于n,k1、k2均为大于1的整数。

40、在其中一个实施例中,所述控制第二存储选择开关进行逻辑电平的判定和数据输出路径的选择包括:

41、控制第二存储选择开关判定第一逻辑电平端sel0和/或第二逻辑电平端sel1输入逻辑电平的高低,选择数据输出路径是通过第一输出驱动或者spi输出模块进行。

42、在其中一个实施例中,所述第一输出驱动输出从第四寄存器组或第五寄存器组中读出的逻辑数据包括:

43、第一逻辑电平端sel0输入有效低电平时,第一输出驱动输出从第四寄存器组中读出的k1(m-n)位逻辑数据;第一逻辑电平端sel0输入有效高电平时,第一输出驱动输出从第五寄存器组中读出的k1(m-n)位逻辑数据;

44、或者第一逻辑电平端sel0输入有效高电平时,第一输出驱动输出从第四寄存器组中读出的k1(m-n)位逻辑数据;第一逻辑电平端sel0输入有效低电平时,第一输出驱动输出从第五寄存器组中读出的k1(m-n)位逻辑数据;

45、其中,m、n均为正整数且m大于n,k1为大于1的整数。

46、在其中一个实施例中,所述第一输出驱动输出从第四寄存器组或第五寄存器组中读出的逻辑数据包括:

47、第二逻辑电平端sel1输入有效低电平时,第一输出驱动输出从第四寄存器组中读出的k1(m-n)位逻辑数据;第二逻辑电平端sel1输入有效高电平时,第一输出驱动输出从第五寄存器组中读出的k1(m-n)位逻辑数据;

48、或者第二逻辑电平端sel1输入有效高电平时,第一输出驱动输出从第四寄存器组中读出的k1(m-n)位逻辑数据;第二逻辑电平端sel1输入有效低电平时,第一输出驱动输出从第五寄存器组中读出的k1(m-n)位逻辑数据;

49、其中,m、n均为正整数且m大于n,k1为大于1的整数。

50、在其中一个实施例中,所述第二输出驱动输出从第六寄存器组中读出的逻辑数据包括:

51、第二输出驱动直接输出从第六寄存器组中存满的逻辑数据。

52、在其中一个实施例中,所述spi输出模块输出从第四寄存器组或第五寄存器组或第六寄存器组中读出的逻辑数据和第二地址位包括:

53、第一逻辑电平端sel0输入有效低电平且第二逻辑电平端sel1输入有效低电平时,spi输出模块输出从第四寄存器组中读出的k1(m-n)位逻辑数据和n位第二地址位;第一逻辑电平端sel0输入有效低电平且第二逻辑电平端sel1输入有效高电平时,spi输出模块输出从第五寄存器组中读出的k1(m-n)位逻辑数据和n位第二地址位;第一逻辑电平端sel0输入有效高电平时,spi输出模块输出从第六寄存器组中读出的k2(m-n)位逻辑数据和n位第二地址位;

54、其中,m、n均为正整数且m大于n,k1、k2均为大于1的整数。

55、在其中一个实施例中,所述spi输出模块输出从第四寄存器组或第五寄存器组或第六寄存器组中读出的逻辑数据和第二地址位包括:

56、第一逻辑电平端sel0输入有效低电平且第二逻辑电平端sel1输入有效高电平时,spi输出模块输出从第四寄存器组中读出的k1(m-n)位逻辑数据和n位第二地址位;第一逻辑电平端sel0输入有效低电平且第二逻辑电平端sel1输入有效低电平时,spi输出模块输出从第五寄存器组中读出的k1(m-n)位逻辑数据和n位第二地址位;第一逻辑电平端sel0输入有效高电平时,spi输出模块输出从第六寄存器组中读出的k2(m-n)位逻辑数据和n位第二地址位;

57、其中,m、n均为正整数且m大于n,k1、k2均为大于1的整数。

58、在其中一个实施例中,所述spi输出模块输出从第四寄存器组或第五寄存器组或第六寄存器组中读出的逻辑数据和第二地址位包括:

59、第一逻辑电平端sel0输入有效高电平且第二逻辑电平端sel1输入有效低电平时,spi输出模块输出从第四寄存器组中读出的k1(m-n)位逻辑数据和n位第二地址位;第一逻辑电平端sel0输入有效高电平且第二逻辑电平端sel1输入有效高电平时,spi输出模块输出从第五寄存器组中读出的k1(m-n)位逻辑数据和n位第二地址位;第一逻辑电平端sel0输入有效低电平时,spi输出模块输出从第六寄存器组中读出的k2(m-n)位逻辑数据和n位第二地址位;

60、其中,m、n均为正整数且m大于n,k1、k2均为大于1的整数。

61、在其中一个实施例中,所述spi输出模块输出从第四寄存器组或第五寄存器组或第六寄存器组中读出的逻辑数据和第二地址位包括:

62、第一逻辑电平端sel0输入有效高电平且第二逻辑电平端sel1输入有效高电平时,spi输出模块输出从第四寄存器组中读出的k1(m-n)位逻辑数据和n位第二地址位;第一逻辑电平端sel0输入有效高电平且第二逻辑电平端sel1输入有效低电平时,spi输出模块输出从第五寄存器组中读出的k1(m-n)位逻辑数据和n位第二地址位;第一逻辑电平端sel0输入有效低电平时,spi输出模块输出从第六寄存器组中读出的k2(m-n)位逻辑数据和n位第二地址位;

63、其中,m、n均为正整数且m大于n,k1、k2均为大于1的整数。

64、在其中一个实施例中,所述spi输出模块包括sclk、ncs和sdo三个端口;其中,sclk为时钟信号端,ncs为有效高电平或有效低电平的片选同步信号端,sdo为数据输出端。

65、在其中一个实施例中,所述数据写入之前还包括芯片地址电路的编程。

66、在其中一个实施例中,其中m等于16,n等于4,k1等于8,k2等于8。

67、在其中一个实施例中,其中m等于17,n等于5,k1等于8,k2等于8。

68、在其中一个实施例中,其中m等于24,n等于8,k1等于6,k2等于6。

69、在其中一个实施例中,其中m等于32,n等于8,k1等于4,k2等于4。

70、第二方面,本技术提供了一种控制芯片,所述控制芯片包括:芯片地址电路、spi输入模块、第一存储选择开关、存储器模块、第二存储选择开关、第一输出驱动、第二输出驱动以及spi输出模块;

71、所述芯片地址电路包括n位第一地址位,作为芯片地址电路的数字识别码;

72、所述spi输入模块包括m位移位寄存器,用于数据写入和地址位判定,所述m位移位寄存器的前n位为第二地址位以及后(m-n)位为逻辑数据;

73、所述存储器模块包括存储器单元、第四寄存器组、第五寄存器组和第六寄存器组,所述存储器单元用于逻辑数据的保存,所述第四寄存器组、第五寄存器组、第六寄存器组均用于写入和读出存储器单元中的逻辑数据;

74、所述第一存储选择开关用于逻辑电平的判定和存储器单元的选择;所述第二存储选择开关用于逻辑电平的判定和数据输出路径的选择;读写使能端wr为第一存储选择开关或第二存储选择开关的读写使能端;

75、所述第一输出驱动用于输出从第四寄存器组或第五寄存器组中读出的逻辑数据,所述第二输出驱动用于输出从第六寄存器组中读出的逻辑数据;

76、所述spi输出模块用于输出从第四寄存器组或第五寄存器组或第六寄存器组中读出的逻辑数据和第二地址位;

77、其中,m、n均为正整数且m大于n。

78、在其中一个实施例中,所述存储器单元包括第一寄存器单元、第二寄存器单元和第三寄存器单元,所述第一寄存器单元包括k1个第一寄存器组,所述第二寄存器单元包括k1个第二寄存器组,所述第三寄存器单元包括k2个第三寄存器组;

79、其中,k1、k2均为大于1的正整数。

80、在其中一个实施例中,所述第四寄存器组、第五寄存器组均分别包括k1(m-n)位移位寄存器,所述第六寄存器组包括k2(m-n)位移位寄存器;

81、其中,m、n均为正整数且m大于n,k1、k2均为大于1的整数。

82、在其中一个实施例中,所述spi输入模块包括sclk、ncs和sdi三个端口,所述spi输出模块包括sclk、ncs和sdo三个端口;其中,sclk为时钟信号端,ncs为有效高电平或有效低电平的片选同步信号端,sdi为数据输入端,sdo为数据输出端。

83、在其中一个实施例中,其中m等于16,n等于4,k1等于8,k2等于8。

84、在其中一个实施例中,其中m等于17,n等于5,k1等于8,k2等于8。

85、在其中一个实施例中,其中m等于24,n等于8,k1等于6,k2等于6。

86、在其中一个实施例中,其中m等于32,n等于8,k1等于4,k2等于4。

87、第三方面,本技术提供了一种控制系统,其应用于如上所述的控制芯片。

- 还没有人留言评论。精彩留言会获得点赞!