芯片引线键合质量检测方法、系统及存储介质

本发明属于芯片封装,本发明涉及一种芯片引线键合质量检测方法、系统及存储介质。

背景技术:

1、随着芯片技术的不断发展,芯片的复杂程度不断增加、性能越来越强,同时其特征尺寸越来越小,组装密度越来越高,对芯片制造、封装等工艺的要求也进一步提高。引线键合是芯片制造和封装中的关键工艺之一,是实现芯片、基板和i/o之间互连最常见的工艺方法,芯片组件内部存在几百乃至上万根键合引线,其互连质量直接决定了组件的性能和可靠性。近年来半导体产业对更高的集成度、可靠性等的需求更加迫切,对引线键合技术提出了更高的要求,因此对引线键合质量的检验更加重要,其在芯片制造、封装中的地位愈发重要。当前人工目检仍然是引线键合最常见的检验方法,然而人工检验对工作人员的经验技术要求较高,同时检验质量难以得到有效保证。

2、虽然目前已经出现了基于视觉、光学检测等技术的新型芯片引线键合质量检测方法和设备,但在成本、检测精度等方面仍有很大的提升空间。申请号为2022109577432的专利公开了一种芯片引脚缺陷的检测方法、检测装置及设备,经过相机标定及立体校正后,得到校正后检测图像中待检测芯片映射到实际三维空间中的空间三维坐标,基于所述空间三维坐标建立重建后的芯片三维图像,完成了3d建模,基于完成的芯片三维图像进行引脚缺陷检测,最终得到检测结果。然而该方法在检测精度方面仍有提升空间。

技术实现思路

1、本发明的目的在于提供一种芯片引线键合质量检测方法、系统及存储介质,提出了多通道信息融合的图像处理方法,以获取芯片引线的精确几何模型信息,同时针对芯片引线不同的质量缺陷,建立芯片引线键合质量检测的数学模型,设计实现相关的算法,从而提高芯片引线键合的检测质量和效率。

2、实现本发明目的的技术解决方案为:

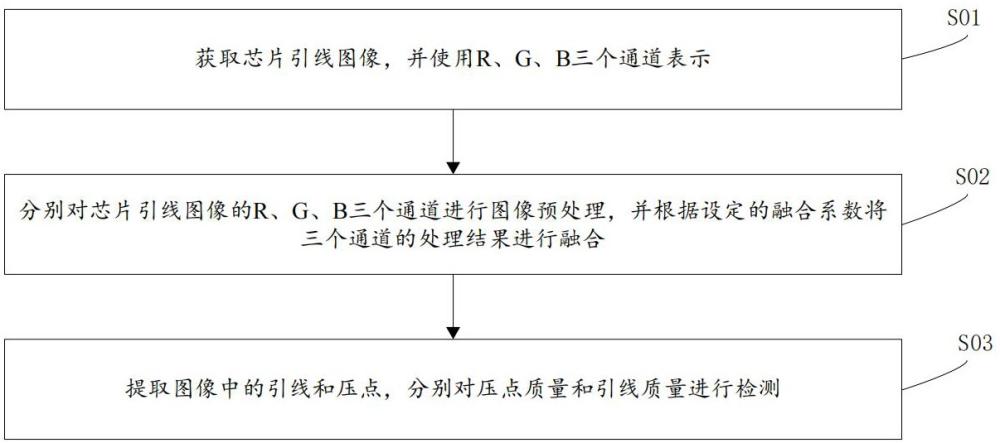

3、一种芯片引线键合质量检测方法,包括以下步骤:

4、s01:获取芯片引线图像,并使用r、g、b三个通道表示;

5、s02:分别对芯片引线图像的r、g、b三个通道进行图像预处理,并根据设定的融合系数将三个通道的处理结果进行融合;

6、s03:提取图像中的引线和压点,分别对压点质量和引线质量进行检测。

7、优选的技术方案中,所述步骤s01中通过芯片引线键合视觉系统获取芯片引线图像,所述芯片引线键合视觉系统包括照明系统、ccd显微摄像系统、图像采集卡及存储系统,所述照明系统将led光源作为芯片成像光源,并从正面和侧面两个方向进行照明,其中正面照明使用面阵led形成同轴光的照明结构,同时通过菲涅尔透镜汇聚光线,侧面光照采用可调节的结构,根据具体场景进行微调,对芯片视场进行光照补偿,在菲涅尔透镜与工作台之间青协设置有一个半透半反射镜,使ccd相机离轴成像。

8、优选的技术方案中,所述步骤s02中分别对芯片引线图像的r、g、b三个通道进行图像预处理的方法包括:

9、对图像的每个通道进行去噪,通过自适应中值滤波算法去除椒盐噪声,通过高斯滤波器去除高斯噪声;

10、使用大律法二值化算法将每个通道进行二值化处理,使用canny算法分别对图像的每个通道进行边缘检测和提取。

11、优选的技术方案中,所述自适应中值滤波算法去除椒盐噪声的方法包括:

12、设置一个大小为的矩形窗口,其中、分别为窗口的宽和高,、的最大值分别为、,设窗口的中心像素点坐标为,其中像素最小值为,像素最大值为,像素中值为,中心点的像素值为,自适应中值滤波算法的计算流程如下:

13、s11:计算、,如果且,跳转至步骤s13,否则执行步骤s12;

14、s12:增大窗口尺寸,如果新的窗口尺寸小于、,重复步骤s11,否则输出为点的像素值;

15、s13:计算、,如果且,说明点不是噪声点予以保留,否则输出为点的像素值。

16、优选的技术方案中,所述高斯滤波器去除高斯噪声的方法包括:

17、设、为图像通道中某一点的像素坐标,表示该点的像素值,高斯滤波的计算公式为:

18、

19、其中,为滤波后的像素值,为高斯滤波器的标准差;

20、设置高斯滤波窗口大小为5×5、,计算得到的高斯滤波窗口为:

21、

22、优选的技术方案中,所述步骤s02中将三个通道的处理结果进行融合的计算方法为:

23、

24、其中,表示通道中点处的像素值,为融合系数,表示融合后点的实际像素值;

25、计算公式为:

26、

27、其中,、分别为点的一个邻域窗口的大小,、分别为像素点坐标的行列索引值。

28、优选的技术方案中,所述步骤s03中对压点质量进行检测的方法包括:

29、计算每个压点的面积:

30、

31、其中,为压点的索引,为压点所覆盖的区域,为压点区域的面积,为图像中的一点,表示仅计算位于内的像素点;

32、计算每个面积与平均面积的差值:

33、

34、其中,表示所有压点的平均面积,表示压点的面积与的差值;

35、当差值大于一定阈值时,说明当前压点在键合时可能存在缺陷,进一步计算压点中心的偏移程度:

36、

37、其中,为中心偏移值,、为图像像素点坐标,为像素值,、为压点区域的三阶矩,、为压点区域的一阶矩,图像矩的计算公式为:

38、

39、其中,、为阶数;

40、当的值接近0时说明压点的偏移较小,当大于一定阈值时,判定当前压点存在较大的超差。

41、优选的技术方案中,所述步骤s03中对引线质量进行检测的方法包括:

42、通过计算每根引线的准直度进行判断,准直度的计算公式为:

43、

44、其中,为引线的索引,为引线的准直度,为引线的长度,为引线所占据的区域,为引线的0阶矩;

45、获取每根引线的准直度后,通过与其他同类引线的准直度值进行比较,当存在差值较大的引线时,判定该引线存在键合质量问题。

46、本发明还公开了一种芯片引线键合质量检测系统,包括:

47、芯片引线图像获取模块,获取芯片引线图像,并使用r、g、b三个通道表示;

48、图像处理模块,分别对芯片引线图像的r、g、b三个通道进行图像预处理,并根据设定的融合系数将三个通道的处理结果进行融合;

49、质量检测模块,提取图像中的引线和压点,分别对压点质量和引线质量进行检测。

50、本发明又公开了一种计算机存储介质,其上存储有计算机程序,所述计算机程序被执行时实现上述的芯片引线键合质量检测方法。

51、本发明与现有技术相比,其显著优点为:

52、针对芯片封装中引线键合的质量检测问题,基于机器视觉和图像处理算法,设计了引线成像系统以提高芯片成像质量,为了提高芯片引线的检测精度,提出了多通道信息融合的图像处理方法,以获取芯片引线的精确几何模型信息。同时针对芯片引线不同的质量缺陷,建立芯片引线键合质量检测的数学模型,从而提高了芯片引线键合的检测质量和效率,具有自动化程度高、检测精度优良的优点,能够有效提升不合格芯片键合引线的检出率,提高芯片产品的封装质量和良率,进而提升芯片运行的稳定性和可靠性。具有广阔的应用市场空间和经济价值。

- 还没有人留言评论。精彩留言会获得点赞!