具有OTP单元的MRAM存储器的制作方法

具有otp单元的mram存储器

技术领域

1.本发明大体上涉及一种mram,且更确切地说,涉及一种具有otp单元的mram。

背景技术:

2.磁阻随机存取存储器(magnetoresistive random access memory,mram)是其存储器单元使用磁性状态存储信息的存储器。通过某一mram,可以存储非易失性存储器并且可以在存储器的使用寿命内多次写入单元。

技术实现要素:

3.根据一种实施方式,一种磁阻随机存取存储器(mram)包括:

4.mram阵列,所述mram阵列包括布置成行和列的mram单元,所述mram阵列的每个mram单元包括磁性隧道结(mtj),所述磁性隧道结包括对应自由层和对应隧道介电层;

5.数据写入电路,所述数据写入电路被配置成在一次可编程(otp)写入模式下或在非otp写入模式下写入到所述mram阵列的mram单元,其中:

6.在所述otp写入模式下,所述数据写入电路被配置成跨越所述mram阵列的一组mram单元中的选定mram单元提供高写入电压量值,以便永久性地熔断所述选定mram单元的所述对应隧道介电层以存储逻辑值,以及

7.在所述非otp写入模式下,所述数据写入电路被配置成跨越待写入的选定mram单元提供低于所述高写入电压量值的较低写入电压量值,其中所述较低写入电压量值设置所述待写入的选定mram单元中的mram单元的自由层的磁化,以将所述mram单元的电阻调节到电阻状态以将逻辑值存储在所述mram单元中,而不熔断所述mram单元的所述对应隧道介电层。

8.在一个或多个实施方式中,在所述非otp写入模式下,当跨越mram单元提供的所述较低写入电压量值具有第一极性时,第一逻辑值存储于所述mram单元中,并且当跨越所述mram单元提供的所述较低写入电压量值具有与所述第一极性相反的第二极性时,与所述第一逻辑值相反的第二逻辑值存储于所述mram单元中。

9.在一个或多个实施方式中,在所述otp写入模式下,所述数据写入电路被配置成跨越所述一组mram单元中的非选定mram单元提供电压量值,所述电压量值不会熔断所述未选定mram单元的所述对应隧道介电层。

10.在一个或多个实施方式中,mram阵列被配置成接收指示待写入的一组mram单元的访问地址,所述mram还包括控制电路,所述控制电路被配置成接收所述访问地址并且基于所述访问地址产生otp模式指示符,其中所述数据写入电路被配置成基于otp模式指示符在所述otp写入模式下或在所述非otp写入模式下写入到所述mram阵列的mram单元。

11.在一个或多个实施方式中,所述控制电路包括存储电路,所述存储电路被配置成存储表示为otp地址的所述mram阵列的地址,其中如果所述访问地址表示为所述存储电路中的otp地址,则在写入到所述访问地址时,所述otp模式指示符指示所述otp写入模式。

12.在一个或多个实施方式中,所述的mram还包括读取电路,所述读取电路被配置成在otp读取模式下或在非otp读取模式下读取所述mram阵列的mram单元,其中:

13.在所述非otp读取模式下,所述读取电路被配置成使用mram参考电阻从所述mram阵列的选定mram单元读取数据,其中具有高mram电阻状态的mram单元具有比所述mram参考电阻更高的电阻,并且其中具有低mram电阻状态的mram单元具有比所述mram参考电阻更低的电阻,以及

14.在所述otp读取模式下,所述读取电路被配置成使用otp参考电阻从所述mram阵列的选定mram单元读取数据,其中非熔断mram单元具有比所述otp参考电阻高的电阻,而不管所述非熔断mram单元的mram电阻状态,并且所述otp参考电阻具有比熔断otp mram单元高的电阻。

15.在一个或多个实施方式中,所述mram阵列被配置成接收指示待读取的选择性mram单元的读取访问地址,其中如果所述读取访问地址对应于所述mram阵列的otp地址,则所述选定mram单元在otp读取模式下读取,并且如果所述读取访问地址对应于所述mram阵列的非otp地址,则所述选定mram单元在所述非otp读取模式下读取。

16.在一个或多个实施方式中,所述读取电路包括多个感测放大器,每个感测放大器用于在数据读取期间将mram单元的电阻与参考电阻相比较,其中在所述otp读取模式下,所述多个感测放大器将所述otp参考电阻用作所述参考电阻,并且在所述非otp读取模式下,所述多个感测放大器将所述mram参考电阻用作所述参考电阻。

17.在一个或多个实施方式中,所述写入电路在所述otp写入模式下将数据写入到所述mram阵列的第一多个行,并且所述写入电路在所述非otp写入模式下将数据写入到所述mram阵列的第二多个行。

18.在一个或多个实施方式中,所述mram阵列的每一mram单元具有相同mtj结构。

19.根据另一实施方式,一种磁阻随机存取存储器(mram)包括:

20.mram阵列,所述mram阵列包括mram单元,所述mram阵列的每个mram单元包括磁性隧道结(mtj),所述磁性隧道结包括对应自由层和对应隧道介电层,其中所述mram阵列的每个mram单元具有相同mtj结构并且所述mram阵列包括:

21.表示为otp单元的第一多个所述mram单元,以及

22.表示为非otp mram单元的第二多个所述mram单元;

23.解码器电路,所述解码器电路被耦合成接收访问地址,所述访问地址寻址所述mram阵列的所述mram单元的子集以用于数据访问;

24.数据写入电路,所述数据写入电路被配置成当所述mram单元的所述子集处于所述第一多个所述mram单元中并且所述数据访问是写入访问时,使用一次可编程(otp)写入模式,以及当所述mram单元的所述子集处于所述第二多个所述mram单元中并且所述数据访问是写入访问时,使用非otp写入模式将接收到的数据写入到所述mram单元的所述子集;以及

25.读取电路,所述读取电路被配置成当所述mram单元的所述子集处于所述第一多个所述mram单元中并且所述数据访问是读取访问时,使用otp读取模式,以及当所述mram单元的所述子集处于所述第二多个所述mram单元中并且所述数据访问是读取访问时,使用非otp读取模式从所述mram单元的子集读取数据。

26.在一个或多个实施方式中:

27.在所述otp写入模式下,所述数据写入电路被配置成跨越所述mram单元的子集中的选定mram单元提供高写入电压量值,以便永久性地熔断所述选定mram单元的所述对应隧道介电层以存储逻辑值,以及

28.在所述非otp写入模式下,所述数据写入电路被配置成跨越待写入的所述mram单元的子集中的mram单元提供低于所述高写入电压量值的较低写入电压量值,其中所述较低写入电压量值设置所述mram单元的所述子集中的mram单元的自由层的磁化,以将所述mram单元的电阻调节到mram电阻状态以存储逻辑值,而不熔断所述mram单元的所述对应隧道介电层。

29.在一个或多个实施方式中,在所述非otp写入模式下,当跨越所述mram单元的所述子集中的mram单元提供的所述较低写入电压量值具有第一极性时,第一逻辑值存储于所述mram单元中,并且当跨越所述mram单元的所述子集中的mram单元提供的所述较低写入电压量值具有与所述第一极性相反的第二极性时,与所述第一逻辑值相反的第二逻辑值存储于所述mram单元中。

30.在一个或多个实施方式中,所述数据写入电路被配置成将高电阻ram状态或低mram电阻状态写入到尚未被熔断的所述mram单元的所述子集中的未选定mram单元。

31.在一个或多个实施方式中,在所述otp写入模式下,所述数据写入电路被配置成跨越所述mram单元的所述子集中的非选定mram单元提供电压量值,以不熔断所述子集中的所述未选定mram单元的所述对应隧道介电层。

32.在一个或多个实施方式中:

33.在所述非otp读取模式下,所述读取电路被配置成使用mram参考电阻从所述mram单元的所述子集读取数据,其中具有高mram电阻状态的所述mram阵列的mram单元具有比所述mram参考电阻更高的电阻,并且其中具有低mram电阻状态的所述mram阵列的mram单元具有比所述mram参考电阻更低的电阻;

34.在所述otp读取模式下,所述读取电路被配置成使用otp参考电阻从所述mram单元的所述子集读取数据,其中非熔断mram单元具有高于所述otp参考电阻的电阻,而不管所述非熔断mram单元的mram电阻状态,并且所述otp参考电阻具有比熔断mram更高的电阻。

35.在一个或多个实施方式中,所述读取电路包括多个感测放大器,每个感测放大器用于在数据读取期间将mram单元的电阻与参考电阻相比较,其中在所述otp读取模式下,所述多个感测放大器将所述otp参考电阻用作所述参考电阻,并且在所述非otp读取模式下,所述多个感测放大器将所述mram参考电阻用作所述参考电阻。

36.在一个或多个实施方式中,所述的mram还包括存储电路,所述存储电路被配置成存储所述otp单元的地址的指示。

37.在一个或多个实施方式中,所述第一多个所述mram单元包括所述mram阵列的一个或多个行。

38.根据另一种实施方式,在包括mram单元的mram阵列中,所述mram阵列的每个mram单元包括磁性隧道结(mtj),所述磁性隧道结包括对应自由层和对应隧道介电层,一种方法包括:

39.对所述mram阵列的写入访问地址执行写入访问,其中所述写入访问地址寻址第一多个mram单元;

40.确定所述写入访问需要一次可编程(otp)写入模式还是非otp写入模式;

41.当所述写入访问需要所述otp写入模式时,所述写入访问包括:

42.跨越所述第一多个mram单元中的选定mram单元提供高写入电压量值,以便永久性地熔断所述选定mram单元的所述对应隧道介电层;以及

43.当所述写入访问需要所述非otp写入模式时,所述写入访问包括:

44.跨越所述第一多个mram单元中的mram单元提供低于所述高写入电压量值的较低写入电压量值,其中所述较低写入电压量值设置所述mram单元中的mram单元的自由层的磁化,以将所述mram单元的电阻调节到mram电阻状态以将逻辑值存储在所述mram单元中,而不熔断所述mram单元的所述对应隧道介电层。

45.在一个或多个实施方式中,所述的方法还包括:

46.对所述mram阵列的读取访问地址执行读取访问,其中所述读取访问地址寻址第二多个mram单元;

47.确定所述读取访问地址需要otp读取模式还是非otp读取模式;

48.当所述读取访问地址需要所述otp读取模式时,所述方法包括:

49.使用mram参考电阻从所述第二多个mram单元读取数据,其中具有高mram电阻状态的mram单元具有比所述mram参考电阻更高的电阻,并且其中具有低mram电阻状态的mram单元具有比所述mram参考电阻更低的电阻;以及

50.当所述读取访问地址需要所述非otp读取模式时,所述方法包括:

51.使用otp参考电阻从所述第二多个mram单元读取数据,其中非熔断mram单元具有比所述otp参考高的电阻,而不管所述非熔断mram单元的mram电阻状态,并且所述otp参考电阻具有比熔断otp mram单元更高的电阻。

52.在一个或多个实施方式中,所述确定所述写入访问需要otp写入模式还是非otp写入模式,以及所述确定所述读取访问地址需要otp读取模式还是非otp读取模式包括:访问存储电路以确定所述写入访问地址或所述读取访问地址指示为otp地址。

附图说明

53.通过参考附图,可以更好地理解本发明,并且使其众多目标、特征和优点对本领域的技术人员显而易见。

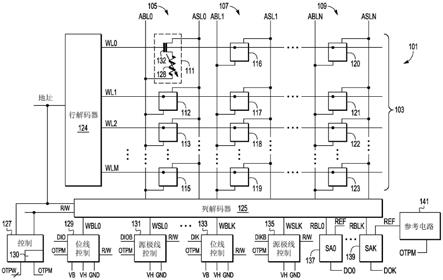

54.图1是根据本发明的一个实施例的mram的图式。

55.图2是根据本发明的一个实施例的图1的mram单元的侧视图。

56.图3是根据本发明的一个实施例的参考电阻电路的电路图。

57.图4是示出根据本发明的一个实施例的mram阵列的单元的电阻分布的图形。

58.图5是说明根据本发明的一个实施例的用于mram读取模式和otp读取模式的电阻状态与数据值之间的关系的图表。

59.图6是根据本发明的一个实施例的写入到mram的方法的流程图。

60.图7是根据本发明的实施例的读取mram的方法的流程图。

61.除非另外指出,否则在不同附图中使用相同附图标记指示相同的物品。各图未必按比例绘制。

具体实施方式

62.下文阐述用于进行本发明的模式的详细描述。所述描述旨在说明本发明且不应被视为是限制性的。

63.如本文所公开,mram包括可以用作可再编程mram单元或一次可编程(one-time programmable,otp)装置的mram单元的阵列。在一些实施例中,阵列的一些mram单元可以用作otp装置,其中在otp模式写入期间,单元的磁性隧道结(magnetic tunnel junction,mtj)的隧道介电层被“熔断”,以提供可从未熔断单元的电阻确定的永久电阻,而不管单元的磁性状态如何。在非otp写入模式中,设定mtj的自由层的磁化方向以存储特定逻辑值。在非otp模式写入期间,未熔断单元的介电隧道层。在一些实施例中,mram具有两个读取模式。一个读取模式用于读取mram阵列的otp单元,且另一读取模式用于读取阵列的非otp单元的磁性状态。在一些实施例中,不同模式涉及在mram的读取操作期间将不同参考电阻提供到感测放大器。

64.图1是根据本发明的一个实施例的mram的图式。存储器101包括位于行和列(105、107及109)中的用于存储数据的mram单元的阵列103。列105包括单元111至115,列107包括单元116至119,并且列109包括单元120至123。在一个实施例中,每个单元(111)表征为mram单元,该mram单元包括磁性隧道结(magnetic tunnel junction,mtj)(针对单元111,128)以及存取晶体管(针对单元111,132),该存取晶体管的控制端耦合到字线(wl0至wlm),该字线被确证存取存储器单元的特定行以读取单元或写入到单元。在图1的视图中未示出用于单元112至123的mtj和存取晶体管。字线(wl0至wlm)由地址行解码器124提供并且基于由地址线(address)上的解码器124从处理电路(未示出)接收的存取请求的存储器地址来选择性地进行确证。列的每个单元(111)连接到列的阵列位线(abl0至abln)和阵列源极线(asl0至asln)。在所示实施例中,单元(111)在存取晶体管(132)的源极处连接到源极线(asl0)。尽管图1示出阵列103包括四个行(对应于字线wl0至wlm)和三个列(105、107和109),但是其它实施例可以包括不同数目的行(m)和/或不同数目的列(n)。

65.在一些实施例中,mram阵列103的单元的mtj具有相同结构。如本文中所使用,具有相同结构的mtj意味着mtj的对应结构具有相同三维尺寸并且在制造公差内由相同材料制成。如本文相对于存储于存储器中的信息所使用,术语“数据”还包括存储于存储器中的指令或命令。

66.存储器101包括数据读取电路,用于读取存储于阵列103的单元中的数据。在所示实施例中,读取电路包括感测放大器137和139,每一个感测放大器用于通过将存储器单元的电阻与参考电阻(ref)相比较来感测存储于存储器单元中的数据值。在读取操作期间,感测放大器(137)通过列解码器125耦合到选定列(例如,105)的位线(例如,abl0),以将所述列的选定单元(例如,111)的电阻与参考电阻(ref)相比较。感测放大器137和139将读取数据(do0至dok)输出到数据总线(未示出)上的处理电路(未示出)。由参考电路141提供参考电阻。

67.存储器101包括用于将输入写入到阵列103的存储器单元的数据写入电路。在所示实施例中,数据写入电路包括位线控制电路129和133,用于在对阵列的选定单元的存储器写入操作期间控制选定列的阵列位线(abl0、abln)的电压。数据写入电路还包括源极线控制电路131和135,用于在对选定单元的存储器写入操作期间控制选定列的阵列源极线

(asl0、asln)的电压。

68.在所示实施例中,列解码器125在存储器写入操作期间将选定阵列列(105、107和109)的阵列位线(abl0、abl1、abln)选择性地耦合到位线控制电路(129和133),并且将选定阵列列的对应阵列源极线(asl0、asl1和asln)选择性地耦合到源极线控制电路(131和135)。在所示实施例中,列解码器125在存储器读取操作期间将选定列(105、107和109)的阵列位线(abl0、abl1、abln)选择性地耦合到感测放大器(137和139),并且将选定列的阵列源极线(asl0、asl1、asln)选择性地耦合到源极线控制电路(131和135)。

69.在一个实施例中,解码器125的解码率(n/k)是8∶1,其中n是阵列列的数目并且k是感测放大器/线控制电路对的数目。然而,在其它实施例中,此比率可以具有其它值(例如,1、4、16)。在一个实施例中,k是64并且n是512,但是在其它实施例中,这些可以具有不同值。一些实施例不包括列解码器,其中每个列包括其自身的感测放大器以及位线控制电路/源极线控制电路对。在一些实施例中,位线控制电路(129)可以与感测放大器(137)集成。列解码器125接收来自地址线的地址的一部分以及读取/写入(r/w)信号,用于确定选择哪些列。

70.在一个实施例中,存储器101与请求存储器存取的处理电路(未示出)位于相同集成电路上。在其它实施例中,存储器101可以位于单独的集成电路上。在又其它实施例中,存储器101可以具有其它配置。

71.阵列103的单元可以用于mram模式,其中可以写入、读取数据并且将数据的非易失性存储于单元中,或者可以用于otp模式,其中在单元中永久性编程数据状态。在一个实施例中,可以在otp模式下逐行地和/或逐列地实施单元。

72.图2是根据本发明的一个实施例的mram单元111的侧视图。在所示实施例中,单元111的存取晶体管132是具有位于集成电路的半导体衬底203中的源极区209和漏极区211的平面晶体管。源极区209连接到阵列源极线asl0。漏极区211通过通孔203连接到磁性隧道结(magnetic tunnel junction,mtj)128,该通孔203位于mram的集成电路的一个或多个互连层中。晶体管132的栅极207连接到字线wl0。

73.在所示实施例中,mtj 128包括导电接触层214、钉扎磁性层215、隧道介电层217,以及自由磁性层219。在所示实施例中,mtj 128还包括另外的层221,该另外的层221包括导电层。在一个实施例中,钉扎磁性层215和自由磁性层219由例如钴铁硼(cofeb)的铁磁性材料制成,并且隧道介电层由例如氧化镁(mgo)的介电材料制成。然而,在其它实施例中,这些层可以由其它材料制成。而且在其它实施例中,mram单元可以具有其它配置。

74.固定钉扎层215的磁化方向。自由层219的磁化方向可以被编程为与钉扎层215的磁化方向处于平行方向或反平行方向,以便将1或0值存储于存储器单元中。当自由层219的磁化方向在反平行方向上时,mtj的电阻处于相对较高值。当自由层219的磁化方向在平行方向上时,mtj的电阻具有相对较低值。当在mram模式下的读取期间,感测放大器耦合到单元的阵列位线以及处于高电阻值与低电阻值之间的参考电阻两者时,可以关于1值(例如,高电阻状态)还是0值(例如,低电阻状态)存储于mtj中进行确定。

75.在mram模式下的写入操作期间,通过跨越mtj施加足够量值的电压差,以产生用于设置自由层219的磁化方向来设置自由层219的磁化方向。在一个实施例中,通过在晶体管132导电时将较高电压(vh)施加到阵列位线(abl0)以及将较低电压(gnd)施加到源极线(asl0),可以在一个方向上设置自由层219的磁化方向,以及通过将较低电压(gnd)施加到

阵列位线以及将较高电压(vh)施加到阵列源极线,可以在另一方向上设置自由层219的磁化方向。

76.在一个实施例中,层214、215、217、219和221具有圆盘配置,其中图2所示的宽度是圆的直径。圆的表面积越大,切换单元的电阻状态所需的电压差就越大。在一个实施例中,vh与接地之间的电压差在1至2伏特的范围中,但是在其它实施例中可以具有其它值。

77.在otp模式下的写入操作期间,当与在未击穿隧道介电层的情况下未熔断单元(高电阻状态或低电阻状态)的电阻值相比,晶体管132有利于将隧道介电层217的电阻永久性地击穿至mtj 128具有相对较低电阻值的情况时,足够高的电压差可以施加在阵列位线与阵列源极线之间。如本文所使用,其隧道介电质已被永久性地击穿的单元被称为“熔断”单元。一旦单元已被熔断,无论自由层219的磁化方向如何,也无法对该单元进行再编程以提供高电阻值或低电阻值。

78.返回参考图1,存储器101的数据写入电路包括用于执行mram模式写入和otp模式写入的电路。控制电路127将otpm信号提供到位线控制电路129和133以及源极线控制电路131和135,以控制这些电路处于mram模式还是otp模式,以将数据写入到存储器单元。在写入操作期间,位线控制电路129和133各自接收数据输入值(di0、dik),并且对应的源极线控制电路131和135各自接收互补数据输入值(di0b、dikb)。在所示实施例中,电路129、131、133和135接收将在写入模式期间指示写入的读取/写入信号(r/w)。如果在mram写入模式(未确证otpm信号)中,取决于分别将写入到单元的di0和dik的值,位线控制电路129和133向选定位线提供高压(vh)或低压(gnd)(通过列解码器125)。在mram模式写入期间,源极线控制电路131和135分别提供与电路129和131所提供的电压值相反的电压值(vh或gnd),使得跨越每一单元的电压差具有适当极性以将所需值写入到单元。

79.在otp模式写入期间(当确证otpm信号时),取决于将0还是1写入到单元,位线控制电路129和133提供用于熔断单元的较高电压(vb),或用于不熔断单元的较低电压(例如,vh或gnd)。如果将写入0,则位线控制电路(129)将电压vb提供到位线以熔断单元。如果将写入1,则位线控制电路(129)将较低电压(例如,vh或gnd)提供到单元,使得单元不被熔断。在根据一个实施例的otp模式写入期间,源极线控制电路131将较低电压(gnd)提供到源极线,而不管将1还是0写入到单元。

80.在所示实施例中,位线控制电路129和133以及源极线控制电路131和135被示为接收电压vb、vh和接地(gnd)(例如,从电压调节器(未示出)),并且将那些电压中的一个选择性地供应到位线。在其它实施例中,位线控制电路和源极线控制电路可以包括电压调节器和/或电荷泵,其输出电压可调整用于提供不同电压。而且,较低电压电平可以是除了接地之外的另一电压电平(例如,例如200mv的负电压电平)。

81.在其它实施例中,位线控制电路129和133可以为mram模式写入和otp模式写入两者提供相同的高电压电平。在此种实施例中,与在mram模式写入期间相比,源极线控制电路131和135在otp模式写入期间提供较低电压,以在otp模式写入期间提供跨越mtj单元的较高电压差以熔断mram单元的mtj。

82.存储器101还包括读取电路,该读取电路可以在mram模式和otp模式两者中读取阵列103的mram单元。在所示实施例中,存储器101包括感测放大器137和139,每个感测放大器从参考电路141接收参考电阻(ref)。参考电阻在两个不同电阻值之间可选择,一个电阻值

用于mram模式读取且一个电阻值用于otp模式读取。

83.图3是根据一个实施例的参考电路141的一个实施例的电路图。电路141被设计成在otp模式读取期间提供与在mram模式读取期间不同的参考电阻。在所示实施例中,电路141包括四个电流支腿302、304、306和308。电路141包括与mram单元(128)的存取晶体管(132)具有相同大小的晶体管307、313、327、333、301、319、321以及339。当r/w信号指示读取时,这些晶体管进行导电。

84.电阻器305和325被设定大小以与在高电阻状态下编程的mtj提供相同电阻(rhm)。电阻器303、317、323和337被设定大小以与在低电阻状态下编程的mtj提供相同电阻(rlm)。晶体管315和335被设定大小以与在熔断状态下的mtj提供相同电阻(rbm)。电路141包括低阻抗开关309、311、329和331。将开关309和329关闭以耦合支腿302和306,以在mram模式读取期间提供参考电阻,并且将开关311和331关闭以耦合支腿304和308,以在otp模式读取期间提供参考电阻。电路141包括接收otpm信号的反相器341,并且提供用于控制开关309和329的反相otpmb信号。

85.当处于mram模式读取时,电路141提供介于rh与rl中间的参考电阻(rh+rl)/2。rh是在高电阻状态下编程的mram单元的电阻,该电阻等于rhm+rs,其中rs是在闭合状态下的晶体管307、313、327、333、301、319、321和339中的一个的电阻。rl是在低电阻状态下的mram单元的电阻,该电阻等于rlm+rs。当处于otp模式读取时,电路141提供介于rb与rl中间的参考电阻(rb+rl)/2。rb是熔断单元的电阻,该电阻等于rbm+rs。因为rb比rh小得多,所以otp模式读取电阻比mram模式读取电阻低得多。在一个实施例中,rhm是25k欧姆,rlm是10k欧姆,rbm是2k欧姆,并且rs是2k欧姆,但是在其它实施例中,这些可以具有其它值。在其它实施例中,其它参考单元可以具有其它配置。

86.图4是示出根据本发明的一个实施例的mram阵列的单元的电阻分布的图形。在图4中,电阻值在x轴上,并且具有特定电阻的单元的数目在y轴上。图4示出被熔断的mram阵列的单元以及未被熔断的mram阵列的那些单元的电阻分布。取决于在一个实施例中,单元的mtj的自由层的磁化方向与固定层的磁化处于平行方向还是反平行方向,未被熔断的单元处于低电阻状态或高电阻状态。

87.在所示实施例中,熔断单元具有以电阻值rb为中心的电阻分布401。低电阻状态单元具有以rl为中心的电阻分布403,并且高电阻状态单元具有以电阻rh为中心的电阻分布405。otp模式参考电阻居中于rb与rl之间。mram模式参考电阻居中于rl与rh之间。

88.在mram模式读取期间,向感测放大器提供mram参考电阻允许感测放大器区分低电阻单元与高电阻单元,以确定单元正存储0还是1。在otp模式读取期间,向感测放大器提供otp参考电阻允许感测放大器区分熔断单元与非熔断单元,而不管非熔断单元具有低电阻状态还是高电阻状态。

89.图5是说明根据一个实施例的用于mram读取模式和otp读取模式的电阻状态与数据值之间的关系的图表。第一行识别8个mram单元中已经受otp模式写入11011011的单元数目。在一个实施例中,在otp模式写入期间,熔断用“0”值写入的单元(在第二行中表示为“b”)。用“1”写入的单元未被熔断并且可以处于高电阻状态(hr)或低电阻状态(lr)。

90.如果在otp模式期间读取单元,其中将otp模式参考电阻提供给提供输出数据值的八个感测放大器,则将读取值11011011,因为将针对高电阻状态或低电阻状态读取1值。参

看图5的第三行。

91.然而,如果将在mram模式中读取单元,其中将mram模式参考电阻提供给感测放大器,则感测放大器将返回值10011000,其中低电阻单元和熔断单元两者将提供0值。

92.在一个实施例中,因为在otp模式写入期间,仅熔断用0写入的单元,所以存储器101使用较低otp模式参考电阻来读取单元,以便确定单元被熔断还是未被熔断,而不管非熔断单元具有高电阻值还是低电阻值。在一些实施例中,这可以允许单元群组用作otp单元,即使随后用高电阻值或低电阻值写入非熔断单元。

93.通过一些实施例,使用较低otp参考电阻的一个优点在于,当经受外部磁场时,可以不改变otp非熔断单元的所存储电阻。通过一些mram单元,将mram暴露于外部磁场可以使mram单元切换磁性状态(例如,从高电阻状态到低电阻状态,或反之亦然)。然而,因为mram的读取电路区分熔断单元和非熔断单元,而不管非熔断单元的电阻状态,所以otp存储数据可以不受外部磁场的损坏。此种特征在阻止外部磁场对mram的恶意攻击方面可能是有利的。在一些实施例中,可以通过otp模式写入将启动代码编程在mram中。如果在利用mram的系统中检测到磁场攻击,则相较于从mram模式写入单元中的可能受损代码重启,系统可以从otp模式写入单元中的代码重启。

94.此外,因为阵列103的单元的mtj都具有相同结构,所以在一些实施例中,对mram中的otp模式写入代码进行反向工程对于第三方可能更加困难。通过将mram单元用作otp装置的某一其它现有技术,otp mram单元具有使确定此类单元装置的位置相对更容易的不同结构(例如,不同大小)。然而通过本发明的一些实施例,无法通过mtj的物理形状确定otp单元的位置,由此使那些单元中的内容更加混淆。

95.返回参考图1,在所示实施例中,控制电路127具有存储器130,用于存储哪些行和/或阵列列包括将以otp模式写入和读取的otp单元。在一个实施例中,存储器可以由集成电路制造商、由系统制造商,或由最终用户可编程。在一些实施例中,可以配置mram 101,使得对访问存储器130进行加密以防止对存储器的未授权访问。在一个实施例中,存储器是非易失性存储器并且通过otpw线写入。在又其它实施例中,固定otp单元的行和/或阵列列(例如,受限于硬接线到控制电路127的电路地址)。在一些实施例中,包含otp单元的行/列将位于不连续地址中以使otp单元对反向工程隐藏。

96.图6是根据本发明的一个实施例的写入到mram的方法的流程图。在操作601中,在otp模式下对阵列103的第一地址执行写入操作。在写入操作期间,通过跨越单元的mtj产生vb的电压差,熔断对应于0值的单元。不熔断对应于1值的单元。在一个实施例中,对于未被熔断的单元,将位线电压和源极线电压设置成接地。在其它实施例中,对于未被熔断的单元,将高电阻mram值(或低电阻mram值)写入到未熔断单元以将单元置于已知的电阻mram状态。

97.在各种实施例中,操作601可以由集成电路制造商、系统制造商,或由最终用户执行。

98.在操作603中,执行第二值的mram模式下的写入操作,以将第二值写入到阵列的第二地址。在mram模式写入下,跨越第二地址的单元的mtj施加较低量值电压(vh)差,以将自由层的磁化调节到期望方向。在一些实施例中,跨越mtj施加的差分电压的极性确定将1还是0写入到单元。

99.在各种实施例中,操作603可以由集成电路制造商、系统制造商,或最终用户执行。在一些实施例中,执行操作603的实体可以是与执行操作601的实体不同的实体。

100.在操作605中,对第二地址进行第三值的mram模式下的写入操作,以在第二地址处覆写第二值。

101.图7是根据本发明的实施例的读取mram的方法的流程图。在操作701中,关于接收到的读取访问是对mram模式写入数据的地址还是对otp模式写入数据的地址进行确定。在一个实施例中,通过图1的控制电路127对来自处理系统(未示出)的总线的地址线上的所接收地址进行解码来进行此确定。

102.如果地址是mram写入数据的地址,则在操作703中,在mram模式下读取数据,其中将mram参考电阻作为参考电阻提供到感测放大器(137、139),以用于读取操作。mram参考电阻位于高电阻mram状态的电阻(在图4中表示为rh)与低电阻mram状态的电阻(在图4中表示为rl)之间。在一个实施例中,高电阻mram状态对应于存储1值的单元,并且低电阻mram状态对应于存储0值的单元。

103.如果地址是otp写入数据的地址,则在操作705中,在otp模式下读取数据,其中将otp参考电阻作为参考电阻提供到感测放大器(137、139),以用于读取操作。otp参考电阻位于熔断单元的电阻(在图4中表示为rb)与低电阻mram状态的电阻(在图4中表示为rl)之间。因此,如果单元具有高mram电阻或低mram电阻,则将产生指示单元是未熔断单元的值1。当电阻是熔断单元的电阻(rb)时将产生0。

104.在其它实施例中,可以通过其它操作执行mram模式读取和写入以及otp模式读取和写入。

105.在一个实施例中,磁阻随机存取存储器(magnetoresistive random access memory,mram)包括mram阵列,该mram阵列包括布置成行和列的mram单元。mram阵列的每个mram单元包括磁性隧道结(magnetic tunnel junction,mtj),该磁性隧道结包括对应自由层和对应隧道介电层。mram包括数据写入电路,该数据写入电路被配置成在一次可编程(one-time-programmable,otp)写入模式下或在非otp写入模式下写入到mram阵列的mram单元。在otp写入模式下,数据写入电路被配置成跨越mram阵列的一组mram单元中的选定mram单元提供高写入电压量值,以便永久性地熔断选定mram单元的对应隧道介电层以存储逻辑值。在非otp写入模式下,数据写入电路被配置成跨越待写入的选定mram单元提供低于高写入电压量值的较低写入电压量值。低写入电压量值设置待写入的选定mram单元中的mram单元的自由层的磁化,以将mram单元的电阻调节到电阻状态以将逻辑值存储在mram单元中,而不熔断mram单元的对应隧道介电层。

106.在另一实施例中,磁阻随机存取存储器(magnetoresistive random access memory,mram)包括mram阵列,该mram阵列包括mram单元。mram阵列的每个mram单元包括磁性隧道结(magnetic tunnel junction,mtj),该磁性隧道结包括对应自由层和对应隧道介电层。mram阵列的每个mram单元具有相同mtj结构。mram阵列包括表示为otp单元的第一多个mram单元,以及表示为非otpmram单元的第二多个mram单元。mram包括解码器电路,该解码器电路被耦合成接收访问地址,该访问地址寻址mram阵列的mram单元的子集以用于数据访问。mram包括数据写入电路,该数据写入电路被配置成当mram单元的子集处于第一多个mram单元中并且数据访问是写入访问时,使用一次可编程(one-time-programmable,otp)

写入模式,以及当mram单元的子集处于第二多个mram单元中并且数据访问是写入访问时,使用非otp写入模式将接收到的数据写入到mram单元的子集。mram包括读取电路,该读取电路被配置成当mram单元的子集处于第一多个mram单元中并且数据访问是读取访问时,使用otp读取模式,以及当mram单元的子集处于第二多个mram单元中并且数据访问是读取访问时,使用非otp读取模式从mram单元的子集读取数据。

107.在另一实施例中,在包括mram单元的mram阵列中,mram阵列的每个mram单元包括磁性隧道结(magnetic tunnel junction,mtj),该磁性隧道结包括对应自由层和对应隧道介电层。方法包括对mram阵列的写入访问地址执行写入访问。写入访问地址寻址第一多个mram单元。方法包括确定写入访问需要一次可编程(one-time-programmable,otp)写入模式还是非otp写入模式。当写入访问需要otp写入模式时,写入访问包括跨越第一多个mram单元中的选定mram单元提供高写入电压量值,以便永久性地熔断选定mram单元的对应隧道介电层。当写入访问需要非otp写入模式时,写入访问包括跨越第一多个mram单元中的mram单元提供低于高写入电压量值的较低写入电压量值,其中较低写入电压量值设置mram单元中的mram单元的自由层的磁化,以将mram单元的电阻调节到mram电阻状态以将逻辑值存储在mram单元中,而不熔断mram单元的对应隧道介电层。

108.虽然已经示出和描述本发明的具体实施例,但本领域的技术人员将认识到,基于本文中的教示,可以在不脱离本发明和其更广泛方面的情况下做出另外改变和修改,且因此所附权利要求书意图将在本发明的真实精神和范围内的所有此类改变和修改涵盖在其范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1