延迟锁相回路装置及其更新方法与流程

1.本发明涉及一种延迟锁相回路装置及其更新方法,尤其涉及一种能够降低消耗功率的延迟锁相回路装置及其更新方法。

背景技术:

2.当dram温度升高或降低时,延迟锁相回路(delay locked loop,dll)会更新延迟码以调整内存装置内部的时序。一般来说,延迟锁相回路可通过延迟码进行随时更新,藉以使延迟锁相回路所提供的延迟时钟能够实时地随着温度变化而变化。然而,上述的方案具有很大的消耗功率。

技术实现要素:

3.本发明提供一种能够降低消耗功率的延迟锁相回路装置及其更新方法。

4.本发明的延迟锁相回路装置适用于内存装置。延迟锁相回路装置包括延迟锁相回路以及更新电路。延迟锁相回路经配置以依据致能信号被致能后接收输入时钟,并且对输入时钟进行延迟以提供延迟时钟。更新电路包括旗标产生电路以及致能电路。旗标产生电路经配置以基于一默认时间区间提供更新旗标。致能电路耦接于旗标产生电路以及延迟锁相回路。致能电路经配置以依据更新旗标以将致能信号触发至第一逻辑电平,并在预设时间区间结束前将致能信号由第一逻辑电平转态至第二逻辑电平。默认时间区间小于内存装置的刷新周期。

5.在本发明的对延迟锁相回路进行更新的更新方法适用于内存装置。更新方法包括:基于一预设时间区间提供更新旗标,其中预设时间区间小于内存装置的刷新周期;依据更新旗标以将致能信号触发至第一逻辑电平,并在预设时间区间结束前将致能信号由第一逻辑电平转态至第二逻辑电平;以及依据致能信号致能延迟锁相回路,藉以使延迟锁相回路对输入时钟进行延迟以提供延迟时钟。

6.基于上述,本发明是基于一预设时间区间提供更新旗标,依据更新旗标以将致能信号触发至第一逻辑电平,并且在预设时间区间结束前将致能信号由第一逻辑电平转态至第二逻辑电平。本发明是在预设时间区间内致能延迟锁相回路。因此,延迟锁相回路是在预设时间区间内才对延迟码进行更新,藉以降低延迟锁相回路的消耗功率。

附图说明

7.包含附图以便进一步理解本发明,且附图并入本说明书中并构成本说明书的一部分。附图说明本发明的实施例,并与描述一起用于解释本发明的原理。

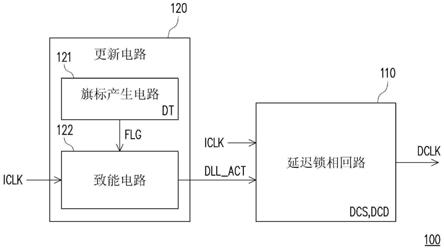

8.图1是依据本发明一实施例所示出的延迟锁相回路装置的装置示意图;

9.图2是依据本发明第一实施例所示出的更新电路的电路示意图;

10.图3是依据本发明第一实施例所示出的信号时序图;

11.图4是依据本发明第二实施例所示出的更新电路的装置示意图;

12.图5是依据本发明第二实施例所示出的信号时序图;

13.图6是依据本发明第三实施例所示出的更新电路的装置示意图;

14.图7是依据本发明第三实施例所示出的信号时序图;

15.图8是依据本发明一实施例所示出的更新方法流程图。

16.附图标号说明

17.100:延迟锁相回路装置;

18.110:延迟锁相回路;

19.120、220、320:更新电路;

20.121:旗标产生电路;

21.1211:振荡器;

22.1212:除频器;

23.122、222、322:致能电路;

24.2221、3321:更新指令产生器;

25.act:致能命令;

26.nand1、nand2:与非门;

27.and3:与门;

28.cmd_act:致能指令;

29.cmd_pre:结束指令;

30.cnt1、cnt2:计数器;

31.d:正反器的数据输入端;

32.dcd:延迟码;

33.dclk:延迟时钟;

34.dcs:延迟控制信号;

35.dt:预设时间区间;

36.dll_act:致能信号;

37.ff1_1、ff1_2、ff2:正反器;

38.flg:更新旗标;

39.iclk:输入时钟;

40.itc:内部时钟;

41.lgc:逻辑电路;

42.pre:刷新命令;

43.q:正反器的输出端;

44.rst:重置信号;

45.s:正反器的设定输入端;

46.s110~s130:步骤;

47.t1~t7:时间点;

48.tg1:第一触发器;

49.tg2:第二触发器;

50.u1:第一触发器的输出端;

51.ud_cmd:更新指令。

具体实施方式

52.现将详细地参考本发明的示范性实施例,示范性实施例的实例说明于附图中。只要有可能,相同组件符号在附图和描述中用来表示相同或相似部分。

53.请参考图1,图1是依据本发明一实施例所示出的延迟锁相回路装置的装置示意图。在本实施例中,延迟锁相回路装置100是被运用于内存装置中。延迟锁相回路装置100包括延迟锁相回路110以及更新电路120。延迟锁相回路110依据致能信号dll_act被致能后接收输入时钟iclk,并且对输入时钟iclk进行延迟以提供延迟时钟dclk。在本实施例中,更新电路120包括旗标产生电路121以及致能电路122。旗标产生电路121基于默认时间区间dt提供更新旗标flg。默认时间区间dt小于内存装置的刷新周期。举例来说明,如果内存装置的刷新周期是7.8微秒,则预设时间区间dt的时间可以被设定为4微秒(本发明不限于此)。致能电路122耦接于旗标产生电路121以及延迟锁相回路110。致能电路122依据更新旗标flg而将致能信号dll_act的逻辑电平触发至第一逻辑电平(例如是高逻辑电平,本发明不限于此)。延迟锁相回路110例如会反应于具有第一逻辑电平的dll_act被致能以提供延迟控制信号dcs,并依据延迟控制信号dcs中的延迟指令产生对应的延迟码dcd。致能电路122还并在默认时间区间dt结束前将致能信号dll_act由第一逻辑电平转态至第二逻辑电平(例如是低逻辑电平,本发明不限于此)。第二逻辑电平不同于第一逻辑电平。

54.在本实施例中,致能信号dll_act维持于第一逻辑电平的时间长度会短于预设时间区间dt。也就是说,致能信号dll_act维持于第一逻辑电平的时间长度会短于内存装置的刷新周期。延迟锁相回路110是在预设时间区间dt内才对延迟码进行更新,藉以降低延迟锁相回路110本身的消耗功率。此外,在预设时间区间dt小于内存装置的刷新周期的情况下,更新旗标flg的提供周期会小于刷新周期。因此,本实施例可使延迟锁相回路110所提供的延迟时钟dclk能够跟随着温度变化而变化。

55.请同时参考图1以及图2,图2是依据本发明第一实施例所示出的更新电路120的电路示意图。在本实施例中,旗标产生电路121包括振荡器1211以及除频器1212。振荡器1211提供内部时钟itc。除频器1212耦接于振荡器1211以及致能电路122。除频器1212对内部时钟itc进行除频。经除频后,除频器1212可使内部时钟itc的周期大致上等于默认时间区间dt,藉以将内部时钟itc转换为更新旗标flg。

56.在本实施例中,致能电路122包括正反器ff1_1、ff1_2以及计数器cnt1。正反器ff1_1、ff1_2彼此串联耦接。正反器ff1_1、ff1_2的设定输入端s分别接收输入时钟iclk。正反器ff1_1的数据输入端d耦接于除频器1212,藉以接收来自于除频器1212的更新旗标flg。正反器ff1_1的输出端q耦接至正反器ff1_2的数据输入端d。正反器ff1_2的输出端q用以输出致能信号dll_act。在本实施例中,彼此串联耦接的正反器ff1_1、ff1_2能够对在更新旗标flg被提供后通过第一个输入时钟iclk与更新旗标flg进行同步,并且在下一个输入时钟iclk将致能信号dll_act的逻辑电平触发至第一逻辑电平。也就是说,正反器ff1_1、ff1_2能够对更新旗标flg进行一个输入时钟iclk到两个输入时钟iclk之间的延迟,藉以产生具有第一逻辑电平的致能信号dll_act。在一些实施例中,正反器的数量可以大于2个,也就是说,致能电路122能够依据正反器的数量对更新旗标flg进行多个输入时钟iclk的延迟,藉

以产生具有第一逻辑电平的致能信号dll_act。

57.在本实施例中,计数器cnt1耦接于正反器ff1_2的输出端q以接收致能信号dll_act。计数器cnt1在接收到致能信号dll_act时会将致能信号dll_act维持于第一逻辑电平,并对输入时钟iclk的次数进行计数。当输入时钟iclk的次数达到一预设次数时,计数器cnt1将致能信号dll_act由第一逻辑电平转态至第二逻辑电平。

58.举例来说明,请同时参考图1至图3,图3是依据本发明第一实施例所示出的信号时序图。在本实施例中,旗标产生电路121在时间点t1基于预设时间区间dt提供更新旗标flg。预设时间区间dt大致上等于从时间点t1到时间点t4之间的时间长度(如,4微秒)。更新旗标flg被提供后(即,在时间点t1后)的时间点t2,致能信号dll_act的逻辑电平会在第二个输入时钟iclk的上升沿被触发至第一逻辑电平。因此,延迟锁相回路110会反应于具有第一逻辑电平的dll_act被致能以提供延迟控制信号dcs,并依据延迟控制信号dcs中的延迟指令(up或dn)产生对应的延迟码dcd。

59.在时间点t2,致能电路122的计数器cnt1也会开始对输入时钟iclk进行计数。在本实施例中,计数器cnt1例如是对输入时钟iclk的上升沿进行计数,本发明不限于此。在一些实施例中,计数器cnt1例如是对输入时钟iclk的下降沿进行计数。在本实施例中,当输入时钟iclk的次数达到预设次数(如,64次)时,计数器cnt1在时间点t3将致能信号dll_act由第一逻辑电平转态至第二逻辑电平。因此,在时间点t3时,延迟锁相回路110反应于具有第二逻辑电平的致能信号dll_act被禁能。

60.在本实施例中,预设时间区间dt的时间长度以及预设次数可以依据设计需求被适当地设定。因此,基于上述的设定,延迟锁相回路110是在预设时间区间dt内才对延迟码dcd进行更新,藉以降低延迟锁相回路110的消耗功率。另外,在预设时间区间dt的时间长度(如,4微秒)小于内存装置的刷新周期(如,7.8微秒)的情况下,本实施例可使延迟锁相回路110所提供的延迟时钟dclk能够实时地随着温度变化而变化。此外,本实施例能够不依赖于内存装置的外部命令提供致能信号dll_act。

61.请同时参考图1以及图4,图4是依据本发明第二实施例所示出的更新电路的装置示意图。在本实施例中,更新电路220包括旗标产生电路121以及致能电路222。致能电路222包括更新指令产生器2221、正反器ff1_1、ff1_2以及计数器cnt2。更新指令产生器2221在接收到更新旗标flg后反应于致能指令cmd_act产生更新指令ud_cmd。在本实施例中,更新指令产生器2221可包括触发器tg1、tg2。触发器tg1耦接于旗标产生电路121以接收更新旗标flg。触发器tg1反应于更新旗标flg的上升沿将位于触发器tg1的输出端u1的逻辑电平触发至第一逻辑电平。触发器tg1还会依据重置信号rst将位于触发器tg1的输出端u1的逻辑电平由第一逻辑电平转态至第二逻辑电平。

62.在本实施例中,触发器tg1接收更新旗标flg以及重置信号rst,并且对更新旗标flg以及重置信号rst进行反相。触发器tg1包括与非(nand)门nand1、nand2。与非门nand1的第一输入端用以接收被反相的更新旗标flg。与非门nand1的第二输入端耦接于与非门nand2的输出端。与非门nand1的输出端被作为触发器tg1的输出端u1。与非门nand2的第一输入端耦接于与非门nand1的输出端。与非门nand1的第二输入端用以接收被反相的重置信号rst。

63.在本实施例中,触发器tg2耦接于触发器tg1的输出端u1。在位于触发器tg1的输出

端u1的逻辑电平为第一逻辑电平的情况下,触发器tg2会反应于致能指令cmd_act的上升沿触发更新指令ud_cmd。在本实施例中,更新指令产生器2221可接收内存装置的外部命令(如致能命令)。在接收到外部命令时,更新指令产生器2221会依据输入时钟iclk的上升沿触发致能指令cmd_act。因此,在本实施例中,致能指令cmd_act的上升沿会与输入时钟iclk的上升沿同步。触发器tg2会依据重置信号rst重置更新指令ud_cmd。

64.在本实施例中,正反器ff1_1、ff1_2彼此串联耦接。正反器ff1_1、ff1_2的设定输入端s分别接收输入时钟iclk。正反器ff1_1的数据输入端d耦接于更新指令产生器2221,藉以接收来自于更新指令产生器2221的更新指令ud_cmd。正反器ff1_1的输出端q耦接至正反器ff1_2的数据输入端d。正反器ff1_2的输出端q用以输出致能信号dll_act。在本实施例中,彼此串联耦接的正反器ff1_1、ff1_2能够对在更新指令ud_cmd被提供时通过第一个输入时钟iclk与更新指令ud_cmd进行同步,并且在下一个输入时钟iclk依据更新指令ud_cmd将致能信号dll_act的逻辑电平触发至第一逻辑电平。也就是说,正反器ff1_1、ff1_2能够对更新指令ud_cmd进行一个输入时钟iclk到两个输入时钟iclk之间的延迟,藉以产生具有第一逻辑电平的致能信号dll_act。

65.在本实施例中,计数器cnt2耦接于正反器ff1_2的输出端q以接收致能信号dll_act。计数器cnt2在接收到致能信号dll_act时会将致能信号dll_act维持于第一逻辑电平,并对输入时钟iclk的次数进行计数。当输入时钟iclk的次数达到第一预设次数时,计数器cnt2会产生用以重置更新指令ud_cmd的重置信号rst。当输入时钟iclk的次数达到第二预设次数时,计数器cnt2将致能信号dll_act由第一逻辑电平转态至第二逻辑电平。第二预设次数大于第一预设次数。因此在致能信号dll_act被转态至第二逻辑电平之前,更新指令ud_cmd会被重置。因此,相较于第一实施例,本实施例可基于内存装置的外部命令提供致能信号dll_act。

66.举例来说明,请同时参考图1、图4以及图5,图5是依据本发明第二实施例所示出的信号时序图。在本实施例中,旗标产生电路121在时间点t1基于预设时间区间dt提供更新旗标flg。预设时间区间dt大致上等于从时间点t1到时间点t6之间的时间长度(如,4微秒)。更新旗标flg被提供后(即,在时间点t1后),位于触发器tg1的输出端u1的逻辑电平会被触发至第一逻辑电平。在位于触发器tg1的输出端u1的逻辑电平为第一逻辑电平的情况下,更新指令产生器2221接收到内存装置的外部命令中的致能命令act(本发明不限于此),并在时间点t2依据输入时钟iclk的上升沿触发致能指令cmd_act。因此在时间点t2,触发器tg2反应于致能指令cmd_act的上升沿将更新指令ud_cmd的逻辑电平触发至第一逻辑电平。

67.在时间点t3,在更新指令ud_cmd的上升沿与输入时钟iclk(即,第一个输入时钟iclk)的上升沿同步的情况下,致能信号dll_act的逻辑电平会在下一个输入时钟iclk(即,第二个输入时钟iclk)的上升沿被触发至第一逻辑电平。在本实施例中,致能指令cmd_act会依据输入时钟iclk的上升沿被重置。在一些情况下,更新指令ud_cmd因为延迟而使更新指令ud_cmd的时序落后于输入时钟iclk的时序。因此,时间点t3会被延迟到下一个输入时钟iclk的上升沿。本发明的致能信号dll_act的触发时间点并不以本实施例的时间点t3为限。在时间点t3,延迟锁相回路110会反应于具有第一逻辑电平的dll_act被致能以提供延迟控制信号dcs,并依据延迟控制信号dcs中的延迟指令产生对应的延迟码dcd。

68.在时间点t3,计数器cnt2也会开始对输入时钟iclk进行计数。在本实施例中,计数

器cnt2例如是对输入时钟iclk的上升沿进行计数。当输入时钟iclk的次数达到第一预设次数(如,31次)时,计数器cnt2会在时间点t4提供重置信号rst。在时间点t4,更新指令产生器2221会依据重置信号rst将位于触发器tg1的输出端u1的逻辑电平重置为第二逻辑电平,并将更新指令ud_cmd重置为第二逻辑电平。因此,更新指令ud_cmd的逻辑电平维持于第一逻辑电平的时间长度(即,时间点t2到时间点t4之间的时间长度)接近或等于输入时钟iclk的周期的32倍。

69.当输入时钟iclk的次数达到第二预设次数(如,64次)时,计数器cnt2会在时间点t5将致能信号dll_act的逻辑电平由第一逻辑电平转态至第二逻辑电平。因此,在时间点t5时,延迟锁相回路110会反应于具有第二逻辑电平的致能信号dll_act被禁能。

70.请同时参考图1以及图6,图6是依据本发明第三实施例所示出的更新电路的装置示意图。在本实施例中,更新电路320包括旗标产生电路121以及致能电路322。致能电路322包括更新指令产生器3321、正反器ff1_1、ff1_2、正反器ff2以及逻辑电路lgc。更新指令产生器3321在接收到更新旗标flg时反应于致能指令cmd_act产生更新指令ud_cmd。进一步地,在本实施例中,更新指令产生器3321包括触发器tg1以及触发器tg2。触发器tg1耦接于旗标产生电路121以更新旗标flg。触发器tg1反应于更新旗标flg的上升沿将位于触发器tg1的输出端u1的逻辑电平触发至第一逻辑电平。触发器tg1还会依据重置信号rst将位于触发器tg1的输出端u1的逻辑电平由第一逻辑电平转态至第二逻辑电平。触发器tg1时施细节可以由图4的实施例中获致足够的教示,故不再赘述。

71.在本实施例中,触发器tg2耦接于触发器tg1的输出端u1。在位于触发器tg1的输出端u1的逻辑电平为第一逻辑电平的情况下,触发器tg2会反应于致能指令cmd_act的上升沿触发更新指令ud_cmd。此外,触发器tg2依据结束指令cmd_pre重置更新指令ud_cmd。在本实施例中,更新指令产生器3321可接收内存装置的第一外部命令(如,致能命令)。在接收到第一外部命令时,更新指令产生器3321会依据输入时钟iclk的上升沿触发致能指令cmd_act。在本实施例中,更新指令产生器3321也会接收内存装置的第二外部命令(如,刷新命令)。在接收到第二外部命令时,更新指令产生器3321会依据输入时钟iclk的上升沿触发结束指令cmd_pre。因此,在本实施例中,致能指令cmd_act的上升沿会与输入时钟iclk的上升沿同步。结束指令cmd_pre的上升沿会与输入时钟iclk的上升沿同步。

72.在本实施例中,正反器ff1_1、ff1_2彼此串联耦接。正反器ff1_1、ff1_2的设定输入端s分别接收输入时钟iclk。正反器ff1_1的数据输入端d耦接于更新指令产生器3321,藉以接收来自于更新指令产生器3321的更新指令ud_cmd。正反器ff1_1的输出端q耦接至正反器ff1_2的数据输入端d。正反器ff1_2的输出端q用以输出致能信号dll_act。正反器ff2数据输入端d耦接至正反器ff1_2的输出端q。正反器ff2的设定输入端s分别接收输入时钟iclk。正反器ff2的输出端q对致能信号dll_act进行延迟以产生内部信号。逻辑电路lgc耦接于正反器ff2的输出端q以及正反器ff1_2的输出端q。逻辑电路lgc对内部信号进行反相,并且对致能信号dll_act以及被反相的内部信号进行逻辑及运算以产生重置信号rst。重置信号rst用以重置位于触发器tg1的输出端u1的逻辑电平。

73.进一步地,逻辑电路lgc包括与门and3。与门and3接收致能信号dll_act以及被反相的内部信号,并且对致能信号dll_act以及被反相的内部信号进行逻辑及运算以产生重置信号rst。相较于第一实施例以及第二实施例,本实施例可不需要计数器提供致能信号

dll_act或重置信号rst。

74.举例来说明,请同时参考图1、图6以及图7,图7是依据本发明第三实施例所示出的信号时序图。在本实施例中,关于时间点t1~t3的实施细节可以由第二实施例中获致足够的教示,故不再赘述。在时间点t4,逻辑电路lgc产生重置信号rst。因此在时间点t4,位于触发器tg1的输出端u1的逻辑电平会依据重置信号rst被重置。在本实施例中,重置信号rst可以被延迟以在时间点t4被产生。在一些实施例中,重置信号rst可以以在时间点t3被产生,本发明并不以重置信号rst的产生时间点为限。

75.接下来,更新指令产生器3321接收到外部命令中的刷新命令pre(本发明不限于此)。更新指令产生器3321会在时间点t5依据输入时钟iclk的上升沿触发结束指令cmd_pre。触发器tg2在时间点t5依据结束指令cmd_pre将更新指令ud_cmd的逻辑电平重置为第二逻辑电平。在时间点t6,致能信号dll_act的逻辑电平由第一逻辑电平转态至第二逻辑电平。因此,在时间点t6时,延迟锁相回路110会反应于具有第二逻辑电平的致能信号dll_act被禁能。在本实施例中,致能指令cmd_pre在时间点t6会依据输入时钟iclk的上升沿被重置(本发明不限于此)。

76.请同时参考图1以及图8,图8是依据本发明一实施例所示出的更新方法流程图。在本实施例中,更新方法会在步骤s110中基于预设时间区间dt提供更新旗标flg。默认时间区间dt小于内存装置的刷新周期。在步骤s120中,依据更新旗标flg以将致能信号dll_act触发至第一逻辑电平,并在预设时间区间dt结束前将致能信号dll_act由第一逻辑电平转态至第二逻辑电平。在步骤s130中,依据致能信号dll_act致能延迟锁相回路110,藉以使延迟锁相回路110对输入时钟iclk进行延迟以提供延迟时钟dclk。

77.综上所述,本发明是基于一预设时间区间提供更新旗标,依据更新旗标以将致能信号触发至第一逻辑电平,并且在预设时间区间结束前将致能信号由第一逻辑电平转态至第二逻辑电平。本发明是在预设时间区间内致能延迟锁相回路。因此,延迟锁相回路是在预设时间区间内才对延迟码进行更新,藉以降低延迟锁相回路的消耗功率。此外,在默认时间区间小于内存装置的刷新周期的情况下,本发明能够使延迟锁相回路所提供的延迟时钟能够跟随着温度变化而变化。

78.最后应说明的是:以上各实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述各实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1