传输电路、接口电路以及存储器的制作方法

[0001]

本实用新型实施例涉及半导体技术领域,特别涉及一种传输电路、接口电路以及存储器。

背景技术:

[0002]

动态随机存取存储器(dynamic random access memory,dram)是计算机中常用的半导体存储器件,由许多重复的存储单元组成。每个存储单元通常包括电容器和晶体管,晶体管的栅极与字线相连、漏极与位线相连、源极与电容器相连,字线上的电压信号能够控制晶体管的打开或关闭,进而通过位线读取存储在电容器中的数据信息,或者通过位线将数据信息写入到电容器中进行存储。

[0003]

dram可以分为双倍速率同步(double data rate,ddr)动态随机存储器、gddr(graphics double data rate)动态随机存储器、低功耗双倍速率同步(low power double data rate,lpddr)动态随机存储器。随着dram应用的领域越来越多,如dram越来越多的应用于移动领域,用户对于dram功耗指标的要求越来越高。

[0004]

然而,目前的dram性能仍有待提高。

技术实现要素:

[0005]

本实用新型实施例解决的技术问题为提供一种传输电路、接口电路以及促成年期,通过设置下层时钟焊盘以及下层数据焊盘实现集中化处理,以实现关键时钟的优化,从而提高时钟性能和减小功率损耗。

[0006]

为解决上述问题,本实用新型实施例提供一种传输电路,包括:上层时钟焊盘,用于传输时钟信号;m个上层数据焊盘,用于传输数据信号;下层时钟焊盘,与所述上层时钟焊盘电连接,且所述下层时钟焊盘的面积小于所述上层时钟焊盘的面积;m个下层数据焊盘,与所述m个上层数据焊盘一一对应的电连接,且所述下层数据焊盘的面积小于所述上层数据焊盘的面积;其中,所述上层时钟焊盘与所述上层数据焊盘位于第一层,所述下层时钟焊盘与所述下层数据焊盘位于第二层,在所述第一层和所述第二层之间包括介质层,所述第一层、所述介质层、所述第二层均位于同一衬底上,所述m为大于等于2的整数。

[0007]

另外,还包括:第一金属连线,所述第一金属连线位于所述下层时钟焊盘与所述上层时钟焊盘之间;第二金属连线,所述第二金属连线位于任一所述下层数据焊盘与所述下层数据焊盘对应的所述上层数据焊盘之间,所述第一金属连线的长度小于所述第二金属连线的长度。

[0008]

另外,所述第一金属连线包括:第一导电孔,所述第一导电孔贯穿所述介质层且与所述下层时钟焊盘相接触;第一金属层,所述第一金属层位于所述介质层远离所述第一层的一侧,且与所述第一导电孔以及所述上层时钟焊盘相接触;所述第二金属连线包括:第二导电孔,所述第二导电孔贯穿所述介质层且与所述下层数据焊盘相接触;第二金属层,所述第二金属层位于所述介质层远离所述第一层的一侧,且与所述第二导电孔以及所述上层数

据焊盘相接触;其中,所述第一导电孔的长度与所述第二导电孔的长度相同,所述第一金属层的长度小于所述第二金属层的长度。

[0009]

另外,所述第一金属连线包括:第一导电插塞,所述第一导电插塞贯穿所述介质层且与所述下层时钟焊盘以及所述上层时钟焊盘相接触;所述第二金属连线包括:第二导电插塞,所述第二导电插塞贯穿所述介质层且与所述下层数据焊盘以及所述上层数据焊盘相接触,且所述第一导电插塞的长度小于所述第二导电插塞的长度。

[0010]

另外,所述下层时钟焊盘和所述下层数据焊盘的面积相同。

[0011]

另外,还包括:多个下层测试焊盘,所述多个下层测试焊盘具有相同的面积,且所述下层测试焊盘的面积大于所述下层数据焊盘的面积。

[0012]

另外,所述上层时钟焊盘和所述m个上层数据焊盘布置于第一行,且所述m个上层数据焊盘布置于所述上层时钟焊盘的两侧,每一侧布置所述m个上层数据焊盘的一半。

[0013]

另外,所述下层时钟焊盘和所述m个下层数据焊盘布置于第二行,且所述m个下层数据焊盘布置于所述下层时钟焊盘的两侧,每一侧布置所述m个下层数据焊盘的一半。

[0014]

相应的,本实用新型实施例还提供一种接口电路,包括上述的传输电路;m个输入缓冲电路,与所述下层数据焊盘一一对应,每一个所述输入缓冲电路在所述时钟信号的驱动下,接收与所述输入缓冲电路对应的所述下层数据焊盘传输的所述数据信号;其中,所述下层时钟焊盘与所述下层数据焊盘布置于第一排,且所述m个下层数据焊盘布置于所述下层时钟焊盘的两侧,每一侧布置所述m个下层数据焊盘的一半,所述m个输入缓冲电路布置于第二排,以所述下层数据焊盘为基准,形成垂直于所述第一排的轴线,所述m个输入缓冲电路布置于所述轴线的两侧,每一侧布置所述m个输入缓冲电路的一半,每一个所述输入缓冲电路与所述轴线的距离小于所述输入缓冲电路对应的所述下层数据焊盘与所述轴线的距离。

[0015]

另外,每一个所述输入缓冲电路到所述输入缓冲电路对应的所述上层数据焊盘之间的输入数据路径长度为第一长度,每一个所述输入缓冲电路与所述上层时钟焊盘之间的时钟路径长度为第二长度,所述第一长度与所述第二长度成正相关。

[0016]

另外,所述下层时钟焊盘为差分输入焊盘,包括第一下层时钟焊盘和第二下层时钟焊盘,所述第一下层时钟焊盘与所述第二下层时钟焊盘分别传输互补的所述时钟信号。

[0017]

另外,所述第一下层时钟焊盘与所述第二下层时钟焊盘相对于所述轴线对称布置。

[0018]

另外,还包括:时钟处理电路,与所述下层时钟焊盘和所述m个输入缓冲电路均电连接,用于接收所述时钟信号,并将所述时钟信号进行处理后作为所述m个输入缓冲电路的驱动时钟。

[0019]

另外,所述时钟处理电路包括时钟接收电路和相位产生电路,所述时钟接收电路与所述下层时钟焊盘电连接,用于接收所述时钟信号,所述时钟接收电路的输出作为所述相位产生电路的输入,所述相位产生电路用于产生所述驱动时钟。

[0020]

另外,还包括:上层标志焊盘,用于传输标志信号,所述上层标志焊盘位于所述第一层;下层标志焊盘,与所述上层标志焊盘电连接,所述下层标志焊盘位于所述第二层,且所述下层标志焊盘的面积小于所述上层标志焊盘的面积;标志缓冲电路,与所述下层标志焊盘对应,用于在所述时钟信号的驱动下,接收所述上层标志焊盘传输的所述标志信号。

[0021]

另外,所述下层标志焊盘布置于所述第一排,且位于所述下层数据焊盘与所述下层时钟焊盘之间;所述标志缓冲电路布置于所述第二排,且与所述下层标志焊盘位于所述轴线的同一侧,且位于所述输入缓冲电路与所述轴线之间;所述标志缓冲电路与所述轴线的距离小于所述标志缓冲电路对应的所述下层标志焊盘与所述轴线的距离。

[0022]

另外,还包括:m个输出缓冲电路,与所述下层数据焊盘一一对应,每一个所述输出缓冲电路在所述时钟信号的驱动下,将所述数据信号发送至对应的下层数据焊盘。

[0023]

另外,每一个所述输出缓冲电路到所述输出缓冲电路对应的所述下层数据焊盘之间的输出数据路径长度相同。

[0024]

另外,所述输入缓冲电路包括多路选择器和锁存器,所述多路选择器接收所述数据信号,并将所述数据信号处理后输出给所述锁存器,所述锁存器的输出作为所述输入缓冲电路的输出。

[0025]

相应的,本实用新型实施例还提供一种存储器,包括上述的接口电路。

[0026]

与现有技术相比,本实用新型实施例提供的技术方案具有以下优点:

[0027]

本实用新型实施例提供一种结构性能优越的传输电路,m个上层数据焊盘以及上层时钟焊盘位于第一层,m个下层数据焊盘以及下层时钟焊盘位于第二层,且下层时钟焊盘的面积小于上层时钟焊盘的面积,下层数据焊盘的面积小于上层数据焊盘的面积。因此,相较于上层数据焊盘与上层时钟焊盘的位置关系而言,下层数据焊盘相对于下层时钟焊盘而言的距离更短,从而实现对下层数据焊盘的集中化处理,进而能够实现对输入缓冲电路进行集中化处理,缩短了时钟信号传输至各输入缓冲电路的时钟路径,提高了时钟路径与数据路径的匹配度,进而有利于减小tdqs2dq或twck2dq和时序违例;此外,由于时钟路径减小,进而降低了接口电路的功率损耗。

附图说明

[0028]

一个或多个实施例通过与之对应的附图中的图片进行示例性说明,这些示例性说明并不构成对实施例的限定,附图中具有相同参考数字标号的元件表示为类似的元件,除非有特别申明,附图中的图不构成比例限制。

[0029]

图1为一种接口电路的结构示意图;

[0030]

图2为本实用新型实施例提供的传输电路的等效电路布局示意图;

[0031]

图3为on die rdl的一种剖面结构示意图;

[0032]

图4为本实施例提供的传输电路的局部剖面结构示意图;

[0033]

图5为本实用新型实施例提供的接口电路的结构示意图;

[0034]

图6为本实用新型实施例提供的接口电路的一种示意图;

[0035]

图7为本实用新型实施例提供的接口电路的另一种布局示意图。

具体实施方式

[0036]

由背景技术可知,现有技术的dram性能仍有待提高。

[0037]

在存储器中,写数据采样信号(dqs信号或wck信号)作为写数据的时钟;在写入操作时,dqs信号或wck的边沿(上升沿和下降沿)在时序上应当与数据信号(dq信号)的中心处对齐(考虑到时序余量,也可能允许在中心处基本对齐)。dq信号的传输路径定义为数据路

径,数据路径的长短会影响dq信号的边沿到达器件端口(例如寄存器的数据端口)的时间,dqs或wck的传输路径定义为时钟路径,时钟路径的长短会影响dqs或wck信号到达器件端口(例如寄存器的时钟端口)的时间,将dq信号的数据路径与dqs或wck信号的时钟路径的差异(dqs或wck信号的边沿和dq信号的中心处之间的时间间隔)定义为tdqs2dq或twck2dq,tdqs2dq或twck2dq越小则数据路径与时钟路径越匹配,相应的电路时序越好。wck的应用情况与dqs相同或相似,例如在lpddr4中将时钟称为dqs,而在lpddr5中将时钟称为wck。

[0038]

现结合图1进行具体分析,图1为一种接口电路的结构示意图。

[0039]

参考图1,接口电路包括:用于传输数据信号的多个并排设置的数据焊盘11,中心轴线aa1,且多个数据焊盘11的一半分布于中心轴线aa1的一侧,另一半分布于中心轴线aa1的另一侧;时钟焊盘13,时钟焊盘13位于中心轴线aa1处;多个输入缓冲电路14,与数据焊盘11对应,且每个输入缓冲电路14到对应的数据焊盘11之间的数据路径相同(或在一定误差范围内基本相同,考虑到实际电路设计和制造过程中,路径相同只是一种理想情况,此处以及下文所述路径相同,均包括在一定误差范围内基本相同的含义,这里的一定误差范围可以理解但不限于不同路径之间的误差在1%以内或3%以内);多个输出缓冲电路(未图示),与数据焊盘101对应,且每个输出缓冲电路到对应的数据焊盘11之间的时序路径相同;时钟接收电路16和时钟产生电路17,时钟接收电路16与时钟焊盘13电连接,用于接收时钟信号并将时钟信号传输至时钟产生电路17,时钟产生电路17接收该时钟信号并产生驱动时钟,且输入缓冲电路14接收该驱动时钟以及数据信号并传输数据信号。

[0040]

图1中以dq0/dq1

…

dq7标示数据焊盘11,以clk标示时钟焊盘13,clk可以表示为dqs或wck,以rx0/rx1

…

rx7标示输入缓冲电路14,该输入缓冲电路14也为接收电路,以rx_clk标示时钟接收电路16,以clk gen标示时钟产生电路17。

[0041]

数据焊盘11的数据信号传输至对应的输入缓冲电路14的数据路径为第一路径,时钟焊盘的时钟信号传输至对应的输入缓冲电路14的时序路径为第二路径。在图1中,不同的输入缓冲电路14具有相同的第一路径,但是,距离时钟焊盘越远的输入缓冲电路14具有的第二路径越长,因此,距离时钟焊盘越远,相应的第一路径与第二路径之间的差距越大,导致对应的tdqs2dq或twck2dq越大,且时序违例的问题越严重,图1中标示出了距离时钟焊盘最远的输入缓冲电路14对应的tdqs2dq或twck2dq。

[0042]

不同的数据焊盘11的数据信号到达对应的输入缓冲电路14的时刻接近,以图1中离时钟焊盘最远和最近的输入缓冲电路14作为示例来说明,时钟信号达到离时钟焊盘13最远的输入缓冲电路14(dq0对应的输入缓冲电路14)的时刻最晚,且时钟信号到达离时钟焊盘最近的输入缓冲电路14(dq3对应的输入缓冲电路14)的时刻最早,这就造成离时钟焊盘最近的输入缓冲电路14最先接收并传输数据信号,而离时钟焊盘最远的输入缓冲电路14最晚传输数据信号,两个输入缓冲电路14传输数据信号的时间差距大。相应的,如果dq3对应的输入缓冲电路14的时钟路径与数据路径匹配,那么dq0对应的输入缓冲电路14的时钟路径与数据路径就不太容易匹配。

[0043]

具体地,结合图1,各数据焊盘11分别对应具有第一端口d0/d1

……

d7,各输入缓冲电路14分别具有与对应数据焊盘11的第一端口连接的第二端口r0/r1

…

r7,各输入缓冲电路14分别具有与时钟产生电路17连接的第三端口v0/v1

…

v7,时钟产生电路17具有与位于中心轴线aa1一侧的各输入缓冲电路14连接的第四端口c0,时钟产生电路17还具有与位于

中心轴线aa1另一侧的各输入缓冲电路14连接的第五端口c1。对于rx0而言,时钟信号的时钟路径为c0

→

v0,数据信号的数据路径为d0

→

r0;对于rx1而言,时钟信号的时钟路径为c1

→

v1,数据信号的数据路径为d1

→

r1;依次类推;不难发现,对于不同的输入缓冲电路14而言,其对应的数据路径不变,但是距离中心轴线aa1越近的输入缓冲电路14具有的时钟路径越短,因此,就出现了tdqs2dq或twck2dq差异较大的问题。

[0044]

由上述分析可知,不同的输入缓冲电路13对应的tdqs2dq或twck2dq差异较大,而在存储器中,对tdqs2dq或twck2dq的值有严格的要求,例如要求tdqs2dq或twck2dq的值不能大于800ps,否则会造成时序违例。

[0045]

为解决上述问题,本实用新型实施例提供一种传输电路,通过on die rdl(redistribution layer,重布线层)的方式设计分别与下层时钟焊盘以及下层数据焊盘连接的上层时钟焊盘以及上层数据焊盘,且下层时钟焊盘以及下层数据焊盘集中布局的方式,使得与下层数据焊盘连接的各输入缓冲电路也能够集中布局,从而缩短了时钟信号传输至各输入缓冲电路的时钟路径,缩短了时钟信号的时钟路径以及数据信号的数据路径的差值,从而缩短了tdqs2dq或twck2dq,进一步改善时序违例的问题。以下将结合附图对本实施例提供的接口电路进行详细说明。

[0046]

图2为本实用新型实施例提供的传输电路的等效电路布局示意图;图3为on die rdl的一种剖面结构示意图;图4为本实施例提供的传输电路的局部剖面结构示意图。

[0047]

参考图2至图4,本实施例中,传输电路包括:上层时钟焊盘101,用于传输时钟信号;m个上层数据焊盘102,用于传输数据信号;下层时钟焊盘111,与上层时钟焊盘101电连接,且下层时钟焊盘111的面积小于上层时钟焊盘101的面积;m个下层数据焊盘112,与m个上层数据焊盘102一一对应的电连接,且下层数据焊盘112的面积小于上层数据焊盘102的面积;上层时钟焊盘101与上层数据焊盘102位于第一层,下层时钟焊盘111以及下层数据焊盘112位于第二层,在第一层和第二层之间包括介质层103,第一层、介质层103以及第二层均位于同一衬底100上,所述m为大于等于2的整数。

[0048]

以下将结合附图对本实施例提供的传输电路进行详细说明。

[0049]

本实施例中,传输电路可应用于dram中,例如lpddr5。

[0050]

上层时钟焊盘101和m个上层数据焊盘102布置于第一行,且m个上层数据焊盘102布置于上层时钟焊盘101的两侧,每一侧布置m个上层数据焊盘102的一半。上层数据焊盘102为dq数据焊盘,用于传输dq信号,即数据信号包括输入输出数据。当m为偶数时,例如m等于8,则轴线aa1的每一侧布置4个上层数据焊盘102;当m为奇数时,例如m等于7,则轴线aa1的一侧布置3个上层数据焊盘102,另一侧布置4个上层数据焊盘102。上文所述的“一半”,在m为偶数时,应当理解为m/2,而当m为奇数时,应当理解为(m-1)/2或(m+1)/2,下同。

[0051]

图2中8个上层数据焊盘102作为示例,且以dq0、dq1、dq2、dq3、dq4、dq5、dq6、da7对各上层数据焊盘102进行标示。可以理解的是,在其他实施例中,可以根据传输电路的实际需求,合理设置上层数据焊盘的数量。

[0052]

上层时钟焊盘101可用于传输clk信号,即时钟信号为dqs或wck信号,dqs或wck信号指写时钟信号或读时钟信号。相应的,上层时钟焊盘101为差分输入焊盘,包括第一上层时钟焊盘141以及第二上层时钟焊盘151,且第一上层时钟焊盘141与第二上层时钟焊盘151分别传输互补的时钟信号。具体地,图2中以wckt标示第一上层时钟焊盘141,第一上层时钟

焊盘141用于传输wckt时钟信号;以wckc标示第二上层时钟焊盘151,第二上层时钟焊盘151用于传输wckc时钟信号。

[0053]

下层时钟焊盘111的数量与上层时钟焊盘101的数量相同,下层数据焊盘112的数量与上层数据含102的数量相同。具体地,下层时钟焊盘111包括:第一下层时钟焊盘142,与第一上层时钟焊盘141电连接;第二下层时钟焊盘152,与第二上层时钟焊盘151电连接。

[0054]

本实施例中,下层时钟焊盘111和m个下层数据焊盘112布置于第二行,且m个下层数据焊盘112布置于下层时钟焊盘111的两侧,每一侧布置m个下层数据焊盘112的一半。

[0055]

需要说明的是,关于“第一层”并非是指上层时钟焊盘101以及上层数据焊盘102位于传输电路整体结构中的第一层,仅是为了说明上层时钟焊盘101与上层数据焊盘102在传输电路中同层设置。在实际传输电路中,上层时钟焊盘101以及上层数据焊盘102可位于传输电路整体结构中的任意一层。同样的,关于“第二层”并非指下层时钟焊盘111以及下层数据焊盘112位于传输电路整体结构中的第二层,仅是为了说明下层时钟焊盘111以及下层数据焊盘112在传输电路中同层设置,且与上层时钟焊盘101以及上层数据焊盘102位于不同层。在实际传输电路中,下层时钟焊盘111以及下层数据焊盘112可位于传输电路整体结构中的任意一层,且第一层与第二层之间还可以设置其他层功能层。

[0056]

相应的,可以理解的是,关于“第一行”以及“第二行”也满足上述类似的表述含义。

[0057]

每一下层数据焊盘112与下层时钟焊盘111之间的距离为第一距离,对应的上层数据焊盘102与上层时钟焊盘101之间的距离为第二距离;由于下层数据焊盘112的面积小于上层数据焊盘102的面积,下层时钟焊盘111的面积小于上层时钟焊盘101的面积,使得第一距离小于第二距离,即,相较于上层数据焊盘102与上层时钟焊盘101而言,下层数据焊盘112更向下层时钟焊盘111靠拢。

[0058]

相较于图1所示的方案而言,本实施例中的传输电路应用于存储器中时会在下层数据焊盘112对应设置输入缓冲电路,离下层时钟焊盘111最远的输入缓冲电路的时钟路径减小,因而时钟信号能够更快的传输至下层时钟焊盘111最远的输入缓冲电路,从而减小数据信号到达而时钟信号未到达导致的信号延迟时间。相应的,每一输入缓冲电路的时钟路径均有所减小,因此相应能够减小所有输入缓冲电路的信号延迟时间。也就是说,本实施例能够减小tdqs2dq或twck2dq,减少时序违例,并减小时钟路径上所消耗的功率。

[0059]

此外,相较于每一上层时钟焊盘101与输入缓冲电路之间的数据路径与每一上层数据焊盘102与输入缓冲电路之间的时钟路径的差值而言,对应的每一下层时钟焊盘111与输入缓冲电路之间的数据路径与每一下层数据焊盘112与输入缓冲电路之间的时钟路径的差值减小,从而使得本实施例能够缩短不同的输入缓冲电路的tdqs2dq或twck2dq,从而提高不同输入缓冲电路的时钟路径和数据路径的匹配度,从而改善不同输入缓冲电路传输数据信号的时序特性。

[0060]

本实施例中,下层数据焊盘112的面积与下层时钟焊盘111的面积相同。在其他实施例中,下层数据焊盘的面积也可以大于或小于下层时钟焊盘的面积。

[0061]

传输电路还包括:第一金属连线104,第一金属连线104位于下层时钟焊盘111与上层时钟焊盘101之间;第二金属连线105,第二金属连线105位于任一下层数据焊盘112与下层数据焊盘112对应的上层数据焊盘102之间,第一金属连线104的长度小于第二金属连线105的长度。

[0062]

由于第一金属连线104的长度小于第二金属连线105的长度,有利于下层时钟焊盘111中心化布局。

[0063]

本实施例中,通过on die rdl的方式,实现下层时钟焊盘111与上层时钟焊盘101之间的电连接,下层数据焊盘112与上层数据焊盘102之间的电连接。

[0064]

图3为on die rdl的一种剖面结构示意图,如图3所示,包括:依次堆叠设置的第一功能层1101以及第二功能层1102;位于第一功能层1101内的第一焊盘1103以第二焊盘1104;贯穿第二功能层1102且与第一焊盘1103电连接的第一导电插塞1113,贯穿第二功能层1102且与第二焊盘1104电连接的第二导电插塞1114;位于第二功能层1102表面且与第一导电插塞1113电连接的第一再布线层1123,位于第二功能层1102表面且与第二导电插塞1114电连接的第二再布线层1124;位于第二功能层1102表面且与第一再布线层1123电连接的第一再布线焊盘1133,位于第二功能层1102表面且与第二再布线层1124电连接的第二再布线焊盘1134。通过第一导电插塞1113以及第一再布线层1123的位置设置,合理的调整第一再布线焊盘1133与第一焊盘1103的相对位置以及大小关系,同样的调整第二再布线焊盘1134与第二焊盘1104的相对位置以及大小关系,使得第一再布线焊盘1133的尺寸大于第一焊盘1103的尺寸,第二再布线焊盘1134的尺寸大于第二焊盘1104的尺寸,且第一再布线焊盘1133与第二再布线焊盘1134之间的距离大于第一焊盘1103与第二焊盘1104之间的距离。第一再布线层1123比第一焊盘1103所在的金属层要厚很多,例如第一再布线层1123的厚度为4um,第一焊盘1103所在的金属层的厚度为400nm。

[0065]

具体到本实施例中,第一焊盘1103以及第二焊盘1104可以为下层数据焊盘或者下层时钟焊盘,第一再布线焊盘1133以及第二再布线焊盘1134可以为上层数据焊盘或者上层时钟焊盘。图4为本实施例提供的传输电路的局部剖面结构示意图。

[0066]

如图4,在一个例子中,下层时钟焊盘111以及下层数据焊盘112位于基底层100内,且基底层100上堆叠设置有介质层103;第一金属连线104包括:第一导电孔114,第一导电孔114贯穿介质层103且与下层时钟焊盘111以及上层时钟焊盘101相接触。第二金属连线105包括:第二导电孔115,第二导电孔115贯穿介质层103且与下层数据焊盘112相接触;第二金属层125,第二金属层125位于介质层103远离第一层的一侧,且与第二导电孔115以及上层数据焊盘102相接触。

[0067]

第一金属连线104还可以包括:第一金属层,第一金属层位于介质层103远离基底层100的表面,且与第一导电孔114以及上层时钟焊盘101相接触。

[0068]

其中,第一导电孔114的长度与第二导电孔115的长度相同,第一金属层的长度小于第二金属层125的长度。其中,第一导电孔114的剖面形状可以作为直线型,第二导电孔115的剖面形状可以为直线型,且第一导电孔114以及第二导电孔115的长度均与介质层103的厚度相同。

[0069]

在另一个例子中,第一金属连线104可以包括:第一导电插塞,第一导电插塞贯穿介质层103且与下层时钟焊盘111以及上层时钟焊盘101相接触;第二金属连线105包括:第二导电插塞,第二导电插塞贯穿介质层103且与下层数据焊盘112以及上层数据焊盘102相接触,且第一导电插塞的长度小于第二导电插塞的长度。

[0070]

具体地,第一导电插塞的剖面形状可以为直线型结构,第二导电插塞的剖面形状可以为折线形结构,且第一导电插塞的长度可以与介质层的厚度相同,第二导电插塞的长

度可以大于介质层的厚度。

[0071]

本实施例中,参考图2,传输电路还可以包括:多个下层测试焊盘106,多个下层测试焊盘106具有相同的面积,且下层测试焊盘106的面积大于下层数据焊盘112的面积。具体地,下层测试焊盘106与下层数据焊盘112以及下层时钟焊盘111同层设置,可作为进行针测的测试焊盘,在测试过程中探针需与下层测试焊盘106相接触,为降低测试难度,下层测试焊盘106需具有相对较大的面积。例如,下层测试焊盘106的面积为60μm*60μm,下层数据焊盘112的面积为40μm*40μm。

[0072]

本实施例提供的传输电路,通过on die rdl的方式,布局与上层时钟焊盘电连接的下层时钟焊盘,布局与上层数据焊盘电连接的下层数据焊盘,且下层时钟焊盘的面积小于上层时钟焊盘的面积,下层数据焊盘的面积小于上层数据焊盘的面积;设置与下层数据焊盘对应的输入缓冲电路后,有利于缩短时钟信号传输至各输入缓冲电路所需的时钟路径长度,提高时钟路径与数据路径的匹配度,从而减小tdqs2dq或twck2dq和时序违例。各输入缓冲电路对应的时钟路径长度相差较小,能够同时满足各输入缓冲电路的时钟路径与数据路径匹配度高的需求。

[0073]

相应的,本实用新型实施例还提供一种接口电路,包括上述实施例中的传输电路,还包括m个输入缓冲电路。以下将结合附图对本实施例提供的接口电路进行详细说明。

[0074]

图5为本实用新型实施例提供的接口电路的结构示意图。

[0075]

参考图5,本实施例中,接口电路包括:上层时钟焊盘101,用于传输时钟信号;m个上层数据焊盘102,用于传输数据信号;下层时钟焊盘111,与上层时钟焊盘101电连接,且下层时钟焊盘111的面积小于上层时钟焊盘101的面积;m个下层数据焊盘112,与m个上层数据焊盘102一一对应的电连接,且下层数据焊盘112的面积小于上层数据焊盘102的面积;上层时钟焊盘101与上层数据焊盘102位于第一层,下层时钟焊盘111以及下层数据焊盘112位于第二层,在第一层和第二层之间包括介质层103,第一层、介质层103以及第二层均位于同一衬底上,所述m为大于等于2的整数;m个输入缓冲电路201,与下层数据焊盘112一一对应,每一个输入缓冲电路201在时钟信号的驱动下,接收与输入缓冲电路对应的下层数据焊盘传输的数据信号;其中,下层时钟焊盘111与下层数据焊盘112布置于第一排,且m个下层数据焊盘112布置于下层时钟焊盘111的两侧,每一侧布置m个下层数据焊盘112的一半,m个输入缓冲电路201布置于第二排,以下层数据焊盘112为基准,形成垂直于第一排的轴线aa1,m个输入缓冲电路201布置于轴线aa1的两侧,每一侧布置m个输入缓冲电路201的一半,每一个输入缓冲电路201与轴线的距离小于输入缓冲电路201对应的下层数据焊盘112与轴线aa1的距离。

[0076]

以下将结合附图对本实施例提供的接口电路进行详细说明。

[0077]

下层时钟焊盘111为差分输入焊盘,包括第一下层时钟焊盘142和第二下层时钟焊盘152,第一下层时钟焊盘142与第二下层时钟焊盘152分别传输互补的时钟信号。且第一下层时钟焊盘142与第二下层时钟焊盘152相对于轴线aa1对称布置。

[0078]

本实施例中,第一下层时钟焊盘142与第二下层时钟焊盘152相对于轴线aa1对称布置。第一下层时钟焊盘142与位于轴线aa1一侧的输入缓冲电路201的时钟路径为第一时钟路径,第二下层时钟焊盘152与位于轴线aa1另一侧的输入缓冲电路201的时钟路径为第二时钟路径,如此设置,有利于减小第一时钟路径与第二时钟路径的差距,从而减小或者避

免由于第一时钟路径与第二时钟路径差距大对于tdqs2dq或twck2dq造成的不良影响。

[0079]

需要说明的是,在其他实施例中,第一下层时钟焊盘与第二下层时钟焊盘也可以布置于轴线同一侧。

[0080]

此外,关于“第一排”以及“第二排”并非特指位于传输电路整体焊盘中的第一排以及第二排,而是为了说明位于第一排的焊盘与位于第二排的焊盘处于不同排。

[0081]

接口电路还包括:时钟处理电路202,与下层时钟焊盘111和数个输入缓冲电路201均电连接,用于接收时钟信号,并将时钟信号进行处理后作为m个输入缓冲电路201的驱动时钟。时钟处理电路202包括时钟接收电路和相位产生电路,时钟接收电路与下层时钟焊盘111电连接,用于接收所述时钟信号,时钟接收电路的输出作为相位产生电路的输入,相位产生电路用于产生驱动时钟。

[0082]

时钟处理电路202与轴线aa1重合,即时钟处理电路202位于轴线aa1所在位置。如此,有利于减小驱动时钟传输至位于轴线aa1两侧的输入缓冲电路201所需的时钟路径的差异。上述时钟处理电路202位于轴线aa1所在位置,并不意味着时钟处理电路202相对于轴线aa1完全对称,考虑到电路设计和制造的实际情况,时钟处理电路大致位于aa1所在的位置,允许其中心线偏离aa1一定的值,例如偏离10%或20%。

[0083]

每一输入缓冲电路201位于对应的下层数据焊盘112的正下方。对于输入缓冲电路201而言,其在时钟信号的驱动下接受数据信号,并继续传输数据信号。也就是说,当上层数据焊盘102的数据信号传输至输入缓冲电路201时,只有在时钟信号也已经传输至输入缓冲电路201的情况下,输入缓冲电路201才会接受该数据信号并将数据信号传输出去;若数据信号传输至输入缓冲电路201且时钟信号还未达到,则输入缓冲电路201不会传输该数据信号。

[0084]

本实施例中,由于下层数据焊盘112相较于上层数据焊盘102而言集中化布局,使得每一个输入缓冲电路201与轴线aa1的距离小于输入缓冲电路201对应的上层数据焊盘102与轴线aa1的距离,即相较于上层数据焊盘101而言各输入缓冲电路201更向轴线aa1靠拢。具体地,以轴线aa1为基准,m个输入缓冲电路201的布局密集度大于m个上层数据焊盘102的布局密集度;对于每一上层数据焊盘102及其对应的输入缓冲电路201而言,上层数据焊盘102与轴线aa1之间的距离大于输入缓冲电路201与轴线aa1之间的距离。并且,上层数据焊盘102与轴线aa1的距离越近,与该上层数据焊盘102对应的输入缓冲电路201与轴线aa1的距离越近。

[0085]

具体地,每一个输入缓冲电路201到该输入缓冲电路201对应的上层数据焊盘102之间的输入数据路径长度为第一长度,每一个输入缓冲电路201与上层时钟焊盘101之间的时钟路径长度为第二长度,且第一长度与第二长度成正相关。即,对于所有的输入缓冲电路201而言,第一长度越大对应的第二长度越大,第一长度越小对应的第二长度越小。也就是说,离轴线aa1越远的上层数据焊盘102,其对应的输入缓冲电路201离轴线aa1越远;离轴线aa1越近的上层数据焊盘102,其对应的输入缓冲电路201离轴线aa1越近。

[0086]

相较于图1所示的每一输入缓冲电路与轴线的距离等于对应的数据焊盘与轴线的距离的方案而言,本实施例中,对于轴线aa1同一侧的每一上层数据焊盘102以及输入缓冲电路201来说,离上层时钟焊盘101最远的输入缓冲电路201的时钟路径减小,因而时钟信号能够更快的传输至离上层时钟焊盘101最远的输入缓冲电路201,从而减小数据信号达到而

时钟信号未到达导致的信号延迟时间。相应的,每一输入缓冲电路201的时钟路径均有所减小,因此相应能够减小所有输入缓冲电路201的信号延迟时间。也就是说,本实施例能够减小tdqs2dq或twck2dq,减少时序违例,并减小时钟路径上所消耗的功率。

[0087]

此外,每一上层数据焊盘102与输入缓冲电路201之间的数据路径与每一上层时钟焊盘101与输入缓冲电路201之间的时钟路径的差值减小,从而使得本实施例能够缩短不同输入缓冲电路201的tdqs2dq或twck2dq,从而提高不同输入缓冲电路201的时钟路径和数据路径的匹配度,从而改善不同输入缓冲电路201传输数据信号的时序特性。

[0088]

举例来说,图5中标记为dq0的上层数据焊盘102的数据信号经由第一长度传输路径传输至对应的输入缓冲电路201,图5中以2010标记该对应的输入缓冲电路,时钟信号经由第二长度传输路径传输至对应的输入缓冲电路201;对于dq0而言,第一长度指的是从a0点到b0点的长度,第二长度指从c0点到d0点的长度,a0点可以理解为传输线与上层数据焊盘102的连接点,b0点可理解为传输线与下层数据焊盘112的连接点,c0点可理解为传输线与时钟处理电路202的连接点,d0可理解为传输线与下层数据焊盘112的连接点,d0与b0可为同一连接点。当数据信号传输至输入缓冲电路201时,时钟信号经由t1时间后传输至输入缓冲电路201中,从而保证输入缓冲电路201能够在接收到数据信号后等待t1时间内将数据信号传输出去;由于数据焊盘201传输数据信号dq0的速率越来越高,dq0维持高电平“1”或低电平“0”的时间越来越短,从而要求等待时间t1要越来越小,进而要求第一长度(对应数据路径)与第二长度(对应时钟路径)要尽可能的匹配。

[0089]

图5中标记为dq3的上层数据焊盘102的数据信号经由第一长度传输路径传输至对应的输入缓冲电路201,图5中以2013标记该对应的输入缓冲电路,时钟信号经由第二长度传输路径传输至对应的输入缓冲电路201;对于dq3而言,第一长度指从a3点到b3点的长度,第二长度指c0点到d3点的长度,b3与d3可为同一点。当数据信号传输至输入缓冲电路201时,时钟信号经由t2时间后传输至输入缓冲电路201中,从而保证输入缓冲电路201能够在收到数据信号后等待t2时间内将数据信号传输出去。对于标记为dq0和标记为dq3的数据焊盘101而言,由于dq0对应的输入缓冲电路201的第一长度与第二长度是匹配的,dq3对应的输入缓冲电路201的第一长度与第二长度也是匹配的,因此t1与t2相等或近似相等。因此,本实施例中能够提高不同的输入缓冲电路201传输数据信号的时间一致性,即更好的时序特性。

[0090]

此外,每一个输入缓冲电路201到该输入缓冲电路201对应的下层数据焊盘112之间的输入数据路径为第三长度,每一个输入缓冲电路201到该输入缓冲电路201对应的下层时钟焊盘111之间的时钟路径长度为第四长度,第三长度与第四长度正相关。

[0091]

此外,接口电路还可以包括:上层标志焊盘203,用于传输标志信号,上层标志焊盘203位于第一层;下层标志焊盘213,与上层标志焊盘203电连接,且位于第二层,且下层标志焊盘213的面积小于上层标志焊盘203的面积;标志缓冲电路223,与标志焊盘203对应,用于在时钟信号的驱动下,接收上层标志焊盘203传输的标志信号。

[0092]

标志信号通常称为data mask inverter,用于标示每一个数据信号是否取反,上层标志焊盘203通常称为dmi(data mask inverter)焊盘、dm焊盘或者dbi焊盘,图5中以dmi对上层标志焊盘203进行标示。

[0093]

本实施例中,下层标志焊盘213布置于第一排,且位于下层数据焊盘112与下层时

钟焊盘111之间;标志缓冲电路223布置于第二排,且与下层标志焊盘213位于轴线aa1的同一侧,且位于输入缓冲电路201与轴线aa1之间;标志缓冲电路223与轴线aa1的距离小于标志缓冲电路223对应的下层标志焊盘213与轴线aa1的距离。

[0094]

接口电路还可以包括:m个输出缓冲电路,与下层数据焊盘112一一对应,每一个输出缓冲电路在时钟信号的驱动下,将数据信号发送对应的下层数据焊盘112。输出缓冲电路除与下层数据焊盘112电连接外,还与下层时钟焊盘111电连接。

[0095]

具体地,输出缓冲电路经由时接收电路和相位产生电路与下层时钟焊盘111电连接。

[0096]

本实施例中,每一个输出缓冲电路到输出缓冲电路对应的下层数据焊盘112之间的输出数据路径长度相同。具体地,每一输出缓冲电路位于对应的下层数据焊盘111的正下方,或者说,每一输出缓冲电路与轴线aa1之间的距离与对应的下层数据焊盘与轴线aa1之间的距离相等。同样的,考虑到电路设计和制造的实际情况,上述长度相同或距离相等也可以是近似相同或近似相等,允许存在一定误差,后面类似描述不再赘述。

[0097]

本实施例中,输出缓冲电路可与输入缓冲电路201集成在一个功能模块中。

[0098]

接口电路还可以包括:多个电源焊盘和接地焊盘,用于接地或者接固定电源。其中多个电源焊盘以及接地焊盘与上层数据焊盘102位于同一排。

[0099]

接口电路还可以包括:位于第一层的第一上层功能焊盘301以及第二上层功能焊盘302,第一上层功能焊盘301以及第二上层功能焊盘302位于上层数据焊盘102与上层时钟焊盘101之间,第一上层功能焊盘301传输rqst信号,第二上层功能焊盘302传输rqsc信号;位于第二层的第一下层功能焊盘311以及第二下层功能焊盘312,第一下层功能焊盘311与第一上层功能焊盘301电连接,第二下层功能焊盘312与第二上层功能焊盘302电连接,且第一下层功能焊盘311的面积小于第一上层功能焊盘301的面积,第二下层功能焊盘312的面积小于第二上层功能焊盘302的面积。图5中以rqst标示第一上层功能焊盘301,以rqsc标示第二上层功能焊盘302。

[0100]

接口电路还可以包括:第一功能缓冲电路321,用于在时钟信号的驱动下,接收第一下层功能焊盘311传输的标志信号;第二功能缓冲电路322,用于在时钟信号的驱动下,接收第二下层功能焊盘312传输的rqsc信号。

[0101]

输入缓冲电路包括多路选择器(mux)和锁存器(latch),多路选择器接收数据信号,并将数据信号处理后输出给锁存器,锁存器的输出作为输入缓冲电路的输出。

[0102]

接口电路还可以包括:m个串并转换电路(s2p),m个串并转换电路与m个输入缓冲电路201一一对应,每一个输入缓冲电路201的输出作为对应的串并转换电路的输入。m个串并转换电路与m个下层数据焊盘112一一对应,且每一个串并转换电路到该串并转换电路对应的下层数据焊盘112的距离相同。可以认为,每一串并转换电路布局在对应下层数据焊盘112的正下方。

[0103]

接口电路还可以包括:m个先入先出电路(output fifo),与m个串并转换电路(s2p,sequential to parallel)一一对应;m个并串转换电路(p2s,parallel to sequential),与m个先入先出电路(output fifo,output first input first output)一一对应,每一个先入先出电路的输出作为先入先出电路对应的并串转换电路的输入;m个驱动电路,与m个并串转换电路一一对应,每一个并串转换电路的输出作为并串转换电路对应

的驱动电路的输入;且m个驱动电路还与m个下层数据焊盘112一一对应。

[0104]

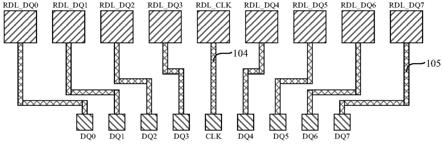

图6为本实施例提供的接口电路的一种布局示意图,图7为本实施例提供的接口电路的另一种布局示意图。在图6以及图7中,以dq0、dq1、dq2、dq3、dq4、dq5、dq6、dq7标示出下层数据焊盘,以rdl_dq0、rdl_dq1、rdl_dq2、rdl_dq3、rdl_dq4、rdl_dq5、rdl_dq6、rdl_dq7标示出对应的上层数据焊盘,以dqs标示出下层时钟焊盘,以rdl_dqs标示出对应的上层时钟焊盘。

[0105]

如图6所示,在一个例子中,上层数据焊盘以及上层时钟焊盘均设置于同一排,下层数据焊盘以及下层时钟焊盘均设置于同一排。如图7所示,在另一个例子中,上层数据焊盘以及上层时钟焊盘中的部分设置于同一行,剩余部分设置于同一列,且下层数据焊盘以及下层时钟焊盘被布局在两排,可以理解的是,下层数据焊盘以及下层时钟焊盘也可以布局在同一排,或者,上层时钟焊盘以及上层数据焊盘被布局成围绕下层时钟焊盘以及下层数据焊盘设置的三条边或者四条边上,可以理解的是,图7所示的情况为,上层时钟焊盘以及上层数据焊盘被布局成围绕下层时钟焊盘以及下层数据焊盘设置的两条边上。本实施例提供的接口电路中,采用on die rdl的方式,布局与上层时钟焊盘电连接的下层时钟焊盘,布局与上层数据焊盘电连接的下层数据焊盘,且下层时钟焊盘的面积小于上层时钟焊盘的面积,下层数据焊盘的面积小于上层数据焊盘的面积,从而实现了各输入缓冲电路的集中化布局,缩短了时钟信号传输至各输入缓冲电路所需的时钟路径长度,提高了时钟路径与数据路径的匹配度,从而减小了tdqs2dq或twck2dq和时序违例。各输入缓冲电路对应的时钟路径长度相差较小,能够同时满足各输入缓冲电路的时钟路径与数据路径匹配度高的需求。

[0106]

此外,由于时钟路径长度缩短,相应缩短了传输时钟信号的导线的长度,因此可以在一定程度上降低数据传输电路的功耗。

[0107]

相应的,本实用新型实施例还提供一种存储器,包括上述的接口电路。

[0108]

存储器可以为dram、sram、mram、feram、pcram、nand、nor等存储器。例如,存储器可以为lpddr4存储器或者lpddr5存储器。

[0109]

本领域的普通技术人员可以理解,上述各实施方式是实现本实用新型的具体实施例,而在实际应用中,可以在形式上和细节上对其作各种改变,而不偏离本实用新型的精神和范围。任何本领域技术人员,在不脱离本实用新型的精神和范围内,均可作各自更动与修改,因此本实用新型的保护范围应当以权利要求限定的范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1