模拟内容可寻址存储器及其操作方法与流程

1.本公开是有关于一种存储器及其操作方法,且特别是有关于一种模拟内容可寻址存储器及其操作方法。

背景技术:

2.随着存储器技术的发展,发明了一种内容可寻址存储器(analog content-address memory,cam)。内容可寻址存储器是应用于超高速搜索的一种特殊存储器。内容可寻址存储器可以以高度并行的方式将输入搜索词与阵列中所有列的储存词进行比较。内容可寻址存储器在许多应用(尤其是图像搜索等应用)提供了非常强大的功能。

3.过去对于这方面的技术采用了各种记忆电阻(例如 reram、pcm、cbram、feram),来代替传统的静态随机存取存储器(sram)。但这些方式仍然只能进行二元或三元的搜索。

4.公开内容

5.本公开有关于一种模拟内容可寻址存储器及其操作方法,其利用浮动栅极存储器来储存模拟内容,以使与输入信号匹配的模拟内容能够被搜索出来。

6.根据本公开的一方面,提出一种模拟内容可寻址存储器(analog content-address memory,analog cam)。模拟内容可寻址存储器包括至少一匹配线、至少一模拟cam存储单元及至少一感测电路。各个模拟cam存储单元包括一第一浮动栅极装置及一第二浮动栅极装置。第一浮动栅极装置具有一n型沟道。第一浮动栅极装置连接于匹配线。第二浮动栅极装置具有一p型沟道。第一浮动栅极装置及第二浮动栅极装置以串联的方式连接。第一浮动栅极装置及第二浮动栅极装置被编程,以设定一匹配范围。模拟cam存储单元的第一浮动栅极装置及第二浮动栅极装置用以接收一输入信号。感测电路连接于匹配线。当输入信号落于匹配范围内,则匹配线的电压被下拉至一预定电平或低于预定电平,感测电路输出一匹配成功结果。

7.根据本公开的另一方面,提出一种模拟内容可寻址存储器(content-address memory,analog cam)。模拟内容可寻址存储器包括至少一匹配线、至少一模拟cam存储单元及至少一感测电路。各个模拟cam存储单元包括一第一浮动栅极装置及一第二浮动栅极装置。第一浮动栅极装置具有一n型沟道。第一浮动栅极装置连接于匹配线。第二浮动栅极装置具有一p型沟道。第一浮动栅极装置及第二浮动栅极装置以并联的方式连接。第一浮动栅极装置及第二浮动栅极装置被编程,以设定一匹配范围。模拟cam存储单元的第一浮动栅极装置及第二浮动栅极装置用以接收一输入信号。感测电路连接于匹配线。当该输入信号落于该匹配范围内,则匹配线的电压维持于一原始电平,感测电路输出一匹配成功结果。

8.根据本公开的再一方面,提出一种模拟内容可寻址存储器(content-address memory,analog cam)的操作方法。操作方法包括以下步骤。对一第一浮动栅极装置进行编程。第一浮动栅极装置具有一n型沟道。对一第二浮动栅极装置进行编程。第二浮动栅极装置具有一p型沟道。第一浮动栅极装置及第二浮动栅极装置以串联或并联的方式连接。第一浮动栅极装置及第二浮动栅极装置被编程后,设定出一匹配范围。

9.为了对本公开的上述及其他方面有更佳的了解,下文特举实施例,并配合附图详细说明如下。

附图说明

10.图1为根据一实施例的数字内容可寻址存储器(digital content-addressable memory,digital cam)的运作。

11.图2为根据一实施例的模拟内容可寻址存储器(analog content-addressable memory,analog cam)的运作。

12.图3为根据一实施例的模拟cam存储单元。

13.图4为根据一实施例的模拟cam存储单元的匹配范围。

14.图5~7为根据一实施例的模拟cam存储单元的匹配范围的多个例子。

15.图8为模拟内容可寻址存储器的操作方法中设定匹配范围的流程图。

16.图9为模拟内容可寻址存储器的操作方法中判断输入信号是否匹配的流程图。

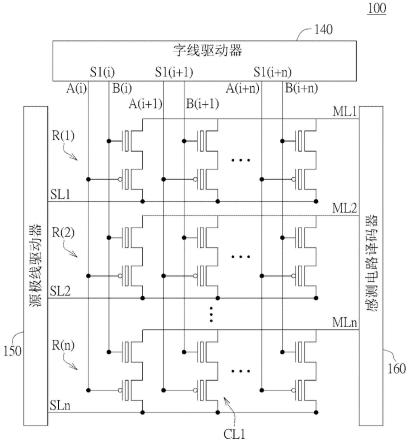

17.图10为根据一实施例的模拟内容可寻址存储器的电路图。

18.图11为匹配线的多个电压曲线。

19.图12为根据一实施例的模拟内容可寻址存储器的阵列结构。

20.图13为根据一实施例的模拟cam存储单元。

21.图14为根据一实施例的模拟cam存储单元的匹配范围。

22.图15~16为根据一实施例的模拟cam存储单元的匹配范围的多个例子。

23.图17为根据一实施例的模拟内容可寻址存储器的电路图。

24.图18为匹配线的多个电压曲线。

25.图19为根据一实施例的模拟内容可寻址存储器的阵列结构。

26.图20为根据另一实施例的模拟cam存储单元。

27.图21为根据另一实施例的模拟cam存储单元。

28.图22为根据另一实施例的模拟cam存储单元。

29.图23为根据另一实施例的模拟cam存储单元。

30.附图标记说明

31.100,200:模拟内容可寻址存储器

32.140:字线驱动器

33.150:源极线驱动器

34.160:感测电路译码器

35.900:数字内容可寻址存储器

36.a(i),a(i+1),a(i+n),b(i),b(i+1),b(i+n):输入线

37.c1,c2,c3,c4,c5,c6:电压曲线

38.cl1,cl2,cl3,cl4,cl5,cl6:模拟cam存储单元

39.cl9:数字cam存储单元

40.cn,cp:曲线

41.gctn,msn,trn:第一浮动栅极装置

42.gctp,msp,trp:第二浮动栅极装置

43.ip:通过电流

44.lb:下限

45.ml,ml1,ml2,mln:匹配线

46.mr:匹配范围

47.pc:预充电控制装置

48.r(1),r(2),r(3),r(4),r(n):列

49.rn:匹配不成功结果

50.ry:匹配成功结果

51.s1,s1(i),s1(i+1),s1(i+n),s9:输入信号

52.s110,s120,s210,s220:步骤

53.sa:感测电路

54.saout:比对结果

55.sl,sl’,sl1,sl2,sln:源极线

56.ub:上限

57.vm:端点

58.vref:参考电压

59.vstart:启动电压

具体实施方式

60.请参照图1,其为根据一实施例的数字内容可寻址存储器(digital content-addressable memory,digital cam)900的运作。数字内容可寻址存储器900包括多个数字cam存储单元cl9。这些数字cam存储单元cl9排列于多列r(1)、r(2)、r(3)、r(4),以储存多笔数字内容。举例来说,储存于列r(1)的内容是“x、1、0”。“x”代表任何数值都能匹配。储存于列r(2)的内容是“1、x、1”。储存于列r(3)的内容是“0、0、x”。储存于列r(4)的内容是“0、0、1”。多个输入信号s9输入至数字内容可寻址存储器100中。第一个输入信号s9的内容是“1”,第二个输入信号s9的内容是“1”,第三个输入信号s9的内容是“0”。这些输入信号s9与储存于列r(1)的内容进行比对后,输出匹配成功结果ry。这些输入信号s9与储存于列r(2)的内容进行比对后,输出匹配不成功结果rn。这些输入信号s9与储存于列r(3)的内容进行比对后,输出匹配不成功结果rn。这些输入信号s9与列r(4)的内容进行比对后,输出匹配不成功结果rn。也就是说,数字内容可寻址存储器900可以储存数字内容,任何与输入信号s9匹配的数字内容可以被搜索出来。

61.请参照图2,其为根据一实施例的模拟内容可寻址存储器(analog content-addressable memory,analog cam)100的运作。模拟内容可寻址存储器100包括多个模拟cam存储单元cl1。模拟cam存储单元cl1排列于多列r(1)、r(2)、r(3)、r(4),以储存多笔模拟内容。举例来说,储存于列r(1)的内容是“0.00~1.00、0.48~0.76、0.00~0.15”。“0.00~1.00”代表任何数值都能匹配。储存于列r(2)的内容是“0.62~1.00、0.25~0.63、0.25~1.00”。储存于列r(3)的内容是“0.26~0.61、0.12~0.40、0.00~1.00”。储存于列r(4)的内容是“0.00~0.43、0.00~0.28、0.58~1.00”。多个输入信号s1输入至模拟内容可寻址存储器100。第一个输入信号s1的内容是“0.81”,第二个输入信号s1的内容是“0.62”,第三个输

入信号s1的内容是“0.12”。

62.这些输入信号s1与储存于列r(1)的内容进行比对。储存于列r(1)的“0.00~1.00、0.48~0.76、0.00~0.15”为匹配范围。由于“0.81”、“0.62”及“0.12”分别落入“0.00~1.00”、“0.48~0.76”及“0.00~0.15”,故据以输出匹配成功结果ry。

63.这些输入信号s1与储存于列r(2)的内容进行比对后,输出匹配不成功结果rn。这些输入信号s1与储存于列r(3)的内容进行比对后,输出匹配不成功结果rn。这些输入信号s1与储存于列r(4)的内容进行比对后,输出匹配不成功结果rn。也就是说,模拟内容可寻址存储器100可以储存模拟内容,任何与输入信号s1匹配的模拟内容可以被搜索出来。

64.请参照图3,其为根据一实施例的模拟cam存储单元cl1。模拟cam存储单元cl1包括一第一浮动栅极装置msn及第二浮动栅极装置msp。第一浮动栅极装置msn具有一n型沟道,第二浮动栅极装置msp具有一p型沟道。第二浮动栅极装置msp以串联的方式连接于第一浮动栅极装置msn。第一浮动栅极装置msn为一n型金属氧化物半导体(nmos),第二浮动栅极装置msp为一p型金属氧化物半导体(pmos)。第一浮动栅极装置msn的漏极连接于一匹配线ml,第一浮动栅极装置msn的源极连接于第二浮动栅极装置msp的漏极。第二浮动栅极装置msp的源极连接于一源极线sl。输入信号s1同时输入至第一浮动栅极装置msn与第二浮动栅极装置msp的栅极。

65.请参照图4,其为根据一实施例的模拟cam存储单元cl1的匹配范围mr。曲线cn为第一浮动栅极装置msn的特性曲线,曲线cp为第二浮动栅极装置msp的特性曲线。曲线cn与曲线cp的陡峭斜率大于0.01mv/dec。举例来说,图4的曲线cn及曲线cp的陡峭曲线为0.015mv/dec。第一浮动栅极装置msn与第二浮动栅极装置msp为超陡峭元件(super steep slope devices)。

66.在模拟cam存储单元cl1中,第一浮动栅极装置msn的阈值电压低于第二浮动栅极装置msp的阈值电压,以于第一浮动栅极装置msn的阈值电压与第二浮动栅极装置msp的阈值电压之间形成匹配范围mr。在模拟cam存储单元cl1中,匹配范围mr的下限lb为第一浮动栅极装置msn的阈值电压,匹配范围mr的上限ub为第二浮动栅极装置msp的阈值电压。

67.如图3及图4所示,当输入信号s1落于匹配范围mr之内时,第一浮动栅极装置msn被导通且第二浮动栅极装置msp也被导通,故形成了通过电流ip。

68.当输入信号s1不位于匹配范围mr之内时,第一浮动栅极装置msn会关闭或者第二浮动栅极装置msp会关闭,故不会形成通过电流ip。

69.请参照图5~7,其为根据一实施例的模拟cam存储单元cl1的匹配范围mr的多个例子。图5的匹配范围mr为“0.00~1.00”,图6的匹配范围mr为“0.42~0.75”,图7的匹配范围mr为“0.69~0.75”。也就是说,模拟cam存储单元cl1的匹配范围mr是可以调整的。匹配范围mr的下限lb(如图4所示)通过第一浮动栅极装置msn进行设定,匹配范围mr的上限ub(如图4所示)通过第二浮动栅极装置msp进行设定。

70.请参照图8,其为模拟内容可寻址存储器100的操作方法中设定匹配范围mr的流程图。匹配范围mr通过第一浮动栅极装置msn及第二浮动栅极装置msp进行设定。在步骤s110中,对第一浮动栅极装置msn进行编程。在此步骤中,第一浮动栅极装置msn通过f-n隧穿技术(fowler-nordheim tunneling,fn tunneling)或沟道热电子注入技术(channel hot electron programming,che programming)进行编程。举例来说,第一浮动栅极装置msn的

栅极被施加一fn电压,第二浮动栅极装置msp的栅极被施加一通过电压。在第一浮动栅极装置msn进行编程之后,匹配范围mr的下限lb(如图4所示)即可被定义出来。

71.在步骤s120中,对第二浮动栅极装置msp进行编程。在此步骤中,第二浮动栅极装置msp通过f-n隧穿技术或沟道热电子注入技术进行编程。举例来说,第一浮动栅极装置msn的栅极被施加通过电压,第二浮动栅极装置msp的栅极被施加fn电压。在第二浮动栅极装置msp进行编程之后,匹配范围mr的上限ub(如图4所示)即可被定义出来。

72.请参照图9,其为模拟内容可寻址存储器100的操作方法中判断输入信号s1是否匹配的流程图。在步骤s210中,输入信号s1输入至第一浮动栅极装置msn及第二浮动栅极装置msp。在此步骤中,输入信号s1同时输入至第一浮动栅极装置msn的栅极与第二浮动栅极装置msp的栅极。

73.在步骤s220中,根据匹配线ml的电压,输出匹配成功结果ry或匹配不成功结果rn。举例来说,输入信号s1落入匹配范围mr时,第一浮动栅极装置msn与第二浮动栅极装置msp皆被导通,且匹配线ml的电压将被下拉。输入信号s1未落入匹配范围mr时,第一浮动栅极装置msn与第二浮动栅极装置msp不会都被导通,且匹配线ml的电压会被维持。

74.请参照图10,其为根据一实施例的模拟内容可寻址存储器100的电路图。模拟内容可寻址存储器100可以包括匹配线ml、多个模拟cam存储单元cl1、一预充电控制装置(pre-charge control device)pc及一感测电路(sense amplifier)sa。各个模拟cam存储单元cl1的第一浮动栅极装置msn连接于匹配线ml。预充电控制装置pc连接于匹配线ml。预充电控制装置pc经由启动电压vstart启动后,将匹配线ml导通至端点vm。感测电路sa连接于匹配线ml与一参考电压vref,感测电路sa可将匹配线ml的电压与餐电压vref进行比对,以输出一比对结果saout。

75.在图10中,第i个输入信号s1(i)输入至输入线a(i)、b(i),第i+1个输入信号s1(i+1)输入至输入线a(i+1)、b(i+1),第i+n个输入信号s1(i+n)输入至输入线a(i+n)、b(i+n)。当第i个输入信号s1(i)落入第i个模拟cam存储单元cl1的匹配范围mr时,第i个模拟cam存储单元cl1的第一浮动栅极装置msn会被导通,第i个模拟cam存储单元cl1的第二浮动栅极装置msp会被导通。

76.同样地,在图10中,当第i+1个输入信号s1(i+1)落入第i+1个模拟cam存储单元cl1的匹配范围mr时,第i+1个模拟cam存储单元cl1的第一浮动栅极装置msn会被导通,第i+1个模拟cam存储单元cl1的第二浮动栅极装置msp会被导通。当第i+n个输入信号s1(i+n)落入第i+n个模拟cam存储单元cl1的匹配范围mr时,第i+n个模拟cam存储单元cl1的第一浮动栅极装置msn会被导通,第i+n个模拟cam存储单元cl1的第二浮动栅极装置msp会被导通。

77.当这些输入信号s1(i)、s1(i+1)、s(i+n)、

…

都落入这些模拟cam存储单元cl1的匹配范围mr时,这些模拟cam存储单元cl1的第一浮动栅极装置msn都会被导通,这些模拟cam存储单元cl1的第二浮动栅极装置msp也都会被导通。如此一来,匹配线ml的电压将会被下拉。

78.请参照图11,其为匹配线ml的多个电压曲线c1、c2、c3。当所有的输入信号s1(i)、s1(i+1)、s(i+n)、

…

均匹配于模拟cam存储单元cl1所储存的内容,匹配线ml的电压将会大幅地下拉至一预定电平(如电压曲线c1所示)或低于预定电平。接着,感测电路sa根据匹配线ml的电压输出匹配成功结果ry。

79.当所有的输入信号s1(i)、s1(i+1)、s(i+n)、

…

皆不匹配于模拟cam存储单元cl1所储存的内容,匹配线ml的电压将会维持于原来电平(如电压曲线c2所示)。接着,感测电路sa根据匹配线ml输出匹配不成功结果rn。

80.在一实施例中,当只有部分的输入信号s1(i)、s1(i+1)、s(i+n)、

…

匹配于模拟cam存储单元cl1所储存的内容时,匹配线ml的电压将会轻微地下拉(如电压曲线c3所示)。电压曲线c3并未低于上述的预定电平,故感测电路sa根据匹配线ml的电压输出匹配不成功结果rn。

81.请参照图12,其为根据一实施例的模拟内容可寻址存储器100的阵列结构。在阵列结构中,模拟内容可寻址存储器100还包括具有搜索暂存器的一字线驱动器(word line driver)140、一源极线驱动器(source line driver)150及一感测电路译码器(sense amplifier encoder)160。输入线a(i)、b(i)、a(i+1)、b(i+1)、

…

、a(i+n)、b(i+n)连接于字线驱动器140。源极线sl1、sl2、

…

、sln连接于源极线驱动器150。感测电路sa设置于感测电路译码器160。匹配线ml1、ml2、

…

、mln连接于感测电路译码器160。

82.模拟cam存储单元cl1按照多列r(1)、r(2)、

…

、r(n)排列,并各列r(1)、r(2)、

…

、r(n)储存不同的内容。多个输入信号s1(i)、s1(i+1)、s(i+n)、

…

分别输入至这些模拟cam存储单元cl1。根据输入信号s1(i)、s1(i+1)、s(i+n)、

…

是否匹配于列r(1)所储存的内容,匹配线ml1的电压将会被下拉或维持。同样地,根据输入信号s1(i)、s1(i+1)、s(i+n)、

…

是否匹配于列r(2)所储存的内容,匹配线ml2的电压将会被下拉或维持。根据输入信号s1(i)、s1(i+1)、s(i+n)、

…

是否匹配于列r(n)所储存的内容,匹配线mln的电压将会被下拉或维持。接着,感测电路译码器160可以分析出哪一列所存的内容最匹配于输入信号s1(i)、s1(i+1)、s(i+n)、

…

。

83.根据上述内容,模拟内容可寻址存储器100可以储存模拟内容,任何与输入信号s1(i)、s1(i+1)、s(i+n)、

…

匹配的模拟内容可以被搜索出来。

84.根据上述实施例,第一浮动栅极装置msn与第二浮动栅极装置msp以串联的方式为例做说明。在另一实施例中,第一浮动栅极装置msn与第二浮动栅极装置msp可以并联的方式连接。请参照图13,其为根据一实施例的模拟cam存储单元cl2。模拟cam存储单元cl2包括具有n型沟道的第一浮动栅极装置msn及具有p型沟道的第二浮动栅极装置msp。在模拟cam存储单元cl2中,第二浮动栅极装置msp以并联的方式连接于第一浮动栅极装置msn。在模拟cam存储单元cl2中,第一浮动栅极装置msn的漏极与第二浮动栅极装置msp的漏极连接于匹配线ml,第一浮动栅极装置msn的源极与第二浮动栅极装置msp的源极连接于源极线sl、sl’。输入信号s1同时输入至第一浮动栅极装置msn的栅极与第二浮动栅极装置msp的栅极。

85.请参照图14,其为根据一实施例的模拟cam存储单元cl2的匹配范围mr。在模拟cam存储单元cl2中,第一浮动栅极装置msn的阈值电压高于第二浮动栅极装置msp的阈值电压,以于第一浮动栅极装置msn的阈值电压与第二浮动栅极装置msp的阈值电压之间形成匹配范围mr。在模拟cam存储单元cl2中,匹配范围mr的下限lb为第二浮动栅极装置msp的阈值电压,匹配范围mr的上限ub为第一浮动栅极装置msn的阈值电压。

86.如图13及图14所示,输入信号s1落于匹配范围mr之内时,第一浮动栅极装置msn会关闭且第二浮动栅极装置msp也会关闭,故通过电流ip不会形成。

87.如图13及图14所示,当输入信号s1不位于匹配范围mr之内时,第一浮动栅极装置

msn会被导通或者第二浮动栅极装置msp会被导通,故形成了通过电流ip。

88.请参照图15~16,其为根据一实施例的模拟cam存储单元cl2的匹配范围mr的多个例子。图14的匹配范围mr为“0.42~0.52”,图15的匹配范围mr为“0.42~0.65”,图16的匹配范围mr为“0.42~0.85”。也就是说,模拟cam存储单元cl2的匹配范围mr是可以调整的。匹配范围mr的下限lb(如图14所示)通过第二浮动栅极装置msp进行设定,匹配范围mr的上限ub(如图14所示)通过第一浮动栅极装置msn进行设定。

89.请参照图17,其为根据一实施例的模拟内容可寻址存储器200的电路图。模拟内容可寻址存储器200可以包括匹配线ml、多个模拟cam存储单元cl2、预充电控制装置pc及感测电路sa。各个模拟cam存储单元cl2的第一浮动栅极装置msn与第二浮动栅极装置msp连接于匹配线ml。预充电控制装置pc连接于匹配线ml。感测电路sa连接于匹配线ml。

90.在图17中,第i个输入信号s1(i)输入至输入线a(i)、b(i),第i+1个输入信号s1(i+1)输入至输入线a(i+1)、b(i+1),第i+n个输入信号s1(i+n)输入至输入线a(i+n)、b(i+n)。当第i(i)个输入信号s1落入第i个模拟cam存储单元cl2的匹配范围mr时,第i个模拟cam存储单元cl2的第一浮动栅极装置msn会关闭,第i个模拟cam存储单元cl2的第二浮动栅极装置msp会关闭。

91.同样地,在图17中,当第i+1个输入信号s1(i+1)落入第i+1个模拟cam存储单元cl2的匹配范围mr时,第i+1个模拟cam存储单元cl2的第一浮动栅极装置msn会关闭,第i+1个模拟cam存储单元cl2的第二浮动栅极装置msp会关闭。当第i+n个输入信号s1(i+n)落入第i+n个模拟cam存储单元cl2的匹配范围mr时,第i+n个模拟cam存储单元cl2的第一浮动栅极装置msn会关闭,第i+n个模拟cam存储单元cl2的第二浮动栅极装置msp会关闭。

92.当这些输入信号s1(i)、s1(i+1)、s(i+n)、

…

都落入这些模拟cam存储单元cl2的匹配范围mr时,这些模拟cam存储单元cl2的第一浮动栅极装置msn都会关闭,这些模拟cam存储单元cl2的第二浮动栅极装置msp也都会关闭。如此一来,匹配线ml的电压将会维持不变。

93.请参照图18,其为匹配线ml的多个电压曲线c4、c5、c6。当所有的输入信号s1(i)、s1(i+1)、s(i+n)、

…

均匹配于模拟cam存储单元cl2所储存的内容,匹配线ml的电压将会维持于原来电平(如电压曲线c4所示)。接着,感测电路sa根据匹配线ml的电压输出匹配成功结果ry。

94.当所有的输入信号s1(i)、s1(i+1)、s(i+n)、

…

皆不匹配于模拟cam存储单元cl2所储存的内容,匹配线ml的电压将会被下拉至预定电平(如电压曲线c5所示)。接着,感测电路sa根据匹配线ml输出匹配不成功结果rn。

95.在一实施例中,当只有部分的输入信号s1(i)、s1(i+1)、s(i+n)、

…

匹配于模拟cam存储单元cl2所储存的内容时,匹配线ml的电压将会轻微地下拉(如电压曲线c6所示)。电压曲线c6并低于上述的原始电平,故感测电路sa根据匹配线ml的电压输出匹配不成功结果rn。

96.请参照图19,其为根据一实施例的模拟内容可寻址存储器200的阵列结构。在阵列结构中,模拟内容可寻址存储器200还包括具有搜索暂存器的字线驱动器140、源极线驱动器150及感测电路译码器160。输入线a(i)、b(i)、a(i+1)、b(i+1)、

…

、a(i+n)、b(i+n)连接于字线驱动器140。源极线sl1、sl2、

…

、sln连接于源极线驱动器150。感测电路sa设置于感测电路译码器160。匹配线ml1、ml2、

…

、mln连接于感测电路译码器160。

97.模拟cam存储单元cl2按照多列r(1)、r(2)、

…

、r(n)排列,并各列r(1)、r(2)、

…

、r(n)储存不同的内容。多个输入信号s1(i)、s1(i+1)、s(i+n)、

…

分别输入至这些模拟cam存储单元cl2。根据输入信号s1(i)、s1(i+1)、s(i+n)、

…

是否匹配于列r(1)所储存的内容,匹配线ml1的电压将会被下拉或维持。同样地,根据输入信号s1(i)、s1(i+1)、s(i+n)、

…

是否匹配于列r(2)所储存的内容,匹配线ml2的电压将会被下拉或维持。根据输入信号s1(i)、s1(i+1)、s(i+n)、

…

是否匹配于列r(n)所储存的内容,匹配线mln的电压将会被下拉或维持。接着,感测电路译码器160可以分析出哪一列所存的内容最匹配于输入信号s1(i)、s1(i+1)、s(i+n)、

…

。

98.根据上述内容,模拟内容可寻址存储器200可以储存模拟内容,任何与输入信号s1(i)、s1(i+1)、s(i+n)、

…

匹配的模拟内容可以被搜索出来。

99.根据上述实施例,第一浮动栅极装置msn与第二浮动栅极装置msp分别以n型金属氧化物半导体(nmos)和p型金属氧化物半导体(pmos)为例做说明。在另一实施例中,第一浮动栅极装置可以是具有n型沟道的任何浮动栅极装置,第二浮动栅极装置可以是具有p型沟道的任何浮动栅极装置。这些实施例叙述如下。

100.请参照图20,其为根据另一实施例的模拟cam存储单元cl3。模拟cam存储单元cl3包括具有ln型沟道的一第一浮动栅极装置trn与具有p型沟道的第二浮动栅极装置trp。第二浮动栅极装置trp以串联的方式连接于第一浮动栅极装置trn。第一浮动栅极装置trn为n型沟道晶闸管(n channel thyristor ram),第二浮动栅极装置trp为p型沟道晶闸管(p channel thyristor ram)。第一浮动栅极装置trn的正极连接于匹配线ml,第一浮动栅极装置trn的负极连接于第二浮动栅极装置trp的正极。第二浮动栅极装置trp的负极连接于源极线sl。输入信号s1同时输入至第一浮动栅极装置trn与第二浮动栅极装置trp的栅极。

101.请参照图21,其为根据另一实施例的模拟cam存储单元cl4。模拟cam存储单元cl4包括具有n型沟道的第一浮动栅极装置trn及具有p型沟道的第二浮动栅极装置trp。在模拟cam存储单元cl4中,第二浮动栅极装置trp以并联的方式连接于第一浮动栅极装置trn。在模拟cam存储单元cl4中,第一浮动栅极装置trn的正极与第二浮动栅极装置trp的正极连接于匹配线ml,第一浮动栅极装置trn的负极与第二浮动栅极装置trp的负极连接于源极线sl、sl’。输入信号s1同时输入至第一浮动栅极装置trn的栅极与第二浮动栅极装置trp的栅极。

102.请参照图22,其为根据另一实施例的模拟cam存储单元cl5。模拟cam存储单元cl5包括具有ln型沟道的一第一浮动栅极装置gctn与具有p型沟道的第二浮动栅极装置gctp。第二浮动栅极装置gctp以串联的方式连接于第一浮动栅极装置gctn。第一浮动栅极装置gctn为n型沟道门控晶闸管(n channel gate control thyristor),第二浮动栅极装置gctp为p型沟道门控晶闸管(p channel gate control thyristor)。第一浮动栅极装置gctn的漏极连接于匹配线ml,第一浮动栅极装置gctn的源极连接于第二浮动栅极装置gctp的漏极。第二浮动栅极装置gctp的源极连接于源极线sl。输入信号s1同时输入至第一浮动栅极装置gctn与第二浮动栅极装置gctp的栅极。

103.请参照图23,其为根据另一实施例的模拟cam存储单元cl6。模拟cam存储单元cl6包括具有n型沟道的第一浮动栅极装置gctn及具有p型沟道的第二浮动栅极装置gctp。在模拟cam存储单元cl6中,第二浮动栅极装置gctp以并联的方式连接于第一浮动栅极装置

gctn。在模拟cam存储单元cl6中,第一浮动栅极装置gctn的漏极与第二浮动栅极装置gctp的漏极连接于匹配线ml,第一浮动栅极装置gctn的源极与第二浮动栅极装置gctp的源极连接于源极线sl、sl’。输入信号s1同时输入至第一浮动栅极装置gctn的栅极与第二浮动栅极装置gctp的栅极。

104.根据上述内容,采用浮动栅极装置的模拟内容可寻址存储器可以储存模拟内容,任何与输入信号s1匹配的模拟内容可以被搜索出来。

105.综上所述,虽然本公开已以实施例公开如上,然其并非用以限定本公开。本公开所属技术领域中的本领域技术人员,在不脱离本公开的精神和范围内,当可作各种的更改与修饰。因此,本公开的保护范围当视随附的权利要求范围所界定的为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1