利用外部磁场进行编程辅助的超低功率推理引擎的制作方法

利用外部磁场进行编程辅助的超低功率推理引擎

背景技术:

1.人工神经网络越来越多地用于人工智能和机器学习应用中。在人工神经网络中,将一组输入通过一个或多个中间或隐藏层传播以生成输出。通过多组权重来连接将输入连接到输出的各层,所述多组权重是在训练或学习阶段中通过以下方式生成的:确定用于将输入转换成输出的一组数学变换,移动通过所述层,计算每个输出的概率。一旦确立了权重,就可以在推理阶段使用所述权重来根据一组输入确定输出。虽然此类神经网络可以提供高度准确的结果,但是它们是极其计算密集型的,并且在从存储器中读取不同层的连接权重并将这些权重传输到某种处理单元的多个处理单元中所涉及的数据传输可能相当密集。

附图说明

2.类似编号的元件是指不同的图中的共同部件。

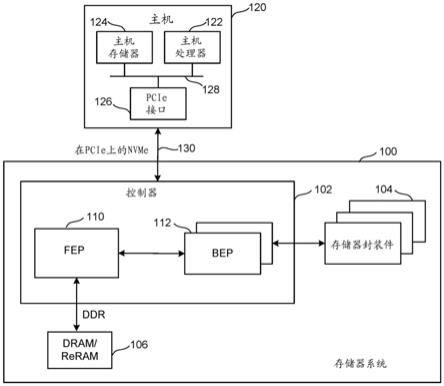

3.图1是连接到主机的存储器系统的一个实施方案的框图。

4.图2是前端处理器电路的一个实施方案的框图。在一些实施方案中,前端处理器电路是控制器的一部分。

5.图3是后端处理器电路的一个实施方案的框图。在一些实施方案中,后端处理器电路是控制器的一部分。

6.图4是存储器封装件的一个实施方案的框图。

7.图5是存储器管芯的一个实施方案的框图。

8.图6a和图6b展示了通过晶圆对晶圆接合而耦接到存储器结构的控制电路的示例。

9.图7示出了卷积神经网络(cnn)的简单示例。

10.图8示出了人工神经网络中的全连接层的简单示例。

11.图9a是描述用于训练神经网络以生成一组权重的过程的一个实施方案的流程图。

12.图9b是描述用于使用神经网络进行推理的过程的一个实施方案的流程图。

13.图10是卷积神经网络中的卷积运算的示意图。

14.图11是矩阵乘法在神经网络的全连接层中的用途的示意图。

15.图12a至图12c描绘了具有交叉点架构的存储器阵列的一部分的一个实施方案。

16.图13是交叉点阵列和用于操作该阵列的一些控制电路的顶视图。

17.图14a示出了用于选择待编程的存储器单元的半选方案。

18.图14b示出了用于选择待编程的存储器单元的全选方案。

19.图15、图16a和图16b示出了mram存储器单元的示例以及电压对切换mram存储器单元的自由层所需的磁场的影响。

20.图17至图19b更详细地示出了由外部磁场辅助对mram交叉点阵列进行编程的实施方案。

21.图20是示出将具有交叉点架构的基于mram的存储器用于推理引擎的实施方案的流程图。

22.图21更详细地示出了mram存储器单元设计的实施方案。

具体实施方式

23.当神经网络执行推理或训练操作时,执行各自涉及大量数据的大量计算,特别是在深度神经网络或dnn的情况下,其结构涉及用来传播输入的大量网络层诸如全连接层和卷积层。为了避免大量数据移入和移出存储器设备,神经网络的层的权重被存储在存储器设备的非易失性存储器阵列中,并且每个层的计算在该设备上执行。为了执行神经网络的层的输入和权重的阵列内乘法,权重值被存储在具有交叉点结构的磁阻随机存取存储器(mram)单元阵列中,该交叉点结构中mram单元位于字线和位线之间的每个交叉点结点处。mram存储器单元可被形成为对于低电阻状态和高电阻状态两者具有高电阻值,同时仍然保持状态之间的较大相对差值。矢量乘法被执行为与神经网络层的输入矢量对应的输入电压矢量与由mram单元状态编码的权重值矩阵之间的阵列内乘法。由于存储器单元即使在低电阻状态下也将汲取少量电流,因此可以在低功率阵列内乘法运算中同时感测多个字线和多个位线。可以使用输入电压和外部磁场的组合对mram单元进行单独编程。外部磁场被选择为使得一组编程电压使各向异性减小到足以利用外部场使选定存储器单元的状态对准,但如果仅施加写入电压的一半,则不足以使存储器单元对准。

24.图1是连接到主机120的存储器系统100的一个实施方案的框图。存储器系统100可实现本文提出的技术,其中从主机120接收神经网络输入或其他数据。根据实施方案,可从主机120接收输入,然后将该输入提供给存储器封装件104以用于对先前编程到存储器封装件104的存储器阵列中的权重进行推断。许多不同类型的存储器系统可与本文提出的技术一起使用。示例性存储器系统包括固态驱动器(“ssd”)、存储卡和嵌入式存储器设备;然而,也可以使用其他类型的存储器系统。

25.图1的存储器系统100包括控制器102、用于存储数据的非易失性存储器104、以及本地存储器(例如,dram/reram)106。控制器102包括前端处理器(fep)电路110和一个或多个后端处理器(bep)电路112。在一个实施方案中,fep电路110在asic上实现。在一个实施方案中,每个bep电路112在单独asic上实现。在其他实施方案中,统一控制器asic可组合前端功能和后端功能两者。用于bep电路112和fep电路110中的每一者的asic在同一半导体上实现,使得控制器102被制造为片上系统(“soc”)。fep电路110和bep电路112均包括其本身的处理器。在一个实施方案中,fep电路110和bep电路112用作主从配置,其中fep电路110是主设备,并且每个bep电路112是从设备。例如,fep电路110实现闪存转换层(ftl)或媒体管理层(mml),该ftl或mml执行存储器管理(例如,垃圾收集、损耗均衡等)、逻辑到物理地址转换、与主机的通信、dram(本地易失性存储器)的管理以及ssd(或其他非易失性存储系统)的整体操作的管理。bep电路112根据fep电路110的请求来管理存储器封装件/管芯中的存储器操作。例如,bep电路112可进行读取、擦除和编程过程。另外,bep电路112可执行缓冲器管理,设置fep电路110所需的特定电压电平,执行纠错(ecc),控制到存储器封装的切换模式接口等。在一个实施方案中,每个bep电路112负责其本身的一组存储器封装。

26.在一个实施方案中,非易失性存储器104包括多个存储器封装件。每个存储器封装件都包括一个或多个存储器管芯。因此,控制器102连接到一个或多个非易失性存储器管芯。在一个实施方案中,存储器封装件104中的每个存储器管芯利用nand闪存存储器(包括

二维nand闪存存储器和/或三维nand闪存存储器)。在其他实施方案中,存储器封装件可包括其他类型的存储器,诸如基于电阻式随机存取存储器(诸如,reram、mram、feram或rram)的存储级存储器(scm)或相变存储器(pcm)。

27.控制器102经由接口130与主机120通信,该接口实现例如pci express(pcie)上的nvm express(nvme)的协议。为了与存储器系统100一起工作,主机120包括沿着总线128连接的主机处理器122、主机存储器124和pcie接口126。主机存储器124是主机的物理存储器,并且可以是dram、sram、非易失性存储器或另一类型的存储装置。主机120在存储器系统100的外部并与该存储器系统分开。在一个实施方案中,存储器系统100嵌入在主机120中。

28.图2是fep电路110的一个实施方案的框图。图2示出与主机120通信的pcie接口150,以及与该pcie接口通信的主机处理器152。主机处理器152可以是本领域中已知的适于实现的任何类型的处理器。主机处理器152与片上网络(noc)154通信。noc是集成电路上的通信子系统,通常在soc中的核心之间。noc可跨越同步和异步时钟域,或者使用非时钟的异步逻辑。noc技术将网络理论和方法应用于片上通信,并且与常规总线和交叉开关互连相比带来了显著的改善。与其他设计相比,noc提高了soc的可扩展性以及复杂soc的功率效率。noc的导线和链路由许多信号共享。由于noc中的所有链路可在不同的数据分组上同时运行,因此实现了高度并行。因此,随着集成子系统的复杂性不断增大,与先前的通信架构(例如,专用的点对点信号线、共享总线或具有桥的分段总线)相比,noc提供增强的性能(诸如吞吐量)和可扩展性。连接到noc 154并且与noc 154通信的是存储器处理器156、sram 160和dram控制器162。dram控制器162用于操作dram(例如,dram 106)并且与该dram通信。sram 160是由存储器处理器156使用的本地ram存储器。存储器处理器156用于运行fep电路并且执行各种存储器操作。与noc通信的还有两个pcie接口164和166。在图2的实施方案中,ssd控制器将包括两个bep电路112;因此,存在两个pcie接口164/166。每个pcie接口与bep电路112中的一个通信。在其他实施方案中,可存在多于或少于两个bep电路112;因此,可存在多于两个pcie接口。

29.fep电路110还可包括闪存转换层(ftl),或更一般地媒体管理层(mml)158,该ftl或mml执行存储器管理(例如,垃圾收集、损耗均衡、负载平衡等)、逻辑到物理地址转换、与主机的通信、dram(本地易失性存储器)的管理,以及ssd或其他非易失性存储系统的整体操作的管理。媒体管理层(mml)158可被集成为可以处理存储器错误并与主机界面交互的存储器管理的一部分。具体地讲,mml可以是fep电路110中的模块,并且可以负责存储器管理的内部。具体地讲,mml 158可包括存储器设备固件中的算法,该算法将来自主机的写入转换为对管芯的存储器结构(例如,下图5中的326)的写入。可能需要mml 158,因为:1)存储器可能具有有限的耐久性;2)该存储器结构可以只写入多个页面;并且/或者3)除非将存储器结构作为块擦除,否则可以不写入该存储器结构。mml158理解存储器结构的这些潜在限制,这些限制可能对主机不可见。因此,mml 158尝试将来自主机的写入转换为向存储器结构的写入。

30.图3是bep电路112的一个实施方案的框图。图3示出用于与fep电路110通信(例如,与图2的pcie接口164和166中的一个通信)的pcie接口200。pcie接口200与两个noc 202和204通信。在一个实施方案中,两个noc可组合成一个大的noc。每个noc(202/204)通过xor引擎(224/254)和ecc引擎(226/256)连接到sram(230/260)、缓冲器(232/262)、处理器(220/

250)和数据路径控制器(222/252)。ecc引擎226/256用于执行纠错,如本领域所知。xor引擎224/254用于对数据执行xor,使得可在存在编程错误的情况下以可恢复的方式组合和存储数据。数据路径控制器222连接到接口模块,以用于经由四个信道与存储器封装件进行通信。因此,顶部noc 202与用于与存储器封装件通信的四个信道的接口228相关联,并且底部noc 204与用于与存储器封装件通信的四个附加信道的接口258相关联。每个接口228/258包括四个切换模式接口(tm接口)、四个缓冲器和四个调度器。对于信道中的每一个存在一个调度器、缓冲器和tm接口。处理器可以是本领域中已知的任何标准处理器。数据路径控制器222/252可以是处理器、fpga、微处理器,或其他类型的控制器。xor引擎224/254和ecc引擎226/256是专用的硬件电路,称为硬件加速器。在其他实施方案中,xor引擎224/254和ecc引擎226/256可在软件中实现。调度器、缓冲器和tm接口是硬件电路。

31.图4是包括连接到存储器总线(数据线和芯片使能线)294的多个存储器管芯292的存储器封装件104的一个实施方案的框图。存储器总线294连接到切换模式接口296以用于与bep电路112的tm接口进行通信(参见例如图3)。在一些实施方案中,存储器封装件可以包括连接到存储器总线和tm接口的小控制器。存储器封装件可以具有一个或多个存储器管芯。在一个实施方案中,每个存储器封装件包括八个或16个存储器管芯;然而,也可以实现其他数量的存储器管芯。本文描述的技术不限于任何特定数量的存储器管芯。

32.图5是存储器管芯300的一个实施方案的功能框图。图5中描绘的部件为电子电路。在一个实施方案中,每个存储器管芯300包括存储器结构326、控制电路310和读/写电路328。存储器结构326能够经由行解码器324由字线来寻址,并且经由列解码器332由位线来寻址。读/写电路328包括多个感测块350并且允许存储器单元页面被并行读取或并行编程,该感测块包括sb1、sb2、

……

、sbp(感测电路)。命令和数据经由线路318在控制器与存储器管芯300之间传输。在一个实施方案中,存储器管芯300包括连接到线路318的一组输入和/或输出(i/o)引脚。

33.控制电路310与读/写电路328配合以在存储器结构326上执行存储器操作(例如,写入、读取等),并且包括状态机312、片上地址解码器314,以及功率控制电路316。状态机312提供存储器操作的管芯级控制。在一个实施方案中,状态机312可由软件编程。在其他实施方案中,状态机312不使用软件并且完全地在硬件(例如,电子电路)中实现。在另一个实施方案中,状态机312被微控制器替换。

34.片上地址解码器314将控制器102使用的地址之间的地址接口提供给解码器324和332所用的硬件地址。功率控制模块316控制在存储器操作期间提供给字线和位线的功率和电压。功率控制模块316可以包括用于产生电压的充电泵。感测块包括位线驱动器。

35.出于本文档的目的,短语“一个或多个控制电路”可包括控制器、状态机、微控制器和/或控制电路310、或用于控制非易失性存储器的其他类似电路。

36.在一个实施方案中,存储器结构326包括非易失性存储器单元的三维存储器阵列,其中多个存储器级形成在单个基板诸如晶圆上方。存储器结构可包括任何类型的非易失性存储器,该非易失性存储器在具有设置在硅(或其他类型的)基板上方的有源区域的存储器单元的一个或多个物理级中一体地形成。在一个示例中,非易失性存储器单元包括具有电荷捕获材料的竖直nand串,诸如例如在美国专利9,721,662中所述的,该专利全文以引用方式并入本文。

37.在另一个实施方案中,存储器结构326包括非易失性存储器单元的二维存储器阵列。在一个示例中,非易失性存储器单元是利用浮栅的nand闪存存储器单元,诸如例如在美国专利9,082,502中所述的,该专利全文以引用方式并入本文。也可使用其他类型的存储器单元(例如,nor型闪存存储器)。

38.包括在存储器结构326中的存储器阵列架构或存储器单元的确切类型不限于上述示例。许多不同类型的存储器阵列架构或存储器技术可用于形成存储器结构326。实现本文提出的要求保护的新实施方案不需要特定的非易失性存储器技术。用于存储器结构326的存储器单元的合适技术的其他示例包括reram存储器(电阻式随机存取存储器)、磁阻存储器(例如,mram、自旋转移扭矩mram、自旋轨道扭矩mram)、feram、相变存储器(例如,pcm)等。用于存储器结构326的存储器单元架构的合适技术的示例包括二维阵列、三维阵列、交叉点阵列、叠堆二维阵列、竖直位线阵列等等。

39.reram交叉点存储器的一个示例包括可逆电阻切换元件,其布置在由x线和y线(例如,字线和位线)存取的交叉点阵列中。在另一个实施方案中,存储器单元可包括导电桥存储器元件。导电桥存储器元件也可称为可编程金属化单元。基于固体电解质内的离子的物理重新定位,导电桥存储器元件可用作状态改变元件。在一些情况下,导电桥存储器元件可包括两个固体金属电极,一个是相对惰性的(例如,钨),而另一个是电化学活性的(例如,银或铜),在两个电极之间具有固体电解质的薄膜。随着温度升高,离子的迁移率也增加,这导致导电桥存储器单元的编程阈值降低。因此,导电桥存储器元件可在整个温度范围内具有宽范围的编程阈值。

40.磁阻随机存取存储器(mram)利用磁存储元件来存储数据。这些元件由两个铁磁薄膜形成,这些铁磁薄膜也被称为层,每层是铁磁性的,由薄绝缘层分开。这两个层中的一个层是被设置为特定极性的永磁体;可以改变另一层的磁化以匹配外磁场的磁化来存储存储器。存储器设备由此类存储器单元的网格构建。在用于编程的一个实施方案中,每个存储器单元位于一对写入线之间,该对写入线被布置成彼此成直角,与单元平行,一个在单元上方并且一个在单元下方。当电流通过它们时,产生感应磁场。下文将更详细地讨论基于mram的存储器实施方案。

41.相变存储器(pcm)利用了硫属化合物玻璃的独特性能。一个实施方案使用gete-sb2te3超晶格通过仅利激光脉冲(或来自另一个源的光脉冲)改变锗原子的配位状态来实现非热相变。因此,编程的剂量是激光脉冲。可以通过阻止存储器单元接收光来抑制存储器单元。在其他pcm实施方案中,存储器单元通过电流脉冲来编程。应当注意,在该文件中使用“脉冲”不需要矩形脉冲,但包括声音、电流、电压光或其他波的(连续或非连续)振动或脉冲串。

42.本领域普通技术人员将认识到,本文所述的技术不限于单个特定存储器结构、存储器配置或材料构成,但涵盖了在如本文所述的以及如本领域普通技术人员所理解的技术实质与范围内的许多相关的存储器结构。

43.可以将图5的元件分成两个部分:存储器单元的存储器结构326;和外围电路,包括所有其他元件。存储器电路的重要特性是其容量,该容量可通过如下方式增加:增加留给存储器结构326作特定用途的存储器管芯300的面积;然而,这减小了可用于外围电路的存储器管芯300的面积。这可以对这些外围元件造成相当严重的限制。例如,需要在可用区域内

装配感测放大器电路,这可是对感测放大器设计架构的重大限制。相对于管芯上控制电路310,可用面积减小会限制可在芯片上实现的可用功能。因此,在存储器管芯300的设计中,需要对存储器结构326的专用面积量以及外围电路的专用面积量进行基本权衡。

44.存储器结构326和外围电路通常相左的另一个领域是形成这些区域所涉及的处理,因为这些区域通常涉及不同的处理技术以及赋予单个管芯以不同制式的权衡。例如,当存储器结构326是nand闪存时,这是nmos结构,而外围电路通常是基于cmos的。例如,感测块350中的感测放大器电路、功率控制块316中的电荷泵、状态机312中的逻辑元件以及其他外围电路通常采用pmos设备。用于制造cmos管芯的处理操作在许多方面将不同于针对nmos闪存nand存储器或其他存储器单元技术所优化的处理操作。

45.为了改进这些限制,下文所述的实施方案可将图5的元件分离到单独形成的管芯上,然后将这些管芯接合在一起。更具体地,存储器结构326可形成在一个管芯上,并且外围电路元件中的一些或全部(包括一个或多个控制电路)可形成在单独的管芯上。例如,存储器管芯可以仅由存储器元件形成,诸如闪存nand存储器、pcm存储器、reram存储器或其他存储器类型的存储器单元阵列。然后可以将外围电路中的一些或全部电路(甚至包括诸如解码器和感测放大器等元件)移到单独的管芯上。这允许根据其技术单独地优化存储器管芯中的每个管芯。例如,nand存储器管芯可针对基于nmos的存储器阵列结构进行优化,而无需担心现在已移到可针对cmos处理进行优化的独立外围电路管芯上的cmos元件。这为外围元件提供了更多空间,如果外围元件被限制于容纳了存储器单元阵列的相同管芯的边缘,则现在可结合可能不容易结合的附加能力。然后可在接合式多管芯存储器电路中将两个管芯接合在一起,其中一个管芯上的阵列连接到另一个存储器电路上的外围元件。例如,虽然下面将集中介绍一个存储器管芯和一个外围电路管芯的接合式存储器电路,但其他实施方案可使用更多管芯,诸如两个存储器管芯和一个外围电路管芯。

46.图6a和图6b示出了图5的另选布置,它可使用晶圆对晶圆接合来实现以提供接合管芯对604。图6a示出了外围电路系统的示例,其包括形成于外围电路或控制管芯608中的控制电路,这些控制电路耦接到形成于存储器管芯610中的存储器结构326。通用部件如图5那样编号。可以看出,控制电路310、读/写电路328和行解码器324(其可通过cmos工艺形成)位于控制管芯608中。附加元件,诸如来自控制器102的功能,也可以移到控制管芯608中。控制电路310、读/写电路328、行解码器324和列解码器332可以由常规工艺(例如,cmos工艺)形成,使得添加更常见于存储器控制器102上的元件和功能可能需要很少的附加工艺步骤或不需要附加工艺步骤(即:用于制造控制器102的相同工艺步骤也可用于制造控制电路310、读/写电路328和行解码器324)。因此,尽管移走管芯(诸如,存储器管芯300)中的此类电路可减少制造此类管芯所需的步骤数量,但向管芯(诸如,控制管芯608)添加此类电路可能不需要任何附加的工艺步骤。

47.图6a示出了控制管芯608上的通过电路径612耦接到存储器管芯610上的存储器结构326的读/写电路328。例如,电路径612可以提供读/写电路328与存储器结构326位线之间的电连接。电路径可以从控制管芯608中的读/写电路328延伸穿过控制管芯608上的焊盘,该焊盘接合到存储器管芯610的对应焊盘,该对应焊盘连接到存储器结构326的位线。存储器结构326的每根位线可具有电路径612中对应的电路径,包括连接到读/写电路328的一对接合焊盘。类似地,行解码器电路324通过电路径614耦接到存储器结构326。电路径614中的

每条电路径可以对应于字线、虚设字线或选定栅极线。也可以在控制管芯608与存储器管芯610之间提供附加的电路径。

48.图6b是示出关于接合的管芯对604的集成存储器组件的一个实施方案的布置的更多细节的框图。存储器管芯610包含存储器单元组成的平面620或阵列。存储器管芯610可以具有附加的平面或阵列。针对每个平面或阵列620示出了一个代表性位线(bl)和代表性字线(wl)。每个平面或阵列620可能有数千条或数万条这样的位线。在一个实施方案中,阵列或平面表示共用一组共同的连续字线和连续位线的一组连接的存储器单元。

49.控制管芯608包括多个感测放大器(sa)350。在一些实施方案中,每个感测放大器350连接到一个位线或者可以连接到多个位线。感测放大器包含位线驱动器。因此,感测放大器可以向与其连接的位线提供电压。感测放大器被配置为感测位线的状况。在一个实施方案中,感测放大器被配置为感测在位线中流动的电流。在一个实施方案中,感测放大器被配置为感测位线上的电压。

50.控制管芯608包括多个字线驱动器660(1)-660(n)。字线驱动器660被配置为向字线提供电压。在该示例中,存储器单元的每个阵列或平面有“n”条字线。在一个实施方案中,如果存储器操作是编程或读取,则选择所选块内的一个字线用于存储器操作。在一个实施方案中,如果存储器操作是擦除,则选择所选块内的所有字线用于擦除。字线驱动器660(例如,功率控制器316的一部分)向存储器管芯610中的字线提供电压。如上面相对于图6a所讨论的,控制管芯608还可以包括电荷泵、电压发生器等(图6b中未表示),其可以用于为字线驱动器660和/或位线驱动器提供电压。

51.存储器管芯610在存储器管芯610的第一主表面682上具有多个接合焊盘670a、670b。可以存在“n”个接合焊盘670a,以从对应的“n”个字线驱动器660(1)

–

660(n)接收电压。与平面620相关联的每个位线可以有一个接合焊盘670b。附图标号670将用于总体上指代主表面682上的接合焊盘。

52.在一些实施方案中,码字的每个数据位和每个奇偶校验位通过不同的接合焊盘对670b、674b传输。码字的位可以通过接合焊盘对670b、674b并行传输。这相对于例如在存储器控制器102与集成存储器组件604之间传输数据提供了非常有效的数据传输。例如,存储器控制器102与集成存储器组件604之间的数据总线可以例如提供要并行传输的8位、16位或可能32位。然而,存储器控制器102与集成存储器组件604之间的数据总线不限于这些示例。

53.控制管芯608在控制管芯608的第一主表面684上具有多个接合焊盘674a、674b。可以存在“n”个接合焊盘674a以将电压从对应的“n”个字线驱动器660(1)-660(n)输送到存储器管芯610。与平面620相关联的每个位线可以有一个接合焊盘674b。附图标号674将用于总体上指代主表面682上的接合焊盘。需注意,可以存在接合焊盘对670a/674a和接合焊盘对670b/674b。在一些实施方案中,接合焊盘670和/或674是倒装芯片接合焊盘。

54.在一个实施方案中,接合焊盘670的图案匹配接合焊盘674的图案。接合焊盘670接合(例如,倒装芯片接合)到接合焊盘674。因此,接合焊盘670、674将存储器管芯610电耦接和物理耦接到控制管芯608。

55.另外,接合焊盘670、674允许存储器管芯610与控制管芯608之间的内部信号传输。因此,存储器管芯610和控制管芯608利用接合焊盘接合在一起。虽然图6a描绘了一个控制

管芯608接合到一个存储器管芯610,但在另一个实施方案中,一个控制管芯608接合到多个存储器管芯610。

56.在本文中,“内部信号传输”意味着控制管芯608与存储器管芯610之间的信号传输。内部信号传输允许控制管芯608上的电路系统控制存储器管芯610中的存储器操作。因此,接合焊盘670、674可以用于存储器操作信号传输。在本文中,“存储器操作信号传输”是指与存储器管芯610中的存储器操作有关的任何信号。存储器操作信号传送可以包括但不限于提供电压、提供电流、接收电压、接收电流、感测电压和/或感测电流。

57.接合焊盘670、674可以由例如铜、铝及其合金形成。在接合焊盘670、674与主表面(682,684)之间可以存在衬垫。衬垫可以由例如钛/氮化钛堆叠形成。接合焊盘670、674和衬垫可以通过气相沉积技术和/或电镀技术施加。接合焊盘和衬垫一起可以具有720nm的厚度,但是在其他实施方案中该厚度可以更大或更小。

58.金属互连件和/或通孔可以用于将管芯中的各种元件电连接到接合焊盘670、674。描述了可以用金属互连件和/或通孔实现的若干导电通路。例如,感测放大器350可通过通路664电连接到接合焊盘674b。相对于图6a,电路径612可以对应于通路664、接合焊盘674b和接合焊盘670b。可能有成千上万个这样的感测放大器、通路和接合焊盘。需注意,bl不一定直接连接到接合焊盘670b。字线驱动器660可以通过通路662电连接到接合焊盘674a。相对于图6a,电路径614可以对应于通路662、接合焊盘674a和接合焊盘670a。需注意,通路662可以包括用于每个字线驱动器660(1)

–

660(n)的单独的导电通路。同样,对于每个字线驱动器660(1)

–

660(n),可以存在单独的接合焊盘674a。存储器管芯610的块2中的字线可以通过通路664电连接到接合焊盘670a。在图6b中,对于块中对应的“n”条字线,存在“n”条通路664。对于每条通路664,可以存在单独的一对接合焊盘670a、674a。

59.相对于图5,图6a的管芯上控制电路也可以包括其逻辑元件内的附加功能,既包括常见于存储器控制器102中的较通用的能力,和一些cpu能力,而且还包括特定于应用的特征。例如,这些激活函数可包括乘法与累加(mac)运算的累加部分所用的加法运算和阈值确定运算、以及更高级运算(诸如,s型函数或tanh函数)。

60.在下文中,状态机312和/或控制器102(或等效功能电路)与图6a中的控制管芯608上所示的其他电路的全部电路或子集电路以及图5中的类似元件相结合,这可视为执行本文所述功能的一个或多个控制电路的一部分。控制电路可以仅包括硬件或者包括硬件和软件(包括固件)的组合。例如,由固件编程以执行本文描述的功能的控制器是控制电路的一个示例。控制电路可包括处理器、fga、asic、集成电路或其他类型的电路。

61.现在转到可存储在非易失性存储器设备中的数据类型,在以下讨论中,所关注的数据类型的具体示例是人工神经网络诸如卷积神经网络或cnn所用的权重。名称“卷积神经网络”是指网络采用称为卷积的数学运算,即一种专用的线性运算。卷积网络是:在其各层中的至少一层中,用卷积代替通用矩阵乘法的神经网络。cnn由输入层和输出层、以及多个中间隐藏层形成。cnn的隐藏层通常是一系列卷积层,这些卷积层对乘法或其他点积进行“卷积”。

62.神经网络中的每个神经元通过将特定函数应用于来自前一层中的接收域的输入值来计算输出值。输入值的应用函数通过权重矢量和偏置来确定。在神经网络中,通过对这些偏置和权重进行迭代调整来进行学习。权重矢量和偏置被称为滤波器并且表示输入的具

体特征(例如,具体形状)。cnn的区别特征是:许多神经元可共享同一滤波器。

63.图7是cnn的示例的示意图。图7示出了像素值阵列的初始输入图像,接着是多个卷积层,继而是多个全连接层,其中最后一层提供输出。第一个卷积层(卷积层1)中的每个神经元获取来自输入图像的n

×

n像素子区域中的输入数据。神经元所习得的权重(统称为其卷积滤波器)确定神经元响应于该输入的单值输出。在该卷积层中,通过沿着图像的x和y维度滑动输入区域以生成卷积层的值,将神经元滤波器应用于输入图像中。实际上,等效卷积通常由神经元针对不同输入区域进行静态相同拷贝来实现。使用每个层的习得权重,通过每个卷积层(卷积层1到卷积层n)来重复该过程,之后使用其习得权重,通过全连接层(l1到lm)来传播该过程。

64.图8更详细地示出了神经网络的若干全连接层。在图8中,所示的三层人工神经网络表示为圆圈所示的节点或人工神经元的互连组,以及从一个人工神经元的输出到另一个人工神经元的输入的一组连接。该示例示出了三个输入节点(i1、i2、i3)和两个输出节点(o1、o2),以及具有四个隐藏或中间节点(h1、h2、h3、h4)的中间层。人工神经网络的节点或人工神经元/突触由主机或其他处理系统的逻辑元件实现为数学函数,该数学函数接收一个或多个输入并将它们进行求和以产生输出。通常,对每个输入进行单独加权,并将总和通过节点的数学函数传递以提供节点的输出。

65.在常见人工神经网络实施方式中,节点(人工神经元/突触)之间的连接处的信号是实数,并且每个人工神经元的输出通过其输入之总和的一些非线性函数来计算。节点及其连接通常具有随着学习过程的进行而调节的权重。权重增大或减小连接处的信号强度。节点可具有阈值,使得仅当聚合信号超过该阈值时才发送信号。通常,节点聚集为层。不同的层可对其输入执行不同类型的转换。信号可能在多次遍历各层之后从第一层(输入层)行进到最后一层(输出层)。虽然图7仅示出单个中间或隐藏层,但是复杂的深度神经网络(dnn)可具有许多此类中间层。

66.受监督的人工神经网络通过供应输入,然后检查和校正输出而被“训练”。例如,受过识别狗品种训练的神经网络将处理一组图像并计算图像中的狗是某一品种的概率。用户可查看结果并选择网络应显示哪些概率(高于特定阈值等),并返回所提议的标签。每一如此的数学变换都被视为一层,并且复杂的神经网络具有许多层。由于大量的中间或隐藏层提供的深度,因此神经网络可以在受训练时对复杂的非线性关系建模。

67.图9a是描述用于训练神经网络以生成一组权重的过程的一个实施方案的流程图。该训练过程往往在云端执行,从而实现待使用的附加或更强大的处理。在步骤901处,接收输入,诸如一组图像(例如,图7中的图像输入)。在步骤903处,使用当前滤波器或权重组,通过将输入连接到下一层(例如,图7中的卷积层1)的层来传播输入。然后在步骤905中,在下一层(例如,图7中的卷积层2)处接收神经网络的输出,使得作为来自一层中的输出所收到的值用作下一层的输入。来自第一层的输入以这种方式通过所有中间层或隐藏层传播,直到它们到达输出。在先前段落的狗品种示例中,输入将是许多狗的图像数据,并且中间层使用当前权重值来计算图像中的狗是某一品种的概率,以及将提议的狗品种标签在步骤905处返回。然后,用户可在步骤907处查看结果,以选择神经网络应返回哪些概率并确定当前权重组是否提供了足够准确的标签,并且如果是,则训练完成(步骤911)。如果结果不够精确,则神经网络基于用户所选择的概率而在步骤909处调节权重,然后循环返回到步骤903

以使用所调节的权重再次运行输入数据。一旦已确定了神经网络的权重组,该权重就可用于“推断”,“推断”是使用所确定的权重来根据输入到神经网络的数据生成输出结果的过程。一旦在步骤911处确定权重,就可以将该权重存储在非易失性存储器中以供稍后使用,其中这些权重在非易失性存储器中的存储过程在下文中进一步详细讨论。

68.图9b是描述了一种使用神经网络进行推理阶段的监督学习的过程的流程图,该过程使用所估计的精确度来预测输入数据的“含义”。根据情况,神经网络可在云端中并且由边缘设备(例如,智能电话、汽车加工,硬件加速器)的处理器进行推断。在步骤921处,接收输入,诸如在上面使用的示例中的狗的图像。如果在运行神经网络应用程序的设备中不存在先前确定的权重,则在步骤922处加载该先前确定的权重。例如,在执行神经网络的主机处理器上,可从存储权重的ssd中读取权重,并加载到主机设备上的ram中。在步骤923处,随后通过神经网络的层来传播输入数据。步骤923将类似于图9b的步骤903,但现在使用在步骤911处的训练过程结束时建立的权重。在通过中间层传播输入之后,然后在步骤925处提供输出。

69.图10是输入图像与滤波器或权重组之间的卷积运算的示意图。在该示例中,输入图像是像素值的6

×

6阵列,并且滤波器是权重的3

×

3阵列。卷积运算通过将3

×

3滤波器与输入图像的3

×

3块的矩阵乘法来执行。例如,将图像的最左上3

×

3块与滤波器相乘得到输出矩阵的左上值。滤波器然后可在图像上滑过一个像素以生成输出的下一个条目,依此类推以生成用于输出的顶行4个元素。通过每次向下滑动滤波器一个像素来重复该过程,生成4

×

4输出矩阵。对每个层执行类似的操作。在实际cnn中,数据集的大小以及所执行卷积的数量意味着:执行极大量的此类操作,从而涉及非常大量的数据。

70.图11是矩阵乘法在神经网络的全连接层中的用途的示意图。矩阵乘法或matmul是神经网络的训练阶段和推断阶段中常用的方法,并且用于机器学习的核方法中。图11的顶部类似于图8,其中在输入层与输出层之间仅示出单个隐藏层。输入数据被表示为长度与输入节点的数量对应的矢量。权重以权重矩阵表示,其中列的数量对应于隐藏层中的中间节点的数量,并且行的数量对应于输入节点的数量。输出是通过输入矢量与权重矩阵的矩阵乘法而确定的,其中输出矢量的每个要素是输入数据的分矢量与权重矩阵的列的点积。

71.用于执行矩阵乘法的常用技术是使用乘法器-累加器(mac,或mac单元)。然而,这有许多问题。重新参见图9b,推理阶段在步骤922处加载神经网络权重,然后在步骤923处通过传播来执行矩阵乘法。然而,由于所涉及的数据量可能非常大,因此使用乘法器-累加器进行推理会产生与权重加载相关的若干问题。这些问题中的一个问题是由于必须使用具有所需位宽的大mac阵列而引起的高能量耗散。另一个问题是由于mac阵列的大小有限而导致的高能量耗散,从而导致逻辑与存储器之间的高数据移动以及可比逻辑计算本身中使用的能量耗散高得多的能量耗散。

72.为了帮助避免这些限制,可以使用其他存储器技术来替代乘法器-累加器阵列的使用。例如,通过利用nand存储器和存储级存储器(scm)的特性,诸如基于以下项的存储器,可以在存储器阵列内计算矩阵乘法:基于reram、pcm、feram或mram的存储器单元。这允许经由读取命令来提供神经网络输入,并且允许预加载神经权重以用于推断。通过使用内存计算,这可以解除对在mac阵列中执行矩阵乘法的逻辑需要以及在存储器与mac阵列之间移动数据的需要。

73.以下呈现了存储器内计算dnn的实施方案,该存储器内计算dnn可通过将神经网络的层的权重存储在存储器单元内并且将层的输入作为电压电平施加到阵列的字线上来执行存储器单元阵列内的推理操作的输入值和权重之间的乘法。位线上的所得电流对应于输入与权重的乘积,其中多个此类乘法可以同时执行。为了减少由此类推理引擎消耗的功率,以下讨论呈现了基于具有交叉点结构的阵列中的mram类型存储器单元的实施方案。mram存储器单元的实施方案具有良好分开的低电阻状态和高电阻状态,同时即使对于低电阻状态也仍然具有高电阻值,从而允许在推理时具有非常低的功率消耗。为了存储dnn的权重,通过使用外部磁场辅助设备上编程电路对mram阵列进行编程。

74.交叉点架构的使用允许具有较小占有面积的阵列,其中矢量乘法由电压到电流转换过程来实现,其中矩阵权重被编码在阵列中的存储器单元的电阻值中。所述mram单元可具有介于低电阻状态(lrs)和高电阻状态(hrs)之间的系数为二或更大的存储器窗口,同时依然具有电阻仍然非常高的低电阻状态,诸如r

lrs

》10mohm。为了降低编程电路通常所需的成本和功率消耗,使用外部磁场进行编程辅助允许在不需要能够提供比执行推理所需高得多的电流和电压的片上电路的情况下进行编程。此外,编程方法允许在不需要针对每个位的专用选择晶体管的情况下选择设备,从而减小了每个位的占位面积。由于存储器设备用于推理,因此存储器设备在被供应给客户之前可使用外部磁场利用先前确定的dnn的权重值进行预编程。

75.更具体地,呈现了超低功率、低成本并且不需要特殊片上编程的基于mram的矢量乘法设备的实施方案。矢量乘法设备可包括在每个交叉点结点处具有mram存储器单元的交叉点阵列和外围阵列电路,该外围阵列电路能够向一个线平面(即字线)中的每个线供应独立的输入电压并且读取另一个线平面(即位线)中的每个线上的电流。输入和权重的矢量相乘被执行为输入电压与由mram存储器单元状态编码的二进制或多状态神经网络权重的乘法。交叉点阵列中的mram存储器单元可使用输入电压和外部磁场的组合进行单独编程,下面的讨论主要集中于mram存储器单元是电压控制的磁各向异性(vcma)mram单元的实施方案。切换vcma单元所需的磁矫顽场(hc)取决于施加到单元的电压。对于一个极性方向,hc单调递减,而对于另一个极性方向,hc单调递增。选择外部场被选择为使得一种极性的输入电压使存储器单元的各向异性减小到足以利用外部场使单元状态对准,但如果仅施加输入电压的一半,则不足以使单元对准。

76.这种布置允许改善的布局效率和更低的成本,因为存储器单元尺寸可由于不使用选择设备或晶体管而更小。另外,由于不需要特殊的编程电路,对于控制/外围元件,可使用较小的晶体管和较不复杂的电路诸如读/写电路。该结构易于延伸达到更紧密的交叉点间距,从而进一步实现更低的成本和更低的功率。由于使用外部场来辅助对存储器单元进行编程,因此可以采用无法单独使用电流或电压来写入的非常高的热稳定性设计。这些设计的高热稳定性允许具有足够保持的存储器单元的小临界尺寸(cd),从而允许使用更小的cd,这继而允许使用更紧密的布线间距。

77.相对于其他存储器单元技术,基于mram的存储器单元通常显示出高度的可调谐性。可通过调谐单元电阻面积(ra)乘积值来实现宽范围的低电阻状态值,而不影响高电阻状态值与低电阻状态值的比率。例如,可利用具有ra=3000ωμm2和200%隧道磁阻比率(tmr)的磁性膜以20nm cd来实现r

lrs

=10mω和r

hrs

=30mω。与其他存储器技术相比,这里

描述的mram结构还可以显示出更好的数据保持、更高的允许操作温度、更长的使用寿命,从而提供优异的读取耐久性和状态稳定性。

78.mram存储器单元通常是被编程为低电阻状态或高电阻状态的二进制设备,并且通常不被操作为每个单元具有多个电阻电平,但是在另选的实施方案中,可以在单个结点处集成若干个位。下面的讨论集中于存储神经网络的二进制值权重或多位权重值的各个位的二进制mram存储器单元。每个存储器单元多个级的能力在推理操作中允许每个操作的更精确计算,可以利用二进制级单元来实现与多级存储器单元等效的精度,但是需要更多的存储器单元来存储每个权重值,从而由于对于要进行n位计算的每个权重值将使用多个mram存储器单元,减少了可存储的权重的数量。下面讨论的实施方案使用基于在每个结点处具有二进制mram存储器单元的交叉点阵列的推理引擎。

79.图12a在斜视图中描绘了形成交叉点架构的存储器阵列326的一部分的一个实施方案。图12a的存储器阵列326是图5中的存储器阵列326的具体实施的一个示例。位线bl

1-bl5沿第一方向(表示为进入页面)布置,并且字线wl

1-wl5沿与第一方向垂直的第二方向布置。图12a是水平交叉点结构的示例,其中字线wl

1-wl5和bl

1-bl5均沿相对于基板的水平方向运行,而存储器单元(1201处示出了其中的两个)被取向成使得电流沿竖直方向运行。在具有存储器单元的附加层的存储器阵列中,将存在位线和字线的对应附加层。

80.如图12a所描绘的,存储器阵列326包括多个存储器单元1201。存储器单元1201可包括可重写的存储器单元,诸如可使用reram、mram、pcm或其他具有可编程电阻的材料来实现。以下讨论将集中于mram存储器单元,但是大部分讨论可以更一般地应用。第一存储器级的存储器单元中的电流可如箭头i

cell

所示向上流动。

81.图12b和图12c分别示出图12a中的交叉点结构的侧视图和顶视图。图12b的侧视图示出了一条底线或字线wl1,和顶线或位线bl

1-bln。在每个顶线和底线之间的交叉点处是mram存储器单元1201。图12c是示出m个底线wl

1-wlm和n个顶线bl

1-bln的交叉点结构的顶视图。在二进制实施方案中,每个交叉点处的mram单元可以被编程为两种电阻状态—高电阻状态和低电阻状态—中的一种。下文给出了关于mram存储器单元设计的实施方案和它们的编程技术的更多细节。

82.图12a至图12c的阵列结构可用于执行推理操作的阵列内乘法,其中神经网络的层的矩阵权重存储在存储器单元中作为其电阻。将电压矢量v

iin

施加到字线的输入端会在位线的输出端中生成电流,该电流对应于输入电压与由mram单元电阻编码的二进制权重的矢量乘法。权重被编码为导电率b

i,j

,它是字线wli和位线blj的交叉点处的存储器单元的电阻r

i,j

的倒数:

[0083][0084]

如果神经网络的层的输入被编码为施加到相应字线wli的电压v

iin

,则每个位线blj上的电流将是以下乘积:

[0085][0086]

其中总和超过i,为通过在多个所选字线上同时执行感测操作,交叉点结构将自动计算该层的输入-权重乘积。

[0087]

需注意,根据该布置,沿着位线的多个存储器单元与施加在其对应字线上的对应输入电压同时被选择用于感测。电流i

jout

对应于所有这些存储器单元的组合结果,并且该过程因此不同于确定沿着位线的各个存储器单元的状态的常规读取操作。此类推理操作的i

jout

是沿着位线的多个存储器单元的组合结果,并且各个存储器单元的贡献将是未知的。

[0088]

图13是交叉点阵列和用于操作该阵列的一些控制电路的顶视图,其中示出了阵列的3

×

3区段。在每个字线wli和位线blj的交叉点处是mram存储器单元m

i,j 1301

i,j

。神经网络的层的输入ini在数模转换器(dac)1311i中从输入值转换为电压电平,即转换为对应的电压电平。层的输入ini可为网络的初始输入或前一层的输出。在二元实施方案中,1输入可以被转换为高读取电压v

read

,0输入可以被转换为低读取电压,诸如0v或地电压,在这种情况下,dac 1311i可以是一位dac。每个位线blj上的模拟电流i

jout

在对应的模数转换器adc 1313j中被转换为数字值,以生成多位数字输出outj。输出值outj然后可转到数字计算块1315,该数字计算块可执行操作,诸如对乘法和累加运算的累积、对输出应用激活功能以及作为将输入传播通过神经网络的一部分而执行的其他此类操作。重新参见图5和图6a,dac 1311i、adc 1313j和数字计算块电路1315可被视为行解码器324、列解码器332和读/写电路328连同310的控制电路的部件的一部分。dac和/或adc可以是多位设备,能够生成或输出以2n(n》1)级量化的信号。

[0089]

考虑到将数据(即权重值)写入阵列,这里呈现的实施方案使用外部磁场辅助mram存储器单元的电编程。更具体地讲,通过电压和外部磁场的组合来进行编程。使用半选方案来完成对选择写入的存储器单元的电选择,如相对于图14a所示。

[0090]

图14a示出了用于选择待编程的存储器单元的半选方案。将电压施加到顶线(位线)和底线(字线),使得沿着位线的旨在被写入的单元具有跨底线和顶线之间的存储器单元施加的写入选择电压v

wr

。未被写入的存储器单元或者仅经历电压降的一半(v

wr

/2)或者不经历电压降。在图14a的示例中,选择写入位线bl

(n-1)

与字线wl1和wl

(m-1)

相交处的两个单元,其中将写入电压v

wr

施加在选定字线上并且将0v(或更一般地,更低的电压电平)施加在选定位线上。其他字线和位线被设置为1/2v

wr

(或者更一般地,写入电压v

wr

和选定字线上的低电压电平中间的某个其他电压电平,使得非选定存储器单元不被编程)。这将v

wr

的差分置于选定存储器单元上,并且将v

wr

或1/2v

wr

置于非选定存储器单元上。可以按逐位线方法执行编程,如下面更详细地讨论的。

[0091]

在图14a的实施方案中,非选定字线和非选定位线两者均被设置为施加到选定字线的v

wr

和施加到选定位线的0v低电压中间的电压。具体地讲,将1/2v

wr

施加到所有非选定位线和字线。然而,其他实施方案可使用不同的值,对于非选定字线使用低于v

wr

的另一个值,对于非选定位线使用高于0v的另一个值。图14b提供了用于偏置阵列以进行编程的另选实施方案的示例。

[0092]

图14b示出了用于选择待编程的存储器单元的全选方案。如本文所用,在全选编程方案中,再次将选定字线偏置到v

wr

并且将选定位线偏置到0v;但是现在,非选定字线被设置为0v,并且非选定位线被设置为v

wr

。在该偏置布置下,非选定存储器单元被稳压,并且半选存储器单元不具有跨半选存储器单元施加的电压,而不是在提供更多编程余量的半选方案中施加的1/2v

wr

。更一般地,非选定字线可被设置为小于v

wr

的另一个电压,并且非选定位线可被设置为高于0v的另一个电压,但是对于非选定字线/位线使用0v/v

wr

可帮助简化所涉及

的偏置电路。

[0093]

在这里主要描述的实施方案中,使用外部磁场来辅助mram单元的电编程。mram单元被设计成能够经由电压控制的磁各向异性(vcma)效应来减小其切换场。这相对于图15、图16a和图16b示出。

[0094]

图15、图16a和图16b示出了mram存储器单元的示例以及电压对切换mram存储器单元的自由层所需的磁场(hc)的影响。更具体地,图15展示了mram存储器单元的结构的一个实施方案。跨存储器单元(在存储器单元的对应字线与位线之间)施加的电压被表示为电压源v

app

1513。该存储器单元包括底部电极1501、被分离层或隧穿层(在该示例中,为氧化镁(mgo)1505)分离的一对磁层(基准层1503和自由层1507),然后是被间隔物1509与自由层1507分离的顶部电极1511。存储器单元的状态基于基准层1503和自由层1507的磁化的相对取向:如果这两个层沿相同方向磁化,则存储器单元将处于低电阻状态(lrs);并且如果它们具有相反取向,则存储器单元将处于高电阻状态(hrs)。基准层1503的取向是固定的,并且在图15的示例中,向下取向。通过将自由层1507编程为具有相同取向或相反取向,来将数据写入存储器单元。通常,通过将所有mram存储器单元设置为处于低电阻状态从而将mram存储器单元阵列置于初始或擦除状态,在低电阻状态下,mram存储器单元的所有自由层具有与其基准层相同的磁场取向。然后,通过将磁场反转为与基准层1503的磁场相反而将存储器单元的自由层1507置于高电阻状态中来对存储器单元中的每个存储器单元选择性地进行编程。基准层1503被形成为使得其将在对自由层1507编程时维持其取向。基准层1503可以具有包括合成反铁磁层和附加基准层的更复杂的设计。为简单起见,附图和讨论省略了这些附加层,并且仅集中于主要负责该单元中的隧穿磁阻的固定磁层。

[0095]

图16a示出了相对于用于辅助在图14a的半选实施方案中进行编程的外部磁场h

prog

的电平,所施加的电压v

app

的电平如何影响由自由层1507经历的磁场hc。当不存在所施加的电压时,自由层1507的磁场hc将较高(例如,约2koe)。例如,当从基准层1503向mram单元的自由层1507侧施加1v时,hc减小(例如,约2koe

→

约1koe)。仅施加0.5v的单元(即,半选单元)具有小于选定单元(例如,约2koe

→

约1.5koe)的hc减小。在外部磁场的辅助下写入选定单元,其中所施加的外部磁场h

prog

被选择为使得其高于能够设置选定单元的磁化的电平,但不高于将使半选单元的状态反转的电平:例如,利用上述值,这可以是外部场h

prog

=+/-1.25koe,其高于偏置到1v的选定存储器单元的自由层1507的hc值,但小于半选(处于0.5v)或非选定存储器单元(处于0v)的hc值。

[0096]

图16b示出了相对于用于辅助在图14b的半选实施方案中进行编程的外部磁场h

prog

的电平,在全选实施方案中所施加的电压v

app

的电平如何影响由自由层1507经历的磁场hc。选定存储器单元将被偏置到处于图16a中的1v,使得其将响应于外部磁场h

prog

而再次编程。对于字线或位线中的一者被选定但另一者未被选定的半选存储器单元,将跨存储器单元施加0v。相对于其中半选存储器单元经历0.5v的图16a的实施方案,这提供了更好的裕度。对于完全非选定存储器单元,其中字线处于0v并且位线处于v

wr

,存储器单元将经历-1v的相对电压(其中v

wr

被视为1v)。通过将图16a与图16b进行比较可以看出,全选实施方案为半选情况和完全非选定情况两者中的非选定存储器单元提供了改善的编程裕度。尽管这跨(完全)非选定存储器单元施加了可引起电流的电压,但由于这里呈现的实施方案对于低电阻状态和高电阻状态均可具有非常高的电阻水平,因此该电流的幅值可相当小并且对于改

善的编程裕度是可接受地权衡。

[0097]

图17至图19b更详细地示出了由外部磁场辅助对mram交叉点阵列进行编程的实施方案。在将权重编程到存储器单元中之前,使用大的外部磁场h

init

将阵列中的所有存储器单元初始化为相同极性。这在图17中示出。如图17的顶部右侧所示,相对较大振幅的外部磁场h

init

向下取向(从顶部电极朝向底部电极)。场h

init

应足以使基准层和自由层沿着相同轴线对准,如图17的下部部分中的mram存储器单元所示。在该示例中,所有单元都被初始化为平行(p)状态,其可以表示二进制1。

[0098]

在初始化之后,以与h

init

相反的极性施加第二磁场(h

prog

),如图18所示。h

prog

被选择为使得具有所施加的v

wr

电压差的单元将从p翻转到可表示二进制0的高电阻反平行(ap)状态,但具有v

wr

/2的单元(如在半选实施方案中)以及具有更小电压的单元(如在全选实施方案中)保持处于低电阻p状态。

[0099]

在施加外部磁场h

prog

的情况下,阵列可被编程,诸如通过逐位编程阵列中的每个位线,诸如图19a中的半选实施方案所示,示出了位线从bl0开始写入并逐位前进到bln。如图19a标示的那样,初始平行状态被标记为p,并且要编程到反平行状态的存储器单元被标记为ap。通过接地来选择要编程的位线,而将所有其他位线设置为v

wr

/2。通过将v

wr

施加到相应的字线,同时将所有其他字线设置为v

wr

/2,来选择要在位线上翻转到ap的单元。例如,在图19a的左侧,选择位线bl1以及字线wl2和wlm上的存储器单元进行写入;并且在图19a的右侧,选择位线bln和字线wl1上的存储器单元进行写入。在没有外部磁场h

prog

的情况下,选定存储器单元上的偏置将不足以引起编程,并且在没有偏置的情况下,外部场h

prog

将不足以引起编程。

[0100]

图19b示出了编程序列如图19a的实施方案,但用于全选实施方案。如前所述,选定位线再次位于0v处,并且对于该位线,要编程的任何字线再次被设置为v

wr

。然而现在,非选定字线现在被设置为0v,并且非选定位线被设置为v

wr

。这将再次偏置沿着选定位线的选定存储器单元,使得它们将再次被编程;但将以改善的裕度偏置非选定存储器单元,如上文相对于图16b所述。图19b示出了在一个实施方案中与图19a中对于位线bl1和bln所选的相同选定存储器单元,该实施方案中编程从bl1顺序地进行到bln。

[0101]

重新参见图5和图6a,涉及存储器单元的读取和写入的控制电路可为行解码器324、列解码器332和读/写电路328连同310的控制电路的部件(诸如状态机312)的一部分。在写入操作期间,行解码器324和列解码器332内的驱动器/偏置电路可偏置字线和位线,如相对于图19a和19b所示,使得单独选定进行编程的mram存储器单元被偏置成使得:当外部磁场处于高于外部磁场的第一值但低于外部磁场的第二值的范围内时,对mram存储器单元进行编程,从而导致整个阵列的重置,该第一值高到足以改变选定存储器单元的状态,该第二值不够高到引起非选定存储器单元和半选存储器单元中的状态变化。使用外部磁场进行编程允许使用相对于操作mram存储器单元的其他技术或比通常用于其他存储器单元技术的电压更低的电压。这些更低的电压电平可改善功率使用并节省布局空间,因为可在电路中使用较小的器件并且可避免使用产生和提供更高电压所需的部件诸如电荷泵和调节器。

[0102]

关于推理操作中的数据读取,如关于图12c所述,不同于确定各个存储器单元的数据状态,行解码器324内的偏置电路将网络的层的输入矢量转换为一组v

in

值,该组值被同时施加到选定一组存储器单元的字线。列解码器332和读/写电路328(包括感测放大器350)将

确定沿着每个字线的总i

out

作为多位感测操作,以指示输入矢量与沿着对应的位线存储的权重值的乘积。由于本文所述的mram存储器单元即使在低电阻(即,平行)状态下也具有高电阻值,所以即使在同时感测多个存储器单元时,电流值仍可相对较低并且推理过程为低功率过程。然后,存储器设备上的控制电路可累积乘法结果作为乘法与累加操作的一部分,以确定神经网络的层的输出,该输出可以是后续层的输入或该网络的输出。

[0103]

多个替代实施方案可结合附加特征。例如,可以在电压辅助下执行关于图17所述的初始化过程。如上所述,如果当跨存储器单元施加的电压v

app

=0时h

init

大于hc的值,则不需要将电压施加到位线或字线以进行初始化。另选地,可将正电压施加到所有字线并且可将位线接地,从而减小初始化所有位需要施加的场的幅值,类似于相对于图16a和图16b所示的过程,但现在选择了阵列的所有存储器单元。

[0104]

在其他另选实施方案中,可使用附加编程步骤来修复不正确编程的位或低编程的位。在此类实施方案中,可通过附加编程步骤来校正编程错误。如上所述,对于具体实施如推理引擎,同时感测沿着共享字线的多个存储器单元。在此类具体实施中,可通过测试阵列在不同输入电压模式下的功能来检测编程错误。潜在错误可以是在编程期间无意中从p翻转到ap的位(或“弱位”)或在编程期间不从p翻转到ap的位(或“硬位”)。可通过应用选择错误位的电压编程序列,但利用被设置为与h

init

相同的极性的外部磁编程场来对弱位进行编程。可通过应用有限编程序列,利用较大外部磁场、较大电压或两者来对硬位进行编程。

[0105]

虽然前述讨论已经在具体实施方案方面进行了呈现,但是它们更普遍地适用。例如,虽然前述讨论主要相对于其中主切换机制是vcma的mram存储器单元进行了描述,但是这些技术也可应用于自旋转移扭矩具体实施。在其他变型中,通过在每个交叉点处堆叠多个mram存储器单元,每个单元可采用多个位。在多位实施方案中,每个单元应具有足够不同的hc值,使得它们可依次写入:首先写入较高hc层,然后逐渐地写入较低hc层。

[0106]

图20是示出将具有交叉点架构的基于mram的存储器用于推理引擎的实施方案的流程图。图20的流程包括用于对mram交叉点存储器阵列进行编程的方法的实施方案(步骤2001-2009)和该存储器阵列用于推理的后续使用(2011-2019)。虽然由于所描述的结构和技术在此类应用中可具有特定实用性,这里的描述是在用于神经网络的推理引擎的上下文中给出的,但是它们可更一般地应用,因为具有高数据保持的低功率非易失性存储器可在许多上下文中使用。

[0107]

从步骤2001开始,如果存储器阵列尚未初始化或需要重新初始化以擦除先前写入的数据,则执行初始化。如相对于图17所述,具有存储器阵列的管芯被放置在磁场h

init

中,该磁场强到足以使自由层1507和基准层1503两者对准。可以在没有跨mram存储器单元施加电压的情况下执行初始化(诸如通过设置字线和位线接地或使它们不偏置),或者在另选的实施方案中,可以跨所有存储器单元施加电压(诸如通过将所有字线偏置到v

wr

并且将所有位线偏置到0v)以使用相对于图16a和16b所述的现象来辅助初始化过程。

[0108]

为了选择性地将数据(诸如神经网络层的权重)写入单独的存储器单元,在步骤2003处,将具有阵列的存储器管芯放置在如图18所示的外部磁场h

prog

中,其中h

prog

将具有相对于h

init

相反的极性和更低的场强。当在外部磁场h

prog

中时,存储器阵列随后在步骤2005被偏置,并且因此在步骤2007被编程。偏置可如图14a所示使用图16a所示的现象来编程选定存储器单元,或者可如图14b中的全选实施方案所示使用图16b所示的现象来编程选定存储

器单元。通过将电压v

wr

(在示例中为1v)施加到选定字线,将0v施加到选定位线,并且将非选定字线和位线设置为1/2v

wr

(在半选实施方案中)或分别设置到0v和v

wr

(在全选实施方案中),自由层1507的磁场hc降至低于h

prog

,并且选定存储器单元的自由层1507将被翻转为处于高电阻反平行状态。可以按逐位线方式进行编程,如图19a所示。

[0109]

在一些实施方案中,在步骤2009处,可执行一个或多个附加编程步骤以校正不正确编程的存储器单元。如上所述,这可用于校正硬位错误和软位错误两者。在一些实施方案中,诸如推理引擎,其中同时感测所有字线或多个字线的子集,可通过顺序地应用适当的一组输入数据模式来检查编程数据以验证先前的编程。

[0110]

由于数据的初始化和编程使用外部磁场的辅助,并且这些磁场的强度通常相当大(诸如在上述示例中外部h

prog

为约1.25koe),因此这些过程通常将在提供给最终用户之前完成。例如,存储器阵列可在运输之前由制造商初始化并编程,诸如在通常在新设备上执行的测试过程结束时。另选地,存储器阵列可在提供给最终用户之前由中间方编程:例如,未编程的存储器阵列(初始化的或未初始化的)可被提供给原始设备制造商(oem),该原始设备制造商然后可对其数据(诸如dnn的权重)进行编程,然后将结合了编程阵列的产品提供给oem的客户。这将是例如依赖于神经网络的自主车辆的情况,并且其中车辆制造商将在将车辆提供给最终运营商之前将其神经网络模型的权重编程到阵列中。

[0111]

步骤2011-2019考虑存储器阵列何时用作推理引擎。深度神经网络可以具有大量层,并且这些层中的每个层的权重可以存储在上述一个或多个mram交叉点类型的阵列中,其中每个存储器管芯可以具有一个或多个此类阵列。为了通过dnn的层传播初始输入,将初始输入矢量施加到第一层的权重,其中第一层的输出用于到下一层的输入,依此类推,通过剩余层,直到实现最终输出。该过程可由一个或多个控制电路(包括管芯上控制电路310和上文相对于图5和图6a所述的其他元件)、存储器系统控制器102(图1)或存储器封装级(104)处的控制电路控制。例如,可在存储器管芯上处理推理操作,诸如管芯上的阵列的乘法和累加运算和管芯内的传播,并且存储器控制器可监视更高层的处理和管芯之间的传输。

[0112]

考虑到给定层的推理,在步骤2011处,接收该层的输入。该输入可以是来自前一层的输出或神经网络的初始输入,这取决于该层在网络内的位置。在步骤2013处,将输入矢量转换为对应的一组字线电压并施加到存储层的权重值的阵列。在这里主要描述的实施方案中,网络是二进制神经网络,其中权重作为二进制值存储在阵列的存储器单元中,并且输入将是输入值的二进制值矢量。如上面关于图13所示,输入矢量ini的多个分量由dac 1311i转换为施加到对应的字线wli的电压电平v

iin

。结果是输入矢量与存储在存储器单元m

i,j 1301

i,j

中的权重之间的阵列内乘法,使得来自每个存储器单元的电流对应于其权重值与所施加的输入的乘积,并且其中每个位线上的电流是来自沿着这些位的存储器单元中的每个存储器单元的电流的总和,如上面关于公式1和公式2所述。

[0113]

步骤2015确定对应于公式2的乘积的每个位线blj上的电流i

jout

,并且该电流由adc 1313j转换为数字输出值outj。然后可在数字计算块1315中累积各个列的这些部分乘积,以在步骤2017中生成该层的输出。步骤2019对应于来自步骤2017的输出的附加传播。根据该实施方案,步骤2019可包括应用激活函数,针对附加值重复推理操作的早期步骤,提供层的输出,或这些操作的某种组合。层的输出随后可用作网络的后续层的输入或网络的最终输

出,具体取决于层在网络内的位置。

[0114]

图21更详细地示出了mram存储器单元设计的实施方案。当放置在交叉点阵列中时,mram存储器单元的顶部电极和底部电极将是阵列的顶线和底线。在这里示出的该实施方案中,底部电极是存储器单元的字线2101,并且顶部电极是该存储器单元的位线2111,但是在一些实施方案中,这些可反转。字线2101与位线2111之间是基准层2103和自由层2107,它们也被mgo势垒2105分离。在图21所示的实施方案中,mgo覆层2108也形成在自由层2107的顶部,并且导电间隔物2109形成在位线2111与mgo覆层2108之间。基准层2103被另一个导电间隔物2102与字线2101分离。存储器单元结构的任一侧是衬里2121和2123,其中这些衬里可以是相同结构的一部分,但是在图21的横截面中看起来是分离的。在衬里2121、2123的任一侧示出了用于填充交叉点结构的原本为空的区域的填充材料2125、2127的一部分。

[0115]

如上所述,在这里用于外部磁场编程辅助交叉点结构的mram单元结构中,存储器单元可形成为对于低电阻平行状态和高电阻反平行状态两者均具有非常高的电阻值,从而允许超低功率推理。根据实施方案,对于在字线和位线之间的平面中的给定区域给出电阻量的ra或电阻面积乘积,ra可以是数十ωμm2(诸如20ωμm2),数百ωμm2,并且甚至多达1000ωμm2或更高,以为字线2101和位线2111之间的总厚度为约20nm-30nm的存储器单元提供1mω或更高的器件电阻。这可连同高电阻反平行状态与低电阻平行状态之间的100%或更高比率电阻差一起获得:(r

ap

–rp

)/r

p

》1。根据实施方案,存储器单元的vcma系数可为至少500oe/v或更高,诸如1koe/v,并且自由层2107的hc值可高于2koe,诸如4koe或更高。

[0116]

关于自由层设计2107,实施方案包括厚度为约1nm至2nm的cofe或cofeb合金,其中ir层可以散布在自由层中靠近mgo势垒2105的位置,并且自由层2107可以掺杂有ta、w或mo。基准层2103的实施方案可以包括与ir或ru间隔物2102耦接的cofeb和copt多层的双层。mgo覆层2108是可选的,但可用于增大自由层2107的各向异性,其中覆层的ra可以为小于主势垒ra的10倍。导电间隔物可以是导电金属,诸如ta、w、ru、cn、tin和tan,等等。

[0117]

在另选的一组实施方案中,可通过使用在存储器管芯自身上生成的奥斯特场来补充或替换用于辅助编程的磁场。推理引擎或更一般的mram阵列仍然可以是交叉点mram阵列,但是其中存储器芯片具有在芯片上生成的磁场的辅助下对单元进行编程的能力。未连接到mram存储器单元的导线阵列(诸如铜线阵列)可以添加在单元之间,或者添加在单元上方或下方的金属层中,该导线阵列用于生成补充的奥斯特磁场并辅助位切换。局部奥斯特磁场添加到外部场并且用于选择用于写入的目标单元,其中附加控制电路可添加到片上控制电路以控制奥斯特场。这可得到更简单的mram单元设计,因为单元不需要能够进行vcma或自旋扭矩转移切换,使得可采用其间具有高比率电阻差的单元,这些单元具有较差的vcma或自旋扭矩转移特性。

[0118]

根据第一组方面,装置包括控制电路,该控制电路被配置为连接到包括沿着一个或多个位线连接的多个磁阻随机存取存储器(mram)存储器单元的阵列。该控制电路被配置为:响应于具有高于第一电平且低于第二电平的场强的所施加的外部磁场,选择性地偏置mram存储器单元中的要编程的单个mram存储器单元;以及响应于施加到沿着共享位线连接的第一多个mram存储器单元的对应的第一多个输入电压,同时感测第一多个mram存储器单元。

[0119]

在附加的方面,方法包括将非易失性存储器设备放置在第一外部磁场中,其中存

储器设备包括根据在非易失性存储器阵列的每个交叉点处具有磁阻随机存取存储器(mram)单元的交叉点架构形成的存储器阵列,mram存储器单元各自具有基准层和自由层,该自由层具有平行极性的磁场。利用第一外部磁场中的非易失性存储器阵列,该方法还包括通过同时进行以下过程沿着存储器阵列的第一位线对一个或多个选定mram存储器单元进行编程以具有自由层,该自由层相对于选定存储器单元的基准层具有反平行极性:将第一位线偏置到低电压值;对于mram存储器单元中的每个mram存储器单元,将存储器阵列的对应字线偏置到写入选择电压;将存储器阵列的除第一位线之外的位线偏置到高于低电压值的电压电平;以及将不与选定mram存储器单元对应的字线偏置到低于写入选择电压值的电压电平,写入选择电压被配置为使得选定mram存储器单元的自由层反转极性,而存储器阵列的非选定mram存储器单元的自由层的极性不反转极性。

[0120]

在另一组方面,非易失性存储器设备包括存储器阵列和连接到该存储器阵列的一个或多个控制电路。该存储器阵列包括:多个字线;多个位线;和多个磁阻随机存取存储器(mram)单元,存储器阵列具有交叉点架构,其中mram存储器单元中的每个mram存储器单元连接在位线中的对应位线与字线中的对应字线之间。该一个或多个控制电路被配置为:响应于具有高于第一电平且低于第二电平的场强的所施加的外部磁场,偏置字线和位线以对mram存储器单元中的选定mram存储器单元进行编程;以及响应于施加到多个位线的电压模式而确定位线中的每个位线上的多位值输出。

[0121]

出于本文件的目的,说明书中提到“实施方案”、“一个实施方案”、“一些实施方案”或“另一个实施方案”可用于描述不同的实施方案或相同的实施方案。

[0122]

出于本文件的目的,连接可为直接连接或间接连接(例如,经由一个或多个其它部件)。在一些情况下,当元件被提及连接或耦接到另一个元件时,该元件可直接连接至另一个元件,或者经由居间元件间接连接至另一个元件。当元件被提及直接连接至另一个元件时,则在该元件与另一个元件之间没有居间元件。如果两个设备是直接连接或间接连接的,则两个设备是“通信”的,使得它们能够在它们之间进行电子信号通信。

[0123]

出于本文档的目的,术语“基于”可理解为“至少部分地基于”。

[0124]

出于本文档的目的,在没有附加上下文的情况下,诸如“第一”对象、“第二”对象和“第三”对象的数字术语的使用可能不意味着对象的排序,而是可用于识别目的以识别不同的对象。

[0125]

出于本文档的目的,对象的术语“组”可指一个或多个对象的“组”。

[0126]

出于说明和描述的目的,已提供了上述详细描述。其并非旨在详尽的或旨在限制本发明所公开的精确形式。根据以上教导内容,很多修改和变型都是可能的。选择所述实施方案以便最好地解释所建议的技术的原理及其实际应用,从而使本领域的其他技术人员能够在各种实施方案中和适合于设想的具体使用的各种修改中最好地利用它。本发明的范围旨在由所附权利要求书限定。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1