一种输入采样方法、电路、存储器和电子设备与流程

1.本技术涉及集成电路领域,尤其涉及一种输入采样方法、电路、存储器和电子设备。

背景技术:

2.随着电子技术的发展,dram(dynamic random access memory,动态随机存取存储器)已经广泛应用在各种各样的电子系统中。由于dram dimm(dual inline memory module,双列直插内存模块)所设计的c/a(command/address,控制/地址)信号的数据总线是由多个dram共享的,即多个dram的c/a信号共同使用一条数据总线,每个dram可能接收到属于其他dram的无效c/a信号。因此,dram需要根据cs(chip select)片选信号,来确定所接收到的c/a信号是否有效。

3.然而,dram会对所接收到的所有c/a信号进行采样,如此,无效的c/a信号也被采样,带来了不必要的能量消耗。同时,dram的工作频率不断提升,c/a信号的和片选信号的脉冲宽度不断收窄,可能导致信号采样失效。

技术实现要素:

4.有鉴于此,本技术实施例提供了一种输入采样方法及电路,在采样之前,对信号进行拓宽与屏蔽。这样,使无效的信号无法被采样,从而减少了能量消耗;同时,拓宽了信号的脉冲宽度,从而降低了信号采样失效的可能性。

5.本技术实施例的技术方案是这样实现的:

6.本技术实施例提供一种输入采样方法,所述方法包括:

7.分别获取第一脉冲信号和第二脉冲信号;

8.对所述第一脉冲信号的脉冲宽度进行拓宽,得到拓宽后的第一脉冲信号;

9.基于所述拓宽后的第一脉冲信号对所述第二脉冲信号中的无效信号进行屏蔽,得到待采样信号;

10.基于时钟信号对所述待采样信号进行采样。

11.本技术实施例还提供一种输入采样电路,所述电路包括:获取单元、拓宽单元、屏蔽单元和采样单元;

12.所述获取单元的第一输出端连接所述拓宽单元的输入端;

13.所述获取单元的第二输出端和所述拓宽单元的输出端分别连接所述屏蔽单元的第一输入端和第二输入端;

14.所述屏蔽单元的输出端连接所述采样单元的数据输入端;

15.时钟信号接入所述采样单元的控制输入端;

16.其中,

17.所述获取单元,用于分别获取第一脉冲信号和第二脉冲信号;

18.所述拓宽单元,用于对所述第一脉冲信号的脉冲宽度进行拓宽,得到拓宽后的第

一脉冲信号;

19.所述屏蔽单元,用于基于所述拓宽后的第一脉冲信号对所述第二脉冲信号中的无效信号进行屏蔽,得到待采样信号;

20.所述采样单元,用于基于时钟信号对所述待采样信号进行采样。

21.本技术实施例还提供了一种存储器,所述存储器至少包括前述的输入采样电路。

22.本技术实施例还提供了一种电子设备,所述电子设备至少包括前述的存储器。

23.由此可见,本技术实施例提供了一种输入采样方法、电路、存储器和电子设备,能够分别获取第一脉冲信号和第二脉冲信号;然后,对第一脉冲信号的脉冲宽度进行拓宽,得到拓宽后的第一脉冲信号;而后,基于拓宽后的第一脉冲信号对第二脉冲信号中的无效信号进行屏蔽,得到待采样信号;最后,基于时钟信号对待采样信号进行采样。这样,在信号采样前,便对无效信号进行了屏蔽,避免了无效信号被采样造成的额外功耗;同时,对信号的脉冲宽度进行了拓宽,避免了采样失效。

附图说明

24.图1为相关技术方案中提供的一种输入采样电路的结构示意图;

25.图2为本技术实施例提供的一种输入采样电路的结构示意图一;

26.图3a为本技术实施例提供的一种输入采样电路的效果示意图一;

27.图3b为本技术实施例提供的一种输入采样电路的效果示意图二;

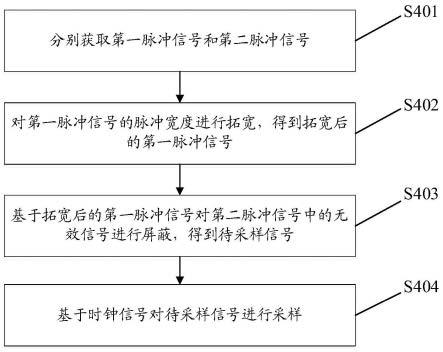

28.图4为本技术实施例提供的一种输入采样方法的流程图一;

29.图5a为本技术实施例提供的一种输入采样电路的效果示意图三;

30.图5b为本技术实施例提供的一种输入采样电路的效果示意图四;

31.图6为本技术实施例提供的一种输入采样电路的效果示意图五;

32.图7为本技术实施例提供的一种输入采样方法的流程图二;

33.图8为本技术实施例提供的一种输入采样方法的流程图三;

34.图9为本技术实施例提供的一种输入采样方法的流程图四;

35.图10为本技术实施例提供的一种输入采样电路的结构示意图二;

36.图11为本技术实施例提供的一种输入采样电路的结构示意图三;

37.图12为本技术实施例提供的一种存储器的结构示意图;

38.图13为本技术实施例提供的一种电子设备的结构示意图。

具体实施方式

39.下面是本技术实施例中所出现的一些名词的解释:

40.dram(dynamic random access memory,动态随机读取存储器):一种半导体存储芯片,常用于内存,属于易失性存储器,即断电以后所存储信息会丢失。dram的作用原理是利用电容内存储电荷的多寡来代表一个二进制比特(bit)是1还是0。

41.ddr-dram(double data rate-dynamic random access memory,双倍数据速率-动态随机读取存储器):一个时钟周期内传输两次数据的dram,能够在时钟的上升期和下降期各传输一次数据,因此能够在相同的总线频率下达到更高的数据传输率。

42.dram dimm(dual inline memory module,双列直插内存模块):具有双插口的内

存模块,两个插口各自独立传输信号,因此可以满足更多数据信号的传输需要。

43.片选信号:选用某一个集成电路芯片时使用的信号。当有多个芯片共用同一总线时,片选信号用来确定总线上的数据、地址信号是传输给哪个芯片的。

44.c/a信号:command/address信号,即控制信号或地址信号。控制信号用于实施对计算机信号的控制。地址信号包含了读取或写入的地址信息。

45.vrefca信号:接收控制与地址信号所采用的参考电压信号,能有效提高系统数据总线的信噪等级。

46.时钟信号:由上级时钟发生器产生的固定周期方波信号,是数字电路中时序逻辑的参考基础,用于决定逻辑单元中的状态何时更新。

47.采样:测量输入信号的样值,并以该样值代替原输入信号在一定时间内的幅值的过程。

48.latch(锁存器):是数字电路中的一种具有记忆功能的逻辑元件,是一种对脉冲电平敏感的存储单元电路,可以在特定输入脉冲电平作用下改变状态,利用电平控制数据的输入,将输入的状态被保存到输出。

49.下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行清楚、完整地描述。

50.在当前dram的c/a输入采样系统中,c/a信号和时钟信号分别通过各自的接收器进入输入采样电路,接着基于时钟信号对c/a信号进行采样,然后输出采样后的c/a信号,用于做之后的逻辑运算。

51.图1是当前dram的c/a输入采样系统中的输入采样电路的结构示意图,如图1所示,输入采样电路10包括:c/a信号接收器11、时钟信号接收器12和采样锁存器(即c/a latch)13。

52.c/a信号通过c/a信号接收器11进入输入采样电路10。c/a信号接收器11接收c/a信号后,输出同步的c/a input信号到采样锁存器13的数据输入端(即d输入端)。时钟信号ckt/ckb通过时钟信号接收器12进入输入采样电路。时钟信号接收器12接收时钟信号后,输出同步的ckt/ckb input信号到采样锁存器13的控制输入端(即ck输入端)。采样锁存器13基于ckt/ckb input信号对c/a input信号进行采样,然后输出采样后的c/aoutput信号。

53.然而,由于dram dimm设计中,c/a数据总线是多个dram共享的,dram需要根据片选信号,来确定所接收到的c/a信号是否有效。在当前的c/a输入采样系统中,dram会对所接收到的所有c/a信号进行采样。这样,无效的c/a信号也被采样,带来了不必要的功耗。

54.图2的输入采样电路20在图1的电路基础上加入了屏蔽单元24,如图2所示,输入采样电路20包括:片选信号接收器21、c/a信号接收器22、时钟信号接收器23、屏蔽单元24和采样锁存器(即c/a latch)25。

55.c/a信号通过c/a信号接收器22进入输入采样电路。c/a信号接收器22接收c/a信号后,输出同步的c/a_1信号到屏蔽单元24的第二输入端。cs_n信号(即片选信号)通过片选信号接收器21进入输入采样电路。片选信号接收器21接收片选信号后,输出同步的cs_1信号到屏蔽单元24的第一输入端。

56.屏蔽单元24对接收到的c/a_1信号和cs_1信号进行逻辑运算,具体逻辑运算表达式(1)如下:

[0057][0058]

表达式(1)中,cs_1表示cs_1信号的逻辑运算值,c/a_1表示c/a_1信号的逻辑运算值,c/a input表示屏蔽单元24输出的c/a input信号的逻辑运算值;“+”表示逻辑或运算,

“”

表示逻辑非运算。

[0059]

而后,屏蔽单元24输出c/a input信号到采样锁存器25的数据输入端(即d输入端)。时钟信号ckt/ckb通过时钟信号接收器23进入输入采样电路20。时钟信号接收器23接收时钟信号ckt/ckb后,输出同步的ckt/ckb input信号到采样锁存器25的控制输入端(即ck输入端)。采样锁存器25基于ckt/ckb input信号对c/a input信号进行采样,然后输出采样后的c/a output信号。

[0060]

在实施时,由于在输入采样电路20中加入了屏蔽单元24,因此,当dram没有接收到片选信号(即cs_n信号为1)时,屏蔽单元24便会屏蔽c/a信号,使c/a input信号恒定为0。这样,在没有接收到片选信号的时候,即使输入采样电路20外部有c/a信号输入,输入采样电路20内部也没有数据翻转,从而节省了功耗。

[0061]

需要说明的是,由于片选信号通常为低电平有效的信号,因此,片选信号常保持为1,当片选信号变化为0时则为有效的触发信号,即当没有接收到片选信号时,cs_n信号为1;c/a信号包含振幅相同而相位相反的两个信号,当两个信号发生了数据翻转时,则为有效的触发信号。

[0062]

然而,dram的工作频率不断提升,c/a信号的和片选信号(即cs_n信号)的脉冲宽度不断收窄。在上述图2所示的输入采样电路20中,由于c/a信号和cs_n信号所经过的路径不同,c/a信号相对于cs_n信号可能提前或者延迟,因此,c/a信号和cs_n信号会发生skew(偏移),从而可能会导致c/a信号的采样失败。如图3a所示的hold time violation,若保持时间不够,则可能导致采样时数据已经发生翻转从而导致采样的数据不准确,而如图3b所示的setup time violation,若采样时,信号还未建立成功,则依然可能会导致c/a信号的采样失败。

[0063]

这样,在偏移的影响下,再加上pvt(process、voltage、temperature,工艺、电压、温度)variation(变化)的影响,屏蔽单元所输出的c/a input信号的脉冲宽度就会变窄,从而可能使c/a采样失效。因此,如何拓宽信号的脉冲宽度成为需要解决的问题。

[0064]

图4是本技术实施例提供的输入采样方法的一个可选的流程示意图,将结合图4示出的步骤进行说明。

[0065]

s401、分别获取第一脉冲信号和第二脉冲信号。

[0066]

本技术实施例中,输入采样电路中的获取单元,会分别获取上级处理单元所发送的第一脉冲信号和第二脉冲信号。

[0067]

其中,第一脉冲信号可以是片选信号;第二脉冲信号可以是c/a信号,即控制信号或者地址信号。片选信号通常为低电平有效,也就是说,片选信号接收器接收到0信号时,则为获取到片选信号。c/a信号中包含了振幅相同、相位相反的两个信号,以脉冲信号形式离散性传输。c/a信号接收器接收到c/a信号发生翻转时,则为获取到有效的c/a信号。

[0068]

需要说明的是,由于在dram dimm设计中,c/a数据总线是多个dram共享的,因此,当前dram所获取到的c/a信号可能是属于其他dram的信号,此时,该c/a信号对当前dram来

说则为无效信号。而判别c/a信号是无效信号还是有效信号,则需要依据片选信号,即c/a信号受到片选信号的控制。具体的,如果当前dram在获取到c/a信号的同时,获取到了片选信号,则该c/a信号是有效信号。

[0069]

s402、对第一脉冲信号的脉冲宽度进行拓宽,得到拓宽后的第一脉冲信号。

[0070]

本技术实施例中,输入采样电路中的拓宽单元,会对第一脉冲信号的脉冲宽度进行拓宽,以得到拓宽后的第一脉冲信号。其中,脉冲宽度是指脉冲达到有效值所持续的时间,对脉冲信号进行拓宽就是延长脉冲有效值所持续的时间。

[0071]

在本技术实施例中,当需要进行拓宽的第一脉冲信号为片选信号时,由于片选信号为低电平有效,因此,拓宽脉冲宽度需要将片选信号的上升沿push(延时),如图5a的cs_a信号所示;和/或,将片选信号的下降沿pull-in(提前),如图5b的cs_b信号所示。这样,便得到了拓宽后的片选信号。

[0072]

图6是本技术实施例中对片选信号进行拓宽的过程示意图,将结合图6对本技术实施例的拓宽过程进行说明。

[0073]

在本技术实施例中,拓宽单元可以将第一脉冲信号通过延时单元,从而对第一脉冲信号进行延时,得到延时后的第一脉冲信号,例如,图6中的cs_2信号就是原cs_1信号延时后的信号。同时,输入采样电路可以减少用于接收第一脉冲信号的第一接收器的绝对延时,或者触发第一接收器的上级处理单元提前发送第一脉冲信号至第一接收器,从而得到提前后的第一脉冲信号,例如,图6中的cs_1信号就是原cs_1信号提前后的信号。

[0074]

而后,拓宽单元可以基于第一脉冲信号、提前后的第一脉冲信号和延时后的第一脉冲信号中的任意两个,生成拓宽后的第一脉冲信号。也就是说,拓宽单元可以对第一脉冲信号和延时后的第一脉冲信号进行第一逻辑运算;或者,对提前后的第一脉冲信号和第一脉冲信号进行第一逻辑运算;又或,对提前后的第一脉冲信号和延时后的第一脉冲信号进行第一逻辑运算。以此,便得到了拓宽后的第一脉冲信号。例如,图6中的cs_3信号就是cs_1信号和cs_2信号经过第一逻辑运算后所得到的拓宽后的信号。

[0075]

需要说明的是,第一逻辑运算的具体形式和第一脉冲信号的种类有关。当第一脉冲信号是片选信号时,由于片选信号为低电平有效,因此,第一逻辑预算为逻辑与运算。以图6为例,对图6中的cs_1信号和cs_2信号进行逻辑与运算,则会得到cs_3信号。其中,cs_1信号中高电平区域a为1信号,和cs_1信号中对应区域的0信号进行逻辑与运算后,得到cs_3信号中对应区域的0信号;同理,cs_2信号中高电平区域b的1信号经过逻辑与运算后,得到了cs_3信号中对应区域的0信号。这样,cs_3信号的下降沿与cs_1信号的下降沿对齐,cs_3信号的上升沿与cs_2信号的上升沿对齐,cs_3信号相对于cs_1信号或cs_2信号便具有了更宽的脉冲宽度,从而完成了对片选信号脉冲宽度的拓宽。

[0076]

而如果第一脉冲信号为其他种类的信号,则第一逻辑运算需要相应调整变化,例如,当第一脉冲信号为高电平有效时,第一逻辑运算需要相应调整为逻辑或运算,在此不做限制。

[0077]

可以理解的是,对片选信号的脉冲宽度进行拓宽,可以在片选信号和c/a信号之间出现skew的情况下,仍然保证片选信号的脉冲宽度能够覆盖c/a信号的脉冲宽度。这样,可以避免后续处理过程中出现的脉冲宽度收窄问题,从而使输入采样不会有出错的风险。

[0078]

s403、基于拓宽后的第一脉冲信号对第二脉冲信号中的无效信号进行屏蔽,得到

待采样信号。

[0079]

本技术实施例中,输入采样电路中的屏蔽单元,会基于拓宽后的第一脉冲信号,对第二脉冲信号中的无效信号进行屏蔽,以得到待采样信号。

[0080]

在本技术实施例中,屏蔽单元可以对第二脉冲信号进行第二逻辑运算,得到第二脉冲信号的中间信号;然后,对拓宽后的第一脉冲信号和第二脉冲信号的中间信号进行第三逻辑运算。这样,便完成了对第二脉冲信号中的无效信号进行屏蔽,得到了待采样信号。

[0081]

需要说明的是,第二逻辑运算和第三逻辑运算的具体形式,与第一脉冲信号和第二脉冲信号的种类有关。当第一脉冲信号和第二脉冲信号分别为片选信号和c/a信号时,由于片选信号为低电平有效,因此,第二逻辑运算为逻辑非运算,第三逻辑运算为逻辑或非运算。也就是说,待采样信号、拓宽后的第一脉冲信号、和第二脉冲信号之间满足逻辑运算表达式(2)如下:

[0082][0083]

表达式(2)中,c/a input表示待采样信号的逻辑运算值,cs_3表示拓宽后的第一脉冲信号的逻辑运算值,c/a表示第二脉冲信号的逻辑运算值;“+”表示逻辑或运算,

“”

表示逻辑非运算。

[0084]

这样,当没有获取到片选信号,即cs_3为1时,不论c/a的值为多少,c/a input的值恒为0。从而实现了基于片选信号对c/a信号中的无效信号进行屏蔽。

[0085]

而如果第一脉冲信号和第二脉冲信号为其他种类的信号,则第二逻辑运算和第三逻辑运算需要相应调整变化,例如,当第一脉冲信号为高电平有效时,第三逻辑运算需要相应调整为逻辑与运算,在此不做限制。

[0086]

需要说明的是,待采样信号的脉冲宽度,与拓宽后的第一脉冲信号以及第二脉冲信号的脉冲宽度有关。当第一脉冲信号和第二脉冲信号分别为片选信号和c/a信号,且满足上述逻辑运算式(2)时,待采样信号的脉冲宽度则为片选信号与c/a信号的脉冲宽度相重合的部分。因此,当片选信号的脉冲宽度被拓宽到足以覆盖c/a信号的脉冲宽度时,屏蔽单元所输出的待采样信号就能够保持与c/a信号具有同样的脉冲宽度。如图5a和图5b中的c/a input信号便能够保持与c/a信号具有同样的脉冲宽度。如此,可以使后续的输入采样不会有出错的风险。

[0087]

可以理解的是,如果c/a信号直接进入采样单元,采样单元会对c/a信号中的无效信号也进行采样,带来了不必要的功耗。因此,屏蔽单元在c/a信号进入采样单元前,将c/a信号中的无效信号屏蔽,这样可以避免无效信号被采样,从而节省了功耗。

[0088]

s404、基于时钟信号对待采样信号进行采样。

[0089]

本技术实施例中,输入采样电路中的采样单元,会分别接收待采样信号和时钟信号,然后,基于时钟信号对待采样信号进行采样。

[0090]

在本技术实施例中,采样单元可以包括c/a latch(即采样锁存器),c/alatch的数据输入端(即d输入端)和控制输入端(即ck输入端)分别接收c/a input信号(即待采样信号)和ckt/ckb input信号(即时钟信号)。当c/alatch获取到时钟信号到达特定的上升沿或下降沿时,触发对c/a input信号进行锁存,将此时c/a input信号的电平保存到输出的c/a output信号,从而完成了基于时钟信号对待采样信号进行采样。

[0091]

需要说明的是,由于c/a latch所接收到的c/a input信号中的无效信号已经被屏蔽,因此,当输入采样电路所获取的c/a信号是无效信号时,采样单元不会进行采样,即c/a latch内部不会发生数据翻转。这样,便节省了功耗。

[0092]

在本技术的一些实施例中,可以通过图7示出的s701至s702来实现上述图4示出的s402,将结合各步骤进行说明。

[0093]

s701、对第一脉冲信号进行延时,得到延时后的第一脉冲信号。

[0094]

本技术实施例中,输入采样电路中的拓宽单元包括了延时单元。延时单元可以对第一脉冲信号进行延时,将第一脉冲信号的脉冲在时间轴上延后,以得到并输出延时后的第一脉冲信号。

[0095]

s702、对第一脉冲信号和延时后的第一脉冲信号进行第一逻辑运算,生成拓宽后的第一脉冲信号;第一逻辑运算为逻辑与运算。

[0096]

本技术实施例中,输入采样电路中的拓宽单元还包括了第一逻辑单元。第一逻辑单元会接收第一脉冲信号和延时后的第一脉冲信号,对这些信号进行第一逻辑运算,以生成拓宽后的第一脉冲信号。

[0097]

需要说明的是,第一逻辑运算的具体形式和第一脉冲信号的种类有关。当第一脉冲信号是低电平有效的片选信号时,第一逻辑预算为逻辑与运算。而如果第一脉冲信号为其他种类的信号,则第一逻辑运算需要相应调整变化,在此不做限制。

[0098]

在本技术的一些实施例中,可以通过图8示出的s801至s803来实现上述图4示出的s402,将结合各步骤进行说明。

[0099]

s801、对第一脉冲信号进行延时,得到延时后的第一脉冲信号。

[0100]

本技术实施例中,输入采样电路中的拓宽单元包括了延时单元。延时单元可以对第一脉冲信号进行延时,将第一脉冲信号的脉冲在时间轴上延后,以得到并输出延时后的第一脉冲信号。

[0101]

s802、对第一脉冲信号进行提前,得到提前后的第一脉冲信号。

[0102]

本技术实施例中,输入采样电路可以对第一脉冲信号进行提前,将第一脉冲信号的脉冲在时间轴上提前,以得到并输出提前后的第一脉冲信号。

[0103]

s803、对提前后的第一脉冲信号和延时后的第一脉冲信号进行第一逻辑运算,生成拓宽后的第一脉冲信号。

[0104]

本技术实施例中,输入采样电路中的拓宽单元还包括了第一逻辑单元。第一逻辑单元会接收提前后的第一脉冲信号和延时后的第一脉冲信号,对这些信号进行第一逻辑运算,以生成拓宽后的第一脉冲信号。

[0105]

需要说明的是,第一逻辑运算的具体形式和第一脉冲信号的种类有关。当第一脉冲信号是低电平有效的片选信号时,第一逻辑预算为逻辑与运算。而如果第一脉冲信号为其他种类的信号,则第一逻辑运算需要相应调整变化,在此不做限制。

[0106]

在本技术的一些实施例中,可以通过s8021-s8022来实现上述图8示出的s802,将结合各步骤进行说明。

[0107]

s8021、减少用于接收第一脉冲信号的第一接收器的绝对延时,得到提前后的第一脉冲信号。

[0108]

本技术实施例中,输入采样电路可以减少自身用于接收第一脉冲信号的第一接收

器的绝对延时,以得到提前后的第一脉冲信号。

[0109]

需要说明的是,第一接收器由于内部结构的影响,具有绝对延时,可以通过改变其内部结构,来减少绝对延时,从而可以得到提前后的第一脉冲信号。

[0110]

s8022、触发第一接收器的上级处理单元提前发送第一脉冲信号至第一接收器,得到提前后的第一脉冲信号。

[0111]

本技术实施例中,输入采样电路可以触发第一接收器的上级处理单元提前发送第一脉冲信号至第一接收器,以得到提前后的第一脉冲信号。

[0112]

需要说明的是,第一脉冲信号是由上级处理单元所发送的,可以通过调节上级处理单元的发送时间,将第一脉冲信号提前发送,以此来对第一脉冲信号进行提前。

[0113]

在本技术的一些实施例中,可以通过图9示出的s901-s902来实现上述图4示出的s403,将结合各步骤进行说明。

[0114]

s901、对第二脉冲信号进行第二逻辑运算,得到第二脉冲信号的中间信号;第二逻辑运算为逻辑非运算。

[0115]

本技术实施例中,输入采样电路中的屏蔽单元包括了第二逻辑单元。第二逻辑单元可以对第二脉冲信号进行第二逻辑运算,以得到并输出第二脉冲信号的中间信号。

[0116]

s902、对拓宽后的第一脉冲信号和第二脉冲信号的中间信号进行第三逻辑运算,得到待采样信号;第三逻辑运算为逻辑或非运算。

[0117]

本技术实施例中,输入采样电路中的屏蔽单元还包括了第三逻辑单元。第三逻辑单元可以接收第一脉冲信号和第二脉冲信号的中间信号,然后对这些信号进行第三逻辑运算,以完成对第二脉冲信号中的无效信号进行屏蔽,得到了待采样信号。

[0118]

需要说明的是,第二逻辑运算和第三逻辑运算的具体形式,与第一脉冲信号和第二脉冲信号的种类有关。当第一脉冲信号和第二脉冲信号分别为低电平有效的片选信号和c/a信号时,第二逻辑运算为逻辑非运算,第三逻辑运算为逻辑或非运算。而如果第一脉冲信号和第二脉冲信号为其他种类的信号,则第二逻辑运算和第三逻辑运算需要相应调整变化,在此不做限制。

[0119]

基于前述的输入采样方法,本技术实施例还提供了一种输入采样电路,参见图10,其示出了本技术实施例提供的一种输入采样电路100的结构示意图。如图10所示,所述输入采样电路100包括:获取单元101、拓宽单元102、屏蔽单元103和采样单元104;

[0120]

所述获取单元101的第一输出端连接所述拓宽单元102的输入端;所述获取单元101的第二输出端和所述拓宽单元102的输出端分别连接所述屏蔽单元103的第一输入端和第二输入端;所述屏蔽单元103的输出端连接所述采样单元104的数据输入端(即d输入端);时钟信号接入所述采样单元104的控制输入端(即ck输入端)。

[0121]

其中,所述获取单元101,用于分别获取第一脉冲信号和第二脉冲信号;所述拓宽单元102,用于对所述第一脉冲信号的脉冲宽度进行拓宽,得到拓宽后的第一脉冲信号;所述屏蔽单元103,用于基于所述拓宽后的第一脉冲信号对所述第二脉冲信号中的无效信号进行屏蔽,得到待采样信号;所述采样单元104,用于基于时钟信号对所述待采样信号进行采样。

[0122]

在本技术实施例中,获取单元101可以分别获取第一脉冲信号和第二脉冲信号。其中,第一脉冲信号是片选信号(即cs_n信号),第二脉冲信号是c/a信号;片选信号为低电平

有效,c/a信号受到片选信号的控制。

[0123]

而后,拓宽单元102接收从获取单元101的第一输出端所输出的第一脉冲信号(即cs_1信号);再对第一脉冲信号的脉冲宽度进行拓宽,得到拓宽后的第一脉冲信号(即cs_3信号)。

[0124]

而后,屏蔽单元103则通过第一输入端接收从拓宽单元102所输出的拓宽后的第一脉冲信号(即cs_3信号),以及,通过第二输入端接收从获取单元101的第二输出端所输出的第二脉冲信号(即ca_1信号);再基于拓宽后的第一脉冲信号对第二脉冲信号中的无效信号进行屏蔽,得到待采样信号(即ca_input信号)。

[0125]

最后,采样单元104通过数据输入端接收屏蔽单元103所输出的待采样信号(即ca_input信号),通过控制输入端接收时钟信号(即ckt/ckb信号);再基于时钟信号对待采样信号进行采样,得到并输出采样后的信号(即ca_output信号)。

[0126]

在上述实施例的输入采样电路100中,所述拓宽单元102包括:延时单元105和第一逻辑单元106;其中,第一逻辑单元106可以为与门;

[0127]

所述获取单元101的第一输出端分别连接所述延时单元105的输入端和所述第一逻辑单元106的第一输入端;所述第一逻辑单元106的输出端和所述获取单元101的第二输出端分别连接所述屏蔽单元103的第一输入端和第二输入端。

[0128]

其中,所述延时单元105,用于对第一脉冲信号进行延时,得到延时后的第一脉冲信号;所述第一逻辑单元106,用于对第一脉冲信号和延时后的第一脉冲信号进行第一逻辑运算,生成拓宽后的第一脉冲信号;第一逻辑运算可以为逻辑与运算。

[0129]

在本技术实施例中,延时单元105接收获取单元101第一输出端所输出的第一脉冲信号(即cs_1信号);再对第一脉冲信号进行延时,得到延时后的第一脉冲信号(即cs_2信号)。

[0130]

第一逻辑单元106通过第一输入端接收获取单元101第一输出端所输出的第一脉冲信号(即cs_1信号),以及,通过第二输入端接收延时单元105所输出的延时后的第一脉冲信号(即cs_2信号);再对第一脉冲信号和延时后的第一脉冲信号进行第一逻辑运算,生成拓宽后的第一脉冲信号(即cs_3信号)。

[0131]

需要说明的是,采用何种第一逻辑单元106,需要依据第一脉冲信号的种类来决定。当第一脉冲信号为低电平有效时,如图11所示,第一逻辑单元106为与门,第一逻辑运算为逻辑与运算;而如果第一脉冲信号为其他种类的信号,则第一逻辑单元106需要相应调整变化,例如,当第一脉冲信号为高电平有效时,第一逻辑单元106需要相应调整为或门,在此不做限制。

[0132]

在上述实施例的输入采样电路100中,所述屏蔽单元103包括:第二逻辑单元107和第三逻辑单元108;所述第二逻辑单元107可以为非门;所述第三逻辑单元108可以为或非门;

[0133]

所述拓宽单元102的输出端连接所述第三逻辑单元108的第一输入端;所述获取单元101的第二输出端连接所述第二逻辑单元107的输入端;所述第二逻辑单元107的输出端连接所述第三逻辑单元108的第二输入端;所述第三逻辑单元108的输出端连接所述采样单元104的数据输入端。

[0134]

其中,所述第二逻辑单元107,用于对第二脉冲信号进行第二逻辑运算,得到第二

脉冲信号的中间信号;第二逻辑运算可以为逻辑非运算;所述第三逻辑单元108,用于对拓宽后的第一脉冲信号和第二脉冲信号的中间信号进行第三逻辑运算,得到待采样信号;第三逻辑运算可以为逻辑或非运算。

[0135]

在本技术实施例中,第二逻辑单元107接收获取单元101第二输出端所输出的第二脉冲信号(即c/a_1信号);再对第二脉冲信号进行逻辑非运算,得到第二脉冲信号的中间信号。

[0136]

第三逻辑单元108通过第一输入端接收拓宽单元102输出端所输出的拓宽后的第一脉冲信号(即cs_3信号),以及,通过第二输入端接收第二逻辑单元107所输出的中间信号;再对拓宽后的第一脉冲信号和中间信号进行逻辑或非运算,得到待采样信号。

[0137]

需要说明的是,采用何种第二逻辑单元107和第三逻辑单元108,需要依据第一脉冲信号和第二脉冲信号的种类来决定。当第一脉冲信号为低电平有效时,如图11所示,第二逻辑单元107为非门,第三逻辑单元108为或非门,相应的,第二逻辑运算为逻辑非运算,第三逻辑运算为逻辑或非运算。而如果第一脉冲信号和第二脉冲信号为其他种类的信号,则第二逻辑单元107和第三逻辑单元108需要相应调整变化,例如,当第一脉冲信号为高电平有效时,第三逻辑单元108需要相应调整为与门,在此不做限制。

[0138]

在上述实施例的输入采样电路100中,所述获取单元101包括:

[0139]

第一接收器109,用于获取第一脉冲信号;所述第一接收器109的输出端作为所述获取单元101的第一输出端;

[0140]

第二接收器110,用于获取第二脉冲信号;所述第二接收器110的输出端作为所述获取单元101的第二输出端。

[0141]

第三接收器111,用于获取时钟信号,并将时钟信号输入到所述采样单元104的控制输入端。

[0142]

需要说明的是,第一接收器109具有绝对延时,可以通过改变其内部结构,来减少绝对延时。而通过减少第一接收器109的绝对延时,或者触发第一接收器109的上级处理单元提前发送第一脉冲信号至第一接收器109,则可以得到提前后的第一脉冲信号;而后,可以将提前后的第一脉冲信号作为cs_1信号输入拓宽单元102。拓宽单元102则可以基于提前后的第一脉冲信号来得到拓宽后的第一脉冲信号。

[0143]

在上述实施例的输入采样电路100中,所述采样单元104包括采样锁存器112;所述屏蔽单元103的输出端连接所述采样锁存器112的数据输入端(即d输入端);时钟信号接入所述采样锁存器的控制输入端(即ck输入端)。

[0144]

在本技术实施例中,采样锁存器112的数据输入端和控制输入端分别接收c/a input信号(即待采样信号)和ckt/ckb input信号(即时钟信号)。当采样锁存器112获取到时钟信号到达特定的上升沿或下降沿时,触发对c/a input信号进行锁存,将此时c/a input信号的电平保存到输出的c/a output信号,从而完成了基于时钟信号对待采样信号进行采样。

[0145]

需要说明的是,本技术实施例所提供的输入采样电路100的设计应用于dram c/a输入采样系统,但不局限于此范围,高频系统中的指令采集和低功耗系统均可采用此电路设计。

[0146]

可以理解的是,本技术实施例所提供的输入采样电路100的设计优化原有的低功

耗设计,使c/a输入采样系统在高频下也能保持足够宽度的有效信号脉冲,从而增加低功耗设计在高频下的可靠性。

[0147]

在本技术的一些实施例中,通过减少片选信号接收器的绝对延时,来pull-in原cs_1信号。然后经过一个延时单元,将整个cs_1脉冲推迟至cs_2的位置。最后通过一个与门对cs_1信号和cs_2信号进行逻辑与运算,形成相较于原cs_1,下降沿被pull-in,上升沿被push的cs_3的片选信号。

[0148]

通过本技术实施例的技术方案,cs片选信号被pull-in,然后将上升沿push一段延迟,如此,可以保证即使在pvt variation的影响下,片选信号的脉冲宽度仍然可以覆盖整个周期内的c/a信号。这样,屏蔽单元的输出将不会由于片选信号和c/a信号之间skew而产生脉冲宽度收窄,从而保证了c/a信号在高频下的足够脉冲宽度,使下一级的输入采样不会有出错的风险。本技术的实施例在解决脉冲宽度收窄这一技术问题的同时,仍然保留了片选信号将非目标dram的c/a信号屏蔽的功能,保证了c/a输入采样系统的低功耗设计依然有效。

[0149]

在本技术的又一实施例中,参见图12,其示出了本技术实施例提供的一种存储器的结构示意图。如图12所示,所述存储器120至少包括前述实施例中任一项所述的输入采样电路100。

[0150]

在本技术实施例中,存储器120可以集成有输入采样电路100,所述输入采样电路100能够分别获取第一脉冲信号和第二脉冲信号;然后,对第一脉冲信号的脉冲宽度进行拓宽,得到拓宽后的第一脉冲信号;而后,基于拓宽后的第一脉冲信号对第二脉冲信号中的无效信号进行屏蔽,得到待采样信号;最后,基于时钟信号对待采样信号进行采样。这样,在信号采样前,便对无效信号进行了屏蔽,避免了无效信号被采样造成的额外功耗;同时,对信号的脉冲宽度进行了拓宽,避免了采样失效。

[0151]

在本技术的再一实施例中,参见图13,其示出了本技术实施例提供的一种电子设备130的结构示意图。如图13所示,所述电子设备130至少包括前述实施例所述的存储器120,通过对无效信号的屏蔽和对信号脉冲宽度的拓宽,能够在信号采样前,便对无效信号进行了屏蔽,避免了无效信号被采样造成的额外功耗;同时,对信号的脉冲宽度进行了拓宽,避免了采样失效。

[0152]

需要说明的是,在本技术中,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者装置不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、物品或者装置所固有的要素。在没有更多限制的情况下,由语句“包括一个

……”

限定的要素,并不排除在包括该要素的过程、方法、物品或者装置中还存在另外的相同要素。

[0153]

上述本技术实施例序号仅仅为了描述,不代表实施例的优劣。本技术所提供的几个方法实施例中所揭露的方法,在不冲突的情况下可以任意组合,得到新的方法实施例。本技术所提供的几个产品实施例中所揭露的特征,在不冲突的情况下可以任意组合,得到新的产品实施例。本技术所提供的几个方法或设备实施例中所揭露的特征,在不冲突的情况下可以任意组合,得到新的方法实施例或设备实施例。

[0154]

以上所述,仅为本技术的具体实施方式,但本技术的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本技术揭露的技术范围内,可轻易想到变化或替换,都应涵

盖在本技术的保护范围之内。因此,本技术的保护范围应以所述权利要求的保护范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1