存储器装置和包括该存储器装置的存储器系统的制作方法

存储器装置和包括该存储器装置的存储器系统

1.于2020年12月9日提交到韩国知识产权局的并且题为“存储器装置和包括该存储器装置的存储器系统”的第10-2020-0171363号韩国专利申请通过引用全部包括在此。

技术领域

2.本公开涉及一种存储器装置以及包括该存储器装置的存储器系统。

背景技术:

3.半导体存储器装置可被分类为非易失性存储器装置(诸如,闪存装置)和易失性存储器装置(诸如,dram)。易失性存储器装置(诸如,dram)相对便宜,并且因此用于存储大容量数据(诸如,系统存储器)。此外,在易失性半导体存储器装置(诸如,dram)中,减小了工艺规模以增加集成度。

技术实现要素:

4.实施例涉及一种存储器装置,所述存储器装置包括:存储器单元阵列,包括布置成多个行的存储器单元;ecc引擎,被配置为:检测响应于读取命令和读取地址而从存储器单元阵列读取的第一数据中的错误,输出第一错误发生信号,并且纠正第一数据中的错误;行故障检测器,被配置为输出故障行地址,故障行地址指示所述多个行之中的故障行;以及标志生成器,被配置为:接收读取地址、第一错误发生信号和故障行地址,并且生成解码状态标志和故障行标志,解码状态标志指示错误是否被检测到以及错误是否被纠正,故障行标志指示包括在读取地址中的读取行地址为故障行地址。

5.实施例还涉及一种存储器装置,所述存储器装置包括:存储器单元阵列,包括布置成多个行的存储器单元;ecc引擎,被配置为:检测响应于读取命令和读取地址而从存储器单元阵列读取的第一数据中的错误,输出错误发生信号和第一数据中的错误的校正子,并且纠正第一数据中的错误;行故障检测器,被配置为周期性地检测故障行地址,故障行地址指示所述多个行之中的故障行;以及标志生成器,被配置为:将包括在读取地址中的读取行地址与故障行地址进行比较,当读取行地址与故障行地址相同时生成指示读取行地址为故障行地址的故障行标志,并且当读取行地址与故障行地址不相同时,基于校正子和错误发生信号生成指示错误是否被检测到以及错误是否被纠正的解码状态标志。

6.实施例还涉及一种存储器系统,所述存储器系统包括:存储器装置;以及存储器控制器,被配置为:将读取命令和读取地址提供给存储器装置。存储器装置可包括:存储器单元阵列,包括布置成多个行的存储器单元;ecc引擎,被配置为:检测响应于读取命令和读取地址而从存储器单元阵列读取的第一数据中的错误,输出第一错误发生信号,并且纠正第一数据中的错误;行故障检测器,被配置为输出故障行地址,故障行地址指示所述多个行之中的故障行;以及标志生成器,被配置为:基于读取地址、第一错误发生信号和故障行地址而生成解码状态标志和故障行标志。故障行标志可由两个比特组成并且可具有第一值,并且解码状态标志可由两个比特组成并且可具有第二值、第三值和第四值中的任何一个值,

第二值、第三值和第四值彼此不同并且均与第一值不同。

附图说明

7.通过参照附图详细描述示例实施例,对于本领域技术人员来说,特征将变得清楚,在附图中:

8.图1是用于说明根据一些示例实施例的存储器系统的框图;

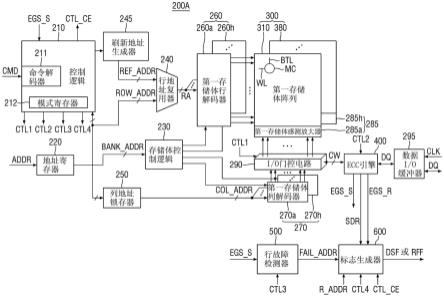

9.图2是用于说明图1的存储器装置的框图;

10.图3是用于说明图2的ecc引擎的框图;

11.图4是用于说明图3的ecc编码电路的框图;

12.图5是用于说明图3的ecc解码电路的框图;

13.图6是用于说明图2的行故障检测器的框图;

14.图7是用于说明图2的标志生成器的框图;

15.图8是用于说明图2的存储器装置的操作的示图;

16.图9是用于说明根据一些示例实施例的存储器装置的操作的流程图;

17.图10是用于说明图9的操作s140的流程图;

18.图11是用于说明图9的操作s150的流程图;

19.图12是用于说明根据图9的示例实施例的存储器装置的操作的时序图;

20.图13是用于说明根据一些其它示例实施例的存储器装置的操作的框图;

21.图14是用于说明根据图13的示例实施例的存储器装置的操作的时序图;

22.图15是用于说明根据一些其它示例实施例的图1的存储器装置的框图;

23.图16是用于说明图15的标志生成器的示图;

24.图17是用于说明图1的存储器控制器的框图;

25.图18是用于说明根据一些示例实施例的存储器装置的框图;以及

26.图19是用于说明应用了根据一些示例实施例的存储器装置的移动系统的框图。

具体实施方式

27.图1是用于说明根据一些示例实施例的存储器系统的框图。

28.参照图1,根据一些示例实施例的存储器系统1可包括存储器控制器100和存储器装置200。

29.存储器控制器100可总体控制存储器系统1的操作。存储器控制器100可应用用于控制存储器装置200的操作命令以控制存储器装置200的操作。

30.存储器控制器100可控制主机与存储器装置200之间的数据交换。存储器控制器100可响应于来自主机的请求,将数据写入存储器装置200中或从存储器装置200读取数据。

31.例如,存储器控制器100可将时钟信号clk、命令cmd和地址addr发送到存储器装置200,并且将数据dq发送到存储器装置200以及从存储器装置200接收数据dq。存储器装置200可将解码状态标志dsf或故障行标志(fail row flag)rff发送到存储器控制器100。

32.解码状态标志dsf可包括关于“是否检测到在存储器装置200的存储器单元阵列300中发生的错误”以及“是否纠正了检测到的错误”的信息。故障行标志rff可包括关于“由读取行地址(包括在与读取命令一起输入的读取地址中)指示的存储器单元阵列300的行是

故障行”的事实的信息。

33.存储器装置200可包括控制逻辑210、存储器单元阵列300、ecc(纠错码)引擎400、行故障检测器500和标志生成器600。

34.在一些示例实施例中,存储器装置200可以是dram(动态随机存取存储器)、ddr4(双倍数据速率4)sdram(同步dram)、lpddr4(低功率ddr4)sdram或lpddr5 sdram、ddr5 sdram或包括动态存储器单元的gddr(图形ddr)。根据一些示例实施例,存储器装置200可以是包括静态存储器单元(或比特单元)的静态存储器(sram)装置。

35.控制逻辑210可总体控制存储器装置200的操作。

36.ecc引擎400可在控制逻辑210的控制下检测从存储器单元阵列300读取的读取数据的错误,并且可生成错误发生信号,对错误进行纠正并且输出错误被纠正的读取数据。ecc引擎400可在控制逻辑210的控制下生成将被写入存储器单元阵列300中的写入数据的奇偶校验位,并且由此生成的奇偶校验位可与写入数据一起被写入存储器单元阵列300中。

37.行故障检测器500可基于从ecc引擎400输出的错误发生信号而周期性地检测故障行地址。

38.在一个示例中,标志生成器600可基于从行故障检测器500输出的故障行地址和从ecc引擎400输出的错误发生信号,生成解码状态标志dsf或故障行标志rff。在另一示例中,标志生成器600可基于与读取命令一起输入的读取地址、从行故障检测器500输出的故障行地址和从ecc引擎400输出的错误发生信号,生成解码状态标志dsf或故障行标志rff。解码状态标志dsf可指示错误是否已经从自存储器单元阵列300读取的读取数据被检测到以及是否纠正了检测到的错误。故障行标志rff可指示包括在读取地址中的读取行地址是故障行地址。

39.解码状态标志dsf和故障行标志rff可由两个或更多个比特组成,并且可具有彼此不同的值。例如,解码状态标志dsf和故障行标志rff可由两个比特组成,并且可具有彼此不同的值。故障行标志可具有第一值,并且解码状态标志dsf可具有与第一值不同的第二值至第四值之一。例如,故障行标志rff可具有值“10”,并且解码状态标志dsf可具有值“00”、“01”和“11”中的任何一个。当没有错误被检测到时,解码状态标志dsf可具有值“00”,当错误被检测到并且检测到的错误被纠正时,解码状态标志dsf可具有值“01”,并且当错误被检测到并且错误未被纠正时,解码状态标志dsf可具有值“11”。解码状态标志dsf和故障行标志rff可具有固定值,并且存储器控制器100可设置用于设置存储器装置200的模式的模式寄存器组,以改变指示解码状态标志dsf和故障行标志rff的错误比特的类型。

40.图2是用于说明图1的存储器装置的框图。

41.参照图1和图2,存储器装置200a可包括控制逻辑210、地址寄存器220、存储体控制逻辑230、行地址复用器240、刷新地址生成器245、列地址锁存器250、行解码器260、列解码器270、感测放大器285、i/o门控电路290、存储器单元阵列300、ecc引擎400、行故障检测器500、标志生成器600和数据i/o缓冲器295。

42.存储器单元阵列300可包括用于存储数据的多个存储器单元mc。例如,存储器单元阵列300可包括第一存储体阵列310至第八存储体阵列380。第一存储体阵列310至第八存储体阵列380中的每个可包括多条字线wl、多条位线btl以及形成在字线wl和位线btl相交的点处的多个存储器单元mc。

43.多个存储器单元mc可包括第一存储体阵列310至第八存储体阵列380。尽管图2示出包括八个存储体阵列310至380的存储器装置200a,但是实施例不限于此,并且存储器装置200a可包括任何数量的存储体阵列。

44.控制逻辑210可控制存储器装置200a的操作。例如,控制逻辑210可生成控制信号,使得存储器装置200a执行写入数据的操作或读取数据的操作。控制逻辑210可包括对从存储器控制器100接收的命令cmd进行解码的命令解码器211和用于设置存储器装置200a的操作模式的模式寄存器212。

45.例如,命令解码器211可对写入使能信号/we、行地址选通信号/ras、列地址选通信号/cas、芯片选择信号/cs等进行解码,以生成对应于命令cmd的控制信号。控制逻辑210还可接收时钟信号clk和时钟使能信号/cke,用于以同步方式驱动存储器装置200a。

46.控制逻辑210可响应于刷新命令而控制刷新地址生成器245生成刷新行地址ref_addr。

47.地址寄存器220可从存储器控制器100接收地址addr。例如,地址寄存器220可接收包括存储体地址bank_addr、行地址row_addr和列地址col_addr的地址addr。地址寄存器220可将接收的存储体地址bank_addr提供给存储体控制逻辑230,将接收的行地址row_addr提供给行地址复用器240,并且将接收的列地址col_addr提供给列地址锁存器250。

48.存储体控制逻辑230可响应于从地址寄存器220接收的存储体地址bank_addr而生成存储体控制信号。响应于存储体控制信号,第一存储体行解码器260a至第八存储体行解码器260h之中的与存储体地址bank_addr对应的存储体行解码器可被激活,并且第一存储体列解码器270a至第八存储体列解码器270h之中的与存储体地址bank_addr对应的存储体列解码器可被激活。

49.行地址复用器240可从地址寄存器220接收行地址row_addr,并且从刷新地址生成器245接收刷新行地址ref_addr。行地址复用器240可选择性地输出从地址寄存器220接收的行地址row_addr或从刷新地址生成器245接收的刷新行地址ref_addr作为行地址ra。从行地址复用器240输出的行地址ra可被施加到第一存储体行解码器260a至第八存储体行解码器260h中的每个。

50.刷新地址生成器245可生成用于刷新存储器单元的刷新行地址ref_addr。刷新地址生成器245可将刷新行地址ref_addr提供给行地址复用器240。因此,位于与刷新行地址ref_addr对应的字线上的存储器单元可被刷新。

51.列地址锁存器250可从地址寄存器220接收列地址col_addr,并临时存储接收的列地址col_addr。列地址锁存器250可在突发模式下逐渐增大接收的列地址col_addr。列地址锁存器250可将临时存储或逐渐增大的列地址col_addr施加到第一存储体列解码器270a至第八存储体列解码器270h中的每个。

52.行解码器260可包括连接到第一存储体阵列310至第八存储体阵列380中的每个的第一存储体行解码器260a至第八存储体行解码器260h。列解码器270可包括连接到第一存储体阵列310至第八存储体阵列380中的每个的第一存储体列解码器270a至第八存储体列解码器270h。感测放大器285可包括连接到第一存储体阵列310至第八存储体阵列380中的每个的第一存储体感测放大器285a至第八存储体感测放大器285h。

53.第一存储体行解码器260a至第八存储体行解码器260h之中的由存储体控制逻辑

230激活的存储体行解码器可对从行地址复用器240输出的行地址ra进行解码,以激活对应于行地址ra的字线。例如,被激活的存储体行解码器可将字线驱动电压施加到对应于行地址ra的字线。

54.第一存储体列解码器270a至第八存储体列解码器270h之中的由存储体控制逻辑230激活的存储体列解码器可通过i/o门控电路290激活第一存储体感测放大器285a至第八存储体感测放大器285h之中的与存储体地址bank_addr和列地址col_addr对应的存储体感测放大器。

55.i/o门控电路290可包括输入数据掩码逻辑(input data mask logic)、读数据锁存器、写入驱动器和门控电路,读数据锁存器用于存储从第一存储体阵列310至第八存储体阵列380输出的数据,写入驱动器用于将数据写入第一存储体阵列310至第八存储体阵列380中,门控电路用于门控i/o数据。

56.将从第一存储体阵列310至第八存储体阵列380中的一个存储体阵列读取的码字cw可由第一存储体感测放大器285a至第八存储体感测放大器285h之中的与所述一个存储体阵列对应的存储体感测放大器检测,并且可被存储在读取数据锁存器中。ecc引擎400可对存储在读取数据锁存器中的码字cw执行ecc解码。当错误从码字cw的数据被检测到时,ecc引擎400可在纠错的同时输出第一错误发生信号egs_r,并且可通过数据i/o缓冲器295将纠正的数据dq提供给存储器控制器100。在由ecc引擎400从码字cw的数据检测错误的处理中生成的第一错误发生信号egs_r和校正子sdr可被提供给标志生成器600。

57.将被写入第一存储体阵列310至第八存储体阵列380中的一个存储体阵列中的数据dq可被提供给ecc引擎400,ecc引擎400可基于数据dq生成奇偶校验位,并且将数据dq和奇偶校验位提供给i/o门控电路290。i/o门控电路290可通过写入驱动器将数据dq和奇偶校验位写入到所述一个存储体阵列的子页上。

58.数据i/o缓冲器295可在写入操作中基于从存储器控制器100提供的时钟信号clk将数据dq提供给ecc引擎400,并且可在读取操作中将从ecc引擎400提供的数据dq提供给存储器控制器100。

59.在包括在存储器单元阵列300中的多个行被执行刷新操作的区段(section)或时段中,ecc引擎400可对从执行刷新操作的每个行读取的码字执行ecc解码。ecc引擎400可通过从构成单个行的每个子页读取码字来执行ecc解码。当错误从自每个行读取的码字数据被检测到时,ecc引擎400可输出第二错误发生信号egs_s,并且可执行纠错并将纠错后的数据再次写入对应的子页上的清理操作(scrubbing operation)。因此,在包括在存储器单元阵列300中的多个行被执行刷新操作的多个区段之中的错误检查和清理区段中,ecc引擎400可输出第二错误发生信号egs_s和第二校正子,并执行清理操作。

60.行故障检测器500可从ecc引擎400接收第二错误发生信号egs_s并对其进行计数。例如,在一个示例中,行故障检测器500可针对包括在存储器单元阵列300中的每个行对第二错误发生信号egs_s进行计数,并且基于此检测故障行。行故障检测器500可将对应于故障行的故障行地址fail_addr提供给标志生成器600。在另一示例中,行故障检测器可对第二错误发生信号egs_s进行计数,并且基于通过对第二错误发生信号egs_s进行计数而获得的值和第二校正子来输出清理行地址作为故障行地址。

61.行故障检测器500可在包括在存储器单元阵列300中的多个行被执行刷新操作的

多个区段之中的错误检查和清理区段中检测故障行。因此,行故障检测器500可周期性地检测对应于故障行的故障行地址fail_addr。

62.标志生成器600可从地址寄存器220接收读取行地址r_addr,从ecc引擎400接收校正子sdr和第一错误发生信号egs_r,并且从行故障检测器500接收故障行地址fail_addr。标志生成器600可基于读取行地址r_addr、故障行地址fail_addr、校正子sdr和第一错误发生信号egs_r生成解码状态标志dsf或故障行标志rff,并且可将解码状态标志dsf或故障行标志rff提供给存储器控制器100。

63.控制逻辑210可生成用于对命令cmd进行解码以控制i/o门控电路290的第一控制信号ctl1、用于控制ecc引擎400的第二控制信号ctl2、用于控制行故障检测器500的第三控制信号ctl3以及用于控制标志生成器600的第四控制信号ctl4和第五控制信号ctl_ce(在下文中,又被称为“比较信号”)。控制逻辑210可基于从ecc引擎400提供的第二错误发生信号egs_s生成第五控制信号ctl_ce。在一个示例中,控制逻辑210可将通过对第二错误发生信号egs_s进行计数而获得的值与阈值进行比较,并输出比较信号ctl_ce。

64.图3是用于说明图2的ecc引擎的框图。为了便于说明,与ecc引擎400一起示出第一存储体阵列310。

65.参照图3,第一存储体阵列310可包括正常单元阵列nca(存储器单元阵列310a)和冗余单元阵列rca(ecc单元阵列310b)。

66.ecc引擎400可包括ecc编码电路410和ecc解码电路420。

67.ecc编码电路410可响应于第二控制信号ctl2而生成与将被写入正常单元阵列nca(310a)的存储器单元中的写入数据wdq(例如,64比特)相关的奇偶校验位prt(例如,8比特)。奇偶校验位prt可被存储在冗余单元阵列rca(310b)中。根据本示例实施例,ecc编码电路410可响应于第二控制信号ctl2而对将被写入正常单元阵列nca(310a)的包括故障单元的存储器单元中的写入数据wdq生成奇偶校验位prt。

68.ecc解码电路420可响应于第二控制信号ctl2而使用从正常单元阵列nca(310a)的存储器单元读取(即,读取数据)的数据rdq(例如,64比特)和从冗余单元阵列rca(310b)读取的奇偶校验位prt(例如,8比特)来纠错,并且可输出纠错后的数据cdq。根据本示例实施例,ecc解码电路420可响应于第二控制信号ctl2而使用从正常单元阵列nca(310a)的包括故障单元的存储器单元读取的读取数据rdq和从冗余单元阵列rca(310b)读取的奇偶校验位来纠错,并且可输出纠错后的数据cdq。ecc解码电路420可在纠错的同时输出错误发生信号egs_r、egs_s。ecc解码电路420可在存储器装置200的读取操作时输出第一错误发生信号egs_r,并且可在存储器装置200的清理操作时输出第二错误发生信号egs_s。

69.图4是用于说明图3的ecc编码电路的框图。

70.参照图4,ecc编码电路410可包括奇偶校验生成器412,奇偶校验生成器412响应于第二控制信号ctl2而接收写入数据wdq和基础比特bb,并且使用异或(xor)阵列计算来生成奇偶校验位prt。基础比特bb可以是用于生成写入数据wdq的奇偶校验位prt的比特。基础比特bb可由例如b个00000000比特组成。基础比特bb可利用其它特定比特来代替b个00000000比特。

71.图5是用于说明图3的ecc解码电路的框图。

72.参照图5,ecc解码电路420可包括校正子生成器422、系数计算器424、错误位置检

测器426和纠错器428。

73.校正子生成器422可响应于第二控制信号ctl2而接收读取数据rdq和奇偶校验位prt,并且使用xor阵列计算来生成校正子sdr。

74.系数计算器424可使用校正子sdr来计算错误位置等式(error position equation)的系数。错误位置等式可以是其中错误比特的倒数是基数(radix)的等式。

75.错误位置检测器426可使用所计算的错误位置等式来计算1比特错误(1-bit error)的位置。错误位置检测器426可向纠错器428提供指示1比特错误的位置的错误位置信号eps。当错误从读取数据rdq被检测到时,错误位置检测器426可输出错误发生信号egs(例如,egs_r和/或egs_s)。

76.纠错器428可接收读取数据rdq,并且基于错误位置信号eps来确定包括在读取数据rdq中的1比特错误的位置。纠错器428可通过根据所确定的1比特错误位置信息来反转读取数据rdq之中已经发生错误的比特的逻辑值来纠错,并且可输出纠错后的读取数据cdq。

77.图6是用于说明图2的行故障检测器的框图。

78.参照图2和图6,行故障检测器500可包括计数器510、阈值寄存器520、比较器530和故障行地址生成器540。

79.计数器510可从ecc引擎400接收在从执行刷新操作的每个行读取的码字中生成的第二错误发生信号egs_s。计数器510可接收第二错误发生信号egs_s并对第二错误发生信号egs_s进行计数。计数器510可基于计数的第二错误发生信号egs_s将指示错误发生次数的信号noe提供给比较器530。

80.阈值寄存器520可存储阈值th_f。阈值th_f可以是例如响应于从存储器控制器(图1的100)提供的命令cmd而设置的值。

81.比较器530可将指示错误发生次数的信号noe与从阈值寄存器520读取的阈值th_f进行比较,并输出指示比较结果的比较信号cs_e。

82.故障行地址生成器540可接收比较信号cs_e和读取的行,并且可基于比较信号cs_e生成故障行地址fail_addr。例如,当从行读取的码字中发生的错误发生次数等于或大于阈值th_f时,故障行地址生成器540可将所述行确定为故障行,并且可输出由所述行指示的行地址s_addr(例如,清理行地址)作为故障行地址fail_addr。

83.因此,行故障检测器500可检测执行刷新的每个行是否是故障行。

84.图7是用于说明图2的标志生成器的框图。

85.参照图2和图7,标志生成器600可包括寄存器610、地址比较器620和信号生成器630。

86.从行故障检测器500提供的故障行地址fail_addr可被存储在寄存器610中。

87.地址比较器620可在存储器单元阵列300的读取操作时接收包括在读取地址addr中的读取行地址r_addr。地址比较器620可将读取行地址r_addr与从寄存器610读取的故障行地址fail_addr进行比较,并且输出指示比较结果的比较信号cs_a。

88.信号生成器630可接收比较信号cs_a,并基于比较信号cs_a输出解码状态标志dsf或故障行标志rff。当读取行地址r_addr与从寄存器610读取的故障行地址fail_addr相同时,信号生成器630可生成故障行标志rff。例如,信号生成器630可生成故障行标志rff,而不管从ecc引擎400提供的第一错误发生信号egs_r和校正子sdr。当读取行地址r_addr与从

寄存器610读取的故障行地址fail_addr不相同时,信号生成器630可生成解码状态标志dsf。信号生成器630可基于从控制逻辑210提供的比较信号ctl_ce和从ecc引擎400提供的第一错误发生信号egs_r来生成解码状态标志dsf。

89.图8是用于说明图2的存储器装置的操作的示图。

90.在图8中,假设存储器核/外围电路(peri)201包括图2的存储器装置200a中的除了ecc引擎400、行故障检测器500和标志生成器600之外的组件。

91.参照图2和图8,在一个示例中,标志生成器600可基于从行故障检测器500提供的故障行地址fail_addr和从ecc引擎400提供的第一错误发生信号egs_r,生成解码状态标志dsf或故障行标志rff。在另一示例中,标志生成器600可基于与读取命令一起输入的读取地址、从行故障检测器500提供的故障行地址fail_addr和从ecc引擎400提供的第一错误发生信号egs_r,生成解码状态标志dsf或故障行标志rff。行故障检测器500可基于从ecc引擎400提供的第二错误发生信号egs_s检测故障行并输出故障行地址fail_addr。

92.存储器装置200可包括彼此不同的第一引脚202和第二引脚204。

93.存储器装置200可通过第一引脚202将数据dq发送到存储器控制器100和从存储器控制器100接收数据dq。其中的错误被ecc引擎400纠正的数据dq可通过第一引脚202被提供给存储器控制器100。第一引脚202可以是例如数据引脚。

94.存储器装置200可通过第二引脚204向存储器控制器100提供解码状态标志dsf或故障行标志rff。第二引脚204可以是例如dmi(直接媒体接口)引脚。第二引脚204可由彼此不同的第一子引脚和第二子引脚组成,并且解码状态标志dsf或故障行标志rff可相应地由两个比特组成。

95.图9是用于说明根据一些示例实施例的存储器装置的操作的流程图。图10是用于说明图9的操作s140的流程图。图11是用于说明图9的操作s150的流程图。图12是用于说明根据图9的示例实施例的存储器装置的操作的时序图。

96.参照图1至图9,根据一些示例实施例的存储器装置200可从存储器控制器100接收读取命令read_cmd和读取地址read_addr(s100)。可将包括在读取地址read_addr中的读取行地址r_addr和从行故障检测器500检测到的故障行地址fail_addr提供给标志生成器600的地址比较器620。

97.地址比较器620可比较读取行地址r_addr与故障行地址fail_addr是否相同(s110)。地址比较器620可输出指示比较结果的比较信号cs_a。

98.标志生成器600的信号生成器630可基于比较信号cs_a,在读取行地址r_addr与故障行地址fail_addr相同(s110,是)时生成故障行标志rff(s120)。故障行标志rff可由两个比特组成,并且可具有值“10”。

99.可输出由ecc引擎400纠错后的数据和由标志生成器600生成的故障行标志rff(s130)。

100.另一方面,在操作s110,当基于比较信号cs_a,读取行地址r_addr与故障行地址fail_addr不相同(s110,否)时,标志生成器600的信号生成器630可基于从控制逻辑210提供的比较信号ctl_ce来确定在存储器装置200的清理操作中检测到的错误的数量是否等于或大于阈值th_ce(s115)。阈值th_ce可以是例如根据存储器控制器100设置的值(例如,可纠正错误(ce)阈值),并且可依靠存储器装置200的规范来设置。

101.当比较信号ctl_ce指示检测到的错误的数量等于或大于阈值th_ce(s115,是)时,信号生成器630可在不考虑阈值th_ce的情况下生成解码状态标志dsf(s140)。

102.参照图10中的操作s140,当ecc引擎400具有sedsec(单比特错误检测单比特错误纠正)的能力时,信号生成器630可基于从ecc引擎400提供的校正子sdr和计数的第一错误发生信号egs_r的数量来确定错误是否从读取数据被检测到以及错误是否被纠正。

103.信号生成器630可确定ecc引擎400的解码结果是否是“未从读取数据检测到错误”的情况(无错误;ne)(s141)。例如,当校正子sdr为0并且计数的第一错误发生信号egs_r的数量为0时,信号生成器630可确定存在“未从读取数据检测到错误”的情况。在操作s141,当ecc引擎400的解码结果是“未从读取数据检测到错误”的情况(s141,ne=是)时,信号生成器630可生成指示这一点的解码状态标志dsf(s142)。该解码状态标志dsf可由两个比特组成,并且可具有值“00”(dsf_ne(00))。

104.在操作s141,当ecc引擎400的解码结果不是“未从读取数据检测到错误”的情况(s141,ne=否)时,信号生成器630可确定是否存在“一个错误从读取数据被检测到并且被纠正”(可纠正错误,ce)的情况(s143)。例如,当校正子sdr不为0并且计数的第一错误发生信号egs_r的数量为1时,信号生成器630可确定存在“一个错误从读取数据被检测到并且被纠正”的情况。在操作s143,当ecc引擎400的解码结果是“一个错误从读取数据被检测到并且被纠正”的情况(s143,ce=是)时,信号生成器630可生成指示这一点的解码状态标志dsf(s144)。解码状态标志dsf可由两个比特组成,并且可具有值“01”(dsf_ce(01))。在操作s143,当ecc引擎400的解码结果不是“一个错误从读取数据被检测到并且被纠正”的情况(s143,ce=否)时,信号生成器630可生成指示“两个或更多个错误从读取数据被找到并且未被纠正”的情况ue的解码状态标志dsf(s146)。该解码状态标志dsf可由两个比特组成,并且可具有值“11”(dsf_ue(11))。

105.再次参照图1至图9,当在图9的操作s115处比较信号ctl_ce指示在存储器装置200的清理操作中检测到的错误的数量小于阈值th_ce(s115,否)时,信号生成器630可考虑阈值th_ce而生成解码状态标志dsf(s150)。

106.参照图11中的操作s150,当ecc引擎400具有sedsec的能力时,信号生成器630可基于从ecc引擎400提供的校正子sdr和第一错误发生信号egs_r来确定错误是否从读取数据被检测到错误以及错误是否被纠正。

107.信号生成器630可确定ecc引擎400的解码结果是否是“未从读取数据检测到错误”的情况ne(s151)。例如,当校正子sdr为0并且计数的第一错误发生信号egs_r的数量为0时,信号生成器630可确定存在“未从读取数据检测到错误”的情况。在操作s151,当ecc引擎400的解码结果是“未从读取数据检测到错误”的情况(s151,ne=是)时,信号生成器630可生成指示这一点的解码状态标志dsf(s152)。该解码状态标志dsf可由两个比特组成,并且可具有值“00”(dsf_ne(00))。

108.在操作s151,当ecc引擎400的解码结果不是“未从读取数据检测到错误”的情况(s151,ne=否)时,信号生成器630可确定是否存在“一个错误从读取数据被检测到并且被纠正”的情况(s153)。例如,当校正子sdr不为0并且计数的第一错误发生信号egs_r的数量为1时,信号生成器630可检测到存在“一个错误从读取数据被检测到并且被纠正”的情况。在操作s153,当ecc引擎400的解码结果是“一个错误从读取数据被检测到并且被纠正”的情

况(s153,ce=是)时,信号生成器630可执行操作s152。因此,信号生成器630可生成由两个比特组成并具有值“00”的解码状态标志dsf。信号生成器630可不生成具有值“01”的解码状态标志dsf。

109.在操作s153,当ecc引擎400的解码结果不是“一个错误从读取数据被检测到并且被纠正”的情况(s153,ce=否)时,信号生成器630可生成指示“两个或更多个错误从读取数据被找到并且未被纠正”的情况ue的解码状态标志dsf(s156)。该解码状态标志dsf可由两个比特组成,并且可具有值“11”(dsf_ue(11))。

110.再次参照图1至图9,可输出由ecc引擎400纠错后的数据和由标志生成器600生成的解码状态标志dsf(图9的s160)。例如,解码状态标志dsf可由两个比特组成,并且可具有“00”、“01”和“11”之中的任何一个值。

111.参照图12,可从存储器控制器100将时钟信号clk提供给存储器装置200。可从存储器控制器100提供写入时钟信号wck连同命令cmd。读取选通信号rdqs是与数据dq一起由存储器装置200发送到存储器控制器100的信号。读取延迟rl可指示从接收到读取命令read至输出数据dq的时延。

112.可通过第一引脚(图8的202)以突发单元dq_brt将读取数据dq提供给存储器控制器100。

113.解码状态标志dsf或故障行标志rff可通过第二引脚204被提供给存储器控制器100。第二引脚(图8的204)可以是dmi引脚(dmip)。解码状态标志dsf或故障行标志rff可与读取数据dq一起被输出。

114.当如在操作s150中一样考虑到可纠正错误的阈值来生成解码状态标志dsf时,在检测到的错误数量小于可纠正错误的阈值时,存储器装置200可仅输出指示“未从读取数据检测到错误”的情况ne的解码状态标志dsf或指示“两个或更多个错误被找到并且未被纠正”的情况ue的解码状态标志dsf。因此,存储器控制器100可不去确定是否存在“一个错误在读取行地址r_addr中被检测到并且被纠正”的情况ce。因此,即使当读取行地址r_addr是故障行时,存储器控制器100也不会确定这一点。

115.另一方面,如在操作s110中一样,当读取行地址r_addr是故障行地址时,根据一些示例实施例的存储器装置200可不管可纠正错误的阈值而输出故障行标志rff。因此,存储器控制器100可确定它是故障行,并且可基于此来确定错误管理策略。因此,可进一步提高或增强存储器装置200的可靠性。

116.图13是用于说明根据一些其它示例实施例的存储器装置的操作的框图。图14是用于说明根据图13的实施例的存储器装置的操作的时序图。

117.参照图1至图13,根据一些示例实施例的存储器装置200可接收读取命令read_cmd和读取地址read_addr(s200),并且比较读取行地址r_addr与故障行地址fail_addr是否相同(s210)。操作s200、s210和s215可分别对应于图9的操作s100、s110和s115。

118.在操作s210,基于比较信号cs_a,当读取行地址r_addr和故障行地址fail_addr相同(s210,是)时,标志生成器600的信号生成器630可在不考虑阈值th_ce的情况下生成解码状态标志dsf(s220)。当在操作s210基于比较信号cs_a,行地址r_addr和故障行地址fail_addr不相同(s210,否)并且在操作s215比较信号ctl_ce指示检测到的错误的数量等于或大于阈值th_ce(s215,是)时,标志生成器600的信号生成器630可执行s220的操作。操作s220

可对应于图9和图10的操作s140。

119.在操作s215,当比较信号ctl_ce指示检测到的错误的数量小于阈值th_ce(s215,否)时,信号生成器630可考虑阈值th_ce来生成解码状态标志dsf(s230)。操作s230可对应于图9和图11的操作s150。

120.可输出由ecc引擎400纠错后的数据和由标志生成器600生成的解码状态标志dsf(s240)。例如,解码状态标志dsf可由两个比特组成,并且可具有“00”、“01”和“11”中的任何一个值。

121.参照图14,可通过第一引脚(图8的202)以突发单元dq_brt将读取数据dq提供给存储器控制器100。

122.可通过第二引脚204将解码状态标志dsf提供给存储器控制器100。第二引脚(图8的204)可以是dmi引脚(dmip)。解码状态标志dsf可与读取数据dq一起被输出。当读取行地址r_addr是故障行地址时,根据一些示例实施例的存储器装置200可输出指示“一个错误从读取数据被检测到并且被纠正”的情况ce的解码状态标志dsf,而不管可纠正错误的阈值如何。因此,存储器控制器100可监测读取行地址r_addr的解码状态标志dsf,并且可基于此来确定错误管理策略。因此,可进一步提高或增强存储装置200的可靠性。

123.图15是用于说明根据一些其它示例实施例的图1的存储器装置的框图。图16是用于说明图15的标志生成器的示图。为了便于说明,将主要说明与参照图1和图2说明的点不同的点。

124.参照图15和图16,根据一些其它示例实施例的存储器装置200b可包括寄存器650。

125.行故障检测器500可检测存储器单元阵列300的故障行地址,并且将检测到的故障行地址fail_addr存储在寄存器650中。行故障检测器500可响应于第三控制信号ctl3而从寄存器650读取故障行地址fail_addr并且将其提供给标志生成器600。

126.标志生成器600可接收故障行地址fail_addr以生成解码状态标志dsf或故障行标志rff。

127.图17是用于说明图1的存储器控制器的框图。

128.参照图1和图17,存储器控制器100可包括解码状态标志或故障行标志解码器120和控制器140。

129.解码状态标志或故障行标志解码器120可对从存储器装置200提供的解码状态标志dsf或故障行标志rff进行解码以生成解码信号ds。

130.控制器140可基于解码信号ds来监测存储器单元阵列300的故障行地址或检测到错误的行地址。控制器140可基于解码信号ds来确定存储器装置200的错误管理策略。

131.例如,当解码信号ds指示“未从读取数据检测到错误”的情况ne时(例如,当解码信号ds具有值“00”时),控制器140可将错误管理策略保持为原样。

132.当解码信号ds指示“一个错误从读取数据被检测到并且被纠正”ce时(例如,当解码信号ds具有值“01”时),控制器140可对该行进行监测。控制器140可对该行进行监测并确定它是否对应于故障行。

133.当解码信号ds指示故障行地址时(例如,当解码信号ds具有值“10”时),控制器140可执行该行的页离线(page offline)。控制器140可改变错误管理策略以便不使用该行。

134.当解码信号ds指示“两个或更多个错误被发现并且未被纠正”的情况ue时(当解码

信号ds具有值“11”时),由于数据是包括错误的数据,因此控制器140可重新尝试将数据读取到存储器装置200。因此,可再次将读取命令提供给存储器装置200。可选择地,控制器140可用额外的行来修复该行。可选择地,控制器140可改变错误管理策略以便不使用该行。

135.图18是用于说明根据一些示例实施例的存储器装置的框图。

136.参照图18,根据一些示例实施例的存储器装置700可使用3d芯片结构来实现。存储器装置700可包括主机裸片710、pcb(印刷电路板)720和存储器组裸片730。

137.主机裸片710可位于pcb 720上。主机裸片710可通过倒装芯片凸块(flip chip bump)fb连接到pcb 720。主机裸片710可以是例如soc(片上系统)、cpu(中央处理器)或gpu(图形处理器)。

138.存储器组裸片730可包括堆叠的多个存储器裸片d11至d14。多个存储器裸片d11至d14可形成hbm(高带宽存储器)结构。tsv线(贯穿硅过孔,也称为硅通孔)可形成在存储器裸片d11至d14中以实现hbm结构。tsv线可电连接到形成于存储器裸片d11至d14之间的微凸块mcb。

139.尽管在图18中省略了缓冲器裸片或逻辑裸片,但是缓冲器裸片或逻辑裸片可位于存储器裸片d11与主机裸片710之间。

140.图19是用于说明应用了根据一些示例实施例的存储器装置的移动系统的框图。

141.参照图19,移动系统800可包括应用处理器(ap)810、连接件820、用户接口830、非易失性存储器装置(nvm)840、易失性存储器装置(vm)850和电源860。易失性存储器装置850可包括存储器单元阵列852和通道接口电路。

142.应用处理器810可执行提供互联网浏览器、游戏、视频等的应用。应用处理器810可包括控制易失性存储器装置850的存储器控制器(mct)812。

143.连接件820可执行与外部装置的无线通信或有线通信。

144.易失性存储器装置850可存储由应用处理器810处理的数据,或者可用作工作存储器。易失性存储器装置850可包括存储器单元阵列mca852、行故障检测器854和标志生成器856。易失性存储器装置850可被实现为参照图1至图16描述的存储器装置。因此,存储器控制器812可监测故障行地址。

145.非易失性存储器装置840可存储用于启动移动系统800的启动镜像(boot image)。

146.用户接口830可包括一个或多个输入装置(诸如,小键盘和触摸屏)和/或一个或多个输出装置(诸如,扬声器和显示装置)。电源860可供应移动系统800的操作电压。

147.移动系统800或移动系统800的组件可使用各种形式的封装来实现。

148.通过总结和回顾,制造工艺规模的减小可导致增加的误码率和降低的良率。

149.如上所述,实施例可提供可靠性被提高的存储器装置和存储器系统。

150.在此已经公开了示例实施例,尽管采用了特定术语,但是它们仅在一般和描述性意义上被使用和解释,而不是出于限制的目的。在一些情况下,如本领域普通技术人员在提交本技术时将清楚的,除非另有具体说明,否则结合特定实施例描述的特征、特性和/或元件可单独使用或与结合其它实施例描述的特征、特性和/或元件组合使用。因此,本领域技术人员将理解,在不脱离如所附权利要求中阐述的本发明的精神和范围的情况下,可在形式和细节上进行各种改变。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1