包含支撑结构的存储器装置的制作方法

1.本文中描述的实施例涉及存储器装置,所述存储器装置包含位于存储器装置的阶梯区域处的支撑结构。

背景技术:

2.存储器装置(例如,快闪存储器装置)中的部件的结构的尺寸相对较小(例如,为纳米大小)。在某个尺寸下,存储器装置的一些结构可能在存储器装置的制造期间发生塌陷。一些常规技术使用附加的化学处理步骤来防止此塌陷。然而,附加步骤可能增加制造存储器装置的成本。

技术实现要素:

3.本公开的一个方面提供了一种设备,其包括:衬底;层面,所述层面在所述衬底上方彼此上下叠放,所述层面包含相应的存储器单元和用于所述存储器单元的控制栅极,所述控制栅极包含最靠近所述衬底的控制栅极而非其它控制栅极,所述控制栅极包含共同形成阶梯结构的相应部分;导电触点,所述导电触点在所述阶梯结构的位置处与所述控制栅极接触,所述导电触点具有从所述衬底竖直延伸的不同长度,所述导电触点包含与第一控制栅极接触的导电触点;介电结构,所述介电结构邻近所述层面的所述控制栅极的侧壁;以及支撑结构,所述支撑结构邻近所述导电触点并且与所述控制栅极和所述导电触点电分离,所述支撑结构具有从所述衬底竖直延伸并延伸穿过所述控制栅极的至少一部分的长度,所述支撑结构包含最靠近所述导电触点的支撑结构而非其它支撑结构,所述支撑结构位于距所述介电结构的边缘一定距离处,其中,所述支撑结构的宽度与所述距离的比率在从1.6至2.0的范围内。

4.本公开的另一方面提供了一种设备,其包括:衬底;层面,所述层面在所述衬底上方彼此上下叠放,所述层面包含相应的存储器单元和用于所述存储器单元的控制栅极,所述控制栅极包含最靠近所述衬底的控制栅极而非其它控制栅极,所述控制栅极包含共同形成阶梯结构的相应部分;导电触点,所述导电触点在所述阶梯结构的位置处与所述控制栅极接触,所述导电触点具有从所述衬底竖直延伸的不同长度,所述导电触点包含与第一控制栅极接触的导电触点;以及支撑结构,所述支撑结构邻近所述导电触点并且与所述控制栅极和所述导电触点电分离,所述支撑结构具有从所述衬底竖直延伸并延伸穿过所述控制栅极的至少一部分的长度,所述支撑结构包含最靠近所述导电触点的支撑结构而非其它支撑结构,其中,所述支撑结构的宽度是至少345纳米。

5.本公开的另一方面提供了一种设备,其包括:衬底;层面,所述层面在所述衬底上方彼此上下叠放,所述层面包含相应的存储器单元和用于所述存储器单元的控制栅极,所述控制栅极包含最靠近所述衬底的控制栅极而非其它控制栅极,所述控制栅极包含共同形成阶梯结构的相应部分;导电触点,所述导电触点在所述阶梯结构的位置处与所述控制栅极接触,所述导电触点具有从所述衬底竖直延伸的不同长度,所述导电触点包含与所述控

制栅极接触的导电触点;支撑结构,所述支撑结构邻近所述导电触点并且与所述控制栅极和所述导电触点电分离,所述支撑结构具有从所述衬底竖直延伸并延伸穿过所述控制栅极的至少一部分的长度,所述支撑结构包含最靠近所述导电触点的支撑结构而非其它支撑结构;以及介电结构,所述介电结构邻近所述控制栅极的侧壁,其中,所述介电结构的边缘与所述支撑结构的边缘之间的距离小于215纳米。

6.本公开的另一方面提供了一种标线,其包括:第一边缘和与所述第一边缘相对的第二边缘;第一图案,所述第一图案紧邻所述第一边缘,所述第一图案包含平行于所述第一边缘的第一侧和连接到所述第一侧并垂直于所述第一边缘的第二侧,所述第二侧具有在从345纳米至375纳米的范围内的尺寸;以及第二图案,所述第二图案紧邻所述第二边缘,所述第二图案包含平行于所述第二边缘的第一侧和连接到所述第二图案的所述第一侧并垂直于所述第二边缘的第二侧,所述第二图案的所述第二侧具有在从345纳米至375纳米的范围内的尺寸,其中,所述标线被配置为包含在用于形成存储器装置的支撑结构的系统中,使得所述支撑结构的尺寸基于所述第一图案和所述第二图案的尺寸,所述支撑结构位于位于所述存储器装置的衬底上方的阶梯结构中的一个阶梯结构处,所述阶梯结构相对于其它阶梯结构的位置位于最靠近所述衬底的位置。

7.本公开的另一方面提供了一种方法,其包括:在存储器装置的衬底上方形成阶梯结构,所述阶梯结构包含第一阶梯结构和第二阶梯结构,所述第一阶梯结构相对于所述第二阶梯结构最靠近所述衬底;形成与所述阶梯结构的相应的导电材料层级接触的导电触点,所述导电触点具有从所述衬底竖直延伸的不同长度,所述导电触点包含与所述导电材料层级中的导电材料层级接触的导电触点;以及形成支撑结构,所述支撑结构邻近所述导电触点并且与所述导电材料层级和所述导电触点电分离,所述支撑结构具有从所述衬底竖直延伸并延伸穿过所述导电材料层级的至少一部分的长度,所述支撑结构包含最靠近所述导电触点的支撑结构而非其它支撑结构,其中,所述支撑结构的宽度是至少345纳米。

附图说明

8.图1示出了根据本文描述的一些实施例的呈存储器装置形式的设备。

9.图2示出了根据本文描述的一些实施例的呈具有存储器单元阵列和存储器单元块的存储器装置形式的设备的示意图。

10.图3示出了根据本文描述的一些实施例的图2的存储器装置的结构的俯视图,所述结构包含存储器单元阵列、阶梯区域和存储器单元块之间的介电结构。

11.图4a示出了图3的存储器装置的一部分(例如,横截面)。

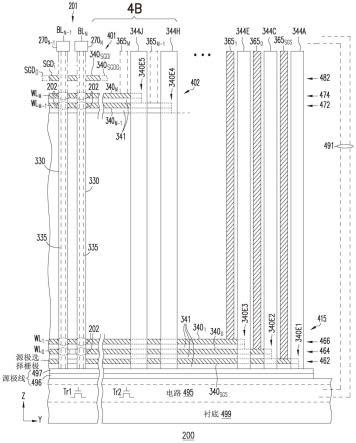

12.图4b示出了图4a的存储器装置的一部分的更多细节。

13.图4c示出了图4b的存储器装置200的一部分的俯视图。

14.图5a、图5b和图5c是示出根据本文描述的一些实施例的图3的存储器装置的不同部分的俯视图的代表图。

15.图6a至图10c是示出根据本文描述的一些实施例在形成图2至图5c的存储器装置的工艺期间的不同结构视图的代表图。

16.图11示出了根据本文描述的一些实施例的被配置为包含在用于形成图6a至图10c的存储器装置的一部分的系统中的标线。

17.图12示出了根据本文描述的一些实施例的包含光刻装备的系统,所述光刻装备包含图11的标线。

具体实施方式

18.本文描述的技术涉及一种存储器装置,除了其它结构之外,所述存储器装置尤其具有阶梯结构和位于阶梯结构处的支撑结构。支撑结构具有特定尺寸(例如,宽度)和与其它结构的特定尺寸关系(例如,比率)。这些特定尺寸和尺寸关系可以防止存储器装置的一些结构在形成存储器装置的工艺期间潜在地塌陷。本文描述的技术还涉及一种标线,所述标线可以被配置为在形成所描述的存储器装置的支撑结构的工艺的一部分期间包含在系统(例如,光刻系统)中。标线被设计成包含图案,使得支撑结构的特定尺寸可以基于标线的图案的尺寸。标线的图案的尺寸被设计(例如,确定),使得支撑结构(其尺寸基于标线的图案的尺寸)可以防止存储器装置的其它结构在形成存储器装置的工艺期间塌陷。下面参考图1至图12进一步讨论本文描述的技术的改进和益处。

19.图1示出了根据本文描述的一些实施例的呈存储器装置100形式的设备。存储器装置100可以包含存储器阵列(或多个存储器阵列)101,其含有以块(存储器单元块)(诸如块191和192)布置的存储器单元102。在存储器装置100的物理结构中,存储器单元102可以竖直地布置在存储器装置100的衬底(例如,半导体衬底)上方(例如,彼此堆叠)。图1将具有两个块191和192的存储器装置100示出为实例。存储器装置100可以具有两个以上的块。

20.如图1所示,存储器装置100可以包含存取线(其可以包含字线)150和数据线(其可以包含位线)170。存取线150可以携带信号(例如,字线信号)wl0至wlm。数据线170可以携带信号(例如,位线信号)bl0至bln。存储器装置100可以使用存取线150来选择性地存取块191和192的存储器单元102,并使用数据线170来选择性地与存储器单元102交换信息(例如,数据)。

21.存储器装置100可以包含地址寄存器107以接收线(例如,地址线)103上的地址信息(例如,地址信号)addr。存储器装置100可以包含可以对来自地址寄存器107的地址信息进行解码的行存取电路108和列存取电路109。基于解码后的地址信息,存储器装置100可以确定在存储器操作期间将存取块191和192的哪些子块的哪些存储器单元102。存储器装置100可以包含驱动器(驱动器电路)140,所述驱动器可以是行存取电路108的一部分。驱动器140可以操作(例如,作为开关操作)以在存储器装置100的操作期间在提供电压的节点与相应的存取线150之间形成(或不形成)导电路径(例如,电流路径)。

22.存储器装置100可以执行读取操作以从块191和192的存储器单元102读取(例如,感测)信息(例如,先前存储的信息),或执行写入(例如,编程)操作以将信息存储(例如,编程)到块191及192的存储器单元102中。存储器装置100可以使用与信号bl0至bln相关联的数据线170来提供要存储在存储器单元102中的信息或获得从存储器单元102读取(例如,感测)的信息。存储器装置100还可以执行擦除操作以从块191和192的存储器单元102中的一些或全部擦除信息。

23.存储器装置100可以包含控制单元118,所述控制单元可以被配置为基于线104上的控制信号来控制存储器装置100的存储器操作。线104上的控制信号的实例包含一或多个时钟信号和其它信号(例如,芯片启用信号ce#、写入启用信号we#)以指示存储器装置100可

以执行哪个操作(例如,读取、写入或擦除操作)。存储器装置100外部的其它装置(例如,存储器控制器或处理器)可以控制线104上的控制信号的值。线104上的信号的组合的特定值可以产生命令(例如,读取、写入或擦除命令),所述命令可导致存储器装置100执行对应的存储器操作(例如,读取、写入或擦除操作)。

24.存储器装置100可以包含感测和缓冲电路120,其可以包含诸如感测放大器及页缓冲电路(例如,数据锁存器)等部件。感测和缓冲电路120可以对来自列存取电路109的信号bl_sel0至bl_seln作出响应。感测和缓冲电路120可以被配置为(例如,通过感测)确定从块191和192的存储器单元102(例如,在读取操作期间)读取的信息的值,并将信息的值提供给线(例如,全局数据线)175。感测和缓冲电路120还可以被配置为基于线175上(例如,在写入操作期间)的信号的值(例如,电压值)使用线175上的信号来确定块190和191的存储器单元102中(例如,在写入操作期间)要存储(例如,编程)的信息的值。

25.存储器装置100可以包含输入/输出(i/o)电路117以在块191和192的存储器单元102与线(例如,i/o线)105之间交换信息。线105上的信号dq0至dqn可以表示从块191和192的存储器单元102读取或存储在其中的信息。线105可以包含存储器装置100内的节点或存储器装置100可以驻留于其中的封装上的引脚(或焊球)。存储器装置100外部的其它装置(例如,存储器控制器或处理器)可以通过线103、104和105与存储器装置100进行通信。

26.存储器装置100可以接收电源电压,包含电源电压vcc和vss。电源电压vss可以在接地电位(例如,具有约零伏的值)下操作。电源电压vcc可以包含从诸如电池或交流到直流(ac-dc)转换器电路等外部电源提供给存储器装置100的外部电压。

27.存储器单元102中的每一者可以被编程为存储表示至多一位(例如,单个位)的值或多个位的值(例如,两个、三个、四个或另一数量的位)的信息。例如,存储器单元102中的每一者可以被编程为存储表示单个位的二进制值“0”或“1”的信息。每个单元的单个位有时被称为单级单元。在另一实例中,存储器单元102中的每一者可以被配置为存储表示多个位的值的信息,诸如两个位的四个可能值“00”、“01”、“10”和“11”中的一者、三个位的八个可能值“000”、“001”、“010”、“011”、“100”、“101”、“110”和“111”中的一者,或另一数量的多个位的其它值中的一者。具有存储多个位的能力的单元有时被称为多级单元(或多态单元)。

28.存储器装置100可以包含非易失性存储器装置,并且存储器单元102可以包含非易失性存储器单元,使得存储器单元102可以在电力(例如,电压vcc、vss或两者)与存储器装置100断开时保留存储于其上的信息。例如,存储器装置100可以是快闪存储器装置,诸如nand快闪(例如,3维(3d)nand)或nor快闪存储器装置,或另一类型的存储器装置,诸如可变电阻存储器装置(例如,相变存储器装置或电阻式随机存取存储器(ram)装置)。

29.本领域技术人员可以认识到,存储器装置100可以包含其它部件,其中的若干部件未在图1中示出,以免混淆本文描述的实例实施例。存储器装置100的至少一部分可以包含与下文参考图2至图12描述的存储器装置中的任一者的结构类似于或等同的结构并执行与所述存储器装置中的任一者的操作类似于或等同的操作。

30.图2示出了根据本文描述的一些实施例的呈具有存储器单元阵列201以及块(例如,存储器单元块)291和292的存储器装置200的形式的设备的示意图。存储器装置200可以包含非易失性(例如,nand快闪存储器装置)或其它类型的存储器装置。存储器装置200可以对应于存储器装置100。例如,存储器阵列(或多个存储器阵列)201以及块291和292可以分

别对应于图1的存储器装置100的存储器阵列101以及块191和192。

31.如图2所示,存储器装置200可以包含存储器单元202、数据线2700至270n(2700至270n)、块291中的控制栅极2500至250m以及块292中的控制栅极250'0至250'm。数据线2700至270n可以对应于图1的存储器装置100的数据线170的一部分。在图2中,紧邻数字(例如,270n)的标签“n”(索引n)表示存储器装置200的数据线的数量。例如,如果存储器装置200包含16条数据线,则n是15(数据线2700至270

15

)。在图2中,紧邻数字(例如,250m)的标记“m”(索引n)表示控制栅极存储器装置200的数量。例如,如果存储器装置200包含128个控制栅极,则m是127(控制栅极2500至250

127

)。存储器装置200可以在存储器装置200的块(例如,块291和292)中具有相同数量的控制栅极(例如,m-1个控制栅极)。

32.在图2中,数据线2700至270n可以包含存储器装置200的位线(例如,局部位线)(或可以为其一部分)。如图2所示,数据线2700至270n可以分别携带信号(例如,位线信号)bl0至bln。在存储器装置200的物理结构中,数据线2700至270n可以被结构化为导电线并且具有在y方向上延伸的相应长度。

33.如图2所示,存储器单元202可以被组织成分离的块(存储器单元的块),诸如块291和292。图2将包括两个块291和292的存储器装置200示出为实例。然而,存储器装置200可以包含许多块。存储器装置200的块(例如,块291和292)可以共享数据线(例如,数据线2700至270n)以携带从存储器装置200的选定存储器单元(例如,块291或292中的选定存储器单元)的存储器单元读取或存储在其中的信息(呈信号形式)。

34.控制栅极2500至250m可以是局部字线的一部分,所述局部字线可以是存储器装置200的可以与图1的存储器装置100的存取线150相对应的存取线(例如,全局字线)的一部分(或可以耦合到所述存取线)。控制栅极250'0至250'm可以是其它局部字线的另一部分,所述局部字线可以是存储器装置200的存取线(例如,全局字线)的一部分。控制栅极2500至250m可以与控制栅极250'0至250'm电分离。因此,可以分别存取块291和292(例如,一次存取一个)。例如,可以使用控制栅极2500至250m在一个时间存取块291,并且可以使用控制栅极250'0至250'm在另一个时间存取块292。

35.图2示出了可以相对于存储器装置200的结构的物理方向(例如,尺寸)的方向x、y和z。例如,z方向可以是垂直于存储器装置200的衬底(例如,图4a所示的衬底499)的方向(例如,相对于所述衬底竖直的方向)。z方向垂直于x方向和y方向(例如,z方向垂直于存储器装置200的x-y平面)。在存储器装置200的物理结构中,控制栅极2500至250m可以在z方向上形成于存储器装置200的不同层级(例如,层)上。在此实例中,控制栅极2500至250m的层级(例如,层)可以在z方向上将一个层级(一层材料)形成(例如,堆叠)于另一层级上。

36.如图2所示,存储器单元202可以包含在存储器装置200的块(例如,块291及292)中的每一者中的相应存储器单元串230中。存储器单元串230中的每一者可以在z方向上具有串联连接的存储器单元(例如,m+1个串联连接的存储器单元)。在存储器装置200的物理结构中,可以在存储器装置200的z方向上以不同层级(例如,图2的实例中的m-1个不同层)形成(例如,彼此竖直堆叠)存储器单元串230中的每一者中的存储器单元202。串230中的每一者中的存储器单元的数量可以等于存储器装置200的控制栅极(例如,控制栅极2500至250m)的层级(例如,层)的数量。

37.如图2所示,控制栅极2500至250m可以携带对应的信号wl0至wlm。如上所述,控制栅

极2500至250m可以包含存储器装置200的存取线(例如,字线)(或可以是其一部分)。控制栅极2500至250m中的每一者可以是位于存储器装置200的层级中的导电材料(例如,导电材料层)的结构(例如,层级)的一部分。存储器装置200可以在操作(例如,读取、写入或擦除操作)期间使用信号wl0至wlm来选择性地控制对块291的存储器单元202的存取。例如,在读取操作期间,存储器装置200可以使用信号wl0至wlm来控制对块291的存储器单元202的存取以从块291的存储器单元202读取(例如,感测)信息(例如,先前存储的信息)。在另一实例中,在写入操作期间,存储器装置200可以使用信号wl0至wlm来控制对块291的存储器单元202的存取以将信息存储在块291的存储器单元202中。

38.如图2所示,控制栅极250'0至250'm可以携带对应的信号wl'0至wl'm。控制栅极250'0至250'm中的每一者可以是位于存储器装置200的单层级中的导电材料(例如,导电材料层)的结构(例如,层级)的一部分。控制栅极250'0至250'm可以分别位于与控制栅极2500至250m相同的层级(在z方向上)。如上所述,控制栅极250'0至250'm(例如,局部字线)可以与控制栅极2500至250m(例如,其它局部字线)电分离。

39.存储器装置200可以在操作(例如,读取、写入或擦除操作)期间使用信号wl'0至wl'm来分别控制对块292的存储器单元202的存取。例如,在读取操作期间,存储器装置200可以使用信号wl'0至wl'm来控制对块292的存储器单元202的存取以从块292的存储器单元202读取(例如,感测)信息(例如,先前存储的信息)。在另一实例中,在写入操作期间,存储器装置200可以使用信号wl'0至wl'm来控制对块292的存储器单元202的存取以将信息存储在块292的存储器单元202中。

40.如图2所示,同一块中的不同存储器单元串中的存储器单元可以共享所述块中的同一控制栅极(例如,可以由其控制)。例如,在块291中,耦合到控制栅极2500的存储器单元202可以共享控制栅极2500(可以由其控制)。在另一实例中,耦合到控制栅极2501的存储器单元202可以共享控制栅极2501(可以由其控制)。在另一实例中,在块292中,耦合到控制栅极250'0的存储器单元202可以共享控制栅极250'0(可以由其控制)。在另一实例中,耦合到控制栅极250'1的存储器单元202可以共享控制栅极250'1(可以由其控制)。

41.存储器装置200可以包含可以携带信号(例如,源极线信号)sl的源极(例如,源极线、源极板或源极区域)298。源极298可以被结构化为存储器装置200的导电线或导电板(例如,导电区域)。源极298可以是块291和292的公共源极线(例如,公共源极板或公共源极区域)。源极298可以耦合到存储器装置200的接地连接。

42.存储器装置200可以包含选择晶体管(例如,漏极选择晶体管)2610至261i(261

0-261i)和选择栅极(例如,漏极选择栅极)2810至281i。晶体管2610可以共享同一选择栅极2810。晶体管261i可以共享同一选择栅极281i。选择栅极2810至281n可以分别携带信号sgd0至sgdi。

43.晶体管2610至261i可以分别由信号sgd0至sgdi控制(例如,接通或关断)。在存储器装置200的存储器操作(例如,读取或写入操作)期间,晶体管2610至261i可以接通(例如,通过激活相应信号sgd0至sgdi)以将块291的存储器单元串230耦合到相应数据线2700至270n。晶体管2610至261i可以关断(例如,通过停用相应信号sgd0至sgdi)以将块291的存储器单元串230与相应数据线2700至270n解耦。

44.存储器装置200可以包含晶体管(例如,源极选择晶体管)260,其中的每一者可以

耦合在块291的相应存储器单元串(存储器单元串230中的一者)中的源极298与存储器单元202之间。存储器装置200可以包含选择栅极(例如,源极选择栅极)280。晶体管260可以共享选择栅极280。晶体管260可以由提供在选择栅极280上的相同信号(诸如sgs信号(例如,源极选择栅极信号))控制(例如,接通或关断)。在存储器装置200的存储器操作(例如,读取或写入操作)期间,晶体管260可以接通(例如,通过激活sgs信号)以将块291的存储器单元串耦合到源极298。晶体管260可以关断(例如,通过停用sgs信号)以将块291的存储器单元串与源极298解耦。

45.存储器装置200可以在块292中包含类似的选择栅极和选择晶体管。例如,在块292中,存储器装置200可以包含选择栅极(例如,漏极选择栅极)281'0至281'i和晶体管(例如,漏极选择晶体管)2610至261i。块291的晶体管2610可以共享同一选择栅极281'0。块292的晶体管261i可以共享同一选择栅281'i。选择栅极281'0至281'i可以分别携带信号sgd0'至sgdi'。

46.块292的晶体管2610至261i可以分别由信号sgd0'至sgdi'控制(例如,接通或关断)。在存储器装置200的存储器操作(例如,读取或写入操作)期间,块292的晶体管2610至261i可以接通(例如,通过激活相应信号sgd0'至sgdi')以将块292的存储器单元串耦合到数据线2700至270n。块292的晶体管2610至261i可以关断(例如,通过停用相应信号sgd0'至sgdi')以将块292的存储器单元串与相应组数据线2700至270n解耦。

47.存储器装置200可以包含晶体管(例如,源极选择晶体管)260,其中的每一者可以耦合在源极298与块292的相应存储器单元串中的存储器单元之间。块292的晶体管260可以共享存储器装置200的同一选择栅极(例如,源极选择栅极)280'。块292的晶体管260可以由提供在选择栅极280'上的相同信号(诸如sgs'信号(例如,源极选择栅极信号))控制(例如,接通或关断)。在存储器装置200的存储器操作(例如,读取或写入操作)期间,块292的晶体管260可以接通(例如,通过激活sgs'信号)以将块292的存储器单元串耦合到源极298。块292的晶体管260可以关断(例如,通过停用sgs'信号)以将块292的存储器单元串与源极298解耦。图2将电分离的选择栅极280和280'示出为实例。替代地,选择栅极280和280'可以彼此电耦合。

48.存储器装置200包含图2中未示出的其它部件,以免混淆本文描述的实例实施例。下文参考图2至图12描述存储器装置200的一些结构。为了简单起见,不再重复附图(图1至图12)中的相同元件的详细描述。

49.图3示出了根据本文描述的一些实施例的存储器装置200的结构的俯视图,所述存储器装置包含存储器单元阵列201、阶梯区域345和346、块290、291、292和293之间的介电结构351a、351b、351c、351d和351e。在本文的附图(图式)中,图2和其它附图(例如,图3至图12)的存储器装置200的类似或相同元件被给予相同标签。它们的详细描述和功能在附图之间重复。为了简单起见,在本文所述的附图中示出的一些或全部元件中省略了截面线(例如,阴影线)。可以从图式的特定附图中省略存储器装置200的一些元件,以免混淆所述特定图中所描述的元件(或多个元件)的视图或描述。此外,本文所述的图式中所示的元件的尺寸(例如,物理结构)未按比例绘制。

50.如图3所示,存储器装置200的块(存储器单元块)290、291、292和293(290至293)可以并排定位在x方向上。将四个块290至293示出为实例。存储器装置200可以包含多个块。图

3的块291和292在上面参考图2被示意性地示出和描述。存储器装置200的其它块(例如,块290和293)未在图2中示出。

51.存储器装置的介电结构351a、351b、351c、351d和351e可以具有在块290至293之间沿y方向延伸的长度。每个介电结构351a、351b、351c、351d和351e可以包含狭缝(例如,在z方向上具有深度的沟槽)和形成(例如,填充)于狭缝中的介电材料(或多种介电材料)。介电结构351a、351b、351c、351d和351e可以将一个块与另一块电分离。例如,介电结构351b可以将块291与块290电分离,而介电结构351c可以将块291与块292电分离。相邻块的控制栅极和选择栅极可以通过相邻块之间的介电结构彼此电分离。例如,控制栅极2500至250m和选择栅极280和2810到281i(图2)可以通过介电结构351c与控制栅极250'0至250'm和选择栅极280'和281'0至281'i(图2)电分离。

52.存储器装置200可以包含耦合到相应数据线数据线2700至270n的块290、291、292和293中的支柱330。存储器单元串的存储器单元202可以沿着对应支柱330的长度(图4a所示)的长度定位(例如,可以沿着长度竖直地形成)。

53.如图3所示,存储器装置200的数据线2700至270n(与信号bl0至bln相关联)可以位于存储器单元阵列201上方并且可以具有沿x方向延伸的长度。数据线2700至270n可以延伸在块290至293上方(例如,在其顶部上)和延伸跨过所述块(在x方向上),并且可以由块290至293共享。数据线2700至270n可以耦合到相应支柱330(所述支柱在z方向上位于数据线2700至270n下方)。

54.存储器装置200的阶梯区域345及346可以位于存储器单元阵列201的相应侧上(在y方向上)。阶梯区域345及346可以包含导电触点以提供与存储器装置200的相应块290、291、292和293中的选择栅极和控制栅极(例如,图2的选择栅极280、2810和281i以及控制栅极2500至250m)的电连接(例如,向其提供信号)。阶梯区域345和346可以包含类似结构。然而,为了简单起见并且在本文的描述中在图3中省略了阶梯区域346的细节。在存储器装置200的替代实施例(例如,替代结构)中,可以从存储器装置200中省略阶梯区域346,使得仅阶梯区域345(而非阶梯区域345和346两者)包含在存储器装置200中。

55.如图3所示,在块291中,存储器装置200可以包含支撑结构344a至344l和存储器装置200的相应部分5a、5b和5c中的导电触点(仅标记导电触点3651、365m和365

sgdi

)。为了简单起见,图3没有给出块290至293的其它支撑结构和其它导电触点的标签。图3的存储器装置200的部分5a、5b和5c分别在图5a、5b和5c中更详细地示出。在图3中,线4a-4a示出了图4a所示的存储器装置200的一部分(例如,横截面)的位置。

56.如图3所示,存储器装置200可以包含块291中的导电材料340

sgs

、3400、3401、340

m-1

、340m、340

sgd0

和340

sgdi

,其可以分别形成图2的选择栅极280、控制栅极2500至250m以及选择栅极2800和280i(形成其材料)。导电材料340

sgd0

和340

sgdi

可以通过间隙347(其可以填充有一种(或多种)介电材料)而彼此电分离。为了简单起见,图3未给出形成块290、292和291的选择栅极和控制栅极的其它导电材料的标签。

57.图4a示出了沿着图3的线4a-4a示出的存储器装置200的一部分(例如,横截面)。如图4a所示,存储器装置200可以包含层级462、463、464、472、474和482,所述层级可以是存储器装置200的z方向上的物理层(例如,部分)。导电材料340

sgs

、3400、3401、340

m-1

、340m、340

sgd0

和340

sgdi

可以沿z方向上在层级462、463、464、472、474和482中一个层级(例如,一层)

在另一层级上方地定位(例如,堆叠)。导电材料340

sgd0

和340

sgdi

可以位于同一层级(例如,层级482)上。导电材料340

sgs

、3400、3401、340

m-1

、340m和340

sgdi

可以称为导电材料340

sgs

、3400、3401、340

m-1

、340m和340

sgdi

的层级。

58.如图4a所示,导电材料340

sgs

、3400、3401、340

m-1

、340m和340

sgdi

可以在z方向上与介电材料341交错。导电材料340

sgs

、3400、3401、340

m-1

、340m和340

sgdi

可以包含金属(例如,钨或其它金属)、其它导电材料或导电材料的组合。介电材料341可以包含二氧化硅。

59.与图4a中的相应导电材料相关联的图4a中的信号sgs、wl0、wl1、wl

m-1

、wlm、sgd0和sgdi与图2中所示的信号相同。导电材料340

sgs

可以形成图2的选择栅极280(与信号sgs相关联)。导电材料3400、3401、340

m-1

和340m可以形成图2的控制栅极2500至250m(分别与信号wl0、wl1、wl

m-1

和wlm相关联)。导电材料340

sdg0

和340

sgdi

(与信号sgd0和sgdi相关联)可以分别形成图2的选择栅极2800及280i。

60.如图4a所示,导电材料3400(其形成与信号wl0相关联的控制栅极2500)可以相对于形成存储器装置200的其它控制栅极2501至250m(与信号wl

m-1

和wlm相关联)的其它导电材料3401、340

m-1

和340m最靠近(在z方向上)衬底499。

61.图4a示出了存储器装置200的实例,所述存储器装置包含形成选择栅极(例如,与信号sgs相关联的源极选择栅极)的导电材料340

sgs

的一个层级。然而,存储器装置200可以包含位于导电材料3401的层级下方(在z方向上)(例如,在层级464下方)的多个导电材料层级(例如,导电材料340

sgs

的多个层级)以形成存储器装置200的多个源极选择栅极。

62.图4a示出了存储器装置200的实例,所述存储器装置包含形成选择栅极(例如,与信号sgd0相关联的漏极选择栅极)的导电材料340

sgd0

的一个层级和形成选择栅极(例如,与信号sgdi相关联的漏极选择栅极)的导电材料340

sgdi

的一个层级。然而,存储器装置200可以在导电材料340m的层级上方(例如,在层级474上方)(在z方向上)包含多个导电材料层级(例如,导电材料340

sgd0

的多个层级)以形成类似于与存储器装置200的信号sgd0相关联的选择栅极的多个漏极选择栅极。类似地,存储器装置200可以在导电材料340m的层级上方(例如,在层级474上方)(在z方向上)包含多个导电材料层级(例如,导电材料340

sgdi

的多个层级)以形成类似于与存储器装置200的信号sgdi相关联的选择栅极的多个漏极选择栅极。

63.如图4a所示,存储器装置200可以包含位于阶梯区域345(图3)中的阶梯结构415、402和401。导电材料340

sgs

、3400和3401的相应部分(例如,末端部分)及其在位置340e1、304e2和340e3处的相应边缘(例如,台阶)可以共同形成阶梯结构415。导电材料340

m-1

和340m的相应部分(例如,末端部分)及其在位置340e4和304e5处的相应边缘(例如,台阶)可以共同形成阶梯结构402。导电材料340

sdg1

的一部分(例如,末端部分)及其在位置340e6处的边缘(例如,台阶)(图4b中所示)可以形成阶梯结构401。本文的描述给出了包含在特定阶梯结构中的边缘(例如,位置340e1至340e6处的边缘)的实例数量。然而,每个阶梯结构可以包含一个以上的边缘,并且可以包含与图4a所示的边缘不同的数个边缘。

64.为了简单起见,图4a省略了阶梯结构402和415之间的其它阶梯结构。存储器装置200可以包含多达15个阶梯结构。替代地,存储器装置200可以包含15个以上的阶梯结构。

65.如图4a所示,阶梯结构415可以相对于阶梯结构(例如,阶梯结构401和402,以及阶梯结构402和415之间的阶梯结构(未示出))中的其它阶梯结构的位置(在z方向上)而位于最靠近(在z方向上)衬底499的位置。

66.在图4a中,一个层级的导电材料(例如,导电材料3401)和相邻层级的介电材料341(例如,导电材料3400与3401之间的介电材料341)可以称为存储器装置200的层面。如图4a所示,这些层面可以在衬底499上方在z方向上彼此上下叠放(例如,堆叠)。图4a示出了用于每个阶梯结构的特定数量的层面(和对应边缘)和对应数量的层面(例如,用于阶梯结构415的三个层面)的实例。然而,存储器装置200的每个阶梯结构可以由与图4a中所示的层面的数量不同的数个层面(和对应边缘)形成。为了简单起见,图4a示出了存储器装置200的若干层面。然而,存储器装置200可以包含多达一百个层面。替代地,存储器装置200可以包含一百个以上的层面。

67.图3的存储器装置200的其它块(例如,块290、292和293)也可以具有其自身的类似于块291的阶梯结构的阶梯结构。为了简单起见,从本文的描述中省略存储器装置200的其它块(例如,块290、292和293)的阶梯结构的细节。

68.如图4a所示,介电材料341还可以包含与相应边缘340e1至340e5相邻(例如,在z方向上对准)的边缘(未标记)。因此,阶梯结构401、402和415也可以部分地由介电材料341的部分和边缘形成。

69.以下描述参考图4a、图4b和图4c。图4b示出了图4a的存储器装置200的一部分的更多细节。图4c示出了图4b的存储器装置200的一部分的俯视图。

70.如图4a和图4c所示,导电材料340

sgd0

和340

sgdi

可以位于同一层级(例如,图4a中的层级482)上并且并排定位(在图4c中的x方向上)。如图4c所示,导电材料340

sgd0

和340

sgdi

(其分别形成选择栅极2810和281i)可以通过间隙347彼此电分离。

71.如图4a和图4b所示,存储器装置200可以包含衬底499和位于衬底499上方(例如,形成于衬底上方)的材料496和497。衬底499可以包含半导体(例如,硅)衬底。衬底499还可以包含电路495,所述电路位于存储器装置200的形成于衬底499上方的其它部件下方。电路495可以包含与衬底499外部的电路元件耦合的电路元件(例如,图4a所示的晶体管tr1和tr2)。例如,衬底499外部的电路元件可以包含数据线2700至270n、导电触点365

sgs

、3651、365m、365

m-1

(图4a)、365

sgdi

(图4b)和365

sgd0

(图4c),以及导电路径491和其它(未图示)导电连接的一部分,以及存储器装置200的其它电路元件。电路495的电路元件(例如,晶体管tr1及tr2)可以被配置为执行存储器装置200的功能的一部分。例如,晶体管tr1和tr2可以是存储器装置200的解码器电路、驱动器电路、缓冲器、感测放大器、电荷泵和其它电路的一部分。

72.如图4a所示,导电路径(例如,导电布线)491可以包含在z方向上延伸(例如,竖直延伸)的部分(区段)。导电路径491可以包含(例如,可以耦合到)存储器装置200的导电触点(例如,导电触点365

sgs

、3650、3651、365m、365

m-1

(图4a)、365

sgdi

(图4b)和365

sgd0

(图4c))中的一些(或全部)。如图4a所示,导电路径491可以耦合到电路495。例如,导电路径491中的至少一者可以耦合到电路495的至少一个晶体管tr1和tr2。

73.导电路径491可以提供导电触点365

sgs

、3650、3651、365m、365

m-1

(图4a)、365

sgdi

(图4b)和365

sgd0

(图4c)与存储器装置200的其它元件之间的电连接。例如,导电路径491可以耦合到导电触点365

sgs

、3650、3651、365m、365

m-1

(图4a)、365

sgdi

(图4b)和365

sgd0

(图4c)以及电路495的电路元件(例如,字线驱动器和字线解码器,未示出),以分别提供从电路495中的电路元件(例如,字线驱动器、字线解码器和电荷泵,未示出)到导电触点365

sgs

、3650、3651、365m、

365

m-1

、365

sgdi

和365

sgd0

的电连接(例如,以信号sgs、wl0、wl1、wl

m-1

、wlm、sgd0和sgdi的形式)。

74.如图4a和图4b所示,导电触点365

sgs

、3650、3651、365m、365

m-1

和365

sgdi

(图4a和图4b的视图中隐藏了导电触点365

sgd0

)可以具有在z方向上延伸(例如,从衬底499竖直地(例如,向外)延伸)的不同长度。每个导电触点365

sgs

、3650、3651、365m、365

m-1

、365

sgd0

和365

sgdi

中的每一者可以接触导电材料340

sgs

、3400、3401、340

m-1

、340m、340

sgd0

和340

sgdi

中的相应层级的导电材料(例如,着陆在其上)以形成与相应层级的导电材料的电触点。因此,导电触点365

sgs

、3650、3651、365m、365

m-1

、365

sgd0

和365

sgdi

可以是导电路径的一部分(例如,导电路径491的一部分)以分别将电信号携带到选择栅极(例如,与信号sgs相关联的源极选择栅极)、控制栅极(例如,与信号wlm和wl

m-1

相关联的控制栅极)和其它选择栅极(例如,与信号sgd0和sgdi相关联的漏极选择栅极)。

75.如图4a所示,导电触点365

sgs

与导电材料340

sgs

电接触,并且与其余的导电材料(例如,导电材料3400、3401、340

m-1

、340m和340

sgdi

)电分离。导电触点3650与导电材料3400电接触并与其余的导电材料(例如,导电材料340

sgs

、3401、340

m-1

、340m和340

sgdi

)电分离。因此,导电触点(例如,导电触点3650)可以仅与存储器装置200的导电材料(例如,导电材料340

sgs

、3400、3401、340

m-1

、340m和340

sgdi

)中的导电材料中的一者电接触。

76.材料496和497(图4a和图4b)是存储器装置200的源极(例如,源极线、源极板或源极区域)298(图2)的一部分。材料496可以包含多晶硅。材料497可以氧化钨。

77.可以形成支撑结构344a到344l以在形成存储器装置200的特定工艺期间向存储器装置200的一部分(例如,阶梯区域345)提供结构支撑,如参考图8a至图10c更详细描述)。

78.如图4a所示,支撑结构344a、344c、344e、344h和344j可以具有在z方向上延伸的相同长度(例如,从衬底499竖直(例如,向外)延伸)。支撑结构344b、344d、344f、344g、344i和344k(图4a和图4b的视图中隐藏)也可以具有与图4a所示的支撑结构344a、344c、344e、344h和344j相同的长度。支撑结构344a至344l可以穿过导电材料340

sgs

、3400、3401、340

m-1

、340m和340

sgdi

的相应部分以及介电材料341。支撑结构344a至344l与导电材料340

sgs

、3400、3401、340

m-1

、340m、340

sgd0

和340

sgdi

电分离。支撑结构344a至344l中的每一者可以接触材料497(例如,着陆在其上)。

79.图5a、图5b和图5c分别示出了根据本文描述的一些实施例的图3的存储器装置200的部分5a、5b和5c的俯视图。如图5a、图5b和图5c所示,导电触点365

sgs

、3650、3651、365m、365

m-1

、365

sgd0

和365

sgdi

可以成组地位于(例如,可以形成于)相应的阶梯结构415、402和401中。例如,该组导电触点365

sgs

、3650和3651可以位于阶梯结构415处并且可以在x方向上具有宽度(例如,直径)w3。该组导电触点365m和365

m-1

可以位于阶梯结构402处,并且可以在x方向上具有宽度(例如,直径)w6。该组导电触点365

sgd0

和365

sgdi

可以位于阶梯结构401处,并且可在x方向上具有宽度(例如,直径)w10。

80.同一组内(位于同一阶梯处)的导电触点可以具有相同宽度。例如,导电触点365

sgs

、3650和3651(位于阶梯结构415处)可以具有相同宽度w3。导电触点365m和365

m-1

(位于阶梯结构402处)可以具有相同宽度w6。导电触点365

sgd0

和365

sgdi

(位于阶梯结构401处)可以具有相同宽度w10。

81.不同组中(位于不同的阶梯处)的导电触点可以具有不同的宽度(不同的尺寸(例如,以纳米为单位的尺寸))。因此,宽度w3、w6和w10可以彼此不同。作为实例,宽度w3可以大

于宽度w6,并且宽度w6可以大于宽度w10。宽度w3、w7和w10中的每一者可小于相应支撑结构344a至344l的宽度w1、w2、w4、w5、w7和w8中的每一者。

82.如图5a、图5b和图5c所示,支撑结构344a至344l可以成组地定位(例如,可以形成)在相应的阶梯结构415、402和401处。如图5a中所示,该组支撑结构344a到344f可以位于阶梯结构415处并且位于相应导电触点365

sgs

、3650和3651附近。支撑结构344a至344f在x方向上可以具有相应宽度(例如,直径)w1和w2。宽度w1和w2可以是相同的(例如,具有相同的纳米尺寸)。

83.如图5b所示,该组支撑结构344g至344j可以位于阶梯结构402处并且位于相应导电触点365

m-1

和365m附近。支撑结构344g至344j可以在x方向上具有相应宽度(例如,直径)w4和w5。宽度w4和w5可以是相同的(例如,具有纳米尺寸)。

84.如图5c所示,该组支撑结构344k和344l可以位于阶梯结构401处,并且位于相应导电触点365

sgd0

和365

sgdi

附近。支撑结构344k和344l可以在x方向上具有相应宽度(例如,直径)w7和w8。宽度w7和w8可以是相同的(例如,具有相同的纳米尺寸)。

85.不同组中的支撑结构(位于不同的阶梯结构处)可以具有不同的宽度(例如,以纳米为单位的不同尺寸)。例如,宽度w1、w4和w7(或宽度w2、w5和w8)可以彼此不同。宽度w1可以小于宽度w4,并且宽度w4可以小于宽度w7。例如,宽度w1可以是360nm(纳米)并且可以具有从345nm至375nm的范围。因此,宽度w1可以是至少345nm并且可以具有高达375nm的尺寸。在另一实例中,宽度w4可以是414nm并且可以具有从399nm至429nm的范围。在另一实例中,宽度w7可以是420nm并且可以具有从405nm至435nm的范围。

86.图5a、图5b和图5c示出了距离d1至d9。距离d1至d9中的每一者可以为存储器装置200的两个邻近元件(两个邻近结构)的边缘之间的最短距离。

87.可以在介电结构351b的边缘(例如侧壁)351b_e1与支撑结构344a的最靠近边缘351b_e1(相对于支撑结构344a的其它部分)的边缘(未标记)或部分(未标记)之间测量距离d1(图5a)。类似地,支撑结构344c和344e中的每一者可以位于距边缘351b_e1距离d1处。介电结构351b包含在x方向上彼此相对的边缘351b_e1和351b_e2。介电结构351b的边缘351b_e1可以是导电材料340

sgs

、3400和3401与介电结构351b的介电材料接触(相交)的位置(例如,y方向上的界面)处的部分。如图5a、5b和5c所示,介电结构351b的边缘351b_e1可以位于导电材料340

sgs

、3400、3401、340

m-1

和340m以及导电材料340

sgd0

的侧壁(未标记)附近(其中3400、3401、340

m-1

、340m形成相应的控制栅极2500至250m)。介电结构351c的边缘351c_e1可以位于导电材料340

sgs

、3400、3401、340

m-1

和340m的其它侧壁(未标记)和导电材料340

sgdi

的侧壁附近。

88.可以在介电结构351c的边缘(例如,侧壁)351c_e1与支撑结构344b的最靠近边缘351c_e1(相对于支撑结构344b的其它部分)的边缘或部分(未标记)之间测量距离d2(图5a)。类似地,支撑结构344d和344f中的每一者可以位于距边缘351c_e1距离d2处。介电结构351b包含在x方向上彼此相对的边缘351c_e2和351c_e1。介电结构351c的边缘351b_c2可以是导电材料340

sgs

、3400和3401与介电结构351c的介电材料接触(相交)的位置(例如,y方向上的界面)处的部分。

89.可以在支撑结构344a和344b的相邻边缘(未标记)之间测量距离d3(图5a)。距离d3可以是支撑结构344a和344b的相应边缘之间的最近距离(在x方向上)。类似地,支撑结构

344c和344d可以彼此分开距离d3。支撑结构344e和344f彼此分开距离d3。

90.可以在介电结构351a的边缘351b_e1与支撑结构344g的最靠近边缘351b_e1(相对于支撑结构344g的其它部分)的边缘或部分(未标记)之间测量距离d4(图5b)。类似地,支撑结构344i可以位于距边缘351b_e1距离d4处。

91.可以在介电结构351c的边缘351c_e1与支撑结构344h的最靠近边缘351c_e1(相对于支撑结构344h的其它部分)的边缘或部分(未标记)之间测量距离d5(图5b)。类似地,支撑结构344j可以位于距边缘351c_e1距离d5处。

92.可以在支撑结构344g和344h的相邻边缘(未标记)之间测量距离d6(图5b)。距离d6可以是支撑结构344g和344h之间的最近距离(在x方向上)。类似地,支撑结构344i和344j分开距离d6。

93.可以在介电结构351a的边缘351b_e1与支撑结构344k的最靠近边缘351b_e1(相对于支撑结构344k的其它部分)的边缘或部分(未标记)之间测量距离d7(图5c)。

94.可以在介电结构351c的边缘351c_e1与支撑结构344l的最靠近边缘351c_e1(相对于支撑结构344l的其它部分)的边缘或部分(未标记)之间测量距离d8(图5c)。

95.可以在支撑结构344k和344l的相邻边缘(未标记)之间测量距离d9(图5c)。距离d9可以是支撑结构344k和344l之间的最近距离(在x方向上)。

96.距离d1、d4和d7(分别在阶梯结构415、402和401处)可以彼此不同。距离d7可以小于距离d4,并且距离d4可以小于距离d1。例如,距离d1可以是203nm并且可以具有从190nm至215nm的范围。因此,距离d1可以小于215nm。在另一实例中,距离d4可以是176nm并且具有从163nm到189nm的范围。在另一实例中,距离d7可以是173nm并且可以具有从160nm至186nm的范围。

97.在不同阶梯结构处的元件之间的距离可以彼此不同。例如,距离d3、d6和d9(分别在阶梯结构415、402和401处)可以彼此不同。距离d9可以小于距离d6,并且距离d6可以小于距离d3。作为实例,距离d3、d6和d9可以分别是214nm、160nm和154nm。在另一实例中,距离d3可以具有从202nm至227nm的范围。因此,距离d3可以小于214nm(并且大于或等于202nm)。

98.在图5a、图5b和图5c中,特定支撑结构的宽度与从所述特定支撑结构的边缘到相应介电结构的边缘的距离的比率(例如,尺寸关系)被表达为为w1/d1、w4/d4和w7/d7。例如,基于上述实例尺寸,比率w1/d1=1.77(其中w1=360并且d1=203)。比率w1/d1可以具有从w1/d1=1.6(其中w1=345并且d1=215)至w1/d1=2.0(其中w1=375并且d1=190)的范围(例如,近似范围)。

99.在形成存储器装置200的工艺期间(下文参考图6a至图10c描述),存储器装置200的特定位置处的一些结构可能发生塌陷(例如,由于静摩擦)。可以通过将存储器装置200的一些元件(例如,支撑结构344a到344l)结构化为具有特定尺寸(例如,临界尺寸)(诸如宽度w1至w10、距离d1至d9的特定尺寸(例如,以纳米为单位))以及宽度与距离的比率来防止此些塌陷,如上文参考图5a、图5b和图5c所描述。防止此些塌陷可以导致改进存储器装置200的良率、可靠性或两者。

100.可以使用下文参考图6a至图10c描述的工艺来形成支撑结构344a到344l(上文参考图3至图5c描述的)。形成支撑结构344a至344l的部分可以包含在下文参考图6a至图10c描述的工艺期间使用标线(例如,掩模)。此标线可以包含下文参考图11描述的标线1100。

101.图6a至图10c示出了根据本文描述的一些实施例的在形成图2至图5c的存储器装置200的工艺期间的不同结构视图。图6a示出了在介电材料(介电材料层级)640与介电材料(介电材料层级)641交替地形成在衬底499上方(例如,以交错方式在衬底499上方相继地形成材料)之后装置200的x方向上的侧视图(例如,截面图)。

102.如图6a所示,导电材料340的层级(例如,单层级)可以具有厚度t1。介电材料641的层级(例如,单层级)可以具有厚度t2。厚度t1可以是32nm并且可以具有从30nm至35nm的范围。厚度t2可以是25nm并且可以具有从22nm至27nm的范围。

103.介电材料640可以包含氮化硅。介电材料641可以包含二氧化硅。如图6a所示,可以形成介电材料640和641,使得介电材料640可以在z方向上分别在层级462、464、466、472、474和482上与介电材料641交错。为了简单起见,图6a省略了层466与472之间的一些介电材料640和641。

104.图6b示出了图6a的存储器装置200的俯视图(例如,x-y平面图)。图6b还示出了阶梯区域345的位置,其中阶梯结构401、402和415(图4a)可以在随后的工艺(例如,与图7相关联的工艺)中形成在阶梯区域345的相应位置中。在图6b中,线6c-6c示出了图6c所示的存储器装置200的一部分(例如,横截面)的位置。

105.如图6c所示,沿y-z方向所示的介电材料640和641的交错形成可以与沿x-z方向所示的介电材料640和641的交错形成(如图6a所示)相同。

106.图7示出了在形成阶梯结构401、402和415之后(在y-z方向上)图6c的存储器装置200。形成阶梯结构401、402和415可以包含去除介电材料640和641的一部分以获得介电材料640和641的其余部分,所述其余部分在位置340e1至340e6处、在层级462、464、466、472和482中的相应层级处具有相应边缘(例如,竖直边缘)。

107.图8a示出了在形成(块292的)支撑结构844和(块291的)支撑结构344b以及狭缝(例如,沟槽)851c之后存储器装置200的侧视图(在x-z方向上,类似于图6a的侧视图)。

108.形成支撑结构344b和844可以包含去除介电材料640和641的部分以在将形成支撑结构344b和844的位置处形成开口(例如,孔),并且然后在开口中形成材料801和802。材料801可以包含材料的组合(例如,不同层)。线8c-8c示出了图8c中详细示出的支撑结构344b的一部分(例如,横截面)。

109.形成狭缝851c(图8a)可以包含去除介电材料640和641的一部分以在狭缝851c的位置处形成开口,使得狭缝851c可以包含边缘(例如,侧壁)851'和851”。边缘851'和851”可以分别对应于图5的边缘351c_e1和351c_e2。如图8a所示,边缘851'和851”中的每一者可以在狭缝851c的位置处包含介电材料640和641的相应侧壁(未标记)(例如,可以由其形成)。狭缝851c可以在形成支撑结构344b和844之后形成。

110.为了简单起见,图8a中仅示出了两个支撑结构344b和844。其它支撑结构(例如,支撑结构344a和344c至344l)可以以与支撑结构344b和844类似的方式形成,并且可以与支撑结构344b和844同时形成(例如,在同一工艺步骤中形成)。

111.图8b示出了在形成支撑结构(仅标记支撑结构334a、344b、344k、344l和844)以及存储器装置200的相应块290、291、292和293之间的狭缝851b、851c和851d之后的存储器装置200。狭缝851b、851c和851d可以分别对应于图3的介电结构351b、351c和351d的相应狭缝。标线(例如,图11的标线1100)可以用于形成块291的支撑结构344a至344l(和其它支撑

结构)的工艺中。其它标线(类似于标线1100)可以用于在存储器装置的其它块(例如,块290、292和293)中形成支撑结构的工艺中。块290、291、292和293的支撑结构可以同时形成(例如,同时使用相同的工艺步骤形成)。

112.如图8c所示,支撑结构344b的材料801可以包含材料801a、810b、801c和801d的组合,所述材料可以一种材料接一种材料(例如,一层接一层)地形成。例如,可以首先形成材料801a,可以在形成材料801a之后形成材料801b,可以在形成材料801b之后形成材料801c,并且可以在形成材料801c之后形成材料801d。可以在形成材料801之后(例如,在形成材料802d之后)形成材料802。材料801a、810b、801c和801d可以分别包含二氧化硅、氮化硅、钛和氮化钛。材料802可以包含金属(例如,钨或其它金属)。

113.存储器装置200的支撑结构(图8a中的支撑结构344b和844,以及未示出的其它支撑结构)可以同时形成(例如,在同一工艺步骤中形成)。然而,如文上参考图5a、图5b和图5c所描述,不同阶梯结构(例如,阶梯结构401、402和415)处的支撑结构可以具有不同的宽度(例如,不同的直径)。可以形成存储器装置200的支撑结构(图8a中的支撑结构344b和844,以及未示出的其它支撑结构)以在形成存储器装置200的特定工艺期间向存储器装置200的部分(例如,阶梯区域345)提供结构支撑。例如,当在形成与图9a相关联的存储器装置200的工艺期间去除介电材料640时,存储器装置200的支撑结构(图8a中的支撑结构344b和844,以及未示出的其它支撑结构)可以向存储器装置200提供结构支撑。

114.图9a示出了在从位置910(图9a)去除(例如,耗尽)介电材料640(图8a)之后的存储器装置200。支撑结构344b和844可以提供结构支撑以防止在形成存储器装置200的工艺期间(例如,在与图9a中的材料640的去除相关联的工艺期间)较高层级的介电材料641下落到较低层级的介电材料641上。

115.图9b示出了实例情况下的存储器装置200,所述实例情况包含介电材料641在狭缝851c的位置处的部分塌陷。如图9b所示,介电材料641的相邻部分可能塌陷,使得介电材料641的相邻部分可以彼此触及(接触)。

116.在厚度t1和t2的某个值处,存储器装置200的一些位置处(例如,在阶梯结构415处)的介电材料641可能发生塌陷(例如,由于静摩擦)。此静摩擦可能由相邻的介电材料641彼此粘附(例如,在经历由表面张力引起的毛细力时)引起,从而导致一些介电材料641像图9b所示的实例情况那样塌陷。塌陷可能导致在后续工艺中在塌陷位置处形成的导电材料(例如,导电材料340

sgs

、3400和3401)彼此短路(例如,电耦合)。此短路可能劣化或破坏存储器装置200的功能。为了防止此塌陷并改进存储器装置200的结构和可靠性,存储器装置200的一些元件可以形成为具有特定尺寸(例如,以纳米为单位的临界尺寸)。例如,如上文参考图5a、图5b和图5c所描述,存储器装置200的宽度(例如,宽度w1至w10)、距离(例如,距离d1至d9)以及宽度与距离的比率可以形成为具有特定尺寸(例如,以纳米为单位的临界尺寸)以防止介电材料641在易于发生此塌陷的位置处(例如,在阶梯结构415处)塌陷。图9a示出了没有此塌陷的介电材料641的实例。

117.图10a示出在形成导电材料(例如,导电材料层)340和介电结构351c之后图9a的存储器装置200。如图10a所示,导电材料340的层级(例如,单层级)可以具有厚度t1'。厚度t1'可以与介电材料640(图8a)的层级的厚度t1相同。例如,厚度t1'可以是32nm并且可以具有从30nm至35nm的范围。

118.可以通过在位置910中填充一种(或多种)材料(图9a)来形成导电材料340。在实例中,导电材料340可以包含单一导电材料,例如,单一金属(例如,钨)。在另一实例中,导电材料340可以包含多种材料(其可以一种材料接一种材料地形成)。多种材料中的一者可以包含导电材料(例如,诸如钨等金属)。例如,导电材料340可以包含氧化铝(alo)、氮化钛(tni)和钨(w)的不同层。导电材料340可以对应于图4a所示的导电材料340

sgs

、3400、3401、340

m-1

、340m、340

sgd0

和340

sgdi

。与图10a中的相应导电材料340相关联的信号sgs、wl0、wl1、wl

m-1

、wlm、sgd0和sgdi与图4a所示的信号相同。介电材料641可以对应于图4a的介电材料341。

119.在与图10a相关联的工艺中,可以通过在狭缝815b(图9a)的位置中填充(例如,沉积)材料1010和1015来形成介电结构351c。材料1010可以包含介电材料(例如,二氧化硅)。材料1015可以包含多晶硅,或替代地,介电材料(例如,二氧化硅或氮化硅)。如图10a所示,可以在介电结构351c的位置处邻近相应材料340和641的侧壁(例如,竖直侧壁)形成(例如,定位)材料1010。

120.图10b示出了图10a的存储器装置200的在介电结构351c处的一部分的俯视图(在x-y方向上)。如图10a和图10b所示,材料1010形成在介电结构351c的两侧上(例如,形成在x方向上的相对侧壁上,未标记)。材料1015可以形成于材料1010的部分(例如,侧壁部分)之间。材料1010和1015可以沿着介电结构351c的长度(在y方向上)形成。

121.图10c示出了包含支撑结构344b、344d、344f、344h、344j和344l(在与图8a相关联的工艺中形成)的图10a的存储器装置200的侧视图(例如,横截面)。图10c的视图中隐藏了其它支撑结构(例如,在与图8a相关联的工艺中形成的支撑结构344b、344d、344f、344g、344i和344k)。在形成存储器装置200的支撑结构(例如,支撑结构344e至344l)之后,可以在存储器装置200的后续工艺中形成导电触点365

sgs

、3651、365m、365

m-1

、365

sgd0

和365

sgdi

(图5a、图5b和图5c)。为了简单起见并且为了不混淆本文描述的实施例,本文不描述完成存储器装置200的后续工艺。

122.图11示出了根据本文描述的一些实施例的标线(例如,掩模)1100。标线1100可以被配置为用于形成图2至图10c的存储器装置200的工艺的一部分中。例如,标线1100可以被配置为在形成存储器装置200的块291(图8b)的支撑结构(例如,支撑结构344a至344l)的工艺期间包含在系统(例如,图12的系统1200)中。

123.如图11所示,标线1100可以包含沿y方向延伸的边缘(例如,侧面)1111和1112,以及边缘1111与1112之间的图案(例如,正方形特征)1144a至1144l。图案1144a可以包含侧面1121和1122。侧面1121和1122可以具有相同尺寸(例如,以nm为单位的尺寸)。如图11所示,图案1144a可以位于边缘1111附近。侧面1121可以平行于边缘1111。侧面1122以一定角度(例如,90度角)连接到侧面1121,并且可以垂直于边缘1111。

124.图案1144b可以包含侧面1131和1132。侧面1131和1132可以具有相同尺寸(例如,以nm为单位的尺寸)。如图11所示,图案1144b可以位于边缘1112附近。侧面1131可以平行于边缘1112。侧面1132以一定角度(例如,90度角)连接到侧面1131,并且可以垂直于边缘1112。

125.标线1100的其它图案(例如,图案1144c至1144l)也可以包含类似于图案1144a和1144b的侧面。可以在存储器装置200(图5a、图5b和图5c)的阶梯结构401、402和415的位置处分别形成支撑结构(例如,支撑结构344a至344l)的工艺期间使用标线1100的相应部分

1101、1102和1115处的图案。

126.图11还(以虚线)示出了存储器装置200的一些结构相对于图案(例如,图案1144a至1144l)的位置。例如,位置351b'和351c'可以分别对应于介电结构351b和351c的位置(图5a、图5b和图5c)。位置365'可以对应于相应导电触点365

sgs

、3650、3651、365m、365

m-1

、365

sgdi

和365

sgd0

的位置(图5a、图5b和图5c)。

127.如图11所示,图案1144a至1144l可以包含相应宽度w1'、w2'、w4'、w5'、w7'和w8'。图案1144a至1144l之间、图案1144a至1144l与相应边缘1111和1112之间的距离由距离d1'至d9'表示。

128.图案1144a至1144l可以分别用于形成存储器装置200的支撑结构344a至344l的工艺(图5a、图5b和图5c)。因此,宽度w1、w2、w4、w5、w7和w8(图5a,图5b及图5c)的尺寸(以nm为单位)可以分别基于标线1100(图11)的宽度w1'、w2'、w4'、w5'、w7'和w8'的尺寸(以nm为单位)。例如,宽度w1'、w2'、w4'、w5'、w7'和w8'(图11)的尺寸可以被确定(例如,选择)为分别与宽度w1、w2、w4、w5、w7和w8(图5a、图5b和图5c)的尺寸相同(或基本相同)。

129.距离d1至d9(图5a、图5b和图5c)的尺寸(以nm为单位)可以分别基于距离d1'至d9'的尺寸。例如,宽度w1'、w2'、w4'、w5'、w7'和w8'的尺寸(以nm为单位)可以被确定(例如,选择)为分别与图5a、图5b和图5c的宽度w1、w2、w4、w5、w7和w8的尺寸相同(或基本相同)。

130.在标线1100中,宽度w1'、w4'和w7'与距离d1'、d4'和d7'的比率(例如,w1'/d1'、w4'/d4'和w7'/d7')可以和宽度w1、w4和w7与距离d1、d4和d7的比率(例如,w1/d1、w4/d4和w7/d7)相同。

131.在形成存储器装置200的支撑结构(例如,支撑结构344a至344l)的工艺中使用标线1100可以允许存储器装置200的支撑结构具有如上文参考图5a、图5b和图5c描述的特定尺寸(以nm为单位)。上文参考图3至图10c描述具有此类特定尺寸(以nm为单位)的存储器装置200的支撑结构(例如,支撑结构344a至344l)的益处和改进。

132.图12示出了根据本文描述的一些实施例的包含光刻装备(例如,步进器)1201和标线1100的系统1200。系统1200可以用于形成存储器装置200的工艺的一部分。例如,光刻装备1201可以用于使光源(未示出)通过标线1100。然后,光刻装备1201的投影透镜(未示出)可以接收光源(在光源通过标线1100之后)并基于光源产生光束1205。投影透镜可以在存储器装置200的支撑结构344a至344l(在图5a、图5b和图5c中详细示出)的形成期间将光束1205投影到晶片1202上,所述支撑结构可以是晶片1202的一部分。支撑结构344a至344l的尺寸(以nm为单元)可以基于标线1100的图案(例如,图案1144a至1144l)的尺寸。上文参考图3至图11描述了支撑结构344a至344l(例如,通过使用系统1200中的标线1100形成)的益处和改进。

133.上文参考图1至图12描述的实施例包含设备和形成所述设备的方法。所述设备中的一者包含衬底;层面,所述层面在所述衬底上方彼此上下叠放,所述层面包含相应的存储器单元和用于所述存储器单元的控制栅极,所述控制栅极包含最靠近所述衬底的控制栅极而非其它控制栅极,所述控制栅极包含共同形成阶梯结构的相应部分;导电触点,所述导电触点在所述阶梯结构的位置处与所述控制栅极接触,所述导电触点具有从所述衬底竖直延伸的不同长度,所述导电触点包含与第一控制栅极接触的导电触点;介电结构,所述介电结构邻近所述层面的所述控制栅极的侧壁;以及支撑结构,所述支撑结构邻近所述导电触点

并且与所述控制栅极和所述导电触点电分离,所述支撑结构具有从所述衬底竖直延伸并延伸穿过所述控制栅极的至少一部分的长度,所述支撑结构包含最靠近所述导电触点的支撑结构而非其它支撑结构,所述支撑结构位于距所述介电结构的边缘一定距离处,其中,所述支撑结构的宽度与所述距离的比率在从1.6至2.0范围内。描述了包含附加设备和方法的其它实施例。

134.在具体实施方式和权利要求中,关于两个或更多个元件(例如,材料)所使用的术语“在

…

上”,一个“在另一个上”是指元件之间(例如,材料之间)有至少一定的接触。术语“在

…

上方”是指元件(例如,材料)紧邻,但可能具有一或多个附加介入元件(例如,材料),使得接触是可能的但不是必需的。“在

…

上”或“在

…

上方”都不意味着如本文使用的任何方向性,除非这样说明。

135.在具体实施方式和权利要求中,由术语

“…

中的至少一者”连接的项目列表可以指所列项目的任何组合。例如,如果列出了项目a和b,则短语“a和b中的至少一者”指仅a;仅b;或a和b。在另一实例中,如果列出项a、b和c,则短语“a、b和c中的至少一者”仅指a;仅b;仅c;a和b(不包含c);a和c(不包含b);b和c(不包含a);或所有a、b和c。项目a可以包含单个元素或多个元素。项目b可以包含单个元素或多个元素。项目c可以包含单个元素或多个元素。

136.在具体实施方式和权利要求中,由术语

“…

中的一者”连接的项目列表可以仅指列表项目中的一者。例如,如果列出项目a和b,则短语“a和b中的一者”指仅a(不包含b)或仅b(不包含a)。在另一实例中,如果列出项a、b和c,则短语“a、b和c中的一者”指仅a;仅b;或仅c。项目a可以包含单个元素或多个元素。项目b可以包含单个元素或多个元素。项目c可以包含单个元素或多个元素。

137.以上描述和附图示出了本发明主题的一些实施例,以使得本领域技术人员能够实践本发明主题的实施例。其它实施例可以包含结构变化、逻辑变化、电气变化、过程变化以及其它变化。实例仅仅代表可能的变化。一些实施例的部分和特征可以包括在其它实施例的部分和特征中或替代其它实施例的部分和特征。在阅读和理解以上描述后,许多其它实施例对于本领域技术人员将是显而易见的。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1