存储芯片以及存储系统的制作方法

本公开实施例涉及半导体,特别涉及一种存储芯片以及存储系统。

背景技术:

1、半导体存储可以分为非易失性存储和易失性存储。动态随机存取存储器(dynamicrandom access memory,dram)作为易失性存储,具备存储密度高、读写速度快等优点,广泛用于各种电子系统中。

2、dram系统通常由控制器以及多个存储芯片构成,因制程等差异使得不同的存储芯片的性能也相应具有差异,这将影响dram系统的整体性能。

技术实现思路

1、本公开实施例提供一种存储芯片以及存储系统,以改善存储系统中数据信号传输冲突的问题。

2、根据本公开一些实施例中,本公开实施例一方面提供一种存储芯片,应用于存储系统,包括:所述存储芯片被配置为,在所述存储芯片上电启动后进行计数并获取计数值,所述计数值用于表征所述存储芯片的工艺角,所述存储芯片内还具有大小可调的参考电压,所述参考电压的大小基于所述计数值可调,且所述存储芯片基于所述参考电压,调整数据从存储单元读出到从数据端口输出的延时。

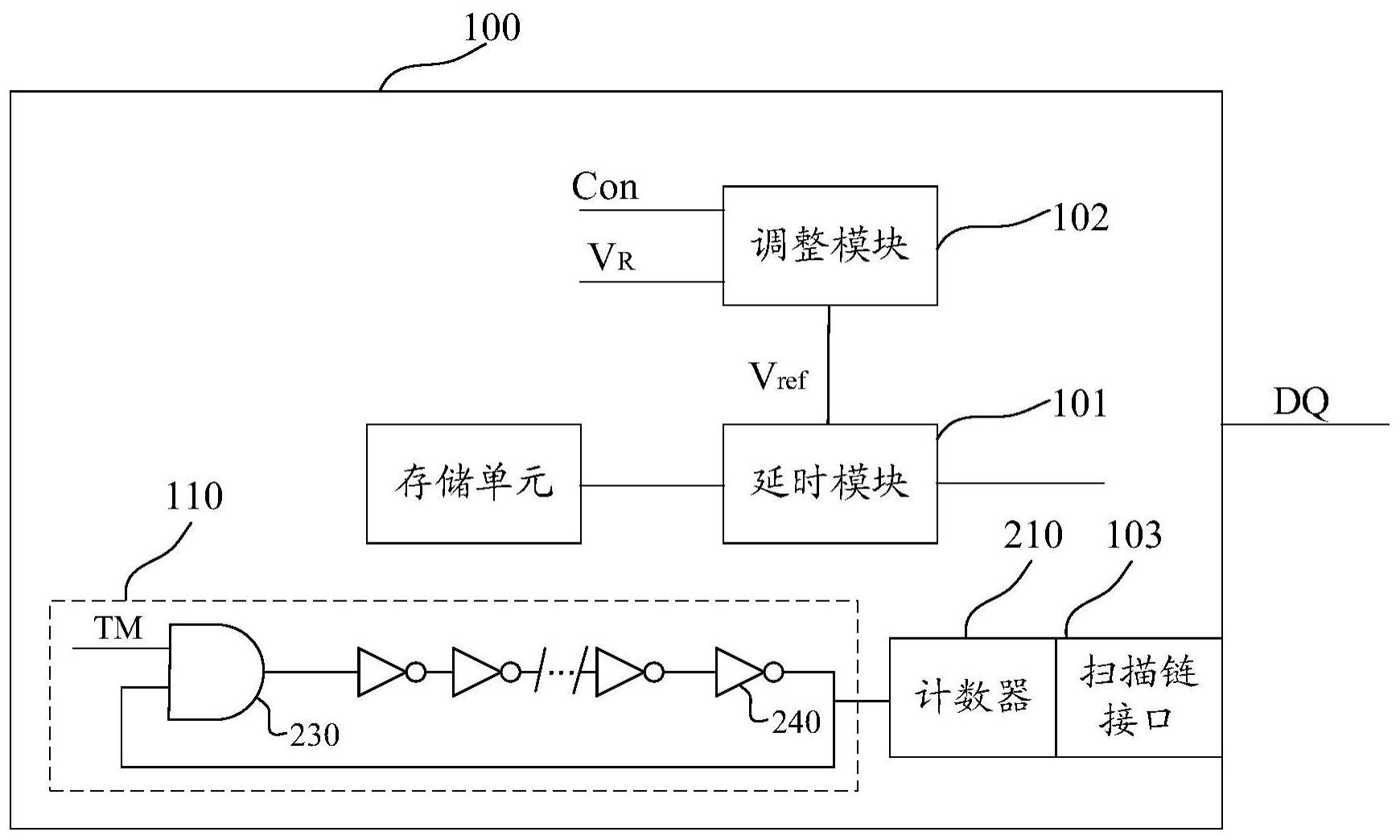

3、在一些实施例中,所述存储芯片包括:环形振荡器;计数器,所述计数器与所述环形振荡器连接,用于在预设时间内对所述环形振荡器的振荡周期进行计数以获取所述计数值。

4、在一些实施例中,所述存储芯片还包括:扫描链接口,所述扫描链接口被配置为,基于控制器发出的命令信号获取所述计数值,并向所述控制器输出所述计数值。

5、在一些实施例中,所述数据具有读出路径,所述读出路径包括数据从所述存储单元读出到从所述数据端口输出的过程,在所述读出路径上传输的所述数据定义为中间数据;所述存储芯片包括:延时模块,所述延时模块设置在所述读出路径上,输入端接收所述中间数据,控制端接收所述参考电压,且输出端基于所述参考电压输出所述中间数据,所述延时模块从接收所述中间数据到输出所述中间数据的延时的长短与所述参考电压的大小相对应;调整模块,所述调整模块的输出端与所述延时模块的控制端连接,输入端接收预设参考电压,控制端接收控制信号,输出端基于所述控制信号以及所述预设参考电压输出大小可调的所述参考电压。

6、在一些实施例中,所述调整模块包括:运算放大器,所述运算放大器的正输入端接收所述预设参考电压;调节单元,所述调节单元与所述运算放大器的负输入端以及输出端连接,所述调节单元的输出端输出所述参考电压,且还基于所述控制信号,调整所述调节单元的输出端与所述运算放大器的输出端之间的等效电阻的大小,或者,调整所述调节单元的输出端与地端之间的等效电阻的大小。

7、在一些实施例中,所述调节单元包括:n个串联在所述负输入端与所述运算放大器的输出端之间的第一电阻,n为大于1的整数,至少一个第二电阻,所述第二电阻连接在所述负输入端与地端之间;m个第一开关,所述第一开关连接所述调节单元的输出端以及相应的所述第一电阻的一端,所述第一开关基于所述控制信号选择性导通,以调整所述调节单元的输出端与所述运算放大器的输出端之间的等效电阻的大小,m为小于或等于n的正整数。

8、在一些实施例中,所述调节单元包括:x个串联在所述负输入端与地端之间的第二电阻,x为大于1的正整数;y个第二开关,所述第二开关连接所述调节单元的输出端以及相应的所述第二电阻的一端,所述第二开关基于所述控制信号选择性导通,以调整所述调节单元的输出端与地端之间的等效电阻的大小,y为小于或等于x的正整数。

9、在一些实施例中,所述延时模块包括:顺次连接的偶数个反相器,所述反相器的电源端连接所述参考电压,处于首位的所述反相器的输入端接收所述中间数据,处于尾位的所述反相器的输出端输出所述中间数据。

10、根据本公开一些实施例中,本公开实施例另一方面提供一种存储系统,包括:多个如上述实施例提供的存储芯片;控制器,所述控制器被配置为,获取所述存储芯片的所述计数值,并基于所述计数值,调整与所述计数值相对应的所述存储芯片的所述参考电压的大小。

11、在一些实施例中,所述存储芯片包括:环形振荡器;计数器,所述计数器与所述环形振荡器连接,用于在预设时间内对所述环形振荡器的振荡周期进行计数以获取所述计数值;所述控制器与所述环形振荡器以及所述计数器连接,用于控制所述环形振荡器启动振荡并获取所述计数值。

12、在一些实施例中,所述存储芯片还包括:扫描链接口,所述扫描链接口被配置为,基于控制器发出的命令信号获取所述计数值,并向所述控制器输出所述计数值;所述控制器还包括:获取模块,所述获取模块被配置为,向所述扫描链接口发出所述命令信号,并接收所述扫描链接口输出的所述计数值。

13、在一些实施例中,所述控制器被配置为,在所述存储系统每次上电启动之后,获取每一所述存储芯片的所述计数值,并调整与所述计数值相对应的所述存储芯片的所述参考电压的大小,直至轮询获取所有所述存储芯片的所述计数值,并调整完所有所述存储芯片的所述参考电压的大小。

14、在一些实施例中,所述数据具有读出路径,所述读出路径包括数据从所述存储单元读出到从所述数据端口输出的过程,在所述读出路径上传输的所述数据定义为中间数据;所述存储芯片包括:延时模块,所述延时模块设置在所述读出路径上,输入端接收所述中间数据,控制端接收所述参考电压,且输出端基于所述参考电压输出所述中间数据,所述延时模块从接收所述中间数据到输出所述中间数据的延时的长短与所述参考电压的大小相对应;调整模块,所述调整模块的输出端与所述延时模块的控制端连接,输入端接收预设参考电压,控制端接收控制信号,输出端基于所述控制信号以及所述预设参考电压输出大小可调的所述参考电压;所述控制器与所述调整模块的控制端连接,所述控制器用于获取所述计数值并基于所述计数值生成所述控制信号。

15、在一些实施例中,所述调整模块包括:运算放大器,所述运算放大器的正输入端接收所述预设参考电压;调节单元,所述调节单元与所述运算放大器的负输入端以及输出端连接,所述调节单元的输出端输出所述参考电压,且还基于所述控制信号,调整所述调节单元的输出端与所述运算放大器的输出端之间的等效电阻的大小,或者,调整所述调节单元的输出端与地端之间的等效电阻的大小;所述控制器与所述调节单元连接,并向所述调节单元提供所述控制信号。

16、在一些实施例中,所述调节单元包括:n个串联在所述负输入端与所述运算放大器的输出端之间的第一电阻,n为大于1的整数,至少一个第二电阻,所述第二电阻连接在所述负输入端与地端之间;m个第一开关,所述第一开关连接所述调节单元的输出端以及相应的所述第一电阻的一端,所述第一开关基于所述控制信号选择性导通,以调整所述调节单元的输出端与所述运算放大器的输出端之间的等效电阻的大小,m为小于或等于n的正整数;所述控制器与m个所述第一开关连接。

17、在一些实施例中,所述调节单元包括:x个串联在所述负输入端与地端之间的第二电阻,x为大于1的正整数;y个第二开关,所述第二开关连接所述调节单元的输出端以及相应的所述第二电阻的一端,所述第二开关基于所述控制信号选择性导通,以调整所述调节单元的输出端与地端之间的等效电阻的大小,y为小于或等于x的正整数;所述控制器与y个所述第二开关连接。

18、在一些实施例中,所述控制器被配置为,若所述计数值表征快工艺角,则生成用于控制所述参考电压小于所述预设参考电压的所述控制信号,若所述计数值表征慢工艺角,则生成用于控制所述参考电压大于所述预设参考电压的所述控制信号。

19、在一些实施例中,多个所述存储芯片依次层叠于所述控制器表面;或者,所述存储系统还包括:承载基板,所述控制器位于所述承载基板表面,多个所述存储芯片依次层叠于所述承载基板表面。

20、本公开实施例提供的技术方案具有以下优点:

21、本公开实施例提供的技术方案中,存储芯片上电启动后可进行计数并获取计数值,该计数值用于表征存储芯片的工艺角,且存储芯片内的参考电压基于计数值可调,若计数值表征存储芯片的工艺角为慢工艺角,则调整该存储芯片的参考电压较快工艺角的存储芯片的参考电压更大一些,以使得慢工艺角的存储芯片的数据的延时得到缩短,若计数值表征存储芯片的工艺角为快工艺角,则降低该存储芯片的参考电压,以使得快工艺角的存储芯片的数据的延时相对变长一些。这样,不同存储芯片的参考电压基于其工艺角的不同得到补偿,使得不同存储芯片的数据传输延时将符合预期,提高数据信号的整齐度,防止出现不同存储芯片的数据传输冲突问题,改善存储系统的读写性能。

- 还没有人留言评论。精彩留言会获得点赞!