半导体存储装置的制作方法

1.本发明涉及一种半导体存储装置,特别是有关于与外部时钟信号非同步地操作的半导体存储装置。

背景技术:

2.现有的半导体存储装置包括同步动态随机存取存储器(synchronous dynamic random access memory,sdram)与伪静态随机存取存储器(pseudo-static random access memory,psram)。例如美国专利公报第5594704号所公开的sdram,其是与外部时钟信号同步地操作。

3.另外,psram是与外部时钟信号非同步地操作,其将动态随机存取存储器(dram)作为存储器单元阵列以储存数据,且具有与静态随机存取存储器(static random access memory,sram)相容的接口。psram采用双倍数数据速率(double data rate,ddr)方法作为数据传输方法,且可以使用扩展序列周边接口(expanded serial peripheral interface,xspi)、hyperbustm接口、或xccellatm接口作为存取接口。

4.图1中的(a)和(b)是在现有的半导体存储装置中,各个信号响应于写入指令的输入的时序图。在此,是以使用hyperbustm接口的psram为例。在此例中,psram被配置为当芯片选择信号cs#有效(低电平)时,执行写入操作;当芯片选择信号cs#无效(高电平)时,停止外部时钟信号ck的输入接收器的运作,以停止生成内部时钟信号。如此一来,芯片选择信号cs#的有效与外部时钟信号ck是非同步地。

5.在图1的(a)的写入指令序列中,以延迟计数为3并且写入数据的丛发长度为4的情况为例。在此例中,自芯片选择信号cs#变为无效(高电平)起,经过时间trwr(半导体存储装置返回读/写操作所需的时间),接着经过3个外部时钟信号ck的延迟计数后,在外部时钟信号ck的第六时钟的上升边缘时输入写入数据。在此虽然延迟计数以3为例,但是延迟计数的值取决于外部时钟信号ck的频率。例如,当外部时钟信号ck的频率越高,延迟计数越大。

6.在图1的(a)示例中,芯片选择信号cs#从无效(高电平)变为有效(低电平)后,根据外部时钟信号ck的第一至第三时钟,依序地输入指令(cmd),列地址(row address,ra),以及栏地址(column address,ca)。之后,根据外部时钟信号ck的第六时钟,将所输入的写入数据(de6,do6)写入到指定的存储器单元。接下来,根据外部时钟信号ck的第七时钟,将所输入的写入数据(de7,do7)写入到指定的存储器单元。

7.然后,当写入指令中的写入数据全部输入完毕时,芯片选择信号cs#从有效变为无效,以结束写入操作。

8.然而,如图1中的(b)所示,若芯片选择信号cs#在写入数据(de7,do7)的输入期间从有效变为无效,半导体存储装置中的某些电路将被立即结束操作,导致所输入的写入数据(de7,do7)不能被传输到存储器单元阵列,结果,可能难以将写入数据(de7,do7)写入到指定的存储器单元。

技术实现要素:

9.鉴于上述课题,本发明的目的是解决半导体存储装置在数据写入期间被非活化,导致数据无法完整地被写入半导体存储装置的问题。

10.为了解决上述课题,本发明提供一种半导体存储装置,响应于有效状态的芯片选择信号而执行写入操作。半导体存储装置包括存储器单元阵列、传输电路与控制电路。当芯片选择信号为有效状态时,传输电路根据外部时钟信号取得写入数据,并传输到存储器单元阵列。控制电路根据外部时钟信号,在输入写入数据的第一写入数据期间,在芯片选择信号从有效状态变为无效状态时,维持传输电路的运作,以使第一写入数据传输到存储器单元阵列。

11.根据本发明,在根据外部时钟信号输入第一写入数据的期间,即使芯片选择信号从有效变为无效时,也可将第一写入数据传输到存储器单元阵列,以将第一写入数据写入到存储器单元阵列中的存储器单元。因此,即使在数据写入期间执行半导体存储装置的非活化时,也可适当地将数据写入到半导体存储装置。

附图说明

12.图1的(a)~(b)是当输入写入指令时,现有的半导体存储装置中的信号的时间变化的时序图。

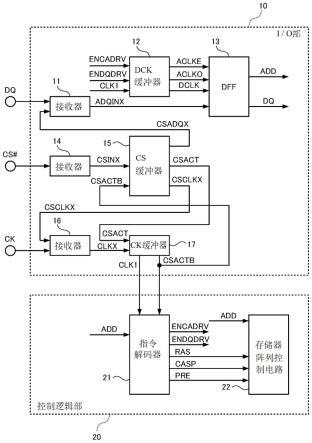

13.图2是与本发明的实施例1有关的半导体存储装置的输入输出接口(i/o)部以及控制逻辑部的配置方块图。

14.图3的(a)是一部分的时钟(ck)缓冲器的配置示例图,图3的(b)是图3的(a)所示的一部分的ck缓冲器中的信号的时间变化的时序图。

15.图4是当输入写入指令时半导体存储装置中的信号的变化的时序图。

16.图5是与本发明的实施例2有关的半导体存储装置的i/o部以及控制逻辑部的配置方块图。

17.图6的(a)是一部分的时钟(ck)缓冲器的配置示例图,图6的(b)是图6的(a)所示的一部分的ck缓冲器中的信号的时间变化的时序图。

18.图7是当输入写入指令时半导体存储装置中的信号的时间变化的时序图。

19.图8是与本发明的变形例有关的半导体存储装置的i/o部以及控制逻辑部的配置方块图。

20.图9的(a)是一部分的指令解码器的配置示例图,图9的(b)是一部分的ck缓冲器的配置示例图。

21.图10的(a)~(b)是图9的(a)所示的一部分的指令解码器和图9的(b)所示的一部分的ck缓冲器中的信号的时间变化的时序图。

22.图11的(a)是基于现有的半导体存储装置规格,芯片选择信号的输入时序的说明示例图,图11的(b)是基于现有的半导体存储装置中,用以输入固定频率的时钟信号而调整芯片选择信号的输入时序的情况的说明示例图,图11的(c)是与本发明的实施例和变形例有关的半导体存储装置中芯片选择信号的输入时序的说明示例图。

23.附图标号:

24.10:i/o部

25.11:接收器

26.12:dck缓冲器

27.13:dff

28.14:接收器

29.15:cs缓冲器

30.16:接收器

31.17:ck缓冲器

32.20:控制逻辑部

33.21:指令解码器

34.22:存储器阵列控制电路

35.100:p通道型mosfet

36.101:n通道型mosfet

37.102:反相器

38.103:反相器

39.104:反相器

40.105:反相器

41.106:延迟电路

42.200:延迟电路

43.201:反相器

44.202:反相器

45.203:反相器

46.204:nand电路

47.205:反相器

48.206:反相器

49.207:反相器

50.208:nor电路

51.209:反相器

52.210:nand电路

53.211:nand电路

54.212:反相器

55.213:反相器

56.214:p通道型mosfet

57.215:n通道型mosfet

58.216:反相器

59.217:反相器

60.218:反相器

61.300:第一计数器300

62.301:第二计数器301

63.302:比较器

64.303:反相器

65.304:nand电路

66.400:p通道型mosfet

67.401:n通道型mosfet

68.402:反相器

69.403:反相器

70.404:反相器

71.405:反相器

72.n01:反相器104和延迟电路106之间的节点

73.aclke:从dck缓冲器12输入的信号

74.aclko:从dck缓冲器12输入的信号

75.add:从dff 13输入的信号

76.adqinx:从接收器11输出的信号

77.casp:栏控制信号

78.caspfp:从反相器209输出的信号

79.ck:外部时钟信号

80.clk1:内部时钟信号

81.clk1d:延迟信号

82.clk1drp:从nand电路204输出的信号

83.clkx:ck缓冲器17从接收器16输入的信号

84.cmd:指令

85.cs#:芯片选择信号

86.csact:反相芯片选择信号

87.csactb:第一控制信号

88.csactc:第二控制信号

89.csadqx:用于活化接收器11的信号

90.csclkx:用于活化接收器16的信号

91.csinx:内部芯片选择信号

92.dclk:数据时钟信号

93.dq:数据信号

94.encadrv:用于活化dck缓冲器12的信号

95.endqdrv:用于活化dck缓冲器12的信号

96.mask1:mask2逻辑反相的信号

97.mask2:从反相器212输出的信号(图6)、从反相器402输出的信号(图9)

98.ra:列地址

99.ras:列控制信号

100.ca:栏地址

101.de6,do6:写入数据

102.de7,do7:写入数据

103.pre:预充电信号

104.wrsta:表示写入操作状态的信号

105.wrmtc:从比较器302输出的信号

106.cntdin:第一计数器300表示计数值的信号

107.cntwr:第二计数器301表示计数值的信号

具体实施方式

108.以下,参照于附图,详细地说明与本发明实施例有关的的半导体存储装置。但是,本发明并不限于这些实施例。再者,在本说明书中的“第一”、“第二”、“第三”等标记用于区别某元件和其他元件,并不限于该元件的数目、顺序、优先顺序等。

109.图2是与本发明的实施例1有关的半导体存储装置的配置方块图。与本实施例有关的半导体存储装置为对于外部时钟信号ck非同步地执行通过芯片选择信号cs#的非活化的半导体存储装置:其中,上述半导体存储装置包括输入输出接口(i/o)部10、控制逻辑部20,以及具有以矩阵配置的多存储器单元的存储器单元阵列(附图省略)。

110.i/o部10被配置为执行与外部装置(例如,存储器控制器)之间的信号(例如,芯片选择信号cs#、数据信号dq、外部时钟信号ck等)的接收与传送。另外,控制逻辑部20被配置为基于从外部装置所接收的指令,以控制对存储器单元的数据的读取或写入等操作。进一步,i/o部10、控制逻辑部20、以及存储器单元阵列可以由专用的硬件装置或逻辑电路配置。

111.与本实施例有关的半导体存储装置,可以是对于外部时钟信号ck非同步地执行通过芯片选择信号cs#的非活化的任何的半导体存储装置(例如,dram,psram,sram等)。在本实施例中,半导体存储装置是以hyperbustm接口的psram为例进行说明。另外,在本实施例中,与图1的(a)和(b)示例相同,写入指令序列中的延迟计数为3并且写入数据的丛发长度为4。在本实施例中,适当地使用并且说明与图1的(a)和(b)所示的信号相同的信号。

112.i/o部10包括连接到数据端子(dq端子)的接收器11、数据时钟(dck)缓冲器12,延迟正反器(dff)13、连接到芯片选择端子(cs#端子)的接收器14、芯片选择(cs)缓冲器15,连接到外部时钟端子(ck端子)的接收器16、以及时钟(ck)缓冲器17。为了简化说明,此处未绘示i/o部10中的其他已知的配置(例如,发送或接收其他信号(数据选通信号,重置信号等)的电路)。

113.cs缓冲器15被配置为输出信号csadqx,且信号csadqx被配置为在有效状态下可活化(activate,又称为致能)接收器11。接收器11被配置为当从cs缓冲器15接收有效状态的信号csadqx时,通过dq端子接收来自外部装置的数据信号dq。在此,数据信号dq是根据外部时钟信号ck被输入,且包括各别的特定长度(在本实施例中,8位)的指令、地址(列地址、栏地址等)以及写入数据。另外,接收器11将所输入的数据信号dq作为信号adqinx输出到dff 13。

114.dck缓冲器12被配置为根据有效状态的信号encadrv和信号endqdrv被活化,其中信号encadrv和信号endqdrv可由指令解码器21(将在后文描述)所提供。

115.另外,在信号encadrv为有效状态的期间,响应于ck缓冲器17所提供的内部时钟信号clk1的时钟的每个上升边缘,在与上述时钟对应的外部时钟信号ck的上升边缘中,dck缓冲器12产生用于取得所输入的指令、地址,以及写入数据(包括信号adqinx)的信号aclke,

并将其输出到dff 13。在此情况下,信号aclke也可以是具有与内部时钟信号clk1的时钟相同相位的信号。

116.再者,当信号encadrv为有效的期间,响应于ck缓冲器17所输入的内部时钟信号clk1的时钟的每个下降边缘,在与上述时钟对应的外部时钟信号ck的下降边缘中,dck缓冲器12产生用于取得所输入的指令、地址,以及写入数据(包括信号adqinx)的信号aclko,并将其输出到dff 13。在此情况下,信号aclko也可以是具有与内部时钟信号clk1的时钟相反相位的信号。

117.再者,当信号endqdrv为有效的期间,响应于ck缓冲器17所输入的内部时钟信号clk1的时钟的每个下降边缘,根据与上述时钟对应的外部时钟信号ck,dck缓冲器12产生用于所输入的写入数据(包括信号adqinx)传输到存储器单元阵列的数据时钟信号dclk,并将其输出到dff 13。在此情况下,数据时钟信号dclk的时钟宽度可以与内部时钟信号clk1的时钟宽度相同或不同。

118.在使芯片选择信号cs#有效时,根据外部时钟信号ck,dff 13取得所输入的写入数据,并传输到存储器单元阵列。另外,dff 13被配置为即使在使芯片选择信号cs#无效时(高电平),在使信号encadrv或信号endqdrv有效时也进行操作。另外,dff 13是本发明中的“传输电路”的示例。

119.具体来说,当使信号encadrv为有效时,每当从dck缓冲器12接收信号aclke和信号aclko时,dff 13取得从接收器11输出的信号adqinx。然后,dff 13将表示包括在信号adqinx中的指令和地址的信号add输出到指令解码器21和存储器阵列控制电路22(稍后描述)。另外,当使信号endqdrv有效时,每当从dck缓冲器12接收信号aclke和信号aclko时,dff 13取得从接收器11输出的信号adqinx的同时,每当dff 13从dck缓冲器12输入数据时钟信号dclk时,平行转换并储存包括已取得信号adqinx的写入数据。然后,dff 13根据数据时钟信号dclk将表示包括信号adqinx的写入数据的信号dq输出(传输)到存储器单元阵列。

120.接收器14将经由cs#端子从外部装置输入的芯片选择信号cs#作为内部芯片选择信号csinx输出到cs缓冲器15。

121.当使内部芯片选择信号csinx有效(低电平)时,或者当使由ck缓冲器17提供的第一控制信号csactb有效(高电平)时,cs缓冲器15进行操作。具体来说,cs缓冲器15对来自接收器14的内部芯片选择信号csinx进行逻辑反相,并且将反相芯片选择信号csact输出到ck缓冲器17。另外,cs缓冲器15将在有效(高电平)状态下的信号csadqx输出到接收器11,并且将在有效(高电平)状态下的用于活化接收器16的信号csclkx输出到接收器16。

122.当从cs缓冲器15输入有效的信号csclkx时,接收器16将经由ck端子从外部装置输入的外部时钟信号ck作为信号clkx输出到ck缓冲器17。另外,不论是否使芯片选择信号cs#有效,外部时钟信号ck可以以固定的频率输入。

123.当从cs缓冲器15输入有效的(高电平)反相芯片选择信号csact时,ck缓冲器17使第一控制信号csactb有效(高电平)并将其输出到cs缓冲器15和指令解码器21。另外,ck缓冲器17将从接收器16输入的信号clkx作为内部时钟信号clk1,并将其输出到dck缓冲器12和指令解码器21。内部时钟信号clk1的频率可以与外部时钟信号ck的频率相同或不同。另外,内部时钟信号clk1的频率可以随时间变化,例如,用在临时加速数据读取或写入操作。

124.另外,根据外部时钟信号ck,在第一写入数据(在此是写入数据(de7,do7))输入期

间,芯片选择信号cs#从有效(低电平)变为无效(高电平)时,ck缓冲器17操作dff 13(传输电路)将写入数据(de7,do7)传输到存储器单元阵列。在此,ck缓冲器17是本发明中的“控制电路”的示例。

125.另外,上述第一写入数据可以是写入指令中的最后写入数据(在本实施例中,写入数据(de7,do7))。由此,根据外部时钟信号ck,在写入数据(de7,do7)输入期间,即使芯片选择信号cs#从有效(低电平)变为无效(高电平)时,由于可以将写入数据(de7,do7)传输到存储器单元阵列,所以可以将写入数据(de7,do7)写入到存储器单元阵列中的存储器单元。由此,在写入指令中所输入的全部的写入数据可以适当地被写入到半导体存储装置。

126.另外,即使芯片选择信号cs#在变为无效(高电平)后,ck缓冲器17也可通过将用以操作dff 13(传输电路)的第一控制信号csactb维持在有效(高电平)状态而使dff 13运作,第一控制信号csactb(控制信号)是基于芯片选择信号cs#而产生。由此,即使当芯片选择信号cs#从有效变为无效时,由于使第一控制信号csactb有效(高电平),所以可以基于有效的第一控制信号csactb来操作dff 13。

127.另外,内部时钟信号clk1是基于外部时钟信号ck而产生,在用于产生上述数据时钟信号dclk的内部时钟信号clk1为有效(高电平)的期间,ck缓冲器17可以维持第一控制信号csactb(控制信号)在有效(高电平)状态;上述数据时钟信号dclk是用于传输第一写入数据(在此为写入数据(de7,do7))到存储器单元阵列的信号。由此,基于内部时钟信号clk1,当产生用于将写入数据(de7,do7)传输到存储器单元阵列的数据时钟信号dclk时,可以操作dff 13。根据所产生的内部时钟信号clk1,可以将写入数据(de7,do7)传输到存储器单元阵列。

128.另外,在芯片选择信号cs#从有效(低电平)变为无效(高电平)之后到下一次有效的期间,ck缓冲器17结束dff 13(传输电路)的操作。由此,芯片选择信号cs#在下一次有效(即,下一次读或写入操作开始)前,可以重置dff 13。

129.接下来,将说明控制逻辑部20的配置。控制逻辑部20包括指令解码器21和存储器阵列控制电路22。另外,为了简化说明,此处未表示控制逻辑部20中的其他已知的配置(例如,控制存储器单元的更新操作的电路)。

130.当从ck缓冲器17输入有效的(高电平)第一控制信号csactb时,在从ck缓冲器17输入的内部时钟信号clk1的特定时钟(在图4的示例中,第一时钟)的上升边缘到特定时钟(在图4的示例中,第三时钟)的下降边缘期间,指令解码器21将有效的(高电平)信号encadrv输出到dck缓冲器12。另外,当从ck缓冲器17输入的有效的第一控制信号csactb时,在内部时钟信号clk1的特定时钟(在图4的示例中,第六时钟)的上升边缘到特定时钟(在图4的示例中,第七时钟)的下降边缘期间,指令解码器21将有效的(高电平)信号endqdrv输出到dck缓冲器12。

131.另外,基于从dff 13输入的信号add而识别出所输入的全部的列地址之后,当输入内部时钟信号clk1的时钟(在图4的示例中,第三时钟)时,指令解码器21通过所输入的列地址,将用于活化所选择的字线的列控制信号ras有效(高电平),并且输出到存储器阵列控制电路22。

132.另外,在内部时钟信号clk1的特定时钟(在图4的示例中,各别的第六时钟和第七时钟)的下降边缘中,指令解码器21根据与上述时钟对应的外部时钟信号ck,将用于选择所

输入的写入数据写入到存储器阵列的位线的栏控制信号casp有效(高电平),并且将其输出到存储器阵列控制电路22。在此,基于包括从dff 13输入的信号add的栏地址来选择存储器单元的位线。

133.另外,当从ck缓冲器17输入无效(低电平)的第一控制信号csactb时,在栏控制信号casp的时钟(在图4的示例中,第七时钟)的下降边缘中,指令解码器21将用于预充电信号pre有效(高电平),并输出到存储器阵列控制电路22,同时使列控制信号ras无效(低电平)。上述栏控制信号casp是用于选择最后的写入数据(在图4的示例中,写入数据(de7,do7))写入到存储器单元的位线的信号。

134.进一步,当经过特定的预先充电时间时,指令解码器21使信号pre无效(低电平),结束操作,并转移到待机状态。

135.基于从dff 13输入的信号add、从指令解码器21输入的列控制信号ras、栏控制信号casp、以及信号pre,存储器阵列控制电路22控制对存储器单元阵列的指令、地址、以及数据。进一步,因为对存储器单元阵列的指令,地址和数据的控制细节与已知的技术相同,因此在本实施例中将省略其说明。

136.接下来,参照于图3的(a)和(b),说明关于一部分的ck缓冲器17的配置和操作。参照图3的(a),为一部分的时钟(ck)缓冲器的配置示例图,本发明一实施例的ck缓冲器17包括p通道型mosfet(metal-oxide-semiconductor field effect transistor,mosfet)100,n通道型mosfet 101,四个反相器102、103、104、105和延迟电路106。

137.p通道型mosfet 100的源极连接到高电压电源,mosfet 100的漏极连接到反相器103的高电压电源侧。内部时钟信号clk1被输入到mosfet 100的栅极。

138.n通道型mosfet 101的漏极连接到反相器103的低电压电源侧。mosfet 101的源极连接到低电压电源。mosfet 101的栅极连接到反相器102的输出端子。

139.内部时钟信号clk1被输入到反相器102的输入端子。反相器102将所输入的内部时钟信号clk1进行逻辑反相,并且将逻辑反相后的信号输出到mosfet 101的栅极。

140.反相芯片选择信号csact被输入到反相器103的输入端子。反相器103的输出端子连接到反相器104的输入端子。当各别的mosfet 100和mosfet 101处于导通状态时,操作反相器103。具体来说,反相器103对反相芯片选择信号csact进行逻辑反相,并且将逻辑反相后的信号输出到反相器104。

141.反相器104的输入端子连接到反相器103的输出端子。反相器104的输出端子连接到延迟电路106。反相器104将从反相器103输出的信号进行逻辑反相,并且将逻辑反相后的信号输出到延迟电路106。

142.反相器105的输入端子连接到反相器104和延迟电路106之间的节点n01。另外,反相器105的输出端子连接到反相器103与反相器104之间的节点。反相器105将从反相器104输出的信号进行逻辑反相,并且将逻辑反相后的信号输出到反相器104。

143.延迟电路106将从反相器104输出的信号延迟特定时间,并且将延迟的信号作为第一控制信号csactb输出到cs缓冲器15和指令解码器21。

144.接下来,参照图3的(b)说明关于如图3的(a)所示的一部分的ck缓冲器17的操作。在本实施例中,在用于输入如图4所示的写入数据(de7,do7)的外部时钟信号ck的时钟(第七时钟)为有效的期间,芯片选择信号cs#从有效(低电平)变为无效(高电平)。首先,当使反

相芯片选择信号csact有效(高电平),并且使内部时钟信号clk1无效(低电平)时,反相芯片选择信号csact经由反相器103和104被输入到延迟电路106。然后,将延迟电路106所输入的信号进行延迟,并且从延迟电路106输出作为有效的(高电平)第一控制信号csactb。

145.接下来,当使外部时钟信号ck的第七时钟有效(高电平)时,在时间t1中,使内部时钟信号clk1的第七时钟有效(高电平)。在此情况下,由于各别的mosfet 100和mosfet 101变为截止状态,所以反相器103的操作停止,并且反相器103的输出端子的电位维持在低电平。由此,从延迟电路106输出的第一控制信号csactb维持在有效(高电平)状态。

146.然后,在时间t2中,在外部时钟信号ck的第七个时钟为有效的期间,芯片选择信号cs#从有效(低电平)变为无效(高电平)时,反相芯片选择信号csact从有效变为无效(低电平)。在此,由于使内部时钟信号clk1的第七时钟保持为有效(高电平),所以各别的mosfet 100和mosfet 101都保持在截止状态。因此,从延迟电路106输出保持为有效的第一控制信号csactb。

147.这样一来,内部时钟信号clk1是基于外部时钟信号ck而产生,在用于产生数据时钟信号dclk的内部时钟信号clk1为有效的期间,ck缓冲器17维持第一控制信号csactb在有效状态;上述数据时钟信号dclk是用于传输写入数据(de7,do7)到存储器单元阵列的信号。

148.进一步,基于从延迟电路106输出的第一控制信号csactb,指令解码器21输出有效的信号endqdrv。另外,dck缓冲器12产生用于将写入数据(de7,do7)传输到存储器单元阵列的数据时钟信号dclk,并将其输出到dff 13。另外,dff 13根据信号aclke、信号aclko、以及数据时钟信号dclk的输入而取得信号adqinx,并且将表示包括信号adqinx的写入数据的信号dq输出(传输)到存储器单元阵列。

149.这样一来,即使芯片选择信号cs#变为无效(高电平),ck缓冲器17仍可通过将用以操作dff 13的第一控制信号csactb维持在有效(高电平)状态而使dff 13运作,第一控制信号csactb是基于芯片选择信号cs#而产生。

150.另外,这样一来,根据外部时钟信号ck,在写入数据(de7,do7)输入期间,芯片选信号cs#从有效(低电平)变为无效(高电平)时,ck缓冲器17操作dff 13以将写入数据(de7,do7)传输到存储器单元阵列。

151.接下来,在时间t3中,当内部时钟信号clk1的第七时钟从有效(高电平)变为无效(低电平)时,各别的mosfet 100和mosfet 101变为导通状态。在此情况下,反相器103将无效的(低电平)反相芯片选择信号csact进行逻辑反相,并输出逻辑反相后的信号。然后,从反相器103输出的信号经由反相器104输入到延迟电路106。然后,将延迟电路106所输入的信号进行延迟,在时间t4中,从延迟电路106输出无效(低电平)的第一控制信号csactb。此时,基于从延迟电路106输出的第一控制信号csactb,指令解码器21输出无效(低电平)的信号endqdrv。由此,结束dck缓冲器12的操作,进一步,结束dff 13的操作。

152.在一实施例中,延迟电路106中的延迟时间可以任意设定,例如,可以设定为小于半导体存储装置中的读取或写入操作之间芯片选择信号cs#的无效持续时间(例如,在hyperbustm接口规格中的tcshi)。在此情况下,在芯片选择信号cs#从有效变为无效之后,再到下一次有效时的期间,ck缓冲器17可以结束dff 13的操作。

153.图4是当输入写入指令时半导体存储装置中的信号的变化的时序图。首先,当芯片选择信号cs#从无效(高电平)变为有效(低电平)时,通过使内部芯片选择信号csinx有效

(低电平),cs缓冲器15开始操作。此时,通过使反相芯片选择信号csact有效(高电平),ck缓冲器17开始运作(即被启用或被活化)。另外,当使信号csadqx和信号csclkx有效(高电平)时,接收器11和接收器16开始运作。另外,通过使第一控制信号csactb有效(高电平)时,指令解码器21开始运作,根据上述动作,dck缓冲器12,dff 13和存储器阵列控制电路22开始运作。

154.接下来,在从外部时钟信号ck的第一时钟的上升边缘至第三时钟的下降边缘之间输入指令(cmd)、列地址(ra)、以及栏地址(ca)。然后,在外部时钟信号ck的第二时钟的下降边缘中,当输入全部的列地址时,响应于根据外部时钟信号ck所产生的内部时钟信号clk1的第三时钟的上升边缘,使列控制信号ras有效,上述列控制信号ras为用于活化由输入的列地址所选择的字线的信号。由此,通过列地址,以使选择的字线活化。

155.接下来,在外部时钟信号ck的第六时钟的上升边缘和下降边缘中,输入写入数据(de6,do6)。然后,响应于内部时钟信号clk1的第六时钟的下降边缘,使数据时钟信号dclk的时钟(第六时钟)有效,上述数据时钟信号dclk为用于通过外部时钟信号ck的第六时钟所输入的数据(de6,do6)传输到存储器单元阵列的信号。根据上述时钟,写入数据(de6,do6)被传输到存储器单元阵列。

156.然后,在使内部时钟信号clk1的第六时钟无效(低电平)之后,使栏控制信号casp的时钟(第六时钟)有效(高电平),上述栏控制信号casp为用于选择写入数据(de6,do6)写入到存储器单元的位线的信号,并且使由栏地址所选择的位线活化。由此,通过外部时钟信号ck的第六时钟,所输入的写入数据(de6,do6)被写入到存储器单元。

157.接下来,在外部时钟信号ck的第七时钟的上升边缘和下降边缘中,输入写入数据(de7,do7)。在此,在外部时钟信号ck的第七时钟有效(高电平)期间,当芯片选择信号cs#从有效(低电平)变为无效(高电平)时,使内部芯片选择信号csinx无效(高电平),进一步,使反相芯片选择信号csact无效(低电平)。

158.另一方面,如图3的(b)所述,在芯片选择信号cs#从有效(低电平)变为无效(高电平)后,第一控制信号csactb仍可维持在有效(高电平)状态,使得信号csadqx和信号csclkx也维持在有效(高电平)状态。在此情况下,接收器11和接受器16,dck缓冲器12,dff 13,cs缓冲器15,ck缓冲器17,指令解码器21和存储器阵列控制电路22继续运作。由此,在内部时钟信号clk1的第七时钟的下降边缘中,使数据时钟信号dclk的时钟(第七时钟)有效(高电平),上述数据时钟信号dclk为用于由外部时钟信号ck的第七时钟所输入的数据(de7,do7)传输到存储器单元阵列的信号。通过上述有效的数据时钟信号dclk,所输入的数据(de7,do7)被传输到存储器单元阵列。

159.然后,在使内部时钟信号clk1的第七时钟无效(低电平)之后,使栏控制信号casp的时钟(第七时钟)有效(高电平),上述栏控制信号casp为用于选择写入数据(de7,do7)写入到存储器单元的位线的信号,并且将由栏地址所选择的位线活化。由此,由外部时钟信号ck的第七时钟所输入的写入数据(de7,do7)被写入到存储器单元。

160.进一步,在从内部时钟信号clk1的第七时钟无效(低电平)开始经过特定时间后,使第一控制信号csactb无效(低电平),以使信号csadqx和信号csclkx无效(低电平)。藉此,接收器11、接收器16、dck缓冲器12、dff 13、cs缓冲器15、以及ck缓冲器17结束运作。

161.另外,在栏控制信号casp的第七时钟的下降边缘中,将用于预充电信号pre有效

(高电平),同时列控制信号ras无效(低电平)。然后,当经过特定的预先充电期间时,使信号pre无效(低电平)。此时,指令解码器21和存储器阵列控制电路22结束运作。

162.如此,根据外部时钟信号ck,在写入数据(de7,do7)输入期间,当芯片选择信号cs#从有效(低电平)变为无效(高电平)时,可以将写入数据(de7,do7)传输到存储器单元阵列,并且可以将写入数据(de7,do7)写入到存储器单元阵列中的存储器单元。

163.如上所述,根据与本实施例有关的半导体存储装置,根据外部时钟信号ck,在写入数据(de7,do7)(第一写入数据)输入期间,即使芯片选择信号cs#从有效(低电平)变为无效(高电平)时,仍可以将写入数据(de7,do7)传输到存储器单元阵列,并且可以将写入数据(de7,do7)写入到存储器单元阵列中的存储器单元。由此,即使在数据写入操作期间执行半导体存储装置的非活化时,仍可以适当地将数据写入到半导体存储装置。

164.另外,根据与本实施例有关的半导体存储装置,无论是否使芯片选择信号cs#有效(低电平),即使外部时钟信号ck以固定频率输入时,可以将写入数据(de7,do7)(第一写入数据)传输到存储器单元阵列,并且可以将写入数据(de7,do7)写入到存储器单元阵列中的存储器单元。另外,根据与本实施例有关的半导体存储装置,从外部装置对半导体存储装置的外部时钟信号的供应时序不受限制(例如,扩大或缩小外部时钟信号的连续两个时钟的间隔等)。由于可以以固定的频率将外部时钟信号提供给半导体存储装置,因此可以实现提高操作性的半导体存储装置。

165.在下文中,将说明关于本发明的实施例2。本实施例的半导体存储装置与实施例1的不同之处在于,ck缓冲器17(控制电路)操作dff 13(传输电路),直到写入数据(de7,do7)(第一写入数据)写入到存储器单元阵列中的任何存储器单元为止。在下文中,将说明关于与实施例1不同的配置。

166.图5是与本实施例有关的半导体存储装置的i/o部以及控制逻辑部20的配置方块图。在图5的示例中,第二控制信号csactc(控制信号)是基于芯片选择信号cs#而产生,以及用于操作dff 13的第二控制信号csactc是从ck缓冲器17输入到指令解码器21。

167.当从cs缓冲器15输入有效(高电平)的反相芯片选择信号csact时,ck缓冲器17使第一控制信号csactb有效(高电平),并将其输出到cs缓冲器15和指令解码器21。另外,在本实施例中,当从cs缓冲器15输入有效(高电平)的反相芯片选择信号csact时,ck缓冲器17使第二控制信号csactc有效(高电平),并且将其输出到指令解码器21。

168.另外,在本实施例中,在用于选择写入数据(de7,do7)(第一写入数据)写入到存储器单元的位线的栏控制信号casp为有效(高电平)的期间,ck缓冲器17操作dff13(传输电路)。由此,由于在用于选择写入数据(de7,do7)写入到存储器单元的位线的栏控制信号casp为有效(高电平)的期间,可以操作dff 13,因此,写入数据(de7,do7)可以更准确地传输到存储器单元阵列。

169.在本实施例中,当从ck缓冲器17输入有效的(高电平)第一控制信号csactb或有效的(高电平)第二控制信号csactc时,在从ck缓冲器17输入的内部时钟信号clk1的特定时钟(在此为第一时钟)的上升边缘到特定时钟(在此为第三时钟)的下降边缘期间,指令解码器21将有效的(高电平)信号encadrv输出到dck缓冲器12。另外,当从ck缓冲器17输入有效的(高电平)第一控制信号csactb或有效的(高电平)第二控制信号csactc时,在从ck缓冲器17输入的内部时钟信号clk1的特定时钟(在此为第六时钟)的上升边缘到特定时钟(在此为第

七时钟)的下降边缘期间,指令解码器21将有效的(高电平)信号endqdrv输出到dck缓冲器12。

170.接下来,参照图6的(a),为一部分的时钟(ck)缓冲器的配置示例图,ck缓冲器17包括延迟电路200,串联连接到三个反相器201、202、203,nand电路204,串联连接到三个反相器205、206、207,nor电路208,反相器209,用两个nand电路210、211所构成的rs正反器,两个反相器212、213,p通道型mosfet 214,n通道型mosfet 215,以及三个反相器216、217、218。

171.内部时钟信号clk1被输入到延迟电路200。延迟电路200将输入的内部时钟信号clk1延迟特定时间,并且将延迟信号clk1d输出到nand电路204和反相器201。

172.反相器201的输入端子连接到延迟电路200和nand电路204之间的节点。另外,反相器203对经由反相器201和202输入的信号进行逻辑反相,并且将逻辑反相后的信号输出到nand电路204。

173.从延迟电路200输出的信号clk1d被输入到nand电路204的一个输入端子。另外,从反相器203输出的信号被输入到nand电路204的另一个输入端子。另外,nand电路204基于输入信号执行nand计算,并且将信号clkdrp作为计算结果输出到nand电路210。

174.栏控制信号casp被输入到反相器205的输入端子。另外,反相器207经由反相器205和206对所输入的信号进行逻辑反相,并且将逻辑反相后的信号输出到nor电路208。

175.栏控制信号casp被输入到nor电路208的一个输入端子。另外,从反相器207输出的信号被输入到nor电路208的另一个输入端子。另外,nor电路208基于输入信号执行nor计算,并且将计算结果输出到反相器209。

176.反相器209对从nor电路208输入的信号进行逻辑反相,并且将逻辑反相后的信号作为信号caspfp输出到nand电路211。

177.从nand电路204输出的信号clk1drp被输入到rs正反器的nand电路210的一个输入端子。另外,nand电路210的另一个输入端子连接到nand电路211的输出端子。另外,nand电路210的输出端子连接到反相器212的输入端子和nand电路211的一个输入端子。另外,从反相器209输出的信号caspfp被输入到nand电路211的另一个输入端子。

178.反相器212对从nand电路210输出的信号进行逻辑反相,并且将逻辑反相后的信号作为信号mask2输出到反相器213和mosfet 215。

179.反相器213对从反相器212输出的信号mask2进行逻辑反相,并且将逻辑反相后的信号作为信号mask1输出到mosfet 214。

180.进一步,mosfet 214、215和三个反相器216、217、218的配置使信号mask1输入到mosfet 214的栅极,信号mask2输入到mosfet 215的栅极,除了如图6的(a)所示的节点n01的信号被输入到反相器216,以及第二控制信号csactc从反相器217输出之外,与图3的(a)所示的mosfet 100、101和三个反相器103、104、105的配置相同。

181.参照图6的(b),是图6的(a)所示的一部分的ck缓冲器中的信号的时间变化的时序图。首先,当使反相芯片选择信号csact有效(高电平),使内部时钟信号clk1无效(低电平),以及使栏控制信号casp无效(低电平)时,信号mask1变为低电平,以及信号mask2变为高电平。由此,反相器216对节点n01所输入的信号进行逻辑反相,并且将逻辑反相后的信号输出到反相器217。另外,反相器217对输入信号进行逻辑反相,并输出逻辑反相后的信号作为有效(高电平)的第二控制信号csactc。

182.接下来,当使外部时钟信号ck的第六时钟有效(高电平)时,在时间t11中,使内部时钟信号clk1的第六时钟有效(高电平)。之后,使信号clk1d有效(高电平),并且将信号clk1drp变为低电平。此时,通过设定rs正反器,信号mask1变为高电平,以及信号mask2变为低电平。在此情况下,由于各别的mosfet 214和mosfet 215变为截止状态,所以停止反相器216的运作,并且反相器216的输出端子的电位维持在低电平。由此,第二控制信号csactc维持在有效(高电平)状态。

183.接下来,在从内部时钟信号clk1的第六时钟的下降边缘开始经过特定时间后,使栏控制信号casp的时钟(第六时钟)有效(高电平)。由此,由外部时钟信号ck的第六时钟所输入的写入数据(de6,do6)写入到存储器单元。然后,当使栏控制信号casp的时钟(第六时钟)无效(低电平)时,在时间t12中,信号caspfp变为低电平。此时,通过重置rs正反器,信号mask1变为低电平,以及信号mask2变为高电平。在此情况下,各别的mosfet 214和mosfet 215变为导通状态,并且反相器216对节点n01的输入信号进行逻辑反相,并且将逻辑反相后的信号输出到反相器217。在此,由于节点n01的信号的逻辑电平与第一控制信号csactb的逻辑电平相同(此时为高电平),所以第二控制信号csactc维持在有效(高电平)状态。

184.接下来,在时间t13中,基于使内部时钟信号clk1的第七时钟有效(高电平),信号clk1drp变为低电平。在此情况下,如上所述,基于重置rs触发器,各别的mosfet 214和mosfet 215变为截止状态。由此,第二控制信号csactc维持在有效(高电平)状态。

185.接下来,当在内部时钟信号clk1的第七时钟为有效(高电平)的期间,反相芯片选择信号csact从有效(高电平)变为无效(低电平)时,在从内部时钟信号clk1的第七时钟有效(高电平)开始经过特定时间后,使第一控制信号csactb无效(低电平)。

186.然后,在从内部时钟信号clk1的第七时钟的下降边缘开始经过特定时间后,使栏控制信号casp的时钟(第七时钟)有效(高电平)。由此,由外部时钟信号ck的第七时钟所输入的写入数据(de7,do7)写入到存储器单元。然后,当使栏控制信号casp的时钟(第七时钟)无效(低电平)时,在时间t14中,信号caspfp变为低电平。此时,通过重置rs正反器,信号mask1变为低电平,以及信号mask2变为高电平。在此情况下,各别的mosfet 214和mosfet 215变为导通状态,并且反相器216对节点n01的输入信号进行逻辑反相,并且将逻辑反相后的信号输出到反相器217。在此,由于节点n01的信号的逻辑电平与第一控制信号csactb的逻辑电平相同(此时为低电平),因此使第二控制信号csactc无效(低电平)。

187.此时,由于使各别的第一控制信号csactb和第二控制信号csactc无效(低电平),因此指令解码器21输出无效(低电平)的信号endqdrv。由此,结束dck缓冲器12的运作,并且进一步,结束dff 13的运作。

188.以此方式,在用于选择写入数据(de7,do7)写入到存储器单元的位线的栏控制信号casp为有效的期间,ck缓冲器17可以操作dff 13。

189.另外,根据外部时钟信号ck,在写入数据(de7,do7)输入期间,即使芯片选择信号cs#从有效(低电平)变为无效(高电平),ck缓冲器17也可以操作dff 13,直到写入数据(de7,do7)写入到存储器单元阵列中的任何存储器单元为止。

190.进一步,在本实施例中,应当注意,必需设定延迟电路200的延迟时间,以使rs正反器交互地设定和重置(即,在使下一次内部时钟信号clk1的延迟信号clk1d的时钟(例如,第七时钟)有效(高电平)之前,使基于内部时钟信号clk1的时钟(例如,第六时钟)所产生的栏

控制信号casp的时钟(例如,第六时钟)无效(低电平))。

191.图7是当输入写入指令时本实施例中的半导体存储装置中的信号的时间变化的时序图。在此,将说明与图4所示的时序图不同的部分。

192.首先,当芯片选择信号cs#从无效(高电平)变为有效(低电平)时,使内部芯片选择信号csinx有效(低电平),并且使反相芯片选择信号csact有效(高电平)。由此,使第一控制信号csactb和第二控制信号csactc有效(高电平)。

193.在此,如图6的(b)所述,直到将用于选择写入数据(de7,do7)写入到存储器单元的位线的栏控制信号casp的时钟(第七时钟)无效(低电平)为止的期间,第二控制信号csactc维持在有效(高电平)状态。在此情况下,如图7所示,因为第二控制信号csactc的有效(高电平)状态比第一控制信号csactb的有效(高电平)状态长,所以基于有效的第二控制信号csactc,以使dck缓冲器12和dff 13长时间操作。由此,与实施例1相比,由于可以扩大数据时钟信号dclk的第七时钟的宽度,所以可以更准确地将写入数据(de7,do7)传输到存储器单元阵列。

194.如上所述,根据本实施例有关的半导体存储装置,由于直到写入数据(de7,do7)(第一写入数据)写入到存储器单元为止仍可以操作dff 13(传输电路),所以可以更准确地将写入数据(de7,do7)(第一写入数据)传输到存储器单元阵列。

195.在下文中,将说明上述实施例2的变形例。在本变形例中,与实施例2的不同之处在于,通过写入数据(de7,do7)(第一写入数据)写入到任何存储器单元,ck缓冲器17(控制电路)可以操作dff 13(传输电路),直到写入指令中写入到任何的存储器单元的写入数据的数量达到写入指令中所输入的写入数据的数量为止。在下文中,将说明与实施例2不同的配置。

196.图8是与本发明的变形例有关的半导体存储装置的i/o部10以及控制逻辑部20的配置图。在图8的示例中,ck缓冲器17被配置为基于从指令解码器21所输入的信号mask1,输出第二控制信号csactc。

197.接下来,参照图9的(a)和(b),将说明关于在本变形例中的指令解码器21和ck缓冲器17的配置。参照图9的(a),是一部分的指令解码器的配置示例图。指令解码器21包括第一计数器300、第二计数器301、比较器30、反相器303、以及nand电路304。

198.在表示写入操作状态的信号wrsta在有效(高电平)状态下输入期间,在从ck缓冲器17输入的内部时钟信号clk1的时钟的写入数据中,在每个与上述写入数据对应的时钟的下降边缘时,第一计数器300对写入数据中所输入的写入数据的数量进行计数。然后,第一计数器300将表示计数值的信号cntdin输出到比较器302。

199.在此,信号wrsta可以通过指令解码器21产生。根据外部时钟信号ck,当输入指令(cmd)表示为写入指令时,指令解码器21可以产生有效(高电平)的信号wrsta。

200.信号wrsta在有效(高电平)状态下输入期间,在每个从指令解码器21输入的栏控制信号casp的时钟的下降边缘时,第二计数器301对在写入指令中写入到任何的存储器单元的写入数据的数量进行计数。然后,第二计数器301将表示计数值的信号cntwr输出到比较器302。

201.比较器302将从第一计数器300输入的信号cntdin与从第二计数器301输入的信号cntwr进行比较。然后,当由各别的信号cntdin和cntwr的表示值一致时,比较器302将高电

平信号wrmtc输出到nand电路304。另外,当由各别的信号cntdin和cntwr的表示值不一致时,比较器302将低电平信号wrmtc输出到nand电路304。

202.反相器303对从ck缓冲器17输入的内部时钟信号clk1进行逻辑反相,并且将逻辑反相后的信号输出到nand电路304。

203.从比较器302输出的信号wrmtc被输入到nand电路304的一个输入端子。另外,从反相器303输出的信号被输入到nand电路304的另一个输入端子。另外,nand电路304基于输入信号执行nand计算,并将计算结果信号mask1输出到ck缓冲器17。

204.接下来,参照于图9的(b),将说明一部分的ck缓冲器17的配置。ck缓冲器17包括p通道型mosfet 400,n通道型mosfet 401以及四个反相器402、403、404和405。

205.进一步,mosfet 400、401和四个反相器402、403、404、405的配置为,除了信号mask1输入到mosfet 400的栅极,信号mask2输入到mosfet 401的栅极,以及从反相器404输出控制信号csactc之外,与图3的(a)所示的mosfet 100、101和四个反相器102、103、104、105的配置相同。

206.参照图10的(a)~(b),将说明图9的(a)所示的一部分的指令解码器21的操作,以及图9的(b)所示的一部分的ck缓冲器17的操作。在此,图10的(a)表示,在使下一次内部时钟信号clk1的时钟(例如,第七时钟)有效(高电平)之前,使基于内部时钟信号clk1的时钟(例如,第六时钟)所产生的栏控制信号casp的时钟(例如,第六时钟)无效(低电平)的情况。另外,图10的(b)表示,在使下一次内部时钟信号clk1的时钟(例如,第七时钟)有效(高电平)之前,使基于内部时钟信号clk1的时钟(例如,第六时钟)所产生的栏控制信号casp的时钟(例如,第六时钟)没有无效(低电平)的情况。

207.首先,参照图10的(a),当使反相芯片选择信号csact有效(高电平),使内部时钟信号clk1无效(低电平),以及由第一计数器300和第二计数器301的计数值一致时(即,信号wrmtc为高电平),信号mask1为低电平,以及信号mask2为高电平。由此,反相器403对所输入的反相芯片选择信号csact进行逻辑反相,并且将逻辑反相后的信号输出到反相器404。另外,反相器404对输入信号进行逻辑反相,并输出逻辑反相后的信号作为有效(高电平)的第二控制信号csactc。

208.接下来,当使外部时钟信号ck的第六时钟有效(高电平)时,在时间t21中,使内部时钟信号clk1的第六时钟有效(高电平)。此时,信号mask1变为高电平,以及信号mask2变为低电平。在这种情况下,由于各别的mosfet 400和mosfet403变为截止状态,所以停止反相器403的运作,并且反相器403的输出端子的电位维持在低电平。由此,第二控制信号csactc维持在有效(高电平)状态。

209.接下来,在时间t22中,使内部时钟信号clk1的第六时钟无效(低电平)。此时,通过第一计数器300的计数值增加,因为各别的信号cntdin和cntwr的值不同,所以信号wrmtc变为低电平。在这种情况下,由于信号mask2为低电平,因此第二控制信号csactc维持在有效(高电平)状态。

210.然后,在从内部时钟信号clk1的第六时钟的下降边缘开始经过特定时间后,使栏控制信号casp的时钟(第六时钟)有效(高电平)。由此,由外部时钟信号ck的第六时钟所输入的写入数据(de6,do6)写入到存储器单元。然后,在时间t23中,当使栏控制信号casp的时钟(第六时钟)无效(低电平)时,第二计数器301的计数值增加。由此,因为各别的信号

cntdin和cntwr的值相等,所以信号wrmtc变为高电平。另外,当信号mask1变为低电平,并且信号mask2变为高电平时,反相器403开始操作。进一步,此时,第二控制信号csactc维持在有效(高电平)状态。

211.另外,内部时钟信号clk1的第七时钟为有效(高电平)的期间,芯片选择信号cs#从有效(低电平)变为无效(高电平)时,反相芯片选择信号csact从有效(高电平)变为无效(低电平)。

212.接下来,在时间t24中,使内部时钟信号clk1的第七时钟无效(低电平)。此时,通过第一计数器300的计数值增加,因为各别的信号cntdin和cntwr的值不同,所以信号wrmtc变为低电平。在此,因为信号mask2为低电平,所以第二控制信号csactc维持在有效(高电平)状态。

213.然后,在从内部时钟信号clk1的第七时钟的下降边缘开始经过特定时间后,使栏控制信号casp的时钟(第七时钟)有效(高电平)。由此,由外部时钟信号ck的第七时钟所输入的写入数据(de7,do7)写入到存储器单元。然后,在时间t25中,当使栏控制信号casp的时钟(第七时钟)无效(低电平)时,第二计数器301的计数值增加。由此,因为各别的信号cntdin和cntwr的值相等,所以信号wrmtc变为高电平。另外,当信号mask1变为低电平,并且信号mask2变为高电平时,反相器403开始运作。反相器403对输入的反相芯片选择信号csact进行逻辑反相,并且将逻辑反相后的信号输出到反相器404。在此,因为第一控制信号csactb的逻辑电平与反相芯片选择信号csact的逻辑电平相同(此时为低电平),所以使第二控制信号csactc无效(低电平)。

214.此时,因为使各别的第一控制信号csactb和第二控制信号csactc无效(低电平),所以指令解码器21输出无效(低电平)的信号endqdrv。由此,结束dck缓冲器12的运作,并且进一步,结束dff 13的运作。

215.以此方式,通过将写入数据(de7,do7)写入任何存储器单元,ck缓冲器17可以操作dff13,直到写入指令中写入到任何的存储器单元的写入数据的数量达到上述写入指令中输入的写入数据的数量为止。

216.接下来,将说明关于图10(b)所示的情况。在此,时间t31中和时间t32中的各别的信号的状态与图10(a)的时间t21中和时间t22中的各别的信号的状态相同。

217.在时间t33中,在栏控制信号casp的时钟(第七时钟)为有效(高电平)的期间,当使内部时钟信号clk1的第七时钟有效(高电平)时,因为各别的信号cntdin,和cntwr的值仍然不同,所以信号wrmtc变为低电平。另外,由于信号mask2为低电平,因此第二控制信号csactc维持在有效(高电平)状态。

218.接下来,在时间t34中,当使栏控制信号casp的时钟(第六时钟)无效(低电平)时,第二计数器301的计数值增加。由此,因为各别的信号cntdin和cntwr的值相等,所以信号wrmtc变为高电平。在此,由于使内部时钟信号clk1的第七时钟有效(高电平),因此信号mask2仍然为低电平。因此,第二控制信号csactc维持在有效(高电平)状态。

219.然后,在时间t35中,使内部时钟信号clk1的第七时钟无效(低电平)。此时,通过第一计数器300的计数值的增加,因为各别的信号cntdin和cntwr的值不同,所以信号wrmtc变为低电平。在这种情况下,由于信号mask2为低电平,因此第二控制信号csactc维持在有效(高电平)状态。

220.在时间t36中的各别的信号的状态与图10(a)中在时间t25中的各别的信号的状态相同。

221.如上所述,根据本变形例,无需调整在内部时钟信号clk1与栏控制信号casp之间的有效时序,就可以获得与上述实施例2相同的效果。进一步,由于当输入写入指令时本变形例的半导体存储装置中的信号的时间变化与上述实施例2的信号的时间变化相同,因此将其省略说明。

222.如上所述,根据本变形例的半导体存储装置,直到在写入指令中写入到存储器单元的写入数据的数量达到在写入指令中输入的写入数据的数量(即,写入数据(de7,do7)(第一写入数据)写入到存储器单元)为止,由于维持dff13(传输电路)的运作,因此可以将写入数据(de7,do7)更准确地传送到存储器单元阵列。

223.进一步,在上述各个实施例及变形例中,虽半导体存储装置是以使用hyperbustm接口的psram的情况为例进行说明,但在这种情况下,发挥了下文中所述的进一步的效果。

224.图11的(a)是基于现有的半导体存储装置规格,芯片选择信号cs#的输入时序的说明示例图,在hyperbustm接口规格中,定义芯片选择信号cs#的动态特性(ac特性)。图11的(a)表示当外部时钟信号ck为200mhz时,各别的参数的最小值的示例。在此,tcss为直到下一次外部时钟信号ck的上升边缘为止的芯片选择信号cs#的设定时间,tcsh为在外部时钟信号ck的下降边缘后的芯片选择信号cs#的保持时间。另外,tck为时钟周期,tckhp为时钟的半周期。

225.如图11的(a)所示,基于各别的参数,当调整芯片选择信号cs#的输入时序时,外部时钟信号ck的第零时钟和第一时钟之间的间隔,以及第七时钟第八时钟之间的间隔,因为与其他时钟之间的间隔不同,因此难以以固定的频率输入外部时钟信号ck。

226.因此,如图11的(b)所示,无论是否使芯片选择信号cs#有效(低电平),当重新定义各别的参数,以便可以以固定的频率输入外部时钟信号ck时,由于tcsh的时序余裕的范围窄至大约0.7ns,因此仍然难以固定频率输入,例如,200mhz等的高频外部时钟信号ck。另外,在现有的半导体存储装置中,在外部时钟信号ck的时钟(在此为第七时钟)为有效(高电平)的期间,当使芯片选择信号cs#无效(高电平)时,在上述时钟所输入的写入数据没有被传送到存储器单元阵列,结果,可能难以将写入数据写入到存储器单元阵列中的存储器单元。

227.另一方面,如图11的(c)所示,根据上述各个实施例以及变形例的半导体存储装置,在输入写入数据期间,即使芯片选信号cs#从有效(低电平)变为无效(高电平)时,也可以将上述写入数据传输到存储器单元阵列,进一步,由于可以将上述写入数据写入到存储器单元阵列中的存储器单元,因此tcsh的值可以往负的方向增加(例如,-1.5ns)。由此,tcsh的时序余裕范围可以扩大到约1.85(=1.5+0.35)ns。因此,根据上述各实施例以及变形例的半导体存储装置,在维持与hyperbustm接口规格的相容性的同时,不论是否使芯片选择信号cs#有效,都可以继续输入200mhz等的高频外部时钟信号ck。因此,可以改善结合外部装置(例如,存储器控制器)和半导体存储装置的系统的性能。

228.以上所述各个实施例以及变形例是用于简单地理解本发明,没有描述为限制本发明。因此,上述各个实施例以及变形例中所示的各个特征,意在包括属于本发明的技术范围的全部设计变更和均等物。

229.例如,在上述各个实施例以及变形例中,虽是以使用hyperbustm接口的情况为例进行说明,但本发明不限于此。例如,即使用xccellatm接口的情况时,也可以获得与上述各个实施例以及变形例相同的效果。

230.另外,在上述各个实施例以及变形例中,低电平时有效的信号可以变更为高电平时有效。另外,高电平时有效的信号可以变更为低电平时有效。

231.另外,在上述各个实施例以及变形例中,虽以ck缓冲器17为控制电路的情况为例进行了说明,但本发明并不限于此。例如,可以提供具有图3的(a),图6的(a),和/或图9的(b)所示的配置的其他的电路作为控制电路。

232.另外,在上述各个实施例以及变形例中,虽以指令解码器21具有图9的(a)所示的配置的情况为例进行了说明,但本发明并不限于此。例如,图9的(a)所示的配置可以被提供在ck缓冲器17中,或者可以被提供在另一电路中。

233.另外,在上述各个实施例以及变形例中,虽以在写入指令中的最后的写入数据(写入数据(de7,do7))输入期间,芯片选择信号cs#从有效变为无效的情况为例进行了说明。但本发明并不限于此。例如,即使在其他写入数据(例如,写入数据(de6,do6))输入期间,芯片选择信号cs#从有效变为无效时,上述各个实施例以及变形例也可以获得与上述相同的作用和效果。

234.另外,图3的(a),图6的(a),图9的(a)和图9的(b)所示的配置为示例,可以适当地变更,也可以采用其他各种的配置。

235.另外,上述各个实施例以及变形例中的i/o部10和控制逻辑部20的配置为示例,可以适当地变更,也可以采用其他各种的配置。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1