存储器电路架构的制作方法

本申请总体上涉及存储器电路,并且更具体地,涉及存储器电路架构和使用这种存储器电路的方法。

背景技术:

1、常规计算设备(例如,智能电话、平板计算机等)可以包括片上系统(soc),片上系统(soc)具有处理器和其他操作电路。soc还可以包括被实现为静态随机存取存储器(ram)(sram)、动态ram(dram)的随机存取存储器(ram)以及各种只读存储器(rom)。ram可以被实现在处理器(诸如中央处理单元(cpu)、图形处理单元(gpu))内,或被实现在处理器外部。

2、目前,一些cpu架构使用许多以3ghz和以大于3ghz操作的宽输入输出(i/o)存储器实例。然而,由于电阻电容(rc)效应,高频下的宽i/o实施方式可能影响存储器性能。一种方法是将较大的存储器电路实例分解为较小的存储器电路实例,这可以减少一些rc效应并且可以针对3ghz及3ghz以上提供可接受的性能。然而,这种方法也可能使硬件重复,因此导致泄漏损失和面积损失。此外,这种解决方案可以使用布线轨道来合并存储器,并且这些布线轨道本身可能产生一定量的rc效应。

3、另一种提议是使用中继器(repeater)来支持在单个实例内水平地布置的多个存储器电路。但是,中继器可能经历较低的速度,并且在一些情况下可能不适合3ghz实施方式。此外,这种实施方式可能增加字线布线的复杂性。

4、因此,本领域需要更多的存储器架构,以在使用存储器的系统中实现性能、功率和面积(ppa)之间的更好折中。

技术实现思路

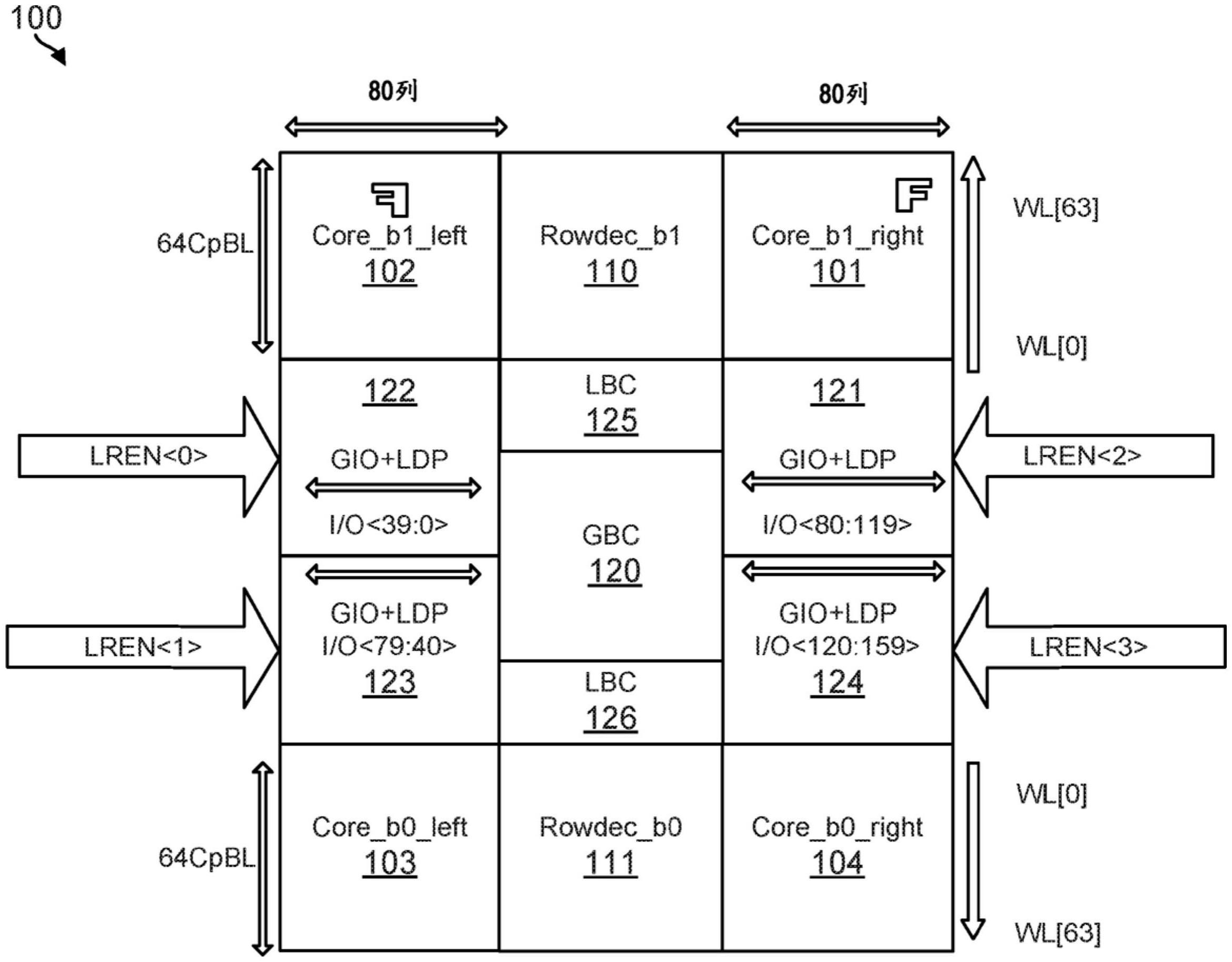

1、各种实施方式提供了存储器架构,该存储器架构提供比现有系统更好的性能、功率和面积(ppa)。实施方式包括具有象限的存储器电路,这些象限被布置在存储器电路的拐角处,并且围绕存储体控制组件。存储体控制组件可以接收指令和地址,预解码这些地址,并且控制行解码器访问存储器核内的特定字线以进行读取和写入访问。存储体控制组件可以包括全局存储体控制器、局部存储体控制器和/或其部分。下面关于图1更详细地讨论全局存储体控制器和局部存储体控制器。存储器电路可以关于平行于象限中的字线的轴线(例如,x轴或水平轴线)对称。此外,一些器件也可以关于y轴对称。一些实施方式包括使用具有该架构的存储器电路的方法。

2、根据一种实施方式,一种半导体器件包括:具有多个象限的存储器电路,多个象限被布置在存储器电路的拐角处并且围绕存储体控制组件;其中多个象限中的第一象限包括第一位单元核和输入输出电路的第一集合,输入输出电路的第一集合被配置为访问第一位单元核,第一象限由包围存储器电路的两个垂直的边缘的部分的矩形边界限定;并且其中多个象限中的第二象限包括第二位单元核和输入输出电路的第二集合,输入输出电路的第二集合被配置为访问第二位单元核,第二象限与第一象限相邻,其中第一象限与第二象限之间的界线限定第一轴线,第一象限和第二象限关于第一轴线对称。例如,多个象限中的第二象限可以关于第一象限水平轴线对称;并且多个象限中的第三象限可以关于第一象限竖直轴线对称。

3、根据另一种实施方式,提供了一种操作半导体器件的方法,方法包括:对存储器电路执行输入输出操作,包括接收指向多个象限中的第一象限的使能信号,多个象限被布置在存储器电路的拐角处并且围绕存储体控制组件;其中多个象限中的第一象限包括第一位单元核和输入输出电路的第一集合,输入输出电路的第一集合被配置为访问第一位单元核,第一象限由包围存储器电路的两个垂直的边缘的部分的矩形边界限定;其中多个象限中的第二象限包括第二位单元核和输入输出电路的第二集合,输入输出电路的第二集合被配置为访问第二位单元核,第二象限与第一象限相邻,其中第一象限与第二象限之间的界线限定第一轴线,第一象限和第二象限关于第一轴线对称;其中对存储器电路执行输入输出操作包括:在存储体控制组件处执行预解码,并且根据预解码来激活行解码器中的字线驱动器。

4、根据另一种实施方式,一种片上系统(soc)包括:随机存取存储器(ram)器件,ram器件包括多个象限,多个象限被布置在ram器件的矩形形状的拐角周围;其中多个象限中的第一象限由包围ram器件的两个垂直的边缘的部分的第一边界限定;其中多个象限中的第二象限关于第一象限水平轴线对称;并且其中多个象限中的第三象限关于第一象限竖直轴线对称。

5、根据另一种实施方式,一种片上系统(soc)包括:具有多个象限的存储器电路,多个象限被布置在存储器电路的拐角处并且围绕用于预解码地址信号的部件;其中多个象限中的第一象限包括输入输出电路的第一集合和用于存储数据的第一部件,输入输出电路的第一集合被配置为访问第一数据存储部件,第一象限由包围存储器电路的两个垂直的边缘的部分的矩形边界限定;其中多个象限中的第二象限包括用于存储数据的第二部件和输入输出电路的第二集合,输入输出电路的第二集合被配置为访问第二数据存储部件,其中第一象限和第二象限之间的界线限定第一轴线,第一象限和第二象限关于第一轴线对称。

6、根据另一种实施方式,一种半导体器件包括:具有多个象限的存储器电路,多个象限被布置在存储器电路的拐角处并且围绕存储体控制组件;其中多个象限中的第一象限包括第一位单元核,第一象限由包围存储器电路的两个垂直的边缘的部分的矩形边界限定;并且其中多个象限中的第二象限包括第二位单元核,第二象限与第一象限相邻,其中第一象限和第二象限之间的界线限定第一轴线,第一象限和第二象限关于第一轴线对称。

技术特征:

1.一种半导体器件,包括:

2.根据权利要求1所述的半导体器件,其中所述界线平行于所述第一位单元核中的字线的方向。

3.根据权利要求1所述的半导体器件,还包括:

4.根据权利要求3所述的半导体器件,还包括:

5.根据权利要求3所述的半导体器件,还包括:

6.根据权利要求5所述的半导体器件,还包括:

7.根据权利要求1所述的半导体器件,其中所述输入输出电路的第一集合和所述输入输出电路的第二集合在所述半导体器件中彼此相邻,此外,其中所述输入输出电路的第一集合与所述输入输出电路的第二集合电隔离。

8.根据权利要求1所述的半导体器件,其中所述第一象限还包括:

9.根据权利要求1所述的半导体器件,其中所述存储体控制组件包括预解码电路装置,所述预解码电路装置被配置为访问所述多个象限中的每个象限。

10.根据权利要求1所述的半导体器件,其中所述存储器电路与来自所述存储器电路外部的四个左右使能信号通信。

11.一种操作半导体器件的方法,所述方法包括:

12.根据权利要求11所述的方法,还包括:

13.根据权利要求11所述的方法,还包括:

14.根据权利要求11所述的方法,还包括第三象限,其中所述第三象限包括第三位单元核和输入输出电路的第三集合,所述输入输出电路的第三集合被配置为访问所述第三位单元核,所述第三象限通过所述行解码器与所述第一象限分离,其中第二轴线垂直于所述第一轴线,并且其中所述第一象限和所述第三象限关于所述第二轴线对称。

15.根据权利要求14所述的方法,还包括:

16.根据权利要求15所述的方法,其中所述输入输出操作和所述附加的输入输出操作被同时执行。

17.根据权利要求15所述的方法,其中执行所述附加的输入输出操作包括:

18.根据权利要求15所述的方法,其中执行所述附加的输入输出操作包括:

19.一种片上系统(soc),包括:

20.根据权利要求19所述的soc,还包括存储体控制组件,所述多个象限中的每个象限共用所述存储体控制组件,其中所述存储体控制组件在内部不对称。

21.根据权利要求19所述的soc,其中所述第一象限包括第一位单元核和输入输出电路的第一集合。

22.根据权利要求19所述的soc,其中所述第二象限与所述第一象限相邻,并且其中所述第一象限与所述第二象限之间的界线限定第一轴线,所述第一象限和所述第二象限关于所述第一轴线对称。

23.根据权利要求19所述的soc,其中所述第一象限和所述第三象限通过具有多个字线驱动器的行解码器被分离,其中所述第一象限和所述第三象限关于平分所述行解码器的竖直轴线对称。

24.根据权利要求19所述的soc,其中所述多个象限中的第四象限关于所述第三象限水平轴线对称。

25.根据权利要求24所述的soc,其中所述第四象限通过行解码器与所述第二象限分离,其中所述第二象限和所述第四象限关于平分所述行解码器的竖直轴线对称。

26.一种片上系统(soc),包括:

27.根据权利要求26所述的soc,其中所述第一数据存储部件包括具有第一多个存储器元件的第一位单元核。

28.根据权利要求27所述的soc,其中所述第二数据存储部件包括具有第二多个存储器元件的第二位单元核。

29.根据权利要求26所述的soc,其中所述用于预解码地址信号的部件包括与所述象限中的每个象限通信的全局存储体控制器。

30.根据权利要求29所述的soc,其中所述全局存储体控制器在内部不对称。

31.根据权利要求29所述的soc,其中所述多个象限中的第三象限包括输入输出电路的第三集合和用于存储数据的第三部件,所述输入输出电路的第三集合被配置为访问所述第三数据存储部件,其中所述第一象限和所述第三象限关于第二轴线对称,所述第二轴线将放置在所述第一象限与所述第三象限之间的行解码器平分。

32.根据权利要求31所述的soc,其中所述第二轴线垂直于所述第一象限中的字线的方向。

33.根据权利要求26所述的soc,其中所述第一轴线平行于所述第一象限中的字线的方向。

34.根据权利要求26所述的soc,其中所述输入输出电路的第一集合和所述输入输出电路的第二集合在所述soc中被彼此相邻布局,此外,其中所述输入输出电路的第一集合与所述输入输出电路的第二集合电隔离。

35.根据权利要求26所述的soc,其中所述存储器电路与来自所述存储器电路外部的四个左右使能信号通信。

36.根据权利要求26所述的soc,其中所述第一象限具有被布置成多列的输入引脚和输出引脚,每列具有两个输入引脚和两个输出引脚。

37.一种半导体器件,包括:

38.根据权利要求37所述的半导体器件,其中所述界线平行于所述第一位单元核中的字线的方向。

39.根据权利要求37所述的半导体器件,还包括:

40.根据权利要求39所述的半导体器件,还包括:

41.根据权利要求39所述的半导体器件,还包括:

技术总结

一种半导体器件包括:具有多个象限的存储器电路,该多个象限被布置在存储器电路的拐角处并且围绕存储体控制组件;其中多个象限中的第一象限包括第一位单元核和输入输出电路的第一集合,输入输出电路的第一集合被配置为访问第一位单元核,第一象限由包围存储器电路的两个垂直的边缘的部分的矩形边界限定;其中多个象限中的第二象限包括第二位单元核和输入输出电路的第二集合,输入输出电路的第二集合被配置为访问第二位单元核,第二象限与第一象限相邻,其中第一象限与第二象限之间的界线限定第一轴线,第一象限和第二象限关于该第一轴线对称。

技术研发人员:D·李,R·比拉达,B·马纳卡姆·维蒂尔,陈薄弘,A·保罗,S·松,S·库什瓦哈,R·R·彻科拉,D·扬

受保护的技术使用者:高通股份有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!