一种信号采样电路以及半导体存储器的制作方法

1.本公开涉及集成电路技术领域,尤其涉及一种信号采样电路以及半导体存储器。

背景技术:

2.随着半导体技术的不断发展,人们在制造和使用计算机等设备时,对数据的传输速度提出了越来越高的要求。为了获得更快的数据传输速度,应运而生了一系列数据可以双倍速率(double data rate,ddr)传输的存储器等器件。

3.在动态随机存取存储器(dynamic random access memory,dram)中,命令地址(command/address,cmd/add或简称为ca)信号既可以作为地址进行采样又可以作为指令进行采样译码。这样,在ca信号采样之后,由于指令还需要进行译码处理,使得指令路径比地址路径多了用于译码的逻辑电路,造成指令信号和地址信号在到达下一级功能模块时会存在较大的时序偏差,进而导致下一级功能模块因为时序偏差出现问题。

技术实现要素:

4.本公开提供了一种信号采样电路以及半导体存储器,可以实现目标指令信号和目标地址信号的时序对齐,避免下一级功能模块因时序偏差而出现问题。

5.第一方面,本公开实施例提供了一种信号采样电路,所述信号采样电路包括输入采样电路、逻辑运算电路、指令译码电路和合并输出电路;其中,

6.所述输入采样电路,用于根据第一时钟信号分别对第一片选信号和第一命令地址信号进行采样处理,得到第二片选信号和第二命令地址信号;其中,所述第二命令地址信号中包括初始指令信号;

7.所述逻辑运算电路,用于对所述第一时钟信号和所述第二片选信号进行逻辑运算,得到片选时钟信号;

8.所述指令译码电路,用于根据所述片选时钟信号和所述第二片选信号对所述初始指令信号进行译码和采样处理,得到目标指令信号;

9.所述合并输出电路,用于根据所述片选时钟信号对所述第二命令地址信号进行采样及输出合并处理,得到目标地址信号。

10.在一些实施例中,所述信号采样电路还包括接收电路,且所述接收电路与所述输入采样电路连接;其中,

11.所述接收电路,用于接收初始命令地址信号、初始片选信号和初始时钟信号,输出所述第一命令地址信号、所述第一片选信号和所述第一时钟信号。

12.在一些实施例中,所述接收电路包括第一接收电路、第二接收电路和第三接收电路;其中,

13.所述第一接收电路,用于接收初始命令地址信号,输出所述第一命令地址信号;

14.所述第二接收电路,用于接收初始片选信号,输出所述第一片选信号;

15.所述第三接收电路,用于接收初始时钟信号,并对所述初始时钟信号进行分频处

理,得到第一时钟奇信号和第一时钟偶信号;其中,所述第一时钟奇信号和所述第一时钟偶信号的时钟周期均是所述初始时钟信号的时钟周期的两倍,且所述第一时钟信号是由所述第一时钟奇信号和所述第一时钟偶信号组成,所述第一时钟奇信号和所述第一时钟偶信号之间的相位差为180度。

16.在一些实施例中,所述输入采样电路包括命令地址采样电路和片选采样电路;其中,

17.所述命令地址采样电路,用于根据所述第一时钟信号对所述第一命令地址信号进行采样处理,得到所述第二命令地址信号;

18.所述片选采样电路,用于根据所述第一时钟信号对所述第一片选信号进行采样及反相处理,得到所述第二片选信号。

19.在一些实施例中,所述命令地址采样电路包括第一采样电路和第二采样电路;其中,

20.所述第一采样电路,用于根据所述第一时钟偶信号对所述第一命令地址信号进行采样处理,得到第二命令地址偶信号;

21.所述第二采样电路,用于根据所述第一时钟奇信号对所述第一命令地址信号进行采样处理,得到第二命令地址奇信号;

22.其中,所述第二命令地址信号是由所述第二命令地址偶信号和所述第二命令地址奇信号组成,所述初始指令信号是由初始指令偶信号和初始指令奇信号组成,且所述第二命令地址偶信号包括所述初始指令偶信号,所述第二命令地址奇信号包括所述初始指令奇信号。

23.在一些实施例中,所述片选采样电路包括第三采样电路和第四采样电路;其中,

24.所述第三采样电路,用于根据所述第一时钟偶信号对所述第一片选信号进行采样及反相处理,得到第二片选偶信号;

25.所述第四采样电路,用于根据所述第一时钟奇信号对所述第一片选信号进行采样及反相处理,得到第二片选奇信号;

26.其中,所述第二片选信号是由所述第二片选偶信号和所述第二片选奇信号组成。

27.在一些实施例中,所述逻辑运算电路包括第一逻辑电路和第二逻辑电路;其中,

28.所述第一逻辑电路,用于接收所述第一时钟偶信号和所述第二片选偶信号,并对所述第一时钟偶信号和所述第二片选偶信号进行逻辑运算,得到片选时钟偶信号;

29.所述第二逻辑电路,用于接收所述第一时钟奇信号和所述第二片选奇信号,并对所述第一时钟奇信号和所述第二片选奇信号进行逻辑运算,得到片选时钟奇信号;

30.其中,所述片选时钟信号是由所述片选时钟偶信号和所述片选时钟奇信号组成。

31.在一些实施例中,所述第一逻辑电路包括第一缓冲器和第一与门;其中,

32.所述第一缓冲器,用于对所述第一时钟偶信号进行延时处理,得到中间时钟偶信号;

33.所述第一与门,用于对所述第二片选偶信号和所述中间时钟偶信号进行与运算,得到所述片选时钟偶信号。

34.在一些实施例中,所述第二逻辑电路包括第二缓冲器和第二与门;其中,

35.所述第二缓冲器,用于对所述第一时钟奇信号进行延时处理,得到中间时钟奇信

号;

36.所述第二与门,用于对所述第二片选奇信号和所述中间时钟奇信号进行与运算,得到所述片选时钟奇信号。

37.在一些实施例中,所述指令译码电路包括第一指令译码电路、第二指令译码电路和或门;其中,

38.所述第一指令译码电路,用于根据所述片选时钟偶信号和所述第二片选偶信号对所述初始指令偶信号进行译码和采样处理,得到指令偶信号;

39.所述第二指令译码电路,用于根据所述片选时钟奇信号和所述第二片选奇信号对所述初始指令奇信号进行译码和采样处理,得到指令奇信号;

40.所述或门,用于对所述指令偶信号和所述指令奇信号进行或运算,得到所述目标指令信号。

41.在一些实施例中,所述第一指令译码电路包括第一译码电路、第五采样电路和第三与门;其中,

42.所述第一译码电路,用于对所述初始指令偶信号进行译码处理,得到指令译码偶信号;

43.所述第五采样电路,用于根据所述片选时钟偶信号对所述指令译码偶信号进行采样处理,得到指令采样偶信号;

44.所述第三与门,用于对所述第二片选偶信号与所述指令采样偶信号进行与运算,得到所述指令偶信号。

45.在一些实施例中,所述第二指令译码电路包括第二译码电路、第六采样电路和第四与门;其中,

46.所述第二译码电路,用于对所述初始指令奇信号进行译码处理,得到指令译码奇信号;

47.所述第六采样电路,用于根据所述片选时钟奇信号对所述指令译码奇信号进行采样处理,得到指令采样奇信号;

48.所述第四与门,用于对所述第二片选奇信号与所述指令采样奇信号进行与运算,得到所述指令奇信号。

49.在一些实施例中,所述第一片选信号是表征目标芯片被选中的信号,且所述第一片选信号为低电平有效的脉冲信号;其中,

50.若所述第一片选信号在偶数时钟周期的上升沿采样为低电平,则确定所述第二片选偶信号为高电平有效的脉冲信号,以及确定所述片选时钟偶信号为高电平有效的脉冲信号;或者,

51.若所述第一片选信号在奇数时钟周期的上升沿采样为低电平,则确定所述第二片选奇信号为高电平有效的脉冲信号,以及确定所述片选时钟奇信号为高电平有效的脉冲信号。

52.在一些实施例中,所述合并输出电路包括第三逻辑电路、第四逻辑电路和第七采样电路;其中,

53.所述第三逻辑电路,用于对所述片选时钟偶信号进行逻辑运算,得到第一使能偶信号和第二使能偶信号,且所述第一使能偶信号和所述第二使能偶信号之间的相位差为

180度;

54.所述第四逻辑电路,用于对所述片选时钟奇信号进行逻辑运算,得到第一使能奇信号和第二使能奇信号,且所述第一使能奇信号和所述第二使能奇信号之间的相位差为180度;

55.所述第七采样电路,用于根据所述第一使能偶信号、所述第二使能偶信号、所述第一使能奇信号和所述第二使能奇信号对所述第二命令地址偶信号和所述第二命令地址奇信号进行采样处理,得到所述目标地址信号。

56.在一些实施例中,所述第七采样电路,具体用于在所述片选时钟偶信号为高电平有效的脉冲信号情况下,根据所述第一使能偶信号和所述第二使能偶信号对所述第二命令地址偶信号进行采样处理,得到所述目标地址信号;或者,在所述片选时钟奇信号为高电平有效的脉冲信号情况下,根据所述第一使能奇信号和所述第二使能奇信号对所述第二命令地址奇信号进行采样处理,得到所述目标地址信号。

57.第二方面,本公开实施例提供了一种半导体存储器,包括如第一方面中任一项所述的信号采样电路。

58.在一些实施例中,该半导体存储器为动态随机存取存储器dram芯片。

59.本公开实施例提供了一种信号采样电路以及半导体存储器,该信号采样电路包括输入采样电路、逻辑运算电路、指令译码电路和合并输出电路;其中,输入采样电路,用于根据第一时钟信号分别对第一片选信号和第一命令地址信号进行采样处理,得到第二片选信号和第二命令地址信号,第二命令地址信号中包括初始指令信号;逻辑运算电路,用于对第一时钟信号和第二片选信号进行逻辑运算,得到片选时钟信号;指令译码电路,用于根据片选时钟信号和第二片选信号对初始指令信号进行译码和采样处理,得到目标指令信号;合并输出电路,用于根据片选时钟信号对第二命令地址信号进行采样及输出合并处理,得到目标地址信号;其中,目标地址信号和目标指令信号之间的时序对齐。这样,基于该信号采样电路,在同一时钟周期的采样下,能够实现目标指令信号和目标地址信号的时序对齐,使得译码之后的指令信号和地址信号之间没有跟随工艺、电压、温度等变化的偏差,从而可以避免下一级功能模块因时序偏差而出现问题。

附图说明

60.图1为一种信号采样电路的组成结构示意图;

61.图2为一种指令译码器的组成结构示意图;

62.图3为一种信号采样电路的信号时序示意图;

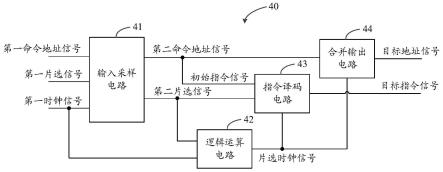

63.图4为本公开实施例提供的一种信号采样电路的组成结构示意图;

64.图5为一个时钟周期命令的信号时序示意图;

65.图6为本公开实施例提供的另一种信号采样电路的组成结构示意图;

66.图7为本公开实施例提供的一种指令译码触发电路的组成结构示意图;

67.图8为本公开实施例提供的一种合并输出电路的组成结构示意图;

68.图9为本公开实施例提供的一种使能反相器的具体电路结构示意图;

69.图10为本公开实施例提供的一种信号采样电路的详细结构示意图;

70.图11为本公开实施例提供的一种信号采样电路的信号时序示意图;

71.图12为本公开实施例提供的一种半导体存储器的组成结构示意图。

具体实施方式

72.下面将结合本公开实施例中的附图,对本公开实施例中的技术方案进行清楚、完整地描述。可以理解的是,此处所描述的具体实施例仅仅用于解释相关申请,而非对该申请的限定。另外还需要说明的是,为了便于描述,附图中仅示出了与有关申请相关的部分。

73.除非另有定义,本文所使用的所有的技术和科学术语与属于本公开的技术领域的技术人员通常理解的含义相同。本文中所使用的术语只是为了描述本公开实施例的目的,不是旨在限制本公开。

74.在以下的描述中,涉及到“一些实施例”,其描述了所有可能实施例的子集,但是可以理解,“一些实施例”可以是所有可能实施例的相同子集或不同子集,并且可以在不冲突的情况下相互结合。

75.需要指出,本公开实施例所涉及的术语“第一\第二\第三”仅是用于区别类似的对象,不代表针对对象的特定排序,可以理解地,“第一\第二\第三”在允许的情况下可以互换特定的顺序或先后次序,以使这里描述的本公开实施例能够以除了在这里图示或描述的以外的顺序实施。

76.以下为本公开实施例中涉及到的专业名词解释以及部分名词的对应关系:

77.动态随机存取存储器(dynamic random access memory,dram)

78.同步动态随机存取存储器(synchronous dynamic random access memory,sdram)

79.双倍速率(double data rate,ddr)

80.第四代ddr(4th ddr,ddr4)

81.第五代ddr(5th ddr,ddr5)

82.命令地址输入(command/address,cmd/add或简称为ca)

83.时钟输入(clock input,clk)

84.片选输入(chip select input,cs)

85.缓冲器(buffer/repeater,rpt)

86.指令译码器(command decoder,cmd dec)

87.d型触发器(data flip-flop或delay flip-flop,dff)

88.工艺、电压、温度(process、voltage、temperature,pvt)

89.可以理解,以ddr5 dram设计为例,ca输入既可以作为地址进行采样又可以作为指令进行采样译码。其中,这里的ca是dram各种命令地址信号的统称,可以包括行地址选通脉冲(row address strobe,ras)、列地址选通脉冲(column address strobe,cas)、写命令(write,we)、激活命令(active,act)等命令信号,以及还可以包括有a13~a0的地址信号等。另外,在实际应用中,该命令地址信号包括几位地址信号,具体可以是根据dram的规格确定,本公开实施例不作任何限定。

90.示例性地,参见图1,其示出了一种信号采样电路的组成结构示意图。如图1所示,该信号采样电路包括第一接收器101、第二接收器102、第三接收器103、第一采样电路104、第二采样电路105、第三采样电路106、第四采样电路107、指令译码器108、或门109、第一功

能模块110、第二功能模块111和第三功能模块112。其中,第一采样电路104和第二采样电路105可以是由d型触发器组成,第三采样电路106和第四采样电路107可以是由d型触发器和反相器组成。另外,对于指令译码器(用cmd dec表示)108而言,其可以是由三输入与非门、二输入或非门和缓冲器等逻辑部件组成,详见图2所示。

91.在图1中,第一接收器101的输入信号为初始命令地址信号(用ca[13:0]表示)和参考信号(用vrefca表示),输出信号为第一命令地址信号(用ca表示);第二接收器102的输入信号为初始片选信号(用cs_n表示)和参考信号(用vrefca表示),输出信号为第一片选信号(用pcs表示);第三接收器103的输入信号为一对输入的互补时钟信号(用ck_t和ck_c表示),输出信号为第一时钟偶信号(用pclk_e表示)和第一时钟奇信号(用pclk_o表示)。然后,通过第一采样电路104,利用第一时钟偶信号对第一命令地址信号进行采样处理,得到目标地址偶信号(用ca[13:0]_e表示),且目标地址偶信号包括初始指令偶信号(用ca[4:0]_e表示);通过第二采样电路105,利用第一时钟奇信号对第一命令地址信号进行采样处理,得到目标地址奇信号(用ca[13:0]_o表示),且目标地址奇信号包括初始指令奇信号(用ca[4:0]_o表示);通过第三采样电路106,利用第一时钟偶信号对第一片选信号进行采样及反相处理,得到第二片选偶信号(用pcs_e表示);通过第四采样电路107,利用第一时钟奇信号对第一片选信号进行采样及反相处理,得到第二片选奇信号(用pcs_o表示);再通过指令译码器108,对ca[4:0]_e、ca[4:0]_o、pcs_e和pcs_o进行译码处理,得到指令偶信号(用cmd_e表示)和指令奇信号(用cmd_o表示);最后,通过或门109对cmd_e和cmd_o进行或逻辑运算,得到目标指令信号(用cmd表示)。另外,目标指令信号、目标地址偶信号和目标地址奇信号与第一功能模块110、第二功能模块111和第三功能模块112之间均存在有长走线路径(long routing line);如此,目标指令信号、目标地址偶信号和目标地址奇信号在经过不同的版图布线路径后将共同到达不同的功能模块(例如,第一功能模块110、第二功能模块111和第三功能模块112等)去实现下一级功能。需要注意的是,这里的ca[13:0]表示一组信号,ca[0]、ca[1]、

…

、ca[13]的合并统称。相应的,第一接收器101中其实包括有14个接收电路,以及输出的线路,甚至包括后面的采样电路,长走线路径也是14根,与ca[0]、ca[1]、

…

、ca[13]是一一对应的。

[0092]

基于图1所示的信号采样电路,其对应的信号时序图如图3所示。在图3中,初始时钟信号用ck_t表示,第一时钟偶信号用pclk_e表示,第一时钟奇信号用pclk_o表示,且ck_t信号的时钟周期为预设时钟周期,pclk_e信号和pclk_o信号的时钟周期均为预设时钟周期的两倍;第一命令地址信号用ca表示,且ca可以包括cy、cz、c0、c1、c2和c3;初始片选信号用cs_n表示,第一片选信号用pcs表示,pcs信号为低电平有效的脉冲信号,且脉冲宽度为预设时钟周期,pcs用于表征目标芯片被选中的信号;在利用pclk_e信号的上升沿对pcs信号进行采样及反相处理后,得到第二片选偶信号用pcs_e表示,其为高电平有效的脉冲信号,而且脉冲宽度为预设时钟周期的两倍;在利用pclk_o信号的上升沿对pcs信号进行采样及反相处理后,得到第二片选奇信号用pcs_o表示,其为低电平信号;在利用pclk_e信号的上升沿对ca信号进行采样处理后,得到的目标地址偶信号用ca[13:0]_e表示和初始指令偶信号用ca[4:0]_e表示;在利用pclk_o信号的上升沿对ca信号进行采样处理后,得到的目标地址奇信号用ca[13:0]_o表示和初始指令奇信号用ca[4:0]_o表示;由于pcs_o信号为低电平信号,那么译码得到的指令奇信号用cmd_o表示,且cmd_o信号也为低电平信号;只有pcs_e信

号和ca[4:0]_e信号进行译码之后,得到的指令偶信号用cmd_e表示,且cmd_e信号为高电平有效的脉冲信号,而且脉冲宽度为预设时钟周期的两倍;但是在经过指令译码等逻辑电路带来的延时之后,导致最终采样得到的ca[13:0]_e信号与cmd_e信号之后存在时序偏差。

[0093]

简单来说,ck_t/ck_c信号在第三接收器103之后分频处理为pclk_e信号和pclk_o信号,然后去采样ca信号。在ca信号被采样之后,由于指令信号还要做译码处理,这样指令路径就比地址路径多出了指令译码器108及或门109等的逻辑电路,再经过不同的版图布线路径共同到达不同的功能模块去实现下一级功能。然而,在同一个时钟周期采样之后,pcs_e信号和ca[4:0]_e信号会输出对齐,但是由于指令路径比地址路径多出的逻辑电路,导致cmd_e信号和ca[13:0]_e信号在到达下一级时就有较大的偏差(skew),并且这个skew在不同pvt条件下会有较大的偏差,从而导致下一级功能会因时序偏差而出现错误。

[0094]

基于此,本公开实施例提供了一种信号采样电路,该信号采样电路包括输入采样电路、逻辑运算电路、指令译码电路和合并输出电路;其中,输入采样电路,用于根据第一时钟信号分别对第一片选信号和第一命令地址信号进行采样处理,得到第二片选信号和第二命令地址信号,第二命令地址信号中包括初始指令信号;逻辑运算电路,用于对第一时钟信号和第二片选信号进行逻辑运算,得到片选时钟信号;指令译码电路,用于根据片选时钟信号和第二片选信号对初始指令信号进行译码和采样处理,得到目标指令信号;合并输出电路,用于根据片选时钟信号对第二命令地址信号进行采样及输出合并处理,得到目标地址信号;其中,目标地址信号和目标指令信号之间的时序对齐。这样,基于该信号采样电路,在同一时钟周期的采样下,能够实现目标指令信号和目标地址信号的时序对齐,使得译码之后的指令信号和地址信号之间没有跟随pvt变化的偏差,从而可以避免下一级功能模块因时序偏差而出现问题。

[0095]

下面将结合附图对本公开各实施例进行详细说明。

[0096]

在本公开的一实施例中,参见图4,其示出了本公开实施例提供的一种信号采样电路的组成结构示意图。如图4所示,该信号采样电路40可以包括输入采样电路41、逻辑运算电路42、指令译码电路43和合并输出电路44;其中,

[0097]

输入采样电路41,用于根据第一时钟信号分别对第一片选信号和第一命令地址信号进行采样处理,得到第二片选信号和第二命令地址信号;其中,第二命令地址信号中包括初始指令信号;

[0098]

逻辑运算电路42,用于对第一时钟信号和第二片选信号进行逻辑运算,得到片选时钟信号;

[0099]

指令译码电路43,用于根据片选时钟信号和第二片选信号对初始指令信号进行译码和采样处理,得到目标指令信号;

[0100]

合并输出电路44,用于根据片选时钟信号对第二命令地址信号进行采样及输出合并处理,得到目标地址信号。

[0101]

需要说明的是,在本公开实施例中,根据指令译码电路43得到的目标地址信号和根据合并输出电路44得到的目标指令信号之间的时序对齐。在这里,时序对齐是指目标指令信号和目标地址信号同时由低电平状态变化为高电平状态,或者同时由高电平状态变化为低电平状态。其中,本公开实施例所述的“时序对齐”和“同时”指的是时序偏差在预设精度范围内。

[0102]

还需要说明的是,在本公开实施例中,这里所述的信号采样电路40应用于一个预设时钟周期的指令信号(用1t cmd表示)。换言之,这里的目标指令信号(用cmd表示)仅包括一个预设时钟周期的有效命令,具体如图5所示。在图5中,cs_n信号为低电平有效的脉冲信号,且脉冲宽度为预设时钟周期;对于预设时钟周期而言,该预设时钟周期对应的ca[13:0]信号是有效(valid)的,而且该预设时钟周期对应的cmd信号也是有效(valid)的。需要注意的是,这里的预设时钟周期是指ck_t/ck_c信号的时钟周期。

[0103]

还需要说明的是,在本公开实施例中,为了实现目标地址信号和目标指令信号之间的时序对齐,这里增加了指令译码电路43和合并输出电路44,两者使用了相同的片选时钟信号进行采样,从而能够使得经由指令译码电路43采样输出的目标指令信号和经由合并输出电路44采样输出的目标地址信号之间时序对齐。

[0104]

在一些实施例中,在图4所示信号采样电路40的基础上,参见图6,该信号采样电路40还可以包括接收电路45,且接收电路45与输入采样电路41连接;其中,

[0105]

接收电路45,用于接收初始命令地址信号、初始片选信号和初始时钟信号,输出所述第一命令地址信号、所述第一片选信号和所述第一时钟信号。

[0106]

需要说明的是,通过接收电路45,可以获得第一命令地址信号、第一片选信号和第一时钟信号,然后将其输入到输入采样电路41进行采样以及后续的逻辑运算。需要注意的是,这里的第一命令地址信号并非是一个信号,而是一组命令地址信号。

[0107]

在一些实施例中,对于接收电路45而言,如图6所示,接收电路45可以包括第一接收电路451、第二接收电路452和第三接收电路453;其中,

[0108]

第一接收电路451,用于接收初始命令地址信号,输出第一命令地址信号;

[0109]

第二接收电路452,用于接收初始片选信号,输出第一片选信号;

[0110]

第三接收电路453,用于接收初始时钟信号,并对初始时钟信号进行分频处理,得到第一时钟奇信号和第一时钟偶信号。

[0111]

需要说明的是,在本公开实施例中,无论是第一接收电路451,还是第二接收电路452或第三接收电路453,均可以是接收器(用recevier表示),或者也可以是缓冲器(用buffer表示)。

[0112]

需要说明的是,在本公开实施例中,这里的初始命令地址信号可以用ca[13:0]表示,第一命令地址信号用ca表示;初始片选信号可以用cs_n表示,第一片选信号用pcs表示;初始时钟信号可以用ck_t和ck_c表示,第一时钟信号可以是由第一时钟奇信号和第一时钟偶信号组成,第一时钟偶信号用pclk_e表示,第一时钟奇信号用pclk_o表示。其中,第一时钟奇信号和第一时钟偶信号的时钟周期均是初始时钟信号的时钟周期的两倍,即pclk_e信号和pclk_o信号的时钟周期均是预设时钟周期的两倍,而且pclk_e信号和pclk_o信号之间的相位差为180度。

[0113]

还需要说明的是,在本公开实施例中,无论是初始命令地址信号还是第一命令地址信号,其并非是一个信号,而是代表一组命令地址信号,即ca[0]~ca[13];因此,对于第一接收电路451而言,这里可以包括有14个接收电路,用于接收ca[0]、ca[1]、

…

、ca[13]等14个信号的,图中仅示出一个接收电路作为示意。

[0114]

进一步地,对于输入采样电路41而言,本公开实施例不仅需要利用第一时钟信号对第一命令地址信号进行采样处理,还需要利用第一时钟信号对第一片选信号进行采样处

理。因此,在一些实施例中,如图6所示,输入采样电路41可以包括命令地址采样电路411和片选采样电路412;其中,

[0115]

命令地址采样电路411,用于根据第一时钟信号对第一命令地址信号进行采样处理,得到第二命令地址信号;

[0116]

片选采样电路412,用于根据第一时钟信号对第一片选信号进行采样及反相处理,得到第二片选信号。

[0117]

在一种具体的实施例中,如图6所示,命令地址采样电路411可以包括第一采样电路和第二采样电路;其中,

[0118]

第一采样电路,用于根据第一时钟偶信号对第一命令地址信号进行采样处理,得到第二命令地址偶信号;

[0119]

第二采样电路,用于根据第一时钟奇信号对第一命令地址信号进行采样处理,得到第二命令地址奇信号。

[0120]

需要说明的是,第二命令地址信号可以是由第二命令地址偶信号和第二命令地址奇信号组成,初始指令信号可以是由初始指令偶信号和初始指令奇信号组成。其中,第二命令地址偶信号包括初始指令偶信号,且第二命令地址偶信号用ca[13:0]_e表示,初始指令偶信号用ca[4:0]_e表示;第二命令地址奇信号包括初始指令奇信号,且第二命令地址奇信号用ca[13:0]_o表示,初始指令奇信号用ca[4:0]_o表示。还需要注意的是,ca[13:0]_e也并非是一个信号,而是代表一组命令地址信号,即ca[0]_e~ca[13]_e,而ca[4:0]_e表示的这一组信号中的ca[0]_e~ca[4]_e;ca[13:0]_o也并非是一个信号,而是代表一组命令地址信号,即ca[0]_o~ca[13]_o,而ca[4:0]_o表示的这一组信号中的ca[0]_o~ca[4]_o。

[0121]

还需要说明的是,第一采样电路和第二采样电路可以是由d型触发器组成;其中,对于第一采样电路来说,d型触发器的时钟端与pclk_e信号连接,d型触发器的输入端与ca信号连接,d型触发器的输出端用于输出ca[13:0]_e信号,且其中的ca[4:0]_e信号组成初始指令偶信号。对于第二采样电路来说,d型触发器的时钟端与pclk_o信号连接,d型触发器的输入端与ca信号连接,d型触发器的输出端用于输出ca[13:0]_o信号,且其中的ca[4:0]_o信号组成初始指令奇信号。

[0122]

在另一种具体的实施例中,如图6所示,片选采样电路412可以包括第三采样电路和第四采样电路;其中,

[0123]

第三采样电路,用于根据第一时钟偶信号对第一片选信号进行采样及反相处理,得到第二片选偶信号;

[0124]

第四采样电路,用于根据第一时钟奇信号对第一片选信号进行采样及反相处理,得到第二片选奇信号。

[0125]

需要说明的是,第二片选信号是由第二片选偶信号和第二片选奇信号组成,其中,第二片选偶信号用pcs_e表示,第二片选奇信号用pcs_o表示。

[0126]

还需要说明的是,第三采样电路和第四采样电路可以是由d型触发器和反相器组成。其中,对于第三采样电路来说,d型触发器的时钟端与pclk_e信号连接,d型触发器的输入端与pcs信号连接,d型触发器的输出端与反相器的输入端连接,反相器的输出端用于输出pcs_e信号。对于第四采样电路来说,d型触发器的时钟端与pclk_o信号连接,d型触发器的输入端与pcs信号连接,d型触发器的输出端与反相器的输入端连接,反相器的输出端用

于输出pcs_o信号。在这里,因为pcs为低电平有效的脉冲信号,增加反相器之后,pcs_o信号或者pcs_e信号就可以变成高电平有效的脉冲信号,以便后续的逻辑运算。另外,对于后续不同的逻辑运算,这里也可以不需要反相器,那么后续的逻辑运算则需进行相应调整,从而也可以达到相同效果。

[0127]

这样,在经过接收电路45和输入采样电路41之后,可以获得第一时钟偶信号(用pclk_e表示)、第一时钟奇信号(用pclk_o表示)、第二片选偶信号(用pcs_e表示)、第二片选奇信号(用pcs_o表示)、以及第二命令地址偶信号(用ca[13:0]_e表示)、第二命令地址奇信号(用ca[13:0]_o表示)、初始指令偶信号(用ca[4:0]_e表示)和初始指令奇信号(用ca[4:0]_o表示);然后利用后续的电路,使用相同的片选时钟信号对第二命令地址偶信号(用ca[13:0]_e表示)和第二命令地址奇信号(用ca[13:0]_o表示)进行采样,以及对初始指令偶信号(用ca[4:0]_e表示)和初始指令奇信号(用ca[4:0]_o表示)进行采样译码,从而能够使得最终输出的目标地址信号和目标指令信号的时序对齐。

[0128]

进一步地,对于逻辑运算电路42而言,本公开实施例不仅需要得到片选时钟偶信号,还需要得到片选时钟奇信号,以便后续能够对指令译码电路43和合并输出电路44进行奇偶采样,以实现地址总线数量减半。因此,在一些实施例中,如图6所示,逻辑运算电路42包括第一逻辑电路421和第二逻辑电路422;其中,

[0129]

第一逻辑电路421,用于接收第一时钟偶信号和第二片选偶信号,并对第一时钟偶信号和第二片选偶信号进行逻辑运算,得到片选时钟偶信号;

[0130]

第二逻辑电路422,用于接收第一时钟奇信号和第二片选奇信号,并对第一时钟奇信号和第二片选奇信号进行逻辑运算,得到片选时钟奇信号。

[0131]

需要说明的是,片选时钟信号可以是由片选时钟偶信号和片选时钟奇信号组成,其中,片选时钟偶信号可以用cs_clk_e表示,片选时钟奇信号可以用cs_clk_o表示。

[0132]

在一种具体的实施例中,对于第一逻辑电路421而言,第一逻辑电路421可以包括第一缓冲器和第一与门;其中,

[0133]

第一缓冲器,用于对第一时钟偶信号进行延时处理,得到中间时钟偶信号;

[0134]

第一与门,用于对第二片选偶信号和中间时钟偶信号进行与运算,得到片选时钟偶信号。

[0135]

在另一种具体的实施例中,对于第二逻辑电路422而言,第二逻辑电路422可以包括第二缓冲器和第二与门;其中,

[0136]

第二缓冲器,用于对第一时钟奇信号进行延时处理,得到中间时钟奇信号;

[0137]

第二与门,用于对第二片选奇信号和中间时钟奇信号进行与运算,得到片选时钟奇信号。

[0138]

需要说明的是,对于缓冲器而言,无论是第一缓冲器还是第二缓冲器,不仅具有延时功能,而且还可以具有增强信号驱动能力的作用。具体地,对于中间时钟偶信号与第一时钟偶信号而言,中间时钟偶信号相比第一时钟偶信号不仅存在时延,而且中间时钟偶信号的驱动能力更强;而对于中间时钟奇信号与第一时钟奇信号而言,中间时钟奇信号相比第一时钟奇信号存在时延,而且中间时钟奇信号的驱动能力更强。

[0139]

还需要说明的是,片选时钟偶信号(用cs_clk_e表示)是通过第一逻辑电路421得到的,片选时钟奇信号(用cs_clk_o表示)是通过第一逻辑电路422得到的。在本公开实施例

中,根据cs_clk_e和cs_clk_o这两个信号对指令译码电路43和合并输出电路44进行相关处理,从而使得最终输出的目标地址信号和目标指令信号的时序对齐。

[0140]

还需要说明的是,在一些实施例中,第一片选信号是表征目标芯片被选中的信号,且第一片选信号为低电平有效的脉冲信号;其中,

[0141]

若第一片选信号在偶数时钟周期的上升沿采样为低电平,则确定第二片选偶信号(用pcs_e表示)为高电平有效的脉冲信号,以及确定片选时钟偶信号(用cs_clk_e表示)为高电平有效的脉冲信号;或者,

[0142]

若第一片选信号在奇数时钟周期的上升沿采样为低电平,则确定第二片选奇信号(用pcs_o表示)为高电平有效的脉冲信号,以及确定片选时钟奇信号(用cs_clk_o表示)为高电平有效的脉冲信号。

[0143]

在这里,偶数时钟周期或者奇数时钟周期是指初始时钟信号(用ck_t/ck_c表示)的时钟周期。具体来说,经过第三接收电路453的分频处理之后,可以得到pclk_e信号和pclk_o信号;然后将pclk_e信号的上升沿所在的时钟周期作为偶数时钟周期,pclk_o信号的上升沿所在的时钟周期作为奇数时钟周期。

[0144]

具体来说,由于pcs_e信号和pcs_o信号中只有一个信号具有高电平,因此利用第一逻辑电路421和第二逻辑电路422,使得在cs_clk_e和cs_clk_o这两个信号中,同样只有一个信号为具有高电平的有效信号,另一个信号则为无效信号(即低电平信号);即通过屏蔽第一片选信号为高电平(即无命令)时的片选时钟信号(用cs_clk_e或者cs_clk_o表示),减少不必要时钟信号振荡,从而还能够实现节省功耗的功能。

[0145]

进一步地,对于指令译码电路43而言,根据片选时钟偶信号和片选时钟奇信号,需要对初始指令信号中的奇偶信号分别进行采样和译码。因此,在一些实施例中,如图6所示,指令译码电路43可以包括指令译码触发电路431和或门432;其中,

[0146]

指令译码触发电路431,用于接收片选时钟信号、第二片选信号和初始指令信号,输出指令偶信号和指令奇信号;

[0147]

或门432,用于对指令偶信号和指令奇信号进行或运算,得到目标指令信号。

[0148]

需要说明的是,这里的指令译码触发电路431也可称为指令译码触发器,用cmd dec dff表示。对于指令译码触发电路431而言,参见图7,指令译码触发电路431可以包括第一指令译码电路a和第二指令译码电路b;其中,

[0149]

第一指令译码电路a,用于根据片选时钟偶信号和第二片选偶信号对初始指令偶信号进行译码和采样处理,得到指令偶信号;

[0150]

第二指令译码电路b,用于根据片选时钟奇信号和第二片选奇信号对初始指令奇信号进行译码和采样处理,得到指令奇信号。

[0151]

需要说明的是,目标指令信号可以用cmd表示,而且目标指令信号是由指令偶信号(用cmd_e表示)和指令奇信号(用cmd_o表示)进行或逻辑运算得到的。其中,cmd_e信号是通过第一指令译码电路a进行译码和采样得到的,cmd_o信号是通过第二指令译码电路b进行译码和采样得到的。

[0152]

在一种具体的实施例中,如图7所示,第一指令译码电路a可以包括第一译码电路、第五采样电路和第三与门;其中,

[0153]

第一译码电路,用于对初始指令偶信号进行译码处理,得到指令译码偶信号;

[0154]

第五采样电路,用于根据片选时钟偶信号对指令译码偶信号进行采样处理,得到指令采样偶信号;

[0155]

第三与门,用于对第二片选偶信号与指令采样偶信号进行与运算,得到指令偶信号。

[0156]

需要说明的是,初始指令偶信号可以包括ca[0]_e、ca[1]_e、ca[2]_e、ca[3]_e、ca[4]_e等指令信号,而且第一译码电路可以是由二输入与非门、三输入与非门和二输入或非门组成。其中,如图7所示,ca[0]_e和ca[1]_e输入到二输入与非门,ca[2]_e、ca[3]_e和ca[4]_e输入到三输入与非门,然后二输入与非门的输出端和三输入与非门的输出端将将与二输入或非门的输入端连接,而二输入或非门的输出端用于输出指令译码偶信号,从而实现对初始指令偶信号的译码。需要注意的是,第一译码电路的设计具体是根据指令译码规则实现的。对于不同的产品,不同的应用场景,不同的指令,译码规则可能不同,那么该译码电路的逻辑也可进行相应调整,本公开实施例不作具体限定。

[0157]

还需要说明的是,第五采样电路可以为d型触发器。其中,如图7所示,d型触发器的时钟端与片选时钟偶信号(用cs_clk_e表示)连接,d型触发器的输入端与二输入或非门的输出端连接,用于接收指令译码偶信号;d型触发器的输出端与第三与门的一个输入端连接,第二片选偶信号(用pcs_e表示)与第三与门的另一个输入端连接,而第三与门的输出端用于输出指令偶信号,从而在对指令译码偶信号进行采样之后,通过第三与门还能够保证只有pcs_e信号为高电平时,可以得到指令偶信号,即保证了指令偶信号和指令奇信号中仅有一个有效信号;换言之,可以屏蔽pcs_e为高电平有效时之外的其他信号。

[0158]

在另一种具体的实施例中,如图7所示,第二指令译码电路b可以包括第二译码电路、第六采样电路和第四与门;其中,

[0159]

第二译码电路,用于对初始指令奇信号进行译码处理,得到指令译码奇信号;

[0160]

第六采样电路,用于根据片选时钟奇信号对指令译码奇信号进行采样处理,得到指令采样奇信号;

[0161]

第四与门,用于对第二片选奇信号与指令采样奇信号进行与运算,得到指令奇信号。

[0162]

需要说明的是,初始指令奇信号可以包括ca[0]_o、ca[1]_o、ca[2]_o、ca[3]_o、ca[4]_o等指令信号,而且第二译码电路也是由二输入与非门、三输入与非门和二输入或非门组成。其中,如图7所示,ca[0]_o和ca[1]_o输入到二输入与非门,ca[2]_o、ca[3]_o和ca[4]_o输入到三输入与非门,然后二输入与非门的输出端和三输入与非门的输出端将与二输入或非门的输入端连接,而二输入或非门的输出端用于输出指令译码奇信号,从而实现对初始指令奇信号的译码。需要注意的是,第二译码电路的设计具体也是根据指令译码规则实现的。对于不同的产品,不同的应用场景,不同的指令,译码规则可能不同,那么该译码电路的逻辑也可进行相应调整,本公开实施例不作具体限定。

[0163]

还需要说明的是,第六采样电路也可以为d型触发器。其中,如图7所示,d型触发器的时钟端与片选时钟奇信号(用cs_clk_o表示)连接,d型触发器的输入端与二输入或非门的输出端连接,用于接收指令译码奇信号;d型触发器的输出端与第四与门的一个输入端连接,第二片选奇信号(用pcs_o表示)与第四与门的另一个输入端连接,而第四与门的输出端用于输出指令奇信号,从而在对指令译码奇信号进行采样之后,通过第四与门还能够保证

只有pcs_o信号为高电平时,可以得到指令奇信号,即保证了指令偶信号和指令奇信号中仅有一个有效信号;换言之,可以屏蔽pcs_o为高电平有效时之外的其他信号。

[0164]

还需要说明的是,在本公开实施例中,片选时钟偶信号(用cs_clk_e表示)和片选时钟奇信号(用cs_clk_o表示)中仅有一个为高电平有效的脉冲信号。这样,如果片选时钟偶信号(cs_clk_e表示)为高电平有效的脉冲信号,这时候由于片选时钟奇信号(用cs_clk_o表示)为低电平信号而不会执行第二指令译码电路b的采样处理,即指令奇信号(用cmd_o表示)为低电平信号,那么此时得到的指令偶信号(用cmd_e表示)与低电平信号通过或门432进行或运算,输出的仍为cmd_e信号;换言之,这时候得到的cmd_e信号即为目标指令信号(用cmd表示)。反之,如果片选时钟奇信号(用cs_clk_o表示)为高电平有效的脉冲信号,这时候由于片选时钟偶信号(用cs_clk_e表示)为低电平信号而不会执行第一指令译码电路a的采样处理,即指令偶信号(用cmd_e表示)为低电平信号,那么此时得到的指令奇信号(用cmd_o表示)与低电平信号通过或门432进行或运算,输出的仍为cmd_o信号;换言之,这时候得到的cmd_o信号即为目标指令信号(用cmd表示)。

[0165]

进一步地,对于合并输出电路44而言,合并输出电路44也可称为合并输出触发器,用output combined dff表示。也就是说,合并输出电路44本质也为一个d型触发器,主要是针对第二命令地址信号进行采样以选取命令有效时的地址总线,并将奇偶地址总线进行合并。因此,在一些实施例中,如图8所示,合并输出电路44可以包括第三逻辑电路441、第四逻辑电路442和第七采样电路443;其中,

[0166]

第三逻辑电路441,用于对片选时钟偶信号进行逻辑运算,得到第一使能偶信号和第二使能偶信号;

[0167]

第四逻辑电路442,用于对片选时钟奇信号进行逻辑运算,得到第一使能奇信号和第二使能奇信号;

[0168]

第七采样电路443,用于根据第一使能偶信号、第二使能偶信号、第一使能奇信号和第二使能奇信号对第二命令地址偶信号和第二命令地址奇信号进行采样处理,得到目标地址信号。

[0169]

需要说明的是,如图8所示,第三逻辑电路441可以是由一个反相器和一个缓冲器组成。其中,第一使能偶信号可以用clkb_e表示,第二使能偶信号可以用clkt_e表示,且clkb_e信号和clkt_e信号之间的相位差为180度。

[0170]

还需要说明的是,如图8所示,第四逻辑电路442也可以是由一个反相器和一个缓冲器组成。其中,第一使能奇信号可以用clkb_o表示,第二使能奇信号可以用clkt_o表示,且clkb_o信号和clkt_o信号之间的相位差为180度。

[0171]

还需要说明的是,对于第二命令地址偶信号而言,用ca[13:0]_e表示,其代表了ca[0]_e、ca[1]_e、ca[2]_e、

…

、ca[13]_e等共14个信号;对于第二命令地址奇信号而言,用ca[13:0]_o表示,其代表了ca[0]_o、ca[1]_o、ca[2]_o、

…

、ca[13]_o等共14个信号;也就是说,对于每一组信号(例如,ca[0]_e和ca[0]_o、ca[1]_e和ca[1]_o、

…

、ca[13]_e和ca[13]_o)都需要一个第七采样电路443,即本公开实施例总共需要14个第七采样电路443。以用ca[0]_e和ca[0]_o这一组信号为例,如图8所示,第七采样电路443可以是由若干个使能反相器和若干个反相器组成。其中,利用第一使能偶信号(用clkb_e表示)和第二使能偶信号(用clkt_e表示)对ca[0]_e信号进行采样处理;以及利用第一使能奇信号(用clkb_o表示)和第

二使能奇信号(用clkt_o表示)对ca[0]_o信号进行采样处理,最终输出的目标地址信号用addr[0]表示。

[0172]

另外,参见图9,其示出了一种使能反相器(enable inverter)的具体电路结构示意图。其中,(a)为使能反相器的器件符号,(b)为使能反相器的具体组成。如图9所示,输入信号用in表示,输出信号用out表示,使能信号用en表示。具体地,在本公开实施例中,若en信号为高电平,则使能反相器工作,即需要对in信号进行反相处理以得到out信号;若en信号为低电平,则使能反相器关断,反相器输出端呈现高阻态。

[0173]

这样,针对图8所示的第七采样电路443的工作原理,具体为:在clkb_e信号为高电平时,把ca[0]_e信号接收,通过一个使能反相器以及紧接着的反相器,把信号传输到该反相器之后这个节点,等clkt_e信号为高电平时,再把该信号输出,所以呈现出clkt_e信号上升沿采样的效果;另外,在clkb_o信号为高电平时,把ca[0]_o信号接收,通过一个使能反相器以及紧接着的反相器,把信号传输到该反相器之后这个节点,等clkt_o信号为高电平时,再把该信号输出,所以呈现出clkt_o信号上升沿采样的效果;最后,在addr[0]信号处的两个首尾相接的反相器则是起到了保持信号的作用。

[0174]

在本公开实施例中,由于片选时钟偶信号(用cs_clk_e表示)和片选时钟奇信号(用cs_clk_o表示)中仅有一个为高电平有效的脉冲信号,因此,第七采样电路443的利用clkt_e信号采样部分和利用clkt_o信号采样部分中只有一部分工作,另一部分输出高阻态,最终的addr就可以输出工作的那一部分的结果。

[0175]

进一步地,由于片选时钟偶信号(用cs_clk_e表示)和片选时钟奇信号(用cs_clk_o表示)中仅有一个为高电平有效的脉冲信号;因此,在一些实施例中,第七采样电路443,具体用于在片选时钟偶信号为高电平有效的脉冲信号情况下,根据第一使能偶信号和第二使能偶信号对第二命令地址偶信号进行采样处理,得到目标地址信号;或者,在片选时钟奇信号为高电平有效的脉冲信号情况下,根据第一使能奇信号和第二使能奇信号对第二命令地址奇信号进行采样处理,得到目标地址信号。

[0176]

综上可知,在本公开实施例中,通过增加指令译码电路43和合并输出电路44,并利用相同的片选时钟信号(用cs_clk_e、cs_clk_o表示)对其进行采样,可以对齐输出的cmd和addr[13:0];同时,由于仅选取同命令有效的地址总线还可以减半地址总线数量,即通过该合并输出电路44,将奇偶采样的地址总线合并,从而能够实现减半地址总线数量。

[0177]

本公开实施例提供了一种信号采样电路,该信号采样电路包括输入采样电路、逻辑运算电路、指令译码电路和合并输出电路;其中,输入采样电路,用于根据第一时钟信号分别对第一片选信号和第一命令地址信号进行采样处理,得到第二片选信号和第二命令地址信号,第二命令地址信号中包括初始指令信号;逻辑运算电路,用于对第一时钟信号和第二片选信号进行逻辑运算,得到片选时钟信号;指令译码电路,用于根据片选时钟信号和第二片选信号对初始指令信号进行译码和采样处理,得到目标指令信号;合并输出电路,用于根据片选时钟信号对第二命令地址信号进行采样及输出合并处理,得到目标地址信号;其中,目标地址信号和目标指令信号之间的时序对齐。这样,基于该信号采样电路,在同一时钟周期的采样下,能够实现目标指令信号和目标地址信号的时序对齐,使得译码之后的指令信号和地址信号之间没有跟随pvt变化的偏差,从而可以避免下一级功能模块因时序偏差而出现问题。

[0178]

在本公开的另一实施例中,基于前述实施例所述的信号采样电路40,参见图10,其示出了本公开实施例提供的一种信号采样电路的详细结构示意图。如图10所示,信号采样电路40可以包括第一接收器601、第二接收器602、第三接收器603、第一采样电路604、第二采样电路605、第三采样电路606、第四采样电路607、第一缓冲器608、第一与门609、第二缓冲器610、第二与门611、指令译码触发器612、或门613、合并输出触发器614、第一功能模块615、第二功能模块616和第三功能模块617。其中,第一采样电路604和第二采样电路605是由d型触发器组成,第三采样电路606和第四采样电路607是由d型触发器和反相器组成;另外,指令译码触发器612的内部结构详见图7所示,合并输出触发器614的内部结构详见图8所示。

[0179]

在图10中,第一接收器601的输入信号为初始命令地址信号(用ca[13:0]表示)和参考信号(用vrefca表示),输出信号为第一命令地址信号(用ca表示);需要注意的是,对于初始命令地址信号ca[13:0],其并非是一个信号,而是代表一组信号,即ca[13]~ca[0];针对每一个信号都需要一个第一接收器601,故本公开实施例需要14个第一接收器601,图中仅示出一个第一接收器601作为示意;第二接收器602的输入信号为初始片选信号(用cs_n表示)和参考信号(用vrefca表示),输出信号为第一片选信号(用pcs表示);第三接收器603的输入信号为一对输入的互补时钟信号(用ck_t和ck_c表示),输出信号为第一时钟偶信号(用pclk_e表示)和第一时钟奇信号(用pclk_o表示)。然后,通过第一采样电路604,利用第一时钟偶信号对第一命令地址信号进行采样处理,得到第二命令地址偶信号(用ca[13:0]_e表示),且第二命令地址偶信号包括初始指令偶信号(用ca[4:0]_e表示);通过第二采样电路605,利用第一时钟奇信号对第一命令地址信号进行采样处理,得到第二命令地址奇信号(用ca[13:0]_o表示),且第二命令地址奇信号包括初始指令奇信号(用ca[4:0]_o表示);通过第三采样电路606,利用第一时钟偶信号对第一片选信号进行采样及反相处理,得到第二片选偶信号(用pcs_e表示);通过第四采样电路607,利用第一时钟奇信号对第一片选信号进行采样及反相处理,得到第二片选奇信号(用pcs_o表示);再利用第一缓冲器608和第一与门609对pclk_e信号和pcs_e信号进行逻辑运算,得到片选时钟偶信号(用cs_clk_e表示);利用第二缓冲器610和第二与门611对pclk_o信号和pcs_o信号进行逻辑运算,得到片选时钟奇信号(用cs_clk_o表示);紧接着,通过指令译码触发器612,利用cs_clk_e信号和cs_clk_o信号对ca[4:0]_e信号、ca[4:0]_o信号、pcs_e信号和pcs_o信号进行译码及采样处理,得到指令偶信号(用cmd_e表示)和指令奇信号(用cmd_o表示),再通过或门613对cmd_e和cmd_o进行或逻辑运算,得到目标指令信号(用cmd表示);以及通过合并输出触发器614,利用cs_clk_e信号和cs_clk_o信号对ca[13:0]_e信号和ca[13:0]_o信号进行采样处理,得到目标地址信号(用addr[13:0]表示)。此外,cmd信号和addr[13:0]信号与第一功能模块615、第二功能模块616和第三功能模块617之间均存在有长走线路径,但是需要控制cmd信号和addr[13:0]信号的长走线路径尽可能的长度和宽度一致,而且由于cmd信号和addr[13:0]信号的输出时序对齐,从而使得cmd信号和addr[13:0]信号到达不同的功能模块(例如,第一功能模块615、第二功能模块616和第三功能模块617等)去实现下一级功能时不会因为时序偏差出现错误。

[0180]

基于图10所示的信号采样电路,其对应的信号时序图如图11所示。在图11中,第一命令地址信号用ca表示,且ca可以包括cy、cz、c0、c1、c2和c3;初始片选信号用cs_n表示,第

一片选信号用pcs表示,pcs信号为低电平有效的脉冲信号,且脉冲宽度为预设时钟周期,pcs用于表征目标芯片被选中的信号;初始时钟信号用ck_t表示,第一时钟偶信号用pclk_e表示,第一时钟奇信号用pclk_o表示,且ck_t信号的时钟周期为预设时钟周期,pclk_e信号和pclk_o信号的时钟周期均为预设时钟周期的两倍。另外,pclk_e信号的上升沿所在的时钟周期作为偶数时钟周期,图11示出了一种第一片选信号在偶数时钟周期的上升沿采样为低电平时对应的信号时序示意图,即在利用pclk_e信号的上升沿对pcs信号进行采样及反相处理后,得到第二片选偶信号用pcs_e表示,其为高电平有效的脉冲信号,而且脉冲宽度为预设时钟周期的两倍;在利用pclk_o信号的上升沿对pcs信号进行采样及反相处理后,得到第二片选奇信号用pcs_o表示,其为低电平信号;在利用pclk_e信号的上升沿对ca信号进行采样处理后,得到初始指令偶信号(用ca[4:0]_e表示),其包括c0和c2;在利用pclk_o信号的上升沿对ca信号进行采样处理后,得到初始指令奇信号(用ca[4:0]_o表示),其包括c1和c3;另外,利用第一缓冲器608和第一与门609对pclk_e信号和pcs_e信号进行逻辑运算后,得到的片选时钟偶信号用cs_clk_e表示,其为高电平有效的脉冲信号,而且脉冲宽度为预设时钟周期;而利用第二缓冲器610和第二与门611对pclk_o信号和pcs_o信号进行逻辑运算后,得到片选时钟奇信号用cs_clk_o表示,其为低电平信号。这样,从图11中可以看出,只有cs_clk_e信号为有效信号,而且使得通过指令译码触发器612和或门613的译码及采样处理后得到的目标指令cmd信号与通过合并输出触发器614的采样处理后得到的目标地址addr[13:0]信号之间的时序对齐。

[0181]

需要注意的是,在图11中,在同一个时钟周期,对于pcs_e信号的上升沿和cs_clk_e信号的上升沿之间的延时,则是由第一缓冲器608和第一与门609等逻辑器件自身产生的。在本公开实施例中,为了避免cmd信号与addr[13:0]信号之间的输出偏差,这里可以利用相同的片选时钟信号(用cs_clk_e或cs_clk_o表示)进行译码采样,从而使得cmd信号与addr[13:0]信号之间的输出时序对齐,进而使得cmd信号和addr[13:0]信号到达不同的功能模块去实现下一级功能时不会因为时序偏差出现错误。

[0182]

本公开实施例提供了一种信号采样电路,通过本实施例对前述实施例的具体实现进行详细阐述,从中可以看出,本公开实施例是在已有的直接采样译码的基础上进行优化,使得译码后的指令(用cmd表示)和采样的地址总线(用addr[13:0]表示)之间没有随pvt变化的偏差。具体来说,在本公开实施例中,通过增加指令译码触发器和合并输出触发器,并且利用片选时钟信号来屏蔽第一片选信号为高电平(即无命令)时的时钟,再运用该片选时钟信号来进行一次采样,从而能够对齐cmd和addr[13:0];而且通过本公开实施例提供的合并输出触发器,将奇偶采样的地址总线合并,从而还能够实现减半地址总线数量。

[0183]

在本公开的又一实施例中,参见图12,其示出了本公开实施例提供的一种半导体存储器120的组成结构示意图。如图12所示,半导体存储器120可以包括前述实施例任一项所述的信号采样电路40。

[0184]

在本公开实施例中,半导体存储器120可以为dram芯片。

[0185]

进一步地,在一些实施例中,dram芯片符合ddr5内存规格。

[0186]

需要说明的是,本公开实施例主要涉及集成电路设计中输入信号采样及指令译码的相关电路,特别涉及dram芯片中,ca信号输入分别作为指令和地址采样和译码之后的控制调节电路。具体来说,本公开实施例是在已有的直接采样译码的基础上进行优化,使得译

码后的cmd信号和采样的addr[13:0]信号之间没有随pvt变化的偏差。

[0187]

还需要说明的是,本公开实施例可以应用于dram芯片中ca信号采样和译码的控制电路,但并不局限于此范围,其他输入信号采样及指令译码的相关电路均可采用此设计。

[0188]

这样,在本公开实施例中,对于半导体存储器120而言,其包括有信号采样电路40,因此,在同一时钟周期的采样下,能够实现目标指令信号和目标地址信号的时序对齐,使得译码之后的指令信号和地址信号之间没有跟随pvt变化的偏差,从而可以避免下一级功能模块因时序偏差而出现问题。

[0189]

以上,仅为本公开的较佳实施例而已,并非用于限定本公开的保护范围。

[0190]

需要说明的是,在本公开中,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者装置不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、物品或者装置所固有的要素。在没有更多限制的情况下,由语句“包括一个

……”

限定的要素,并不排除在包括该要素的过程、方法、物品或者装置中还存在另外的相同要素。

[0191]

上述本公开实施例序号仅仅为了描述,不代表实施例的优劣。

[0192]

本公开所提供的几个方法实施例中所揭露的方法,在不冲突的情况下可以任意组合,得到新的方法实施例。

[0193]

本公开所提供的几个产品实施例中所揭露的特征,在不冲突的情况下可以任意组合,得到新的产品实施例。

[0194]

本公开所提供的几个方法或设备实施例中所揭露的特征,在不冲突的情况下可以任意组合,得到新的方法实施例或设备实施例。

[0195]

以上,仅为本公开的具体实施方式,但本公开的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本公开揭露的技术范围内,可轻易想到变化或替换,都应涵盖在本公开的保护范围之内。因此,本公开的保护范围应以权利要求的保护范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1