一种存储单元对、阵列、存储电路、电子设备及方法

本技术涉及电子领域,具体涉及存储单元对、阵列、存储电路、电子设备及方法。

背景技术:

1、随着半导体工艺尺寸的不断缩小,摩尔定律放缓,漏电流的增加和互联延迟成为传统cmos存储器的瓶颈。寻找新一代存储技术的解决方案成为集成电路研究的重点,其中新型非易失性存储器由于其接近零静态功耗的特点,受到业界的广泛关注。新型非易失性存储器主要包括阻变存储器、相变存储器与磁存储器等,其主要特点是通过器件的高低阻态表示数据,而非易失存储器的电平,从而获得了可以忽略的漏电电流。

2、常见新型非易失性存储器的存储单元由一个选择单元(以nmos晶体管为主)和一个非易失存储器件构成,而随着cmos工艺尺寸的不断缩小,电源电压也随之降低,最小尺寸的nmos晶体管导通电阻又随之上升,使得选择晶体管的驱动压力逐渐增大,单个最小尺寸的nmos晶体管很难满足驱动需求,需要增大尺寸、提升电压或者降低速度,这些都不利于新型非易失性存储器的性能提升。

技术实现思路

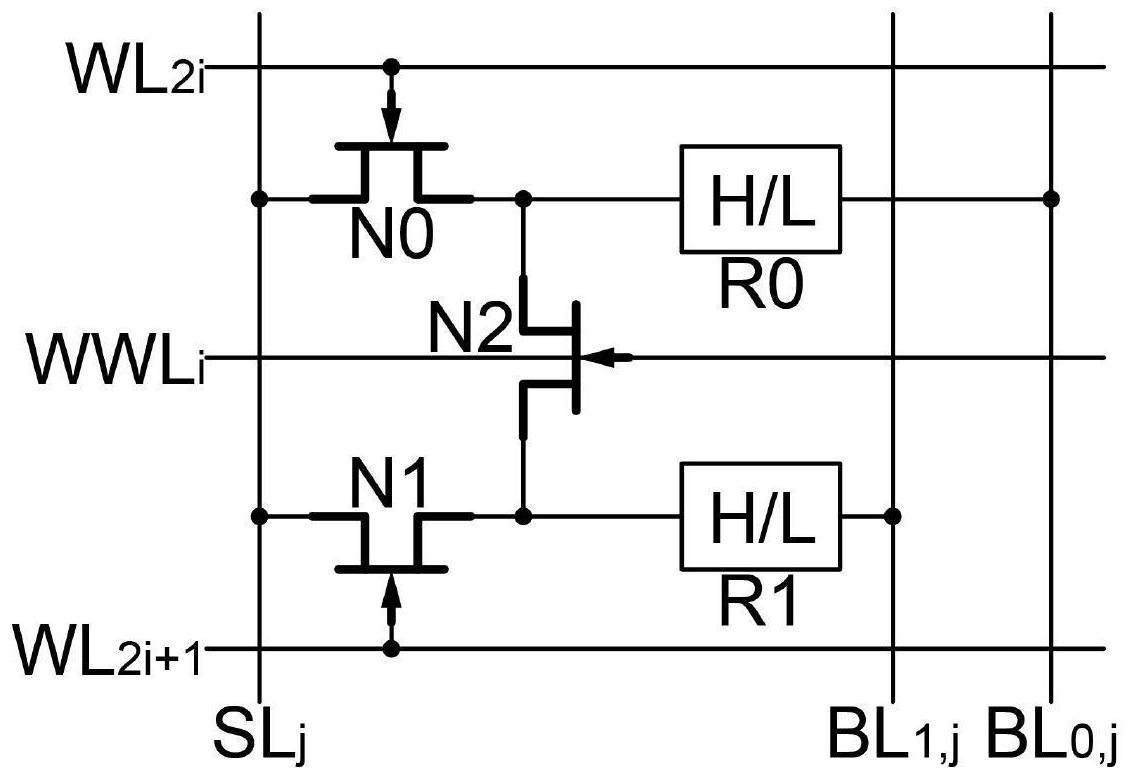

1、针对现有技术中的问题,本技术提供一种存储单元对以及基于所述存储单元对构成的存储单元对阵列、存储电路、电子设备,其中存储单元对包括:一对存储子单元以及一公共晶体管;每个存储子单元包括一独立晶体管和一存储元件;所述公共晶体管的控制极与一写字线耦接,其第一极和第二极各自耦接在一存储子单元的独立晶体管和存储元件之间。本发明通过公共晶体管与独立晶体管的串、并联,达到减小驱动电阻的目的,同时引入的公共晶体管合理布局于两个存储子单元之间的间隔处,在不增加面积的情况下,通过减小驱动电阻提升了存储单元的驱动能力。

2、本发明的一方面,提供一种存储单元对,包括:

3、一对存储子单元以及一公共晶体管;

4、每个存储子单元包括一独立晶体管和一存储元件;其中每个晶体管包括第一极、第二极以及控制所述第一极与第二极导通的控制极;

5、针对每个独立晶体管,其控制极与一字线耦接、其第一极与对应的存储元件一端耦接,每个独立晶体管的第二极耦接至一公共源线上,每个存储元件的另一端各自耦接一位线;

6、所述公共晶体管的控制极与一写字线耦接,其第一极和第二极各自耦接在一存储子单元的独立晶体管和存储元件之间。

7、在优选的实施例中,所述存储元件为存储电阻。

8、在优选的实施例中,所述公共晶体管为nmos晶体管和pmos晶体管中的其中一种。

9、在优选的实施例中,每个独立晶体管各自为nmos晶体管和pmos晶体管中的其中一种。

10、本发明的又一方面,提供一种存储单元对阵列,其包括多个阵列排布的存储单元对,每个存储单元对包括:

11、一对存储子单元以及一公共晶体管;

12、每个存储子单元包括一独立晶体管和一存储元件;其中每个晶体管包括第一极、第二极以及控制所述第一极与第二极导通的控制极;

13、针对每个独立晶体管,其控制极与一字线耦接、其第一极与对应的存储元件一端耦接,每个独立晶体管的第二极耦接至一公共源线上,每个存储元件的另一端各自耦接一位线;

14、所述公共晶体管的控制极与一写字线耦接,其第一极和第二极各自耦接在一存储子单元的独立晶体管和存储元件之间。

15、本发明的又一方面,提供一种存储电路,其包括至少一个存储单元对阵列,每个存储单元对阵列包括多个阵列排布的存储单元对,每个存储单元对包括:

16、一对存储子单元以及一公共晶体管;

17、每个存储子单元包括一独立晶体管和一存储元件;其中每个晶体管包括第一极、第二极以及控制所述第一极与第二极导通的控制极;

18、针对每个独立晶体管,其控制极与一字线耦接、其第一极与对应的存储元件一端耦接,每个独立晶体管的第二极耦接至一公共源线上,每个存储元件的另一端各自耦接一位线;

19、所述公共晶体管的控制极与一写字线耦接,其第一极和第二极各自耦接在一存储子单元的独立晶体管和存储元件之间。

20、本发明的又一方面,提供一种存储器,其包括存储电路,所述存储电路包括至少一个存储单元对阵列,每个存储单元对阵列包括多个阵列排布的存储单元对,每个存储单元对包括:

21、一对存储子单元以及一公共晶体管;

22、每个存储子单元包括一独立晶体管和一存储元件;其中每个晶体管包括第一极、第二极以及控制所述第一极与第二极导通的控制极;

23、针对每个独立晶体管,其控制极与一字线耦接、其第一极与对应的存储元件一端耦接,每个独立晶体管的第二极耦接至一公共源线上,每个存储元件的另一端各自耦接一位线;

24、所述公共晶体管的控制极与一写字线耦接,其第一极和第二极各自耦接在一存储子单元的独立晶体管和存储元件之间。

25、本发明的又一方面,提供一种电子设备,其包括存储器以及处理器,所述处理器用于执行所述存储器中存储的数据和/或程序,所述存储器包括存储电路,所述存储电路包括至少一个存储单元对阵列,每个存储单元对阵列包括多个阵列排布的存储单元对,每个存储单元对包括:

26、一对存储子单元以及一公共晶体管;

27、每个存储子单元包括一独立晶体管和一存储元件;其中每个晶体管包括第一极、第二极以及控制所述第一极与第二极导通的控制极;

28、针对每个独立晶体管,其控制极与一字线耦接、其第一极与对应的存储元件一端耦接,每个独立晶体管的第二极耦接至一公共源线上,每个存储元件的另一端各自耦接一位线;

29、所述公共晶体管的控制极与一写字线耦接,其第一极和第二极各自耦接在一存储子单元的独立晶体管和存储元件之间。

30、本发明的又一方面,提供一种存储单元对的写入方法,包括:

31、向任意一待写入的存储子单元中存储元件另一端耦接的位线接入第一电压;

32、向该存储子单元中独立晶体管的第一极耦接的源线接入第二电压;

33、向所述写字线和两个字线导入控制电压,以控制该存储子单元中的所述存储元件导通一设定方向电流,所述设定方向电流基于所述第一电压和所述第二电压的压差确定。

34、本发明的又一方面,提供一种存储单元对的读取方法,包括:

35、向任意一待读取的存储子单元存储元件另一端耦接的位线接入第三电压;

36、向该存储子单元中独立晶体管的第一极耦接的源线接入第四电压;

37、向该存储子单元中独立晶体管的控制极耦接的字线导入控制电压,获取所述存储子单元存储元件的电压值信息和电流值信息,所述电压值信息是基于所述第三电压和所述第四电压的压差确定;

38、根据所述电压值信息和电流值信息,确定该存储子单元中的存储信息。

39、本发明的又一方面,提供一种存储单元对的制作方法,包括:

40、在同一刻蚀工艺步骤下在一衬底上形成一对存储子单元以及一公共晶体管;每个存储子单元包括一独立晶体管和一存储元件;其中每个晶体管包括第一、第二极以及控制所述第一极与第二极导通的控制极;

41、针对每个独立晶体管,将其控制极与一字线耦接、将其第一极与对应的存储元件一端耦接,将其第二极与一公共源线耦接,并将每个存储元件的另一端各自耦接在一位线上;

42、将所述公共晶体管的控制极与一写字线耦接,将其第一极和第二极各自耦接在一存储子单元的独立晶体管和存储元件之间。

43、由上述技术方案可知,本技术提供的一种存储单元对、阵列、存储电路、电子设备及方法,其中存储单元对包括:一对存储子单元以及一公共晶体管;每个存储子单元包括一独立晶体管和一存储元件;其中每个晶体管包括第一极、第二极以及控制所述第一极与第二极导通的控制极;所述公共晶体管的控制极与一写字线耦接,其第一极和第二极各自耦接在一存储子单元的独立晶体管和存储元件之间。本发明通过公共晶体管与独立晶体管的串、并联,达到减小驱动电阻的目的,同时引入的公共晶体管合理布局于两个存储子单元之间的间隔处,在不增加面积的情况下,通过减小驱动电阻提升了存储单元的驱动能力。

- 还没有人留言评论。精彩留言会获得点赞!