集成电路、存储器电路及用于数据存取的方法与流程

1.本技术涉及存储器电路,且更具体来说,涉及集成电路、存储器电路及用于数据存取的方法。

背景技术:

2.在集成电路中,存储器电路提供用于数据存取的高容量存储器。在一些集成电路中,将一个或多个存储器管芯与封装中的系统管芯接合(bonded),以用于高效的数据存取。存储器管芯与系统管芯包括传统的输入/输出(input/output,i/o)界面及存储器控制电路,以彼此进行通信。然而,随着接合(bonding)技术取得进步,以在存储器管芯与系统管芯之间提供高效的电通信,传统的输入/输出界面及存储器控制电路可能对数据存取效率产生不利的影响。

技术实现要素:

3.本公开的实施例提供一种集成电路、存储器电路及用于数据存取的方法。

4.这些实施例包括一种存储器电路。存储器电路包括:存储器单元阵列;以及输入/输出(i/o)连接界面,耦合到存储器单元阵列。i/o连接界面被配置用于耦合到外部信号线,以从外部存储器控制器直接接收晶体管级操作信号,以用于存取存储器单元阵列中的数据。

5.这些实施例还包括一种用于数据存取的方法。方法包括接收晶体管级操作信号,晶体管级操作信号对应于读取操作或写入操作;接收晶体管级地址信号;以及根据晶体管级操作信号传送或接收晶体管级数据信号。

6.这些实施例还包括一种集成电路。集成电路包括:存储器电路,包括存储器单元阵列;以及系统芯片(system-on-chip,soc)电路,通过内连件耦合到存储器电路且被配置成:通过第一多个内连件向存储器电路传送晶体管级操作信号及晶体管级地址信号,晶体管级操作信号对应于读取操作或写入操作;以及通过第二多个内连件向存储器电路传送晶体管级数据信号或从存储器电路接收晶体管级数据信号。

7.应理解,前面的一般性说明及以下详细说明仅为示例性的阐释,不用于限制本发明。

附图说明

8.图1a示出传统的集成电路的截面图;

9.图1b示出传统的集成电路的方块图;

10.图2示出传统的双倍数据速率(double data rate,ddr)同步动态随机存取存储器(synchronous dynamic random-access memory,sdram)的方块图;

11.图3示出根据本公开一些实施例的包括soc管芯及存储器管芯的示例性集成电路的截面图;

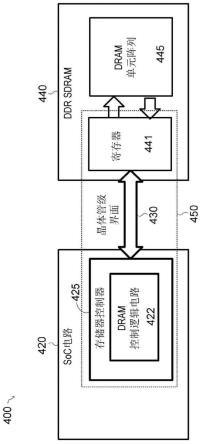

12.图4及图5示出根据本公开一些实施例的包括soc电路及存储器电路的示例性集成电路的方块图;

13.图6示出根据本公开一些实施例的示例性存储器电路的方块图;

14.图7是根据本公开一些实施例的示例性存储器电路的示例性时序图;

15.图8是根据本公开一些实施例的用于示例性存储器电路中的数据存取的示例性方法的流程图。

16.[符号的说明]

[0017]

100、300、400、500:集成电路

[0018]

120、320:soc管芯

[0019]

121:ddr i/o电路

[0020]

122、142:物理(phy)界面电路

[0021]

123:ddr控制逻辑电路

[0022]

125、425、525:存储器控制器

[0023]

130:ddr界面

[0024]

131、133:微凸块

[0025]

132:导电线

[0026]

140、200、440、540:ddr sdram

[0027]

141:ddr i/o电路

[0028]

143:ddr phy界面电路

[0029]

144:逻辑管芯

[0030]

145、240、445、545、630:dram单元阵列

[0031]

146-1、146-2、146-3、146-4:动态随机存取存储器(dram)管芯

[0032]

150、450、550:存储器存取电路

[0033]

160:中介层

[0034]

180:封装衬底

[0035]

210、620:电力产生器

[0036]

220:命令解码器

[0037]

222:存储库控制逻辑电路

[0038]

230:地址寄存器

[0039]

231:列计数器

[0040]

232:刷新计数器

[0041]

241、631:行解码器

[0042]

242、632:列解码器

[0043]

250:写入驱动器及读取感测放大器

[0044]

260:数据寄存器

[0045]

270:i/o驱动器

[0046]

280:数据路径控制器

[0047]

310、422:dram控制逻辑电路

[0048]

321、322、323、324:无凸块内连件

[0049]

330、350、370:dram管芯

[0050]

380:封装衬底

[0051]

420、520:soc电路

[0052]

430、530:晶体管级界面

[0053]

441、541:寄存器

[0054]

600:dram

[0055]

610:i/o连接界面

[0056]

612:数据i/o连接界面

[0057]

640:驱动器

[0058]

650:读取感测放大器

[0059]

660:输入数据寄存器

[0060]

670:输出数据寄存器

[0061]

700:时序图

[0062]

710:激活

[0063]

720、730:读取

[0064]

740、750:写入

[0065]

760:预充电

[0066]

800:方法

[0067]

810、820、830、840:步骤

[0068]

act:激活信号

[0069]

address:输入地址信号

[0070]

ca、column address:列地址信号

[0071]

cas:列地址选通

[0072]

ck:时钟信号

[0073]

ck_b:第二时钟信号

[0074]

ck_t:第一时钟信号

[0075]

cke:时钟使能信号

[0076]

col-1、col-4:列地址

[0077]

col-2:第二列地址

[0078]

col-3:第三列地址

[0079]

command:命令信号

[0080]

csl:列选择线信号

[0081]

dm:数据屏蔽信号

[0082]

dq:输入数据信号/输出数据信号

[0083]

dqs:数据总线选通信号

[0084]

r0、r1、r2、r3、w0、w1、w2、w3:数据

[0085]

ra、row address:行地址信号

[0086]

ras:行地址选通

[0087]

rdq:晶体管级读取数据信号/读取数据信号/晶体管级数据信号

[0088]

rdqs:读取数据选通信号

[0089]

saen:感测放大器使能信号

[0090]

tsv:硅穿孔

[0091]vext

:输入电力/外部电力

[0092]

wdm:写入数据屏蔽信号

[0093]

wdq:写入数据信号

[0094]

wdqs:数据选通信号

[0095]

wr:控制信号

具体实施方式

[0096]

图1a示出传统的集成电路100的截面图。集成电路100包括soc管芯120、逻辑管芯144、动态随机存取存储器(dram)管芯146-1、146-2、146-3及146-4、中介层160以及封装衬底180。逻辑管芯144以及dram管芯146-1、146-2、146-3及146-4通过硅穿孔(through-silicon via,tsv)(未标记)、微凸块(未标记)及金属线(未标记)内连在一起作为多个dram。soc管芯120与逻辑管芯144分别通过微凸块131及133以及多个微凸块与中介层160内连。中介层160也通过多个微凸块与封装衬底180内连。中介层160包括从soc管芯120及逻辑管芯144到封装衬底180的连接路径以及soc管芯120与逻辑管芯144之间的内连路径。

[0097]

soc管芯120包括物理(physical,phy)界面电路122。逻辑管芯144包括物理(phy)界面电路142。soc管芯120的phy界面电路122通过中介层160以通信方式耦合到逻辑管芯144的phy界面电路142。举例来说,phy界面电路122与phy界面电路142之间的内连路径中的一者包括微凸块131、导电线132及微凸块133。

[0098]

图1b示出集成电路100的方块图。集成电路100包括soc管芯120及ddr sdram 140。逻辑管芯144以及dram管芯146-1、146-2、146-3及146-4(图1a)被实施成ddr sdram 140(图1b)。如图1b中所示,soc管芯120包括ddr i/o电路121、ddr控制逻辑电路123及存储器控制器125。存储器控制器125经由ddr phy界面(ddr phy interface,dfi)而与ddr控制逻辑电路123进行通信,以用于存取ddr sdram 140中的数据。ddr控制逻辑电路123控制ddr i/o电路121与ddr sdram 140进行通信。ddr sdram 140包括ddr i/o电路141、ddr phy界面电路143及dram单元阵列145。ddr phy界面电路143以通信方式耦合到dram单元阵列145且控制ddr i/o电路141与soc管芯120进行通信。soc管芯120的ddr i/o电路121与ddr sdram 140的ddr i/o电路141经由ddr界面130彼此进行通信。举例来说,ddr界面130可包括短截线串联端接逻辑(stub series terminated logic,sstl)界面。

[0099]

当soc管芯120需要存取ddr sdram 140中的数据时,存储器控制器125经由dfi向ddr控制逻辑电路123发送控制信号。根据控制信号,ddr控制逻辑电路123控制ddr i/o电路121经由ddr界面130向ddr sdram 140的ddr i/o电路141传送操作信号、地址信号和/或数据信号。ddr phy界面电路143经由ddr i/o电路141接收操作信号、地址信号和/或数据信号;对操作信号进行解码;以及在操作信号对应于写入操作的情况下控制ddr sdram 140存储数据,或者在操作信号对应于读取操作的情况下控制ddr sdram 140经由ddr i/o电路141向soc管芯120提供数据。当ddr sdram 140在读取操作中提供数据时,ddr控制逻辑电路123控制ddr i/o电路121从ddr i/o电路141接收数据信号和/或控制信号。ddr控制逻辑电

路123可经由dfi向存储器控制器125通知数据接收。

[0100]

ddr i/o电路121及ddr i/o电路141驱动和/或缓冲soc管芯120与ddr sdram 140之间的操作信号、地址信号、数据信号和/或控制信号,以确保信号在两个集成电路管芯(即soc管芯120与ddr sdram 140)之间正确地进行交换。信号的驱动和/或缓冲会针对soc管芯120与ddr sdram 140之间的内连电阻改善信号强度。举例来说,如图1a中所示,phy界面电路122经由多个内连路径连接到phy界面电路142。内连路径中的一者包括微凸块131、导电线132及微凸块133。微凸块131及133具有高电阻,且高电阻可能导致高内连电阻,高内连电阻会引起电阻/电容(resistance/capacitance,rc)延迟。ddr i/o电路121及ddr i/o电路141包括驱动电路和/或缓冲电路,以针对高内连电阻及rc延迟而驱动和/或缓冲信号,从而在soc管芯120与ddr sdram 140之间正确地交换信号。

[0101]

在集成电路100(图1b)中,存储器存取电路150包括ddr i/o电路121、ddr控制逻辑电路123、ddr界面130、ddr i/o电路141及ddr phy界面电路143。因此,在传统的集成电路中要求存储器存取电路150以用于集成电路芯片之间的数据存取。

[0102]

图2示出传统的ddr sdram 200的方块图。ddr sdram 200可被实施成ddr sdram 140(图1b)。ddr sdram 200包括电力产生器210、命令解码器220、存储库(bank)控制逻辑电路222、地址寄存器230、列计数器231、刷新计数器232、dram单元阵列240、行解码器241、列解码器242、写入驱动器及读取感测放大器250、数据寄存器260、i/o驱动器270及数据路径控制器280。

[0103]

电力产生器210接收外部电力(v

ext

),产生内部电力,且将内部电力供应到ddr sdram 200的其他组件(例如dram单元阵列240)。

[0104]

命令解码器220被配置成接收命令信号(command)、时钟信号(ck)及时钟使能信号(cke);将命令信号解码成存储库控制信号及地址控制信号;以及向存储库控制逻辑电路222传送存储库控制信号且向地址寄存器230传送地址控制信号。

[0105]

地址寄存器230被配置成从命令解码器220接收输入地址信号(address)及地址控制信号;向存储库控制逻辑电路222提供地址信息;分别向行解码器241及列解码器242提供行地址及列地址;以及分别与列计数器231及刷新计数器232进行通信,以用于列计数及刷新计数。

[0106]

存储库控制逻辑电路222被配置成从命令解码器220接收存储库控制信号且从地址寄存器230接收地址信息;以及向行解码器241提供行地址控制信号,向数据路径控制器280提供数据路径控制信号,且向写入驱动器及读取感测放大器250提供读取/写入控制信号。

[0107]

行解码器241被配置成从地址寄存器230接收行地址且从存储库控制逻辑电路222接收行地址控制信号且选择dram单元阵列240中的一行或多行的存储器单元。列解码器242被配置成从地址寄存器230接收列地址且选择dram单元阵列240中的一列或多列的存储器单元。dram单元阵列240包括被排列成行及列的多个存储器单元。基于所选择的行及列,将存储器单元中的一些存储器单元激活,以用于数据存取。

[0108]

如果命令信号(command)指示写入操作,则写入驱动器及读取感测放大器250驱动来自数据寄存器260的数据信号且提供将被存储在激活的存储器单元中的经驱动数据信号。如果命令信号(command)指示读取操作,则写入驱动器及读取感测放大器250感测并放

大来自激活的存储器单元的数据信号,且将经放大数据信号提供到数据寄存器260。数据寄存器260保存用于写入操作的来自i/o驱动器270的输入数据信号以及用于读取操作的来自写入驱动器及读取感测放大器250的经放大数据信号。

[0109]

i/o驱动器270被配置成接收数据总线选通信号(dqs)、输入数据信号(dq)和/或数据屏蔽信号(dm)且将输入数据信号提供到数据寄存器260以用于写入操作;以及从数据寄存器260接收数据信号,增强数据信号的驱动能力,且将增强的数据信号作为输出数据信号(dq)提供到数据总线以用于读取操作。

[0110]

数据路径控制器280被配置成与存储库控制逻辑电路222进行通信且控制写入驱动器及读取感测放大器250、数据寄存器260及i/o驱动器270处理用于写入操作及读取操作的数据信号。

[0111]

在传统的集成电路100中,使用中介层160(图1a)将soc管芯120与逻辑管芯144内连。然而,将中介层160接合到集成电路100中会导致额外的成本且增加集成电路100的封装大小。此外,使用包括ddr i/o电路121、ddr控制逻辑电路123、ddr界面130、ddr i/o电路141及ddr phy界面电路143的存储器存取电路150(图1b)来克服soc管芯120与ddr sdram 140之间的内连处的高电阻和/或rc延迟。然而,存储器存取电路150引起附加的存取等待时间(latency),消耗额外的电力,且要求soc管芯120及ddr sdram 140中的特定电路面积。因此,存储器存取电路150会增加集成电路100的功耗及电路面积且对数据存取效率产生不利的影响。举例来说,i/o驱动器270(图2)可具有相当大的电路面积且消耗相当大的电力。命令解码器220(图2)可增加存取等待时间且消耗特定的电力。

[0112]

图3示出根据本公开一些实施例的包括soc管芯及存储器管芯的示例性集成电路300的截面图。集成电路300包括soc管芯320、dram管芯330、350及370以及封装衬底380。dram管芯330、350及370通过tsv内连在一起作为多个dram。soc管芯320通过多个无凸块内连件(未全部示出)(包括无凸块内连件321、322、323及324)与dram管芯330内连,且通过多个微凸块内连件(未标记)与封装衬底380内连。无凸块内连件不包括微凸块,且因此不具有高电阻且不会在soc管芯320与dram管芯330之间的内连处引起显著的rc延迟。因此,soc管芯320被配置成通过使用晶体管级信号(transistor-level signal)存取同一管芯上的存储器来存取dram管芯330、350及370中的数据。

[0113]

如本文中所使用的,晶体管级信号被定义为两个晶体管之间的电信号,电信号的电压电平及电流电平足以使两个晶体管正确地进行操作。由于传统的集成电路芯片或管芯之间的高电阻和/或显著的rc延迟,因此可能无法在传统的集成电路芯片或管芯之间正确地传送晶体管级信号。

[0114]

集成电路300的dram管芯330、350及370是存储器电路且包括用于存储数据的存储器单元阵列。集成电路300的soc管芯320包括soc电路且以通信方式耦合到dram管芯330、350及370中的存储器电路。soc管芯320可包括一个或多个处理电路,例如一个或多个图形处理单元(graphical processing unit,gpu)、一个或多个中央处理单元(central processing unit,cpu)、一个或多个专用集成电路(application-specific integrated circuit,asic)和/或用于各种应用的任何其他逻辑电路。soc管芯320被配置成通过无凸块内连件中的一者或多者向dram管芯330、350和/或370中的存储器电路传送晶体管级操作信号及晶体管级地址信号,以用于数据存取。

[0115]

晶体管级操作信号对应于读取、写入或其他存储器操作。晶体管级地址信号包括存储器地址。如果晶体管级操作信号对应于写入操作,则soc管芯320被配置成通过多个无凸块内连件(包括无凸块内连件321、322、323及324)中的一者或多者向位于dram管芯330、350和/或370的存储器电路中的存储器地址处的多个存储器单元传送晶体管级数据信号。晶体管级数据信号包括soc管芯320打算写入到dram管芯330、350和/或370的存储器电路中的数据。如果晶体管级操作信号对应于读取操作,则soc管芯320被配置成通过多个无凸块内连件(包括无凸块内连件321、322、323及324)中的一者或多者从位于dram管芯330、350和/或370的存储器电路中的存储器地址处的多个存储器单元接收晶体管级数据信号。晶体管级数据信号包括soc管芯320打算从dram管芯330、350和/或370的存储器电路读取的数据。

[0116]

在一些实施例中,soc管芯320包括dram控制逻辑电路310,dram控制逻辑电路310被配置成通过多个无凸块内连件(包括无凸块内连件321、322、323及324)中的一者或多者向dram管芯330、350和/或370的存储器电路传送晶体管级操作信号及晶体管级地址信号;以及通过多个无凸块内连件(包括无凸块内连件321、322、323及324)中的一者或多者向存储器电路传送晶体管级数据信号或从存储器电路接收晶体管级数据信号。

[0117]

表1示出本文中公开的示例性dram与由联合电子器件工程委员会(joint electron device engineering council,jedec)固态技术协会(solid state technology association)规定的低功率双倍数据速率(low-power double data rate,lpddr)sdram、低功率双倍数据速率2(low-power double data rate 2,lpddr2)sdram、低功率双倍数据速率3(low-power double data rate 3,lpddr3)sdram及低功率双倍数据速率4(low-power double data rate 4,lpddr4)sdram之间的i/o界面参数的比较。

[0118]

表1 i/o界面的比较

[0119][0120]

dram管芯330、350和/或370可为表1的第一行中的示例性dram。dram包括互补金属氧化物半导体(complementary metal-oxide semiconductor,cmos)界面。cmos界面使得两个金属氧化物半导体(metal-oxide semiconductor,mos)晶体管之间的电信号能够处于足以使两个晶体管正确地进行操作的电压电平及电流电平处。电压电平(即输出级漏极电源电压(vddq))为0.6伏(v)。电流电平(即驱动电流)为4毫安(ma)。dram的数据输入及输出具有0.4皮法(pf)到0.6皮法(pf)的i/o电容(i/o cap.)。dram的控制及地址输入具有0.4pf到0.6pf的控制/地址电容(c/a cap.)。cmos界面不需要端接。

[0121]

lpddr包括低电压cmos(low voltage cmos,lvcmos)界面。lvcmos界面要求1.8v或1.2v的vddq及60ma的驱动电流。lvcmos界面具有3pf到5pf的数据i/o电容及1.5pf到3pf的c/a电容。lvcmos界面要求端接,且lvcmos界面的终端级(terminal level)为vddq/2。lpddr2及lpddr3二者包括高速未端接逻辑(high speed unterminated logic,hsul)界面。hsul界面要求1.2v的vddq及30ma的驱动电流。lpddr2的hsul界面具有1.25pf到2.5pf的数

据i/o电容及1pf到2pf的c/a电容。lpddr3的hsul界面具有1pf到1.8pf的数据i/o电容及0.5pf到1.1pf的c/a电容。hsul界面要求端接,且hsul界面的终端级为vddq/2。lpddr4包括低电压摆幅端接逻辑(low voltage swing terminated logic,lvstl)界面。lvstl界面要求1.1v或1.6v的vddq及18ma的驱动电流。lvstl界面具有0.7pf到1.3pf的数据i/o电容及0.5pf到0.9pf的c/a电容。lvstl界面要求端接,且lvstl界面的终端级是输出级电源电压(vssq)。

[0122]

如表1中所示,示例性dram的cmos界面要求比lpddr的lvcmos界面、lpddr2及lpddr3的hsul界面以及lpddr4的lvstl界面低的数据i/o电容。较低的vddq的原因中的一者是例如dram管芯330与soc管芯320之间的多个无凸块内连件的低电阻。此外,示例性dram的cmos界面具有比lpddr的lvcmos界面、lpddr2及lpddr3的hsul界面以及lpddr4的lvstl界面低的数据i/o电容及低的c/a电容。因此,例如dram管芯330与soc管芯320之间的电信号的rc延迟(即信号延迟)小于例如处理器与lpddr、lpddr2、lpddr3及lpddr4中的任意者之间的rc延迟。因此,soc管芯320可如存取同一管芯上的存储器那般存取dram管芯330中的数据。dram管芯330与soc管芯320之间的电信号类似于cmos晶体管之间的电信号,且因此被定义为晶体管级信号。另外,cmos界面不要求端接。因此,cmos界面的电流消耗远低于lvcmos界面、hsul界面及lvstl界面的电流消耗。

[0123]

图4示出根据本公开一些实施例的包括soc电路及存储器电路的示例性集成电路400的方块图。集成电路400可被实施、制造及接合成集成电路300(图3)。集成电路400包括soc电路420及ddr sdram 440。soc电路420对应于soc管芯320。ddr sdram 440对应于dram管芯330、350及370中的一者或多者。soc电路420与ddr sdram 440通过晶体管级界面430彼此以通信方式耦合。晶体管级界面430包括位于soc电路420与ddr sdram 440之间的多个内连件(例如多个无凸块内连件(包括无凸块内连件321、322、323及324(图3)))。soc电路420包括存储器控制器425。存储器控制器425包括dram控制逻辑电路422。ddr sdram 440包括寄存器441及dram单元阵列445。

[0124]

在一些实施例中,soc电路420的存储器控制器425被配置成通过晶体管级界面430的内连件中的一者或多者向ddr sdram 440传送晶体管级操作信号及晶体管级地址信号,以用于存取ddr sdram 440中的数据。存储器控制器425还被配置成通过晶体管级界面430的内连件中的一者或多者向ddr sdram 440传送晶体管级数据信号或从ddr sdram 440接收晶体管级数据信号。

[0125]

当晶体管级操作信号对应于写入操作时,ddr sdram 440的寄存器441被配置成从soc电路420直接接收晶体管级数据信号且保存晶体管级数据信号中携带的数据。寄存器441还被配置成提供将被写入到dram单元阵列445中的数据。dram单元阵列445被配置成根据晶体管级地址信号中的存储器地址来存储数据。

[0126]

当晶体管级操作信号对应于读取操作时,dram单元阵列445被配置成根据晶体管级地址信号中的存储器地址来提供数据。寄存器441被配置成接收及保存来自dram单元阵列445的数据。寄存器441还被配置成通过晶体管级界面430将数据作为晶体管级数据信号直接传送到soc电路420。

[0127]

在一些实施例中,存储器控制器425被配置成与dram控制逻辑电路422进行通信,以用于存取ddr sdram 440中的数据。根据与存储器控制器425的通信,dram控制逻辑电路

422被配置成通过晶体管级界面430的内连件中的一者或多者向ddr sdram 440传送晶体管级操作信号及晶体管级地址信号。dram控制逻辑电路422还被配置成通过晶体管级界面430的内连件中的一者或多者向ddr sdram 440传送晶体管级数据信号或从ddr sdram 440接收晶体管级数据信号。

[0128]

寄存器441及dram单元阵列445被配置成当存储器控制器425传送晶体管级操作信号及晶体管级地址信号时,与上述操作类似地进行操作。

[0129]

在集成电路400(图4)中,存储器存取电路450包括存储器控制器425、晶体管级界面430及寄存器441。存储器存取电路450用于soc电路420与ddr sdram 440之间的数据存取。与存储器存取电路150(图1b)相比,存储器存取电路450不包括ddr i/o电路121、ddr控制逻辑电路123、ddr i/o电路141及ddr phy界面电路143的对应物。由于soc电路420与ddr sdram 440可交换晶体管级信号,因此soc电路420能够仅通过存储器存取电路450存取dram单元阵列445中的数据。与传统的集成电路100相比,使用存储器存取电路450而不是存储器存取电路150会在集成电路400中实现更短的存取等待时间、更少的功耗及更小的用于数据存取的物理面积。

[0130]

图5示出根据本公开一些实施例的包括soc电路及存储器电路的示例性集成电路500的方块图。集成电路500可被实施、制造及接合成集成电路300(图3)。集成电路500包括soc电路520及ddr sdram 540。soc电路520对应于soc管芯320。ddr sdram 540对应于dram管芯330、350及370中的一者或多者。soc电路520与ddr sdram 540通过晶体管级界面530彼此以通信方式耦合。晶体管级界面530包括位于soc电路520与ddr sdram 540之间的多个内连件(例如多个无凸块内连件(包括无凸块内连件321、322、323及324(图3)))。soc电路520包括存储器控制器525。ddr sdram 540包括寄存器541及dram单元阵列545。

[0131]

soc电路520的存储器控制器525被配置成通过晶体管级界面530的内连件中的一者或多者向ddr sdram 540传送晶体管级操作信号及晶体管级地址信号,以用于存取ddr sdram 540中的数据。存储器控制器525还被配置成通过晶体管级界面530的内连件中的一者或多者向ddr sdram 540传送晶体管级数据信号或从ddr sdram 540接收晶体管级数据信号。

[0132]

寄存器541及dram单元阵列545被配置成与以上参照图4针对寄存器441及dram单元阵列445所示的操作类似地进行操作。

[0133]

在集成电路500(图5)中,存储器存取电路550包括存储器控制器525、晶体管级界面530及寄存器541。存储器存取电路550用于soc电路520与ddr sdram 540之间的数据存取。与存储器存取电路150(图1b)相比,存储器存取电路550不包括ddr i/o电路121、ddr控制逻辑电路123、ddr i/o电路141及ddr phy界面电路143的对应物。由于soc电路520与ddr sdram 540可交换晶体管级信号,因此soc电路520能够仅通过存储器存取电路550存取dram单元阵列545中的数据。与传统的集成电路100相比,使用存储器存取电路550而不是存储器存取电路150会在集成电路500中实现更短的存取等待时间、更少的功耗及更小的用于数据存取的物理面积。

[0134]

图6示出根据本公开一些实施例的示例性dram 600的方块图。dram 600可被实施成dram管芯330、350及370(图3)、ddr sdram 440(图4)和/或ddr sdram 540(图5)。dram 600包括i/o连接界面610、电力产生器620、dram单元阵列630、行解码器631、列解码器632、

写入驱动器640、读取感测放大器650、输入数据寄存器660及输出数据寄存器670。dram单元阵列630对应于dram单元阵列445(图4)和/或545(图5)。输入数据寄存器660和/或输出数据寄存器670对应于寄存器441(图4)和/或541(图5)。

[0135]

i/o连接界面610包括多条导电线,多条导电线被配置成接收外部电力(v

ext

)、存储库控制信号、时钟信号(ck)、行地址信号(row address)、列地址信号(column address)、写入数据选通信号(wdqs)、写入数据信号(wdq)、写入数据屏蔽信号(wdm)及读取数据选通信号(rdqs);以及传送读取数据信号(rdq)。

[0136]

dram 600的i/o连接界面610被配置用于耦合到外部信号线,以从外部存储器控制器直接接收晶体管级操作信号,以用于存取存储器单元阵列中的数据。举例来说,当dram 600被实施成ddr sdram 540(图5)时,dram单元阵列630对应于dram单元阵列545。i/o连接界面610被配置用于耦合到位于ddr sdram 540与soc电路520之间的多条信号线(未示出),以直接从存储器控制器525接收晶体管级操作信号,以用于存取dram单元阵列545中的数据。信号线是晶体管级界面530的一部分,且因此是ddr sdram 540(即,dram 600)的外部信号线。来自存储器控制器525的晶体管级操作信号包括存储库控制信号、写入数据选通信号(wdqs)和/或读取数据选通信号(rdqs)。

[0137]

当soc电路520打算将数据写入到ddr sdram 540(即,dram 600)中时,存储器控制器525被配置成将用于控制写入驱动器640的存储库控制信号及写入数据选通信号(wdqs)作为晶体管级操作信号传送到ddr sdram 540(即,dram 600)。因此,dram 600(即,ddr sdram 540)的i/o连接界面610被配置用于耦合到晶体管级界面530的信号线,以直接接收来自存储器控制器525的用于控制写入驱动器640的存储库控制信号及写入数据选通信号(wdqs),从而将数据写入到dram单元阵列545。如本文中所使用的,直接接收存储库控制信号及写入数据选通信号(wdqs)意味着通过i/o连接界面610接收来自存储器控制器525的这些信号,而不通过其他电路进行缓冲或增强。

[0138]

在一些实施例中,晶体管级操作信号是互补金属氧化物半导体(cmos)级信号。举例来说,如参照图5所示,晶体管级界面530包括位于soc电路520与ddr sdram 540之间的多个内连件(例如多个无凸块内连件(包括无凸块内连件321、322、323及324(图3)))。晶体管级界面530的内连件不具有高电阻,且因此不会对soc电路520与ddr sdram 540之间的内连引起显著的rc延迟。因此,soc电路520的存储器控制器525被配置成以用于晶体管之间而不是集成电路芯片之间通信的电压电平和/或电流电平传送存储库控制信号、写入数据选通信号(wdqs)和/或读取数据选通信号(rdqs)。在一些实施例中,soc电路520及ddr sdram 540各自包括cmos电路。存储器控制器525被配置成以用于soc电路520的cmos晶体管与ddr sdram 540的cmos晶体管之间通信的电压电平和/或信号强度传送存储库控制信号、写入数据选通信号(wdqs)和/或读取数据选通信号(rdqs)。

[0139]

电力产生器620被配置成经由i/o连接界面610从外部电源接收输入电力(v

ext

)。电力产生器620还被配置成基于输入电力(v

ext

)产生内部电力。电力产生器620被配置成将内部电力供应到dram单元阵列630和/或dram 600的其他组件。

[0140]

在一些实施例中,dram不包括电力产生器,或者,dram的组件由一个或多个外部电源供应电力。

[0141]

dram单元阵列630包括多个dram单元,即存储器单元。dram单元被排列成行及列。

每一dram单元包括例如通过传递晶体管(pass transistor)连接到列线(或数字线或位线)的电容器。列线连接到被排列成列的多个dram单元。行线(或字线)也连接到被排列成行的多个dram单元。根据来自存储器控制器(例如,存储器控制器525)的存储器地址来选择dram单元的行线及列线。

[0142]

行解码器631包括行地址解码器(即解码电路)且耦合到dram单元阵列630。行解码器631还被耦合以经由i/o连接界面610直接接收外部产生的晶体管级行地址信号(row address)。如本文中所使用的,经由i/o连接界面610直接接收晶体管级行地址信号意味着行解码器631经由i/o连接界面610接收输入到dram 600的晶体管级行地址信号(row address),而不进行信号缓冲或驱动能力的增强。举例来说,存储器控制器525(图5)被配置成产生晶体管级行地址信号(row address)且将晶体管级行地址信号(row address)传送到ddr sdram 540(即,dram 600)。存储器控制器525是ddr sdram 540(即,dram600)的外部电路。在行解码器631对晶体管级行地址信号(row address)进行解码之后,行解码器631被配置成基于晶体管级行地址信号(row address)中的行地址来选择dram单元阵列630中的sdram单元的行线中的一者或多者。

[0143]

列解码器632包括列地址解码器(即解码电路)且耦合到dram单元阵列630。列解码器632还被耦合以经由i/o连接界面610直接接收外部产生的晶体管级列地址信号(column address)。如本文中所使用的,经由i/o连接界面610直接接收晶体管级列地址信号意味着列解码器632经由i/o连接界面610接收输入到dram 600的晶体管级列地址信号(column address),而不进行信号缓冲或驱动能力的增强。举例来说,存储器控制器525(图5)被配置成产生晶体管级列地址信号(column address)且将晶体管级列地址信号(column address)传送到ddr sdram 540(即,dram 600)。存储器控制器525是ddr sdram 540(即,dram 600)的外部电路。在列解码器632对晶体管级列地址信号(column address)进行解码之后,列解码器632被配置成基于晶体管级列地址信号(column address)中的列地址来选择dram单元阵列630中的dram单元的列线中的一者或多者。

[0144]

写入驱动器640包括耦合在输入数据寄存器660与dram单元阵列630之间的写入驱动器电路。写入驱动器640被配置成驱动来自输入数据寄存器660的将被写入到dram单元阵列630中的数据信号。

[0145]

读取感测放大器650包括耦合在输出数据寄存器670与dram单元阵列630之间的读取感测放大器电路。读取感测放大器650被配置成感测并放大来自dram单元阵列630的将由输出数据寄存器670保存的数据信号。

[0146]

输入数据寄存器660包括被配置成保存用于写入操作的输入数据的多个数据寄存器。输入数据寄存器660被配置成经由i/o连接界面610从外部存储器控制器接收写入数据选通信号(wdqs)及从数据总线接收写入数据信号(wdq)。输入数据寄存器660被配置成基于写入数据选通信号(wdqs)而在写入数据信号(wdq)中保存数据。当dram 600被实施成ddr sdram 540(图5)时,外部存储器控制器可为例如存储器控制器525。数据总线例如是晶体管级界面530(图5)的一部分且包括位于ddr sdram 540与soc电路520之间的多条数据信号线。数据信号线可为从soc电路520到ddr sdram 540的单向的,或者是ddr sdram 540与soc电路520之间的双向的。

[0147]

输出数据寄存器670包括被配置成保存用于读取操作的输出数据的多个数据寄存

器。输出数据寄存器670被配置成经由i/o连接界面610从外部存储器控制器接收读取数据选通信号(rdqs)。输出数据寄存器670还被配置成保存来自读取感测放大器650的数据且将数据提供到i/o连接界面610,以基于读取数据选通信号(rdqs)传送到数据总线。i/o连接界面610被配置成将包括数据的读取数据信号(rdq)在数据总线上传送。当dram 600被实施成ddr sdram 540(图5)时,外部存储器控制器可为例如存储器控制器525。数据总线是例如晶体管级界面530(图5)且包括位于ddr sdram 540与soc电路520之间的多条数据信号线。数据信号线可为从ddr sdram 540到soc电路520的单向的,或者是ddr sdram 540与soc电路520之间的双向的。

[0148]

用于写入数据信号(wdq)的数据信号线及用于读取数据信号(rdq)的数据信号线二者包括在晶体管级界面530(图5)中,且因此是ddr sdram 540(即,dram 600)的外部信号线。

[0149]

在一些实施例中,用于写入数据信号(wdq)的双向数据信号线与用于读取数据信号(rdq)的双向数据信号线相同。作为另一种选择,用于写入数据信号(wdq)的双向数据线不同于用于读取数据信号(rdq)的双向数据线。

[0150]

在一些实施例中,dram 600接收晶体管级操作信号(包括读取操作信号或写入操作信号)。dram 600包括耦合在dram单元阵列630与i/o连接界面610之间的多个寄存器,分别根据读取操作信号或写入操作信号从多个寄存器直接传送或直接接收数据信号。举例来说,dram 600的i/o连接界面610被配置成接收用于控制写入驱动器640或读取感测放大器650的存储库控制信号作为晶体管级操作信号(包括读取操作信号或写入操作信号)。dram 600包括耦合在dram单元阵列630与i/o连接界面610之间的输入数据寄存器660及输出数据寄存器670,以根据存储库控制信号中的写入操作信号或读取操作信号从输入数据寄存器660直接接收数据信号或从输出数据寄存器670直接传送数据信号。

[0151]

在一些实施例中,dram 600的i/o连接界面610包括数据i/o连接界面,数据i/o连接界面被配置成传送或接收晶体管级数据信号。如图6中所示,i/o连接界面610包括数据i/o连接界面612。数据i/o连接界面612包括被配置成接收写入数据信号(wdq)及输出读取数据信号(rdq)的多条导电线。当dram 600被实施成dram管芯330时,写入数据信号(wdq)及读取数据信号(rdq)二者是晶体管级数据信号,如以上参照图3所示。写入数据信号(wdq)包括多个输入数据。读取数据信号(rdq)包括多个输出数据。dram 600包括耦合在dram单元阵列630与i/o连接界面610之间的输入数据寄存器660及输出数据寄存器670,且保存写入数据信号(wdq)中的输入数据或读取数据信号(rdq)中的输出数据。

[0152]

在一些实施例中,i/o连接界面610被配置成通过i/o连接界面610传导(conduct)晶体管级操作信号,而不进行信号缓冲或驱动能力的增强。举例来说,如图6中所示,i/o连接界面610被配置成通过i/o连接界面610传导存储库控制信号、写入数据选通信号(wdqs)和/或读取数据选通信号(rdqs),而不进行信号缓冲或驱动能力的增强。i/o连接界面610不包括缓冲器或驱动器。

[0153]

在一些实施例中,外部信号线包括多条信号线。i/o连接界面610包括用于连接到多条信号线的多个连接件。连接件中的相邻连接件之间的距离等于或小于十微米且大于或等于4.5微米。举例来说,当dram 600被实施成dram管芯330(图3)时,soc管芯320的多条导电线(未示出)经由多个无凸块内连件连接到dram管芯330的多条导电线(未示出)。soc管芯

320的导电线是dram管芯330的外部信号线。dram 600(即,dram管芯330)的i/o连接界面610被配置用于耦合到soc管芯320的导电线,以从soc管芯320直接接收存储库控制信号、写入数据选通信号(wdqs)和/或读取数据选通信号(rdqs)。i/o连接界面610包括多个连接件(例如dram管芯330(即dram 600)的导电线的端子),以用于连接到soc管芯320的导电线。

[0154]

将根据位于soc管芯与dram管芯之间的内连件的大小以及半导体工艺来确定连接件中的相邻连接件之间的最小距离。举例来说,传统的标准受控塌陷芯片连接(controlled collapse chip connection,c4)凸块具有100微米(μm)的大小,且标准c4凸块的凸块节距为150μm到200μm。因此,dram管芯的连接件中的相邻连接件之间的最小距离为150μm。本文中的距离是dram管芯的连接件中的相邻连接件之间的中心到中心的距离。作为另一实例,传统的微c4凸块具有20μm到30μm的大小,且微c4凸块的凸块节距为30μm到60μm。dram管芯的连接件中的相邻连接件之间的距离为30μm。

[0155]

位于soc管芯320与dram管芯330之间的无凸块内连件具有例如5μm、3μm或2μm的大小,且无凸块内连件的节距为10μm或小于10μm。当半导体处理的技术节点按比例缩小时,无凸块内连件的大小也按比例缩小。因此,无凸块内连件的节距也按比例缩小。在示例性的七纳米(7nm)半导体工艺中,连接件中的相邻连接件之间的最小距离将为约9μm。在示例性的五纳米(5nm)半导体工艺中,连接件中的相邻连接件之间的最小距离将为约6μm。在示例性的三纳米(3nm)半导体工艺中,连接件中的相邻连接件之间的最小距离将为4.5μm。在一些实施例中,连接件中的相邻连接件之间的距离可大于最小距离。举例来说,在3nm半导体工艺中,dram管芯330的连接件中的相邻连接件之间的距离可为4.5μm到6μm或者甚至更大的距离。作为另一实例,在5nm半导体工艺中,dram管芯330的连接件中的相邻连接件之间的距离可为6μm到9μm或者甚至更大的距离。作为另一实例,在7nm半导体工艺中,dram管芯330的连接件中的相邻连接件之间的距离可为9μm到10μm或者甚至更大的距离。如以上所提及,本文中的距离是dram管芯的连接件中的相邻连接件之间的中心到中心的距离。

[0156]

当soc电路520打算从ddr sdram 540(即,dram 600)读取数据时,存储器控制器525被配置成将用于控制读取感测放大器650的存储库控制信号及读取数据选通信号(rdqs)作为晶体管级操作信号传送到ddr sdram 540(即,dram 600)。因此,dram 600(即,ddr sdram 540)的i/o连接界面610被配置用于耦合到晶体管级界面530的信号线,以直接接收来自存储器控制器525的用于控制读取感测放大器650的存储库控制信号及读取数据选通信号(rdqs),以用于读取dram单元阵列545中的数据。

[0157]

与传统的ddr sdram 200(图2)相比,dram 600不包括命令解码器220、存储库控制逻辑电路222、地址寄存器230及i/o驱动器270的对应物。与传统的ddr sdram 200相比,在不具有这些电路的条件下,dram 600提供更高效的数据存取,消耗更少的电力,且要求更小的电路面积。

[0158]

图7是根据本公开一些实施例的示例性存储器电路的示例性时序图700。时序图700可为dram 600的时序图。时序图700包括第一时钟信号(ck_t)、第二时钟信号(ck_b)、行地址信号(ra)、激活信号(act)、感测放大器使能信号(saen)、列地址信号(ca)、写入控制信号(wr)、列选择线信号(csl)、写入数据选通信号(wdqs)、写入数据信号(wdq)、读取数据选通信号(rdqs)及读取数据信号(rdq)。当dram 600被实施成例如ddr sdram 540时,存储器控制器525被配置成传送这些信号(除了读取数据信号(rdq)之外)或控制soc电路520将这

些信号(除了读取数据信号(rdq)之外)传送到dram 600(即,ddr sdram 540)。

[0159]

第一时钟信号(ck_t)与第二时钟信号(ck_b)是差分时钟信号且具有相反的相位。时钟信号(ck_t及ck_b)中的一者或两者对应于dram 600(图6)的时钟信号(ck)。行地址信号(ra)及列地址信号(ca)分别对应于dram 600(图6)的行地址信号(row address)及列地址信号(column address)。激活信号(act)、感测放大器使能信号(saen)、写入控制信号(wr)及列选择线信号(csl)对应于dram 600(图6)的存储库控制信号。写入数据选通信号(wdqs)、写入数据信号(wdq)、读取数据选通信号(rdqs)及读取数据信号(rdq)分别对应于dram 600(图6)的写入数据选通信号(wdqs)、写入数据信号(wdq)、读取数据选通信号(rdqs)及读取数据信号(rdq)。

[0160]

dram 600被配置成实行激活710、读取720、读取730、写入740、写入750及预充电760操作。当激活信号(act)从低电平转变到高电平且保持在高电平处时,dram 600被激活(即,激活710操作),且行解码器631被配置成对来自行地址信号(ra)的行地址(row)进行解码。在一个时钟周期内,感测放大器使能信号(saen)也从低电平转换到高电平且保持在高电平处。高电平处的感测放大器使能信号(saen)使得写入驱动器640和/或读取感测放大器650能够进行写入和/或读取操作。

[0161]

在行地址选通(ras)到列地址选通(cas)延迟(ras到cas延迟)之后,在列地址信号(ca)中提供第一列地址(col-1)且激活列选择线信号(csl)以实行读取720操作。将列解码器632配置成基于列选择线信号(csl)对列地址信号(ca)中的列地址(col-1)进行解码。将读取感测放大器650配置成基于行地址(row)及列地址(col-1)感测并放大dram单元阵列630中的数据信号且将数据信号提供到输出数据寄存器670。在读取等待时间之后,将读取数据选通信号(rdqs)激活,且将dram 600配置成传送读取数据信号(rdq)中的数据r0及r1。

[0162]

在cas到cas延迟之后,在列地址信号(ca)中提供第二列地址(col-2)且激活列选择线信号(csl)以实行读取730操作。类似于激活710操作,在读取等待时间延迟之后,将读取数据选通信号(rdqs)激活,且将dram 600配置成传送读取数据信号(rdq)中的数据r2及r3。

[0163]

在写入740操作之前的一个时钟周期中,写入数据信号(wdq)包括数据w0及w1。将写入数据选通信号激活以触发输入数据寄存器660保存数据w0及w1。当在列地址信号(ca)中提供第三列地址(col-3)且将列选择线信号(csl)激活以用于实行写入740操作时,写入驱动器640被配置成将数据w0及w1写入到dram单元阵列630中。

[0164]

dram 600被配置成实行写入750操作,以通过与以上针对写入740操作所示类似的步骤,基于行地址及列地址(col-4)将数据w2及w3写入到dram单元阵列630中。

[0165]

在写入750操作之后,存储器控制器525被配置成将激活信号(act)从高电平转换到低电平。dram 600被配置成实行预充电760操作,以对dram单元阵列630的一个或多个存储库进行充电。

[0166]

图8是根据本公开一些实施例的用于示例性存储器电路中的数据存取的示例性方法800的流程图。方法800可由dram管芯330、350及370、ddr sdram 440、ddr sdram 540、dram 600和/或其他存储器电路来实践。方法800包括接收晶体管级操作信号(步骤810);接收晶体管级地址信号(步骤820);根据晶体管级操作信号传送或接收晶体管级数据信号(步骤830);以及从电源接收输入电力,基于输入电力产生内部电力,且将内部电力供应到存储

器电路的存储器单元阵列(步骤840)。

[0167]

步骤810包括接收晶体管级操作信号。举例来说,当dram 600(图6)被实施成ddr sdram 540(图5)时,dram 600的i/o连接界面610被配置成从soc电路520的存储器控制器525直接接收晶体管级操作信号,以用于存取dram单元阵列545中的数据。来自存储器控制器525的晶体管级操作信号包括存储库控制信号、写入数据选通信号(wdqs)和/或读取数据选通信号(rdqs)。包括用于控制写入驱动器640的存储库控制信号及写入数据选通信号(wdqs)的晶体管级操作信号指示写入操作。包括用于控制读取感测放大器650的存储库控制信号及读取数据选通信号(rdqs)的晶体管级操作信号指示读取操作。

[0168]

步骤820包括接收晶体管级地址信号。举例来说,当dram 600(图6)被实施成ddr sdram 540(图5)时,dram 600的i/o连接界面610被配置成从soc电路520的存储器控制器525接收晶体管级行地址信号(row address)及晶体管级列地址信号(column address),以用于存取dram单元阵列545中的数据。

[0169]

步骤830包括根据晶体管级操作信号传送或接收晶体管级数据信号。举例来说,当dram 600(图6)被实施成ddr sdram 540(图5)时,当来自存储器控制器525的晶体管级操作信号包括用于控制读取感测放大器650的存储库控制信号及读取数据选通信号(rdqs)时,dram 600的i/o连接界面610被配置成向soc电路520传送晶体管级数据信号(rdq)。作为另一种选择,当来自存储器控制器525的晶体管级操作信号包括用于控制写入驱动器640的存储库控制信号及写入数据选通信号(wdqs)时,dram 600的i/o连接界面610被配置成从soc电路520接收晶体管级数据信号(wdq)。

[0170]

步骤840包括从电源接收输入电力,基于输入电力产生内部电力,且将内部电力供应到存储器电路的存储器单元阵列。举例来说,dram 600(图6)的电力产生器620被配置成经由i/o连接界面610从外部电源接收输入电力(v

ext

)。电力产生器620还被配置成基于输入电力(v

ext

)产生内部电力。电力产生器620被配置成将内部电力供应到dram单元阵列630和/或dram 600的其他组件。

[0171]

在一些实施例中,步骤810中的晶体管级操作信号是cmos级信号。举例来说,soc电路520及ddr sdram 540可各自包括cmos电路。soc电路520的存储器控制器525被配置成以用于soc电路520的cmos晶体管与ddr sdram 540的cmos晶体管之间的通信的电压电平和/或电流电平将存储库控制信号、写入数据选通信号(wdqs)和/或读取数据选通信号(rdqs)作为晶体管级操作信号进行传送。

[0172]

在一些实施例中,接收步骤810的晶体管级操作信号包括接收读取选通信号或写入选通信号。举例来说,当dram 600(图6)被实施成ddr sdram 540(图5)时,dram 600的i/o连接界面610被配置成将存储库控制信号、写入数据选通信号(wdqs)和/或读取数据选通信号(rdqs)作为晶体管级操作信号进行接收。包括写入数据选通信号(wdqs)的晶体管级操作信号指示写入操作。包括读取数据选通信号(rdqs)的晶体管级操作信号指示读取操作。

[0173]

在一些实施例中,接收步骤830的晶体管级数据信号包括将第一晶体管级数据信号直接接收到存储器电路的多个第一寄存器中,且传送步骤830的晶体管级数据信号包括从存储器电路的多个第二寄存器直接传送第二晶体管级数据信号。举例来说,dram 600(图6)被配置成在写入操作中将晶体管级写入数据信号(wdq)从数据总线(例如晶体管级界面530或430)直接接收到dram 600的输入数据寄存器660中。作为另一实例,在读取操作中,

dram 600(图6)被配置成将晶体管级读取数据信号(rdq)从dram 600的输出数据寄存器670直接传送到数据总线(例如晶体管级界面530或430)。

[0174]

在一些实施例中,直接从存储器电路的多个寄存器传送步骤830中的晶体管级数据信号或将步骤830中的晶体管级数据信号直接接收到存储器电路的多个寄存器中,而不进行信号缓冲或驱动能力的增强。举例来说,dram 600(图6)的数据i/o连接界面612不包括任何缓冲器或驱动器。在读取操作中,dram 600被配置成经由数据i/o连接界面612从输出数据寄存器670直接传送晶体管级读取数据信号(rdq),而不进行信号缓冲或驱动能力的增强。在写入操作中,dram 600被配置成经由数据i/o连接界面612将晶体管级写入数据信号(wdq)直接接收到输入数据寄存器660中,而不进行信号缓冲或驱动能力的增强。

[0175]

在一些实施例中,接收步骤820的晶体管级地址信号包括接收晶体管级行地址信号及接收晶体管级列地址信号。举例来说,当dram 600(图6)被实施成ddr sdram 540(图5)时,dram 600的i/o连接界面610被配置成从soc电路520的存储器控制器525接收晶体管级行地址信号(row address)及晶体管级列地址信号(column address),以用于存取dram单元阵列545中的数据。

[0176]

在一些实施例中,本文中公开的存储器电路可包括被提供来存储任何类型信息的任何适当类型的大容量存储器,例如易失性或非易失性、磁性、半导体、光学、可移动、不可移动或其他类型的存储器件或有形(即,非暂时性)计算机可读介质,包括但不限于只读存储器(read-only memory,rom)、闪存、动态随机存取存储器(dynamic random-access memory,dram)及静态ram。

[0177]

对于所属领域中的技术人员来说,可对所公开的集成电路、存储器电路及用于数据存取的方法进行各种修改及变化。考虑到所公开的集成电路、存储器电路及用于数据存取的方法的规范及实践,其他实施例对于所属领域中的技术人员来说将是可以理解的。说明书及实例仅被认为是示例性的,真正的范围由所附权利要求及其等效物指示。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1