一种双路8位并口NANDFLASH存储电路的制作方法

一种双路8位并口nand flash存储电路

技术领域

1.本发明属于嵌入式系统的数据存储技术领域,具体涉及一种双路8位并口nand flash存储电路。

背景技术:

2.目前,嵌入式系统随着功能的复杂,数据吞吐量不断增加,部分数据需要实时的保存在片外非易失性存储器上,以便于嵌入式系统掉电后正常读取工作时的数据信息。在嵌入式系统的数据存储领域主要有spiflash、sd卡和并口访问方式,并口访问具有速度快的优势,便于一次性保存较多量的数据。nand flash内部采用非线性宏单元模式,具有容量大、改写速度快等优点,适用于大量数据的存储。在主流的嵌入式芯片arm或dsp等处理器中,其自带一路与flash通信的并口总线。在某些特殊应用场景,产品的使用是一次性的,产品使用中的数据需要完整保存,以便后续查看产品工作状态或排查问题,此时需要对保存的数据进行备份,增加数据的可靠性。系统需要快速的同时保存相同的数据到两个的flash中,而处理器的一路快速并行总线不能直接与两个flash总线同时通信,需要在硬件电路和软件设计中解决该问题。

技术实现要素:

3.针对上述情况,本发明设计了一种双路8位并口nand flash存储电路,突破嵌入式系统只能单路存储数据于nand flash的局限性,实现对两个nand flash读写数据。

4.为了实现以上目的,本发明采用如下技术方案:

5.一种双路8位并口nand flash存储电路,包括arm嵌入式芯片电路、双路存储电路和并行接口电路,所述arm嵌入式芯片电路包括一个arm处理器u1,所述arm处理器为stm32f427微控制器,所述arm嵌入式芯片电路还包括晶振jz1和复位芯片u2,以及电容c1、c2,晶振jz1和电容c1一端与3.3v和jz1连接,一端与jz1的2脚连接;复位芯片u2,电容c2两端与u2的1、2连接,电阻r1两端与u2的3、4连接;软件配置程序调试接口采用swd5线模式,swd插座与arm的仿真调试器相连接。所述双路存储电路包括两个nand flash存储器芯片m1、m2,arm处理器的接口电路为并口,通过软件配置,在一个并口总线上完成两片nand flash存储器的读写,所述双路存储电路中nand flash存储器的r/b引脚和/ce引脚独立与arm处理器连接,其他引脚并行与arm处理器连接,双路存储电路还包括电阻r3、r4,以及电容c3、c4、c5、c6,电阻r3、r4分别两端与nand flash存储器芯片m1、m2的7脚和3.3v电源相连,电容c3、c4、c5、c6的两端分别与nand flash存储器芯片m1、m2的12、19、37和dgnd相连,nand flash存储器芯片m1的/ce(片选)脚与stm32f427微控制器的pd7相连,nand flash存储器芯片m2的/ce(片选)脚与stm32f427微控制器的pg9相连接。

6.nand flash存储器芯片和arm的fmc接口相连,nand flash地址/数据是共用数据线的,其片选信号通过总线控制。存储器芯片正常读写数据之前,需要进行初始化配置,同样型号的存储器芯片,配置命令相同,在芯片配置时,芯片与arm处理器有信号交互。如果直

接将两片相同的存储器芯片的所有引脚并行与arm的fmc接口相连,由于芯片的配置命令相同,当芯片向arm处理器发送信息时,会造成总线竞争,致使arm处理器不能正常读写数据。通过设计将两块存储器的片选信号分别与arm的fmc总线的nce2(存储区域2)和nce3(存储区域3)相连,通过总线中不同的软件配置来实现不同存储器的片选。同时,存储器的r/b(就绪/忙)引脚分别与arm处理器不同的引脚相连,以实现不同存储器和同一个arm处理器的交互通信,避免总线竞争。

7.进一步的,通过arm处理器不断的切换总线的nce2和nce3,每次存储数据之前,进行相应的初始化,实现同一路总线上不同存储器的读写数据。

8.进一步的,通过arm处理器的不同引脚,识别不同存储器的r/b信号,根据r/b的高低电平信号,分时切换总线,实现总线的分时复用。

9.本发明还包括能够使其正常使用的其它组件,均为本领域的常规手段,另外,本发明中未加限定的装置或组件,均采用本领域的现有技术。

10.本发明的有益效果如下:

11.(1)有效提高嵌入式系统数据存储的速度,系统在0.5ms工作循环周期内,实现双路512字节的写入。

12.(2)保证嵌入式系统数据存储的可靠性,两个nand flash存储芯片循环保存系统数据,提高数据的完整性。

13.(3)在不额外增加硬件电路复杂性的前提下,通过电路的设计和合理的软件时序实现arm处理器和存储器的双路8位并口通信,有效节约了成本。

附图说明

14.图1为本发明的arm处理器电路图。

15.图2为本发明的双路存储电路图。

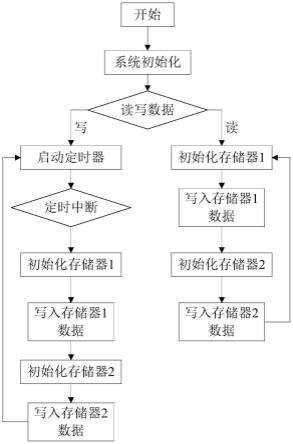

16.图3为本发明的处理器数据读写流程图。

具体实施方式

17.下面将结合具体的实施例,对本发明的技术方案进行清晰完整地描述,显然,所描述实施例仅仅是本发明的部分实施例,而非全部实施例。

18.实施例

19.如图1-2所示,一种双路8位并口nand flash存储电路,包括arm嵌入式芯片电路、双路存储电路和并行接口电路,所述arm嵌入式芯片电路包括一个arm处理器u1,所述arm处理器为stm32f427微控制器,所述arm嵌入式芯片电路还包括晶振jz1和复位芯片u2,复位芯片u2为imp811seus/t芯片,以及电容c1、c2,嵌入式电路根据arm处理器stm32f427的特性,选用25m的晶振,选用imp811复位芯片搭建复位电路,晶振和电容c1一端与3.3v和晶振连接,一端与晶振的2脚连接;复位芯片u2,电容c2两端与复位芯片u2的1、2连接,电阻r1两端与复位芯片u2的3、4连接;软件配置程序调试接口采用swd五线模式,swd插座p1与arm的仿真调试器相连接。所述双路存储电路包括两个nand flash存储器芯片m1、m2,arm处理器的接口电路为并口,通过软件配置,在一个并口总线上完成两片nand flash存储器的读写,nand flash芯片以三星k9f2g08u0b芯片为存储器芯片设计存储器电路,所述双路存储电路

中nand flash存储器的r/b引脚和/ce引脚独立与arm处理器连接,其他引脚并行与arm处理器连接,双路存储电路还包括电阻r3、r4,以及电容c3、c4、c5、c6,电阻r3、r4分别两端与nand flash存储器芯片m1、m2的7脚和3.3v电源相连,电容c3、c4、c5、c6的两端分别与nand flash存储器芯片m1、m2的12、19、37和dgnd相连,nand flash存储器芯片m1的/ce(片选)脚与stm32f427微控制器的pd7相连,nand flash存储器芯片m2的/ce(片选)脚与stm32f427微控制器的pg9相连接。

20.nand flash存储器芯片和arm的fmc接口相连,nand flash地址/数据是共用数据线的,其片选信号通过总线控制。arm处理器的fmc总线的8位地址/数据总线为pd14、pd15、pd0、pd1、pe7、pe8、pe9、pe10,pd5、pd12、pd11、pd4,读写总线分别与存储器的/we、ale、cle、/re连接,上述总线为两个存储器共用,方便数据读写。

21.如图3所示,存储器芯片正常读写数据之前,需要进行初始化配置,同样型号的存储器芯片,配置命令相同,在芯片配置时,芯片与arm处理器有信号交互。如果直接将两片相同的存储器芯片的所有引脚并行与arm的fmc接口相连,由于芯片的配置命令相同,当芯片向处理器发送信息时,会造成总线竞争,致使处理器不能正常读写数据。通过设计将两块存储器的片选信号分别与arm的fmc总线的nce2(存储区域2)和nce3(存储区域3)相连,通过总线中不同的软件配置实现不同存储器的片选。同时,存储器的r/b(就绪/忙)引脚分别与处理器不同的引脚相连,实现不同存储器和同一个处理器的交互通信,避免总线竞争。

22.通过arm处理器不断的切换总线的nce2和nce3,每次存储数据之前,进行相应的初始化,实现同一路总线上不同存储器的读写数据。

23.通过arm处理器的不同引脚,识别不同存储器的r/b信号,根据r/b的高低电平信号,分时切换总线,实现总线的分时复用。

24.处理器的pg6与存储器m1的r/b引脚相连,pg7与存储器m2的r/b引脚相连,两个存储器的r/b引脚相互独立,互不影响。处理器通过不同的io引脚来判断两个存储器的就绪/忙状态,识别不同存储器的工作状态,实现一个处理器和两个存储器的交互通信。

25.处理器的pd7与存储器m1的/ce引脚相连,pg9与存储器m2的/ce引脚相连,两个存储器的/ce引脚相互独立。/ce引脚是存储器的片选使能引脚,该引脚的有效与否与处理器的fmc总线相关,两个存储器正常工作前,需要对两个存储器分别初始化。

26.由于处理器和存储器之间的地址/数据总线是共用的,其中一个存储器初始化之后,默认该存储器处于工作状态,而另一个存储器会挂起,这时只能向一个存储器读写数据。为解决该问题,需要在每次(512字节)读写存储器中的数据前,对相应的存储器进行初始化,以使能需要工作的存储器的/ce引脚,如图3流程图所示,嵌入式读写部分软件程序如下:

27.[0028][0029][0030]

通过软件程序的适当逻辑,处理器可以在0.5ms周期内完成两片存储器512个字节

数据的写入,循环的读出两片存储器里的数据。读写程序代码在系统中断程序外顺序执行,可以被打断,而不影响数据后续的读写。在确保嵌入式系统正常工作的同时,完整的完成两片nand flash存储器的读写,有效防止特殊应用场合下个别存储器损坏引起的数据丢失,增加了数据的可靠性和完整性。

[0031]

本发明的技术方案并不限于上述具体实施例的限制,在不偏离所说明实施例的范围和精神的情况下,对于本技术领域的普通技术人员来说许多修改和变更都是显而易见的,凡在本发明的精神和原则之内,所作的任何技术变形,均落入本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1