一种忆阻器阵列PUF电路及其使用方法

一种忆阻器阵列puf电路及其使用方法

技术领域

1.本发明属于puf电路技术领域。具体涉及一种忆阻器阵列puf电路及其使用方法。

背景技术:

2.随着电子技术的不断发展,硬件电子设备的数量呈爆发式的增长,所面临的安全问题也日益突出。目前的硬件安全防护是基于密码学中的方法来实现的,即将传统密码学中的加密手段应用到硬件电路当中,例如:aes、rsa、数字签名、哈希函数等。但是电子设备正在向嵌入式、微型化、便携式的方向发展,传统密码学中的加密算法复杂度较高,在硬件电路中实现具有较大的技术难度,会导致较多的资源消耗,并且需要把加密所用的密钥储存在非易失性存储器中,这增加了额外的硬件开销并带来了密钥泄露和丢失的隐患。

3.为了解决这些问题,研究人员提出了物理不可克隆函数(physically unclonable function,puf)电路的概念,在硬件安全领域作为一种全新的硬件安全保护方案备受人们的广泛关注。puf电路是研究人员受人体指纹启发而创造出的概念。每个人的指纹都不同,因而指纹可以作为人体的唯一标识符,由于在相同工艺下制造出的电子器件的参数有差异,puf电路则是将这种差异提取出来作为硬件设备的指纹。这种参数差异是随机的,不可控的,因而puf电路是唯一的,不可克隆的,可以作为硬件设备的唯一标识符。puf电路的输入信号被称作激励(challenge),输出信号被称为响应(response),输入任意激励都将产生独特且不可预测的响应,每个激励都有其唯一对应的响应。一个激励和其对应的响应称为激励响应对(challenge response pairs:crps)。puf电路具有唯一性和随机性等特性,即puf一旦生产出来便是独一无二的,连生产厂家也无法复制。利用这些性质,puf主要用于硬件安全领域,尤其是在硬件设备身份认证和防克隆等安全问题上具有独特的优势。

4.puf电路根据crps的数量可以分为强puf电路和弱puf电路。强puf电路拥有大量的crps,而弱puf电路一般只有少量的crps。在众多强puf电路中,忆阻器阵列puf电路作为一种新型的puf电路受到了研究人员的广泛关注。忆阻器阵列puf电路以忆阻器作为基本的组成单元,由于忆阻器高阻态和低阻态的阻值分布具有随机性,并且高阻态阻值分布的分散性更强,因此可以作为良好的puf电路熵源。忆阻器具有阈值特性,只有在外电场达到一定阈值时,忆阻器的阻值才会在高阻和低阻之间切换。此外,忆阻器还具有操作电压低、结构简单、功耗低、读写速度快、便于集成等特点,这使得忆阻器阵列puf电路相对于其他强puf电路具有更好的核心特性和更小的资源开销。

[0005]“一种物理不可克隆函数电路及其操作方法”(cn 113096709 a)专利技术,该技术以忆阻器处于高阻态时阻值分布的随机性作为熵源,在开始工作时首先对忆阻器阵列中所有忆阻器进行复位,根据输入的激励选中忆阻器阵列中同一行相邻两列的两个忆阻器单元,例如选中第i行、第j列和第j+1列的两个忆阻器单元。然后对第i行、第j列的忆阻器单元施加高电平电压信号,对第i行第j+1列的忆阻器单元施加低电平的信号,使所选中的两个忆阻器单元构成串联电路,并将串联电路中间分压点处的电压与设定的参考电压进行比较得出响应。该忆阻器阵列puf电路不会受到串扰电流的影响,因此puf电路输出响应的可靠

性较高,但是该puf电路难以确定合适的参考电压以保证puf电路具有良好的核心性能,并且该puf电路没有施加任何抵抗机器学习建模攻击的措施,因而其安全性较低。

[0006]“一种采用2t2r混合结构的物理不可克隆函数电路”(cn 109547207 a)专利技术,该技术提出了一种采用2t2r混合结构的puf电路。该puf电路由2t2r忆阻器阵列和控制电路组成,puf电路开始工作时首先对2t2r忆阻器阵列中所有忆阻器进行复位,使其处于高阻态,然后对2t2r忆阻器阵列中两个并联的忆阻器施加“forming”电压使忆阻器从高阻态变为低阻态,施加过“forming”电压后,两个并联忆阻器的其中一个会率先由高阻态变为低阻态并阻止另外一个变为低阻态,由于同样生产工艺下生产的同一批忆阻器的内部参数有差异,因此哪一个忆阻器变为低阻态是随机的。然后给2t2r单元中的其中一个忆阻器施加电压,将其产生的电流与参考电流比较来判断该忆阻器是否仍处于高阻态,并根据比较结果输出响应。该发明中的忆阻器阵列由于采用2t2r混合结构,可以防止串扰电流对输出响应的干扰,提高了可靠性,但该puf电路同样没有设计任何抵抗机器学习建模攻击的方案,难以保证其安全性。

[0007]

g.rose等人(rose g s,meade c a.performance analysis of a memristive crossbar puf design[c]//2015 52nd acm/edac/ieee design automation conference(dac).ieee,2015:1-6.)设计了一种忆阻器阵列puf电路,该puf电路以忆阻器处于高阻态时阻值分布的随机性作为熵源,其特点是puf电路中每一位激励对应忆阻器阵列中的两行忆阻器。puf电路开始工作时首先对忆阻器阵列中的所有忆阻器进行复位,使其处于高阻态,然后根据输入的激励使得忆阻器阵列中每个激励所对应两行忆阻器中的其中一行保持高阻态不变,另外一行忆阻器的阻值由高阻态变为低阻态,最后给所有忆阻器施加读电压,比较阵列上相邻两列电流流经负载电阻产生的电压以得到puf电路的输出响应。由于该puf电路不需要选取参考电压,因而具有稳定的核心性能。但其工作方法决定了每位激励必须对两行忆阻器的阻值进行控制才能得到最终的输出响应,因此造成了熵源的浪费,并且该puf电路仍不具有抗机器学习的能力。

[0008]

m.uddin等人(uddin m,majumder m b,rose g s.robustness analysis of a memristive crossbar puf against modeling attacks[j].ieee transactions on nanotechnology,2017,16(3):396-405.)在g.rose等人的基础上对忆阻器阵列puf电路进行了结构上的改进,使该忆阻器阵列puf电路具有了抗机器学习的能力。其改进的方法是将puf电路输出的两个响应再通过异或电路进行逻辑运算得到最终的puf电路响应。这种方法增强了puf电路的非线性特性,提高了抗机器学习的能力,但同时也减少了puf电路响应的位数。

技术实现要素:

[0009]

本发明旨在克服现有技术的缺陷,目的是提出一种具有抗机器学习能力强、熵源利用率高和核心性能指标良好的忆阻器阵列puf电路及其使用方法。

[0010]

为实现上述目的,本发明采用的技术方案是:

[0011]

为了叙述方便,先将下述字母所表示的物理意义统一描述如下:

[0012]

i表示行控制电路的个数,1《i≤m,m为大于1的自然数;

[0013]

j表示响应输出电路的个数,1《j≤n,n为大于1的自然数。

[0014]

所述忆阻器阵列puf电路是由随机延迟电路、m个行控制电路、m

×

2n个阵列忆阻器(103)组成的忆阻器阵列和n个响应输出电路组成。其中:

[0015]

随机延迟电路的端子v

pulse

与电压输入端子v

pl

连接,随机延迟电路的端子v

c11

、

……

、v

c1i

、

……

、v

c1m

与对应的电压输入端子v

c1

、

……

、v

ci

、

……

、v

cm

连接;随机延迟电路的端子v

delay

与第1行控制电路的端子v

dly1

、

……

、第i行控制电路的端子v

dlyi

、

……

、第m行控制电路的端子v

dlym

分别连接。

[0016]

第1行控制电路的端子v

chlg1

、

……

、第i行控制电路的端子v

chlgi

、

……

、第m行控制电路的端子v

chlgm

分别与电压输入端子v

chlg

连接;第1行控制电路的端子v

c01

、

……

、第i行控制电路的端子v

c0i

、

……

、第m行控制电路的端子v

c0m

与对应的电压输入端子v

c1

、

……

、v

ci

、

……

、v

cm

连接;第1行控制电路的端子v

rd1

、

……

、第i行控制电路的端子v

rdi

、

……

、第m行控制电路的端子v

rdm

分别与电压输入端子v

rd

连接;第1行控制电路的端子v

cr01

、

……

、第i行控制电路的端子v

cr0i

、

……

、第m行控制电路的端子v

cr0m

分别与电压输入端子v

cr0

连接。

[0017]

忆阻器阵列由m

×

2n个阵列忆阻器组成;第1行控制电路的端子v

out1

通过对应的字线wl1与第1行的2n个阵列忆阻器的端子a

r0

连接,

……

,第i行控制电路的端子v

outi

通过对应的字线wli与第i行的2n个阵列忆阻器的端子a

r0

连接,

……

,第m行控制电路的端子v

outm

通过对应的字线wlm与第m行的2n个阵列忆阻器的端子a

r0

连接。

[0018]

第1响应输出电路的端子i1、端子i2通过各自的位线bl1、bl2与忆阻器阵列中第1列阵列忆阻器的端子a

r1

、第2列阵列忆阻器的端子a

r1

对应连接,

……

,第j响应输出电路的端子i

2j-1

、端子i

2j

通过各自的位线bl

2j-1

、bl

2j

与忆阻器阵列中第2j-1列阵列忆阻器的端子a

r1

、第2j列阵列忆阻器的端子a

r1

对应连接,

……

,第n响应输出电路的端子i

2n-1

、端子i

2n

通过各自的位线bl

2n-1

、bl

2n

与忆阻器阵列中第2n-1列阵列忆阻器的端子a

r1

、第2n列阵列忆阻器的端子a

r1

对应连接。

[0019]

第1响应输出电路的端子v

cr11

、

……

、第j响应输出电路的端子v

cr1j

、

……

、第n响应输出电路的端子v

cr1n

分别与电压输入端子v

cr1

连接;第1响应输出电路的端子v

rs1

、

……

、第j响应输出电路的端子v

rsj

、

……

、第n响应输出电路的端子v

rsn

分别与电压输入端子v

rs

连接;第1响应输出电路的端子v

cr21

、

……

、第j响应输出电路的端子v

cr2j

、

……

、第n响应输出电路的端子v

cr2n

分别与电压输入端子v

cr2

连接。

[0020]

在电压输入端子v

pl

、v

chlg

、v

rd

、v

cr0

、v

cr1

、v

rs

、v

cr2

与端子gnd之间施加对应的电压信号u

pl

、u

chlg

、u

rd

、u

cr0

、u

cr1

、u

rs

、u

cr2

;在电压输入端子v

c1

、

……

、v

ci

、

……

、v

cm

与端子gnd之间施加对应的电压信号u

c1

或uc、

……

、u

ci

或uc、

……

、u

cm

或uc。

[0021]

第1响应输出电路的端子v

r1

、

……

、第j响应输出电路的端子v

rj

、

……

、第n响应输出电路的端子v

rn

输出对应的响应电压u

r1

、

……

、u

rj

、

……

、u

rn

。

[0022]

所述随机延迟电路由m个延迟单元和nmos晶体管组成;第1延迟单元的端子out与第2延迟单元的端子in连接,

……

,第i-1延迟单元的端子out与第i延迟单元的端子in连接,

……

,第m-1延迟单元的端子out与第m延迟单元的端子in连接,第m延迟单元的端子out与nmos晶体管的漏极连接。

[0023]

第1延迟单元的端子in与两个延迟电路忆阻器的端子a

r0

分别连接,两个延迟电路忆阻器的端子a

r1

与第1延迟电路选通器的端子1_chan和端子0_chan对应连接;所述第2延迟单元、

……

、第i延迟单元、

……

、第m延迟单元与第1延迟单元的结构相同。

[0024]

第1延迟单元的端子in与随机延迟电路的端子v

pulse

连接,第m延迟单元的端子out与随机延迟电路的端子v

delay

连接;所述第1延迟单元、

……

、第i延迟单元、

……

、第m延迟单元的端子sel与随机延迟电路的端子v

cl1

、

……

、v

cli

、

……

、v

clm

对应连接。

[0025]

所述第1行控制电路由第1控制电路选通器、第2控制电路选通器和第3控制电路选通器组成;第1控制电路选通器的端子out与第2控制电路选通器的端子1_chan连接,第2控制电路选通器的端子out与第3控制电路选通器的端子1_chan连接,第3控制电路选通器的端子out与第1行控制电路端子v

out1

连接。

[0026]

第1控制电路选通器的端子1_chan与gnd连接,第1控制电路选通器的端子0_chan与第1行控制电路的端子v

chlg1

连接,第1控制电路选通器的端子sel与第1行控制电路的端子v

dly1

连接,第2控制电路选通器的端子0_chan与gnd连接,第2控制电路选通器的端子sel与第1行控制电路的端子v

c01

连接,第3控制电路选通器的端子0_chan与第1行控制电路端子v

rd1

连接,第3控制电路选通器的端子sel与第1行控制电路的v

cr01

连接。

[0027]

所述第2行控制电路、

……

、第i行控制电路、

……

、第m行控制电路均与第1行控制电路的结构相同。

[0028]

所述第1响应输出电路的结构是,第1分路器的端子in与第1响应输出电路的端子i1连接,第2分路器的端子in与第1响应输出电路的端子i2连接,第1分路器的端子sel和第2分路器的端子sel分别与第1响应输出电路的端子v

cr11

连接,第1分路器的端子1_chan和第2分路器的端子1_chan分别与第1响应输出电路的端子v

rs1

连接,第1分路器的端子0_chan与第1负载电阻的端子rl

10

连接,第2分路器的端子0_chan与第2负载电阻的端子rl

20

连接。

[0029]

第1负载电阻和第2负载电阻的端子rl

11

、rl

21

分别与gnd连接;电压比较器的输入端子v

+

和v-与第1负载电阻的端子rl

10

和第2负载电阻的端子rl

20

对应连接,电压比较器的输出端子vo与输出电路选通器的端子0_chan连接,输出电路选通器的端子1_chan与gnd连接,输出电路选通器端子sel与第1响应输出电路的端子v

cr21

连接,输出电路选通器的端子out与第1响应输出电路的端子v

r1

连接。

[0030]

所述第2响应输出电路、

……

、第j响应输出电路、

……

、与第n响应输出电路均与第1响应输出电路的结构相同。

[0031]

所述的阵列忆阻器和延迟电路忆阻器相同,均为具有阈值电压的忆阻器;阵列忆阻器和延迟电路忆阻器的初始状态均处于高阻态。

[0032]

所述忆阻器阵列puf电路使用方法的步骤是:

[0033]

步骤一、所有忆阻器复位

[0034]

在电压输入端子v

c1

、

……

、v

ci

、

……

、v

cm

与端子gnd之间施加相同的低电平的电压信号uc;在电压输入端子v

cr0

、v

cr1

、v

cr2

、v

rs

与端子gnd之间施加对应的高电平的电压信号u

cr0

、u

cr1

、u

cr2

、u

rs

,其余电压输入端子与端子gnd之间均不施加任何电压信号。

[0035]

在电压输入端子v

c1

、

……

、v

ci

、

……

、v

cm

与端子gnd之间施加相同的低电平的电压信号uc,每个第2控制电路选通器中的端子0_chan与端子out连通。在电压输入端子v

cr0

与端子gnd之间施加高电平的电压信号u

cr0

,每个第3控制电路选通器中的端子1_chan与端子out连通,则每个行控制电路的端子v

out1

、

……

、v

outi

、

……

、v

outm

均与gnd连接,忆阻器阵列中每个阵列忆阻器的端子a

r0

与gnd连接。

[0036]

在电压输入端子v

cr1

与端子gnd之间施加高电平的电压信号u

cr1

,每个响应输出电

路中,第1分路器中的端子in与端子1_chan连通、第2分路器中的端子in与端子1_chan连通。

[0037]

在电压输入端子v

cr2

与端子gnd之间施加高电平的电压信号u

cr2

,每个响应输出电路中输出电路选通器中的端子1_chan与端子out连通,则每个响应输出电路的端子v

r1

、

……

、v

rj

、

……

、v

rn

均与gnd连接,puf电路不输出响应。

[0038]

此时,在电压输入端子v

rs

与端子gnd之间施加高电平的电压信号u

rs

将施加在忆阻器阵列中每个阵列忆阻器的端子a

r1

上,高电平的电压信号u

rs

的幅值大于阵列忆阻器的阈值电压且持续时间超过阵列忆阻器复位所需的最小时间t

min

,则忆阻器阵列中的阵列忆阻器都复位为高阻态。

[0039]

步骤二、施加激励

[0040]

在电压输入端子v

pl

、v

chlg

、v

cr0

、v

cr2

与端子gnd之间施加对应的高电平的电压信号u

pl

、u

chlg

、u

cr0

、u

cr2

;在电压输入端子v

c1

、

……

、v

ci

、

……

、v

cm

与端子gnd之间施加对应的高电平或低电平的激励电压信号u

c1

、

……

、u

ci

、

……

、u

cm

;在电压输入端子v

cr1

与端子gnd之间施加低电平的电压信号u

cr1

,其余电压输入端子与端子gnd之间均不施加任何电压信号。

[0041]

在电压输入端子v

pl

与端子gnd之间施加高电平的电压信号u

pl

,随机延迟电路的端子v

delay

输出为低电平,每个第1控制电路选通器中的端子0_chan与端子out连通。

[0042]

在电压输入端子v

cr0

与端子gnd之间施加高电平的电压信号u

cr0

,每个行控制电路中第3控制电路选通器中的端子1_chan与端子out连通。

[0043]

在电压输入端子v

cr1

与端子gnd之间施加低电平的电压信号u

cr1

,每个响应输出电路中第1分路器中的端子in与端子0_chan连通、第2分路器中的端子in与端子0_chan连通。

[0044]

在电压输入端子v

cr2

与端子gnd之间施加高电平的电压信号u

cr2

,每个响应输出电路中输出电路选通器中的端子1_chan与端子out连通,从而每个响应输出电路的端子v

r1

、

……

、v

rj

、

……

、v

rn

分别与gnd连接。

[0045]

在电压输入端子v

chlg

与端子gnd之间施加高电平的电压信号u

chlg

,第1行控制电路、

……

、第i行控制电路、

……

、第m行控制电路的端子v

chlg1

、

……

、v

chlgi

、

……

、v

chlgm

处均为高电平的电压信号u

chlg

,高电平的电压信号u

chlg

的幅值大于阵列忆阻器的阈值电压。

[0046]

在电压输入端子v

c1

、

……

、v

ci

、

……

、v

cm

与端子gnd之间施加对应的高电平或低电平的激励电压信号u

c1

、

……

、u

ci

、

……

、u

cm

,每个行控制电路的第2控制电路选通器中的端子1_chan或端子0_chan与端子out连通。

[0047]

每个行控制电路的第2控制电路选通器中的端子1_chan与端子out连通时,高电平的电压信号u

chlg

会施加在每个行控制电路的端子v

outi

上,即施加在忆阻器阵列中每个阵列忆阻器的端子a

r0

上。

[0048]

每个行控制电路的第2控制电路选通器中的端子0_chan与端子out连通时,高电平的电压信号u

chlg

在每个行控制电路的端子v

outi

上均未施加。即忆阻器阵列puf电路会根据施加的激励,成行的选中忆阻器阵列中的阵列忆阻器,对选中阵列忆阻器的a

r0

端施加高电平的电压信号u

chlg

,使选中的阵列忆阻器阻值减小,未选中的阵列忆阻器则保持其阻值不变。

[0049]

同时,激励电压信号u

c1

、

……

、u

ci

、

……

、u

cm

施加在随机延迟电路对应的端子v

c11

、

……

、v

c1i

、、

……

、v

c1m

上,根据激励电压信号u

c1

、

……

、u

ci

、

……

、u

cm

电平的高或低,随机延迟电路在每个延迟单元中选中两个延迟电路忆阻器中的一个与nmos晶体管的寄生电容组成rc延迟电路,延迟电路忆阻器高阻态的阻值分布是随机的,则高电平的电压信号u

pl

经

过随机延迟电路后会产生随机的延迟。不同的激励电压信号,选中的延迟电路忆阻器不同,高电平的电压信号u

pl

随机延迟的时间也不相同;相同的激励电压信号,选中的延迟电路忆阻器相同,高电平的电压信号u

pl

随机延迟的时间也相同。

[0050]

高电平的电压信号u

pl

经过随机延迟后在随机延迟电路的端子v

delay

输出,则每个行控制电路中第1控制电路选通器中的端子1_chan与端子out连通,此时高电平的电压信号u

chlg

不能继续施加在所选中阵列忆阻器的端子a

r0

上,阵列忆阻器的阻值不再减小,从而实现了阵列忆阻器阻值的随机减小。

[0051]

步骤三、响应输出

[0052]

在电压输入端子v

rd

与端子gnd之间施加高电平的电压信号u

rd

;在电压输入端子v

cr0

、v

cr1

、v

cr2

与端子gnd之间施加对应的低电平的电压信号u

cr0

、u

cr1

、u

cr2

,其余电压输入端子与端子gnd之间均不施加任何电压信号;第1响应输出电路的端子v

r1

、

……

、第j响应输出电路的端子v

rj

、

……

、第n响应输出电路的端子v

rn

分别输出响应电压。

[0053]

在电压输入端子v

rd

与端子gnd之间施加高电平的电压信号u

rd

,第1行控制电路、

……

、第i行控制电路、

……

、第m行控制电路的端子v

rd1

、

……

、v

rdi

、

……

、v

rdm

处为高电平的电压信号u

rd

,高电平的电压信号u

rd

的幅值小于阵列忆阻器阈值电压;在电压输入端子v

cr0

与端子gnd之间施加低电平的电压信号u

cr0

使每个行控制电路中第3控制电路选通器中的端子0_chan与端子out连通,即每个行控制电路的端子v

out1

、

……

、v

outi

、

……

、v

outm

与各自对应的端子v

rd1

、

……

、v

rdi

、

……

、v

rdm

连通,则高电平的电压信号u

rd

施加在忆阻器阵列中每个阵列忆阻器的端子a

r0

上。

[0054]

在电压输入端子v

cr1

与端子gnd之间施加低电平的电压信号u

cr1

,每个响应输出电路中第1分路器中的端子in与端子0_chan连通、第2分路器中的端子in与端子0_chan连通,从而使响应输出电路端子i

2j-1

和i

2j

与第1负载电阻的端子rl

10

和第2负载电阻的端子rl

20

对应连接。

[0055]

在电压输入端子v

cr2

与端子gnd之间施加低电平的电压信号u

cr2

,每个响应输出电路中输出电路选通器中的端子0_chan与端子out连通,每个响应输出电路中电压比较器的端子vo与端子v

rj

连通。

[0056]

施加高电平的电压信号u

rd

后,忆阻器阵列中每个阵列忆阻器所产生的电流叠加在各自所在的位线上。

[0057]

所述忆阻器阵列位线bl

2j-1

的电流为:

[0058][0059]

式(1)中:

[0060]ard

表示高电平的电压信号u

rd

的幅值,v;

[0061]ri,2j-1

表示忆阻器阵列第i行第2j-1列阵列忆阻器的阻值,ω;

[0062]rl1

表示响应输出电路中第1负载电阻的阻值,ω。

[0063]

所述忆阻器阵列位线bl

2j

的电流为:

[0064]

[0065]

式(2)中:

[0066]ard

表示高电平的电压信号u

rd

的幅值,v;

[0067]ri,2j

表示忆阻器阵列第i行第2j列上阵列忆阻器的阻值,ω;

[0068]rl2

表示响应输出电路中第2负载电阻的阻值,ω。

[0069]

位线bl1的电流i1通过第1响应输出电路的端子i1流经第1响应输出电路中的第1负载电阻,第1负载电阻的端子rl

10

处的电压输入到电压比较器的正向输入端子v

+

。

[0070]

位线bl2的电流i2通过第1响应输出电路的端子i2流经第1个响应输出电路中的第2负载电阻,第2负载电阻的端子rl

20

处的电压输入到电压比较器的反向输入端子v-,第1个响应输出电路的端子v

r1

输出响应电压u

r1

。

[0071]

……

;类似地,

[0072]

第j响应输出电路的端子v

rj

输出响应电压u

rj

。

[0073]

第n响应输出电路的端子v

rn

输出响应电压u

rn

。

[0074]

由于采用上述技术方案,本发明具有如下积极效果:

[0075]

本发明以阵列忆阻器和延迟电路忆阻器处于高阻态时阻值分布的随机性作为忆阻器阵列puf电路的熵源,在步骤一时,给行控制电路和响应输出电路施加相关电压信号,使忆阻器阵列puf电路中所有忆阻器阵列中的阵列忆阻器均复位为高阻态。在步骤二时,忆阻器阵列puf电路根据输入的激励电压信号选中忆阻器阵列中的部分阵列忆阻器,对选中的阵列忆阻器施加高电平的电压信号u

chlg

,且在随机延迟电路的作用下使得高电平的电压信号u

chlg

施加在阵列忆阻器上的时间是随机的,最终导致被选中忆阻器阵列中的阵列忆阻器在高阻状态下进行一次随机的阻值减小。在步骤三时,给行控制电路和响应输出电路施加相关电压信号,并通过比较忆阻器阵列每列电流流经负载电阻产生的电压大小得出响应。

[0076]

综上所述,本发明每次产生的响应电压用到了忆阻器阵列puf电路所有的熵源,熵源利用效率高。

[0077]

本发明在步骤二时,忆阻器阵列puf电路根据施加的激励电压信号选中忆阻器阵列中的部分阵列忆阻器,对选中的阵列忆阻器进行一次随机的阻值减小,激励电压信号不同,所选中的阵列忆阻器亦不同,选中阵列忆阻器的阻值减小量也不同;导致激励电压信号不同时,忆阻器阵列中阵列忆阻器的阻值不同,即忆阻器阵列puf电路的参数不同,随着激励电压信号的变化电路参数也随之变化,这使机器学习算法难以准确的建立忆阻器阵列puf电路的模型。因而,该忆阻器阵列puf电路具有抗机器学习的能力,且未减少忆阻器阵列puf电路响应的位数。

[0078]

本发明除了忆阻器阵列中阵列忆阻器处于高阻态时阻值分布的随机性作为忆阻器阵列puf电路的熵源外,随机延迟电路中的延迟电路忆阻器处于高阻态时阻值分布的随机性也能作为puf的熵源,因此具有双重熵源,故具有良好的核心性能。

[0079]

因此,本发明具有抗机器学习能力强、熵源利用率高和核心性能指标良好的特点。

附图说明

[0080]

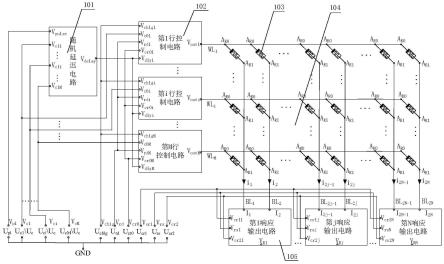

图1为本发明的一种结构示意图;

[0081]

图2为图1中随机延迟电路101的一种结构示意图;

[0082]

图3为图1中第1行控制电路102的一种结构示意图;

[0083]

图4为图1中第1响应输出电路105的一种结构示意图;

[0084]

图5为本发明的另一种结构示意图;

[0085]

图6为图5中随机延迟电路101的一种结构示意图;

[0086]

图7为本发明的又一种结构示意图;

[0087]

图8为图7中随机延迟电路101的一种结构示意图。

具体实施方式

[0088]

现结合附图和具体实施方式对本发明作进一步的描述,并非对其保护范围的限制。

[0089]

一种忆阻器阵列puf电路及其使用方法。

[0090]

为了叙述方便,先将下述字母所表示的物理意义统一描述如下:

[0091]

i表示行控制电路102的个数,1《i≤m,m为大于1的自然数;

[0092]

j表示响应输出电路105的个数,1《j≤n,n为大于1的自然数。

[0093]

如图1所示,所述忆阻器阵列puf电路是由随机延迟电路101、m个行控制电路102、m

×

2n个阵列忆阻器103组成的忆阻器阵列104和n个响应输出电路105组成。其中:

[0094]

如图1所示,随机延迟电路101的端子v

pulse

与电压输入端子v

pl

连接,随机延迟电路101的端子v

c11

、

……

、v

c1i

、

……

、v

c1m

与对应的电压输入端子v

c1

、

……

、v

ci

、

……

、v

cm

连接;随机延迟电路101的端子v

delay

与第1行控制电路102的端子v

dly1

、

……

、第i行控制电路102的端子v

dlyi

、

……

、第m行控制电路102的端子v

dlym

分别连接。

[0095]

如图1所示,第1行控制电路102的端子v

chlg1

、

……

、第i行控制电路102的端子v

chlgi

、

……

、第m行控制电路102的端子v

chlgm

分别与电压输入端子v

chlg

连接;第1行控制电路102的端子v

c01

、

……

、第i行控制电路102的端子v

c0i

、

……

、第m行控制电路102的端子v

c0m

与对应的电压输入端子v

c1

、

……

、v

ci

、

……

、v

cm

连接;第1行控制电路102的端子v

rd1

、

……

、第i行控制电路102的端子v

rdi

、

……

、第m行控制电路102的端子v

rdm

分别与电压输入端子v

rd

连接;第1行控制电路102的端子v

cr01

、

……

、第i行控制电路102的端子v

cr0i

、

……

、第m行控制电路102的端子v

cr0m

分别与电压输入端子v

cr0

连接。

[0096]

如图1所示,忆阻器阵列104由m

×

2n个阵列忆阻器103组成;第1行控制电路102的端子v

out1

通过对应的字线wl1与第1行的2n个阵列忆阻器103的端子a

r0

连接,

……

,第i行控制电路102的端子v

outi

通过对应的字线wli与第i行的2n个阵列忆阻器103的端子a

r0

连接,

……

,第m行控制电路102的端子v

outm

通过对应的字线wlm与第m行的2n个阵列忆阻器103的端子a

r0

连接。

[0097]

如图1所示,第1响应输出电路105的端子i1、端子i2通过各自的位线bl1、bl2与忆阻器阵列104中第1列阵列忆阻器103的端子a

r1

、第2列阵列忆阻器103的端子a

r1

对应连接,

……

,第j响应输出电路105的端子i

2j-1

、端子i

2j

通过各自的位线bl

2j-1

、bl

2j

与忆阻器阵列104中第2j-1列阵列忆阻器103的端子a

r1

、第2j列阵列忆阻器103的端子a

r1

对应连接,

……

,第n响应输出电路105的端子i

2n-1

、端子i

2n

通过各自的位线bl

2n-1

、bl

2n

与忆阻器阵列104中第2n-1列阵列忆阻器103的端子a

r1

、第2n列阵列忆阻器103的端子a

r1

对应连接。

[0098]

如图1所示,第1响应输出电路105的端子v

cr11

、

……

、第j响应输出电路105的端子vcr1j

、

……

、第n响应输出电路105的端子v

cr1n

分别与电压输入端子v

cr1

连接;第1响应输出电路105的端子v

rs1

、

……

、第j响应输出电路105的端子v

rsj

、

……

、第n响应输出电路105的端子v

rsn

分别与电压输入端子v

rs

连接;第1响应输出电路105的端子v

cr21

、

……

、第j响应输出电路105的端子v

cr2j

、

……

、第n响应输出电路105的端子v

cr2n

分别与电压输入端子v

cr2

连接。

[0099]

如图1所示,在电压输入端子v

pl

、v

chlg

、v

rd

、v

cr0

、v

cr1

、v

rs

、v

cr2

与端子gnd之间施加对应的电压信号u

pl

、u

chlg

、u

rd

、u

cr0

、u

cr1

、u

rs

、u

cr2

;在电压输入端子v

c1

、

……

、v

ci

、

……

、v

cm

与端子gnd之间施加对应的电压信号u

c1

或uc、

……

、u

ci

或uc、

……

、u

cm

或uc。

[0100]

第1响应输出电路105的端子v

r1

、

……

、第j响应输出电路105的端子v

rj

、

……

、第n响应输出电路105的端子v

rn

输出对应的响应电压u

r1

、

……

、u

rj

、

……

、u

rn

。

[0101]

如图2所示,所述随机延迟电路101由m个延迟单元202和nmos晶体管204组成;第1延迟单元202的端子out与第2延迟单元202的端子in连接,

……

,第i-1延迟单元202的端子out与第i延迟单元202的端子in连接,

……

,第m-1延迟单元202的端子out与第m延迟单元202的端子in连接,第m延迟单元202的端子out与nmos晶体管204的漏极连接。

[0102]

如图2所示,第1延迟单元202的端子in与两个延迟电路忆阻器201的端子a

r0

分别连接,两个延迟电路忆阻器201的端子a

r1

与第1延迟电路选通器203的端子1_chan和端子0_chan对应连接;所述第2延迟单元202、

……

、第i延迟单元202、

……

、第m延迟单元202与第1延迟单元202的结构相同。

[0103]

如图2所示,第1延迟单元202的端子in与随机延迟电路101的端子v

pulse

连接,第m延迟单元202的端子out与随机延迟电路101的端子v

delay

连接;所述第1延迟单元202、

……

、第i延迟单元202、

……

、第m延迟单元202的端子sel与随机延迟电路101的端子v

cl1

、

……

、v

cli

、

……

、v

clm

对应连接。

[0104]

如图3所示,所述第1行控制电路102由第1控制电路选通器301、第2控制电路选通器302和第3控制电路选通器303组成;第1控制电路选通器301的端子out与第2控制电路选通器302的端子1_chan连接,第2控制电路选通器302的端子out与第3控制电路选通器303的端子1_chan连接,第3控制电路选通器303的端子out与第1行控制电路102端子v

out1

连接。

[0105]

如图3所示,第1控制电路选通器301的端子1_chan与gnd连接,第1控制电路选通器301的端子0_chan与第1行控制电路102的端子v

chlg1

连接,第1控制电路选通器301的端子sel与第1行控制电路102的端子v

dly1

连接,第2控制电路选通器302的端子0_chan与gnd连接,第2控制电路选通器302的端子sel与第1行控制电路102的端子v

c01

连接,第3控制电路选通器303的端子0_chan与第1行控制电路102端子v

rd1

连接,第3控制电路选通器303的端子sel与第1行控制电路102的v

cr01

连接。

[0106]

所述第2行控制电路102、

……

、第i行控制电路102、

……

、第m行控制电路102均与第1行控制电路102的结构相同。

[0107]

如图4所示,所述第1响应输出电路105的结构是,第1分路器401的端子in与第1响应输出电路105的端子i1连接,第2分路器402的端子in与第1响应输出电路105的端子i2连接,第1分路器401的端子sel和第2分路器402的端子sel分别与第1响应输出电路105的端子v

cr11

连接,第1分路器401的端子1_chan和第2分路器402的端子1_chan分别与第1响应输出电路105的端子v

rs1

连接,第1分路器401的端子0_chan与第1负载电阻406的端子rl

10

连接,第2分路器402的端子0_chan与第2负载电阻403的端子rl

20

连接。

[0108]

如图4所示,第1负载电阻406和第2负载电阻403的端子rl

11

、rl

21

分别与gnd连接;电压比较器404的输入端子v

+

和v-与第1负载电阻406的端子rl

10

和第2负载电阻403的端子rl

20

对应连接,电压比较器404的输出端子vo与输出电路选通器405的端子0_chan连接,输出电路选通器405的端子1_chan与gnd连接,输出电路选通器405端子sel与第1响应输出电路105的端子v

cr21

连接,输出电路选通器405的端子out与第1响应输出电路105的端子v

r1

连接。

[0109]

所述第2响应输出电路105、

……

、第j响应输出电路105、

……

、与第n响应输出电路105均与第1响应输出电路105的结构相同。

[0110]

所述的阵列忆阻器103和延迟电路忆阻器201相同,均为具有阈值电压的忆阻器;阵列忆阻器103和延迟电路忆阻器201的初始状态均处于高阻态。

[0111]

所述忆阻器阵列puf电路的使用方法是:

[0112]

步骤一、所有忆阻器复位

[0113]

在电压输入端子v

c1

、

……

、v

ci

、

……

、v

cm

与端子gnd之间施加相同的低电平的电压信号uc;在电压输入端子v

cr0

、v

cr1

、v

cr2

、v

rs

与端子gnd之间施加对应的高电平的电压信号u

cr0

、u

cr1

、u

cr2

、u

rs

,其余电压输入端子与端子gnd之间均不施加任何电压信号。

[0114]

在电压输入端子v

c1

、

……

、v

ci

、

……

、v

cm

与端子gnd之间施加相同的低电平的电压信号uc,每个行控制电路102中第2控制电路选通器302中的端子0_chan与端子out连通。在电压输入端子v

cr0

与端子gnd之间施加高电平的电压信号u

cr0

,每个行控制电路102中第3控制电路选通器303中的端子1_chan与端子out连通,则每个行控制电路102的端子v

out1

、

……

、v

outi

、

……

、v

outm

均与gnd连接,忆阻器阵列104中每个阵列忆阻器103的端子a

r0

与gnd连接。

[0115]

在电压输入端子v

cr1

与端子gnd之间施加高电平的电压信号u

cr1

,每个响应输出电路105中,第1分路器401中的端子in与端子1_chan连通、第2分路器402中的端子in与端子1_chan连通。

[0116]

在电压输入端子v

cr2

与端子gnd之间施加高电平的电压信号u

cr2

,每个响应输出电路105中输出电路选通器405中的端子1_chan与端子out连通,则每个响应输出电路105的端子v

r1

、

……

、v

rj

、

……

、v

rn

均与gnd连接,puf电路不输出响应。

[0117]

此时,在电压输入端子v

rs

与端子gnd之间施加高电平的电压信号u

rs

将施加在忆阻器阵列104中每个阵列忆阻器103的端子a

r1

上,高电平的电压信号u

rs

的幅值大于阵列忆阻器103的阈值电压且持续时间超过阵列忆阻器103复位所需的最小时间t

min

,则忆阻器阵列104中的阵列忆阻器103都复位为高阻态。

[0118]

步骤二、施加激励

[0119]

在电压输入端子v

pl

、v

chlg

、v

cr0

、v

cr2

与端子gnd之间施加对应的高电平的电压信号u

pl

、u

chlg

、u

cr0

、u

cr2

;在电压输入端子v

c1

、

……

、v

ci

、

……

、v

cm

与端子gnd之间施加对应的高电平或低电平的激励电压信号u

c1

、

……

、u

ci

、

……

、u

cm

;在电压输入端子v

cr1

与端子gnd之间施加低电平的电压信号u

cr1

,其余电压输入端子与端子gnd之间均不施加任何电压信号。

[0120]

在电压输入端子v

pl

与端子gnd之间施加高电平的电压信号u

pl

,随机延迟电路101的端子v

delay

输出为低电平,每个行控制电路102中第1控制电路选通器301中的端子0_chan与端子out连通。

[0121]

在电压输入端子v

cr0

与端子gnd之间施加高电平的电压信号u

cr0

,每个行控制电路

102中第3控制电路选通器303中的端子1_chan与端子out连通。

[0122]

在电压输入端子v

cr1

与端子gnd之间施加低电平的电压信号u

cr1

,每个响应输出电路105中第1分路器401中的端子in与端子0_chan连通、第2分路器402的端子in与端子0_chan连通。

[0123]

在电压输入端子v

cr2

与端子gnd之间施加高电平的电压信号u

cr2

,每个响应输出电路105中输出电路选通器405中的端子1_chan与端子out连通,从而每个响应输出电路105的端子v

r1

、

……

、v

rj

、

……

、v

rn

分别与gnd连接。

[0124]

在电压输入端子v

chlg

与端子gnd之间施加高电平的电压信号u

chlg

,第1行控制电路102、

……

、第i行控制电路102、

……

、第m行控制电路102的端子v

chlg1

、

……

、v

chlgi

、

……

、v

chlgm

处均为高电平的电压信号u

chlg

,高电平的电压信号u

chlg

的幅值大于阵列忆阻器103的阈值电压。

[0125]

在电压输入端子v

c1

、

……

、v

ci

、

……

、v

cm

与端子gnd之间施加对应的高电平或低电平的激励电压信号u

c1

、

……

、u

ci

、

……

、u

cm

,每个行控制电路102的第2控制电路选通器302中的端子1_chan或端子0_chan与端子out连通。

[0126]

每个行控制电路102的第2控制电路选通器302中的端子1_chan与端子out连通时,高电平的电压信号u

chlg

会施加在每个行控制电路102的端子v

outi

上,即施加在忆阻器阵列104中每个阵列忆阻器103的端子a

r0

上。

[0127]

每个行控制电路102的第2控制电路选通器302中的端子0_chan与端子out连通时,高电平的电压信号u

chlg

在每个行控制电路102的端子v

outi

上均未施加。即忆阻器阵列puf电路会根据施加的激励,成行的选中忆阻器阵列104中的阵列忆阻器103,对选中阵列忆阻器103的a

r0

端施加高电平的电压信号u

chlg

,使选中的阵列忆阻器103阻值减小,未选中的阵列忆阻器103则保持其阻值不变。

[0128]

同时,激励电压信号u

c1

、

……

、u

ci

、

……

、u

cm

施加在随机延迟电路101对应的端子v

c11

、

……

、v

c1i

、、

……

、v

c1m

上,根据激励电压信号u

c1

、

……

、u

ci

、

……

、u

cm

电平的高或低,随机延迟电路101在每个延迟单元202中选中两个延迟电路忆阻器201中的一个与nmos晶体管204的寄生电容组成rc延迟电路,延迟电路忆阻器201高阻态的阻值分布是随机的,则高电平的电压信号u

pl

经过随机延迟电路101后会产生随机的延迟。不同的激励电压信号,选中的延迟电路忆阻器201不同,高电平的电压信号u

pl

随机延迟的时间也不相同;相同的激励电压信号,选中的延迟电路忆阻器201相同,高电平的电压信号u

pl

随机延迟的时间也相同。

[0129]

高电平的电压信号u

pl

经过随机延迟后在随机延迟电路101的端子v

delay

输出,则每个行控制电路102中第1控制电路选通器301中的端子1_chan与端子out连通,此时高电平的电压信号u

chlg

不能继续施加在所选中阵列忆阻器103的端子a

r0

上,阵列忆阻器103的阻值不再减小,从而实现了阵列忆阻器103阻值的随机减小。

[0130]

步骤三、响应输出

[0131]

在电压输入端子v

rd

与端子gnd之间施加高电平的电压信号u

rd

;在电压输入端子v

cr0

、v

cr1

、v

cr2

与端子gnd之间施加对应的低电平的电压信号u

cr0

、u

cr1

、u

cr2

,其余电压输入端子与端子gnd之间均不施加任何电压信号;第1响应输出电路105的端子v

r1

、

……

、第j响应输出电路105的端子v

rj

、

……

、第n响应输出电路105的端子v

rn

分别输出响应电压。

[0132]

在电压输入端子v

rd

与端子gnd之间施加高电平的电压信号u

rd

,第1行控制电路

102、

……

、第i行控制电路102、

……

、第m行控制电路102的端子v

rd1

、

……

、v

rdi

、

……

、v

rdm

处为高电平的电压信号u

rd

,高电平的电压信号u

rd

的幅值小于阵列忆阻器103阈值电压;在电压输入端子v

cr0

与端子gnd之间施加低电平的电压信号u

cr0

使每个行控制电路102中第3控制电路选通器303中的端子0_chan与端子out连通,即每个行控制电路102的端子v

out1

、

……

、v

outi

、

……

、v

outm

与各自对应的端子v

rd1

、

……

、v

rdi

、

……

、v

rdm

连通,则高电平的电压信号u

rd

施加在忆阻器阵列104中每个阵列忆阻器103的端子a

r0

上。

[0133]

在电压输入端子v

cr1

与端子gnd之间施加低电平的电压信号u

cr1

,每个响应输出电路105中第1分路器401中的端子in与端子0_chan连通、第2分路器402的端子in与第2分路器402的端子0_chan连通,从而使响应输出电路105端子i

2j-1

和i

2j

与第1负载电阻406的端子rl

10

和第2负载电阻403的端子rl

20

对应连接。

[0134]

在电压输入端子v

cr2

与端子gnd之间施加低电平的电压信号u

cr2

,每个响应输出电路105中输出电路选通器405中的端子0_chan与端子out连通,每个响应输出电路105中电压比较器404的端子vo与端子v

rj

连通。

[0135]

施加高电平的电压信号u

rd

后,忆阻器阵列104中每个阵列忆阻器103所产生的电流叠加在各自所在的位线上。

[0136]

所述忆阻器阵列104位线bl

2j-1

的电流为:

[0137][0138]

式(1)中:

[0139]ard

表示高电平的电压信号u

rd

的幅值,v;

[0140]ri,2j-1

表示忆阻器阵列104第i行第2j-1列阵列忆阻器103的阻值,ω;

[0141]rl1

表示响应输出电路105中第1负载电阻406的阻值,ω。

[0142]

所述忆阻器阵列104位线bl

2j

的电流为:

[0143][0144]

式(2)中:

[0145]ard

表示高电平的电压信号u

rd

的幅值,v;

[0146]ri,2j

表示忆阻器阵列104第i行第2j列上阵列忆阻器103的阻值,ω;

[0147]rl2

表示响应输出电路105中第2负载电阻403的阻值,ω。

[0148]

位线bl1的电流i1通过第1响应输出电路105的端子i1流经第1响应输出电路105中的第1负载电阻406,第1负载电阻406的端子rl

10

处的电压输入到电压比较器404的正向输入端子v

+

。

[0149]

位线bl2的电流i2通过第1响应输出电路105的端子i2流经第1个响应输出电路105中的第2负载电阻403,第2负载电阻403的端子rl

20

处的电压输入到电压比较器404的反向输入端子v-,第1个响应输出电路105的端子v

r1

输出响应电压u

r1

。

[0150]

……

;类似地,

[0151]

第j响应输出电路105的端子v

rj

输出响应电压u

rj

。

[0152]

第n响应输出电路105的端子v

rn

输出响应电压u

rn

。

[0153]

实施例1

[0154]

一种忆阻器阵列puf电路及其使用方法。

[0155]

为了叙述方便,先将下述字母所表示的物理意义统一描述如下:

[0156]

i表示行控制电路102的个数,1《i≤m,m=3;

[0157]

j表示响应输出电路105的个数,1《j≤n,n=3。

[0158]

如图5所示,所述忆阻器阵列puf电路是由随机延迟电路101、3个行控制电路102、3

×2×

3个阵列忆阻器103组成的忆阻器阵列104和3个响应输出电路105组成。其中:

[0159]

如图5所示,随机延迟电路101的端子v

pulse

与电压输入端子v

pl

连接,随机延迟电路101的端子v

c11

、v

c12

、v

c13

与对应的电压输入端子v

c1

、v

c2

、v

c3

连接;随机延迟电路101的端子v

delay

与第1行控制电路102的端子v

dly1

、第2行控制电路102的端子v

dly2

、第3行控制电路102的端子v

dly3

分别连接。

[0160]

如图5所示,第1行控制电路102的端子v

chlg1

、第2行控制电路102的端子v

chlg2

、第3行控制电路102的端子v

chlg3

分别与电压输入端子v

chlg

连接;第1行控制电路102的端子v

c01

、第2行控制电路102的端子v

c02

、第3行控制电路102的端子v

c03

与对应的电压输入端子v

c1

、v

c2

、v

c3

连接;第1行控制电路102的端子v

rd1

、第2行控制电路102的端子v

rd2

、第3行控制电路102的端子v

rd3

分别与电压输入端子v

rd

连接;第1行控制电路102的端子v

cr01

、第2行控制电路102的端子v

cr02

、第3行控制电路102的端子v

cr03

分别与电压输入端子v

cr0

连接。

[0161]

如图5所示,忆阻器阵列104由3

×2×

3个阵列忆阻器103组成;第1行控制电路102的端子v

out1

通过对应的字线wl1与第1行的2n个阵列忆阻器103的端子a

r0

连接,第2行控制电路102的端子v

out2

通过对应的字线wl2与第2行的2

×

2个阵列忆阻器103的端子a

r0

连接,第3行控制电路102的端子v

out3

通过对应的字线wl3与第3行的2

×

2个阵列忆阻器103的端子a

r0

连接。

[0162]

如图5所示,第1响应输出电路105的端子i1、端子i2通过各自的位线bl1、bl2与忆阻器阵列104中第1列阵列忆阻器103的端子a

r1

、第2列阵列忆阻器103的端子a

r1

对应连接,第2响应输出电路105的端子i2×

2-1

、端子i2×2通过各自的位线bl2×

2-1

、bl2×2与忆阻器阵列104中第2

×

2-1列阵列忆阻器103的端子a

r1

、第2

×

2列阵列忆阻器103的端子a

r1

对应连接,第3响应输出电路105的端子i2×

3-1

、端子i2×3通过各自的位线bl2×

3-1

、bl2×3与忆阻器阵列104中第2

×

3-1列阵列忆阻器103的端子a

r1

、第2

×

3列阵列忆阻器103的端子a

r1

对应连接。

[0163]

如图5所示,第1响应输出电路105的端子v

cr11

、第2响应输出电路105的端子v

cr12

、第3响应输出电路105的端子v

cr13

分别与电压输入端子v

cr1

连接;第1响应输出电路105的端子v

rs1

、第2响应输出电路105的端子v

rs2

、第3响应输出电路105的端子v

rs3

分别与电压输入端子v

rs

连接;第1响应输出电路105的端子v

cr21

、第2响应输出电路105的端子v

cr22

、第3响应输出电路105的端子v

cr23

分别与电压输入端子v

cr2

连接。

[0164]

如图5所示,在电压输入端子v

pl

、v

chlg

、v

rd

、v

cr0

、v

cr1

、v

rs

、v

cr2

与端子gnd之间施加对应的电压信号u

pl

、u

chlg

、u

rd

、u

cr0

、u

cr1

、u

rs

、u

cr2

;在电压输入端子v

c1

、v

c2

、v

c3

与端子gnd之间施加对应的电压信号u

c1

或uc、u

c2

或uc、u

c3

或uc。

[0165]

第1响应输出电路105的端子v

r1

、第2响应输出电路105的端子v

r2

、第3响应输出电路105的端子v

r3

输出对应的响应电压u

r1

、u

r2

、u

r3

。

[0166]

如图6所示,所述随机延迟电路101由3个延迟单元202和nmos晶体管204组成;第1

延迟单元202的端子out与第2延迟单元202的端子in连接,第3-1延迟单元202的端子out与第3延迟单元202的端子in连接,第3延迟单元202的端子out与nmos晶体管204的漏极连接。

[0167]

如图6所示,第1延迟单元202的端子in与两个延迟电路忆阻器201的端子a

r0

分别连接,两个延迟电路忆阻器201的端子a

r1

与第1延迟电路选通器203的端子1_chan和端子0_chan对应连接;所述第2延迟单元202、第3延迟单元202与第1延迟单元202的结构相同。

[0168]

如图6所示,第1延迟单元202的端子in与随机延迟电路101的端子v

pulse

连接,第3延迟单元202的端子out与随机延迟电路101的端子v

delay

连接;所述第1延迟单元202、第2延迟单元202、第3延迟单元202的端子sel与随机延迟电路101的端子v

cl1

、v

cl2

、v

cl3

对应连接。

[0169]

如图3所示,所述第1行控制电路102由第1控制电路选通器301、第2控制电路选通器302和第3控制电路选通器303组成;第1控制电路选通器301的端子out与第2控制电路选通器302的端子1_chan连接,第2控制电路选通器302的端子out与第3控制电路选通器303的端子1_chan连接,第3控制电路选通器303的端子out与第1行控制电路102端子v

out1

连接。

[0170]

如图3所示,第1控制电路选通器301的端子1_chan与gnd连接,第1控制电路选通器301的端子0_chan与第1行控制电路102的端子v

chlg1

连接,第1控制电路选通器301的端子sel与第1行控制电路102的端子v

dly1

连接,第2控制电路选通器302的端子0_chan与gnd连接,第2控制电路选通器302的端子sel与第1行控制电路102的端子v

c01

连接,第3控制电路选通器303的端子0_chan与第1行控制电路102端子v

rd1

连接,第3控制电路选通器303的端子sel与第1行控制电路102的v

cr01

连接。

[0171]

所述第2行控制电路102、第3行控制电路102均与第1行控制电路102的结构相同;

[0172]

如图4所示,所述第1响应输出电路105的结构是,第1分路器401的端子in与第1响应输出电路105的端子i1连接,第2分路器402的端子in与第1响应输出电路105的端子i2连接,第1分路器401的端子sel和第2分路器402的端子sel分别与第1响应输出电路105的端子v

cr11

连接,第1分路器401的端子1_chan和第2分路器402的端子1_chan分别与第1响应输出电路105的端子v

rs1

连接,第1分路器401的端子0_chan与第1负载电阻406的端子rl

10

连接,第2分路器402的端子0_chan与第2负载电阻403的端子rl

20

连接。

[0173]

如图4所示,第1负载电阻406和第2负载电阻403的端子rl

11

、rl

21

分别与gnd连接;电压比较器404的输入端子v

+

和v-与第1负载电阻406的端子rl

10

和第2负载电阻403的端子rl

20

对应连接,电压比较器404的输出端子vo与输出电路选通器405的端子0_chan连接,输出电路选通器405的端子1_chan与gnd连接,输出电路选通器405端子sel与第1响应输出电路105的端子v

cr21

连接,输出电路选通器405的端子out与第1响应输出电路105的端子v

r1

连接。

[0174]

所述第2响应输出电路105、第3响应输出电路105均与第1响应输出电路105的结构相同。

[0175]

所述的阵列忆阻器103和延迟电路忆阻器201相同,均为具有阈值电压的忆阻器;阵列忆阻器103和延迟电路忆阻器201的初始状态均处于高阻态。

[0176]

所述忆阻器阵列puf电路使用方法的步骤是:

[0177]

步骤一、所有忆阻器复位

[0178]

在电压输入端子v

c1

、v

c2

、v

c3

与端子gnd之间施加相同的低电平的电压信号uc=0v;在电压输入端子v

cr0

、v

cr1

、v

cr2

、v

rs

与端子gnd之间施加对应的高电平的电压信号u

cr0

=1.8v、u

cr1

=1.8v、u

cr2

=1.8v、u

rs

=2v;其余电压输入端子与端子gnd之间均不施加任何电压信号。

[0179]

在步骤一中,忆阻器阵列104中的所有阵列忆阻器103复位为高阻态:

[0180]

第1行第1列至第1行第6列的阻值依次为11005.07ω、10796.31ω、10188.86ω、9030.03ω、11257.14ω、9399.94ω;

[0181]

第2行第1列至第2行第6列的阻值依次为9020.38ω、11563.61ω、8554.45ω、11362.87ω、8974.11ω、8786.38ω;

[0182]

第3行第1列至第3行第6列的阻值依次为10023.83ω、11837.17ω、8597.18ω、9017.13ω、11717.05ω、9004.34ω。

[0183]

步骤二、施加激励

[0184]

在电压输入端子v

pl

、v

chlg

、v

cr0

、v

cr2

与端子gnd之间施加对应的高电平的电压信号u

pl

=2v、u

chlg

=2v、u

cr0

=1.8v、u

cr2

=1.8v;在电压输入端子v

c1

、v

c2

、v

c3

与端子gnd之间施加对应的高电平或低电平的激励电压信号u

c1

=1.8v、u

c2

=1.8v、u

c3

=0v;在电压输入端子v

cr1

与端子gnd之间施加低电平的电压信号u

cr1

=0v,其余电压输入端子与端子gnd之间均不施加任何电压信号;

[0185]

在过步骤二中,忆阻器阵列104中的所有阵列忆阻器103的阻值随机减小,减小后的阻值为:

[0186]

第1行第1列至第1行第6列的阻值依次为8682.30ω、8564.08ω、8210.38ω、7494.76ω、8822.78ω、7729.08;

[0187]

第2行第1列至第2行第6列的阻值依次为7488.57ω、8990.28ω、7185.30ω、8880.97ω、7458.84ω、7337.36ω;

[0188]

第3行第1列至第3行第6列的阻值依次为10023.83ω、11837.17ω、8597.18ω、9017.13ω、11717.05ω、9004.34ω。

[0189]

步骤三、响应输出

[0190]

在电压输入端子v

rd

与端子gnd之间施加高电平的电压信号u

rd

=1.5v;在电压输入端子v

cr0

、v

cr1

、v

cr2

与端子gnd之间施加对应的低电平的电压信号u

cr0

=0v、u

cr1

=0v、u

cr2

=0v,其余电压输入端子与端子gnd之间均不施加任何电压信号;第1响应输出电路105的端子v

r1

、第2响应输出电路105的端子v

r2

、第3响应输出电路105的端子v

r3

分别输出响应电压。

[0191]

本实例中第1负载电阻406和第2负载电阻403的阻值r

l1

和r

l2

均为500ω。

[0192]

所述忆阻器阵列104位线bl1的电流为:

[0193][0194]

式(1)中:

[0195]ard

表示高电平的电压信号u

rd

的幅值,v;

[0196]ri,1

表示忆阻器阵列104第i行第1列阵列忆阻器103的阻值,ω;

[0197]rl1

表示响应输出电路105中第1负载电阻406的阻值,ω。

[0198]

将步骤二和步骤三中的高电平的电压信号u

rd

的幅值、第1行~第3行的第1列阵列忆阻器103的阻值、响应输出电路105中第1负载电阻406的阻值代入式(1)。

[0199]

则,所述忆阻器阵列104位线bl1的电流为电流i1=0.0003946a。

[0200]

所述忆阻器阵列104位线bl2的电流为:

[0201][0202]

式(2)中:

[0203]ard

表示高电平的电压信号u

rd

的幅值,v;

[0204]ri,2

表示忆阻器阵列104第i行第2列上阵列忆阻器103的阻值,ω;

[0205]rl2

表示响应输出电路105中第2负载电阻403的阻值,ω。

[0206]

将步骤二和步骤三中的高电平的电压信号u

rd

的幅值、第1行~第3行的第2列阵列忆阻器103的阻值、响应输出电路105中第2负载电阻406的阻值代入式(2)。

[0207]

则,所述忆阻器阵列104位线bl2的电流i2=0.0003561a。

[0208]

类似地,所述忆阻器阵列104位线bl3、位线bl4、位线bl5、位线bl6的电流依次为i3=0.0004258a、i4=0.0004041a、i5=0.0003777a、i6=0.0004252a。

[0209]

第1响应输出电路105中电压比较器404的正向输入端子v

+

处的电压为0.1975v,反向输入端子v-处的电压为0.1781v,因此响应电压u

r1

=2v;第2响应输出电路105中电压比较器404的正向输入端子v

+

处的电压为0.2129v,反向输入端子v-处的电压为0.2021v,因此响应电压u

r2

=2v;第3响应输出电路105中电压比较器404的正向输入端子v

+

处的电压为0.1889v,反向输入端子v-处的电压为0.2126v,因此响应电压u

r3

=0v。

[0210]

实施例2

[0211]

一种忆阻器阵列puf电路及其使用方法。

[0212]

为了叙述方便,先将下述字母所表示的物理意义统一描述如下:

[0213]

i表示行控制电路102的个数,1《i≤m,m=5;

[0214]

j表示响应输出电路105的个数,1《j≤n,n=2。

[0215]

如图7所示,所述忆阻器阵列puf电路是由随机延迟电路101、5个行控制电路102、5

×2×

2个阵列忆阻器103组成的忆阻器阵列104和2个响应输出电路105组成。其中:

[0216]

如图7所示,随机延迟电路101的端子v

pulse

与电压输入端子v

pl

连接,随机延迟电路101的端子v

c11

、v

c12

、v

c13

、v

c14

、v

c15

与对应的电压输入端子v

c1

、v

c2

、v

c3

、v

c4

、v

c5

连接;随机延迟电路101的端子v

delay

与第1行控制电路102的端子v

dly1

、第2行控制电路102的端子v

dly2

、第3行控制电路102的端子v

dly3

、第4行控制电路102的端子v

dly4

、第5行控制电路102的端子v

dly5

分别连接。

[0217]

如图7所示,第1行控制电路102的端子v

chlg1

、第2行控制电路102的端子v

chlg2

、第3行控制电路102的端子v

chlg3

、第4行控制电路102的端子v

chlg4

、第5行控制电路102的端子v

chlg5

分别与电压输入端子v

chlg

连接;第1行控制电路102的端子v

c01

、第2行控制电路102的端子v

c02

、第3行控制电路102的端子v

c03

、第4行控制电路102的端子v

c04

、第5行控制电路102的端子v

c05

与对应的电压输入端子v

c1

、v

c2

、v

c3

、v

c4

、v

c5

连接;第1行控制电路102的端子v

rd1

、第2行控制电路102的端子v

rd2

、第3行控制电路102的端子v

rd3

、第4行控制电路102的端子v

rd4

、第5行控制电路102的端子v

rd5

分别与电压输入端子v

rd

连接;第1行控制电路102的端子v

cr01

、第2行控制电路102的端子v

cr02

、第3行控制电路102的端子v

cr03

、第4行控制电路102的端子v

cr04

、第5行控制电路102的端子v

cr05

分别与电压输入端子v

cr0

连接。

[0218]

如图7所示,忆阻器阵列104由5

×2×

2个阵列忆阻器103组成;第1行控制电路102

的端子v

out1

通过对应的字线wl1与第1行的2n个阵列忆阻器103的端子a

r0

连接,第2行控制电路102的端子v

out2

通过对应的字线wl2与第2行的2

×

2个阵列忆阻器103的端子a

r0

连接,第3行控制电路102的端子v

out3

通过对应的字线wl3与第3行的2

×

2个阵列忆阻器103的端子a

r0

连接,第4行控制电路102的端子v

out4

通过对应的字线wl4与第4行的2

×

2个阵列忆阻器103的端子a

r0

连接,第5行控制电路102的端子v

out5

通过对应的字线wl5与第5行的2

×

2个阵列忆阻器103的端子a

r0

连接。

[0219]

如图7所示,第1响应输出电路105的端子i1、端子i2通过各自的位线bl1、bl2与忆阻器阵列104中第1列阵列忆阻器103的端子a

r1

、第2列阵列忆阻器103的端子a

r1

对应连接,第2响应输出电路105的端子i2×

2-1

、端子i2×2通过各自的位线bl2×

2-1

、bl2×2与忆阻器阵列104中第2

×

2-1列阵列忆阻器103的端子a

r1

、第2

×

2列阵列忆阻器103的端子a

r1

对应连接。

[0220]

如图7所示,第1响应输出电路105的端子v

cr11

、第2响应输出电路105的端子v

cr12

分别与电压输入端子v

cr1

连接;第1响应输出电路105的端子v

rs1

、第2响应输出电路105的端子v

rs2

分别与电压输入端子v

rs

连接;第1响应输出电路105的端子v

cr21

、第2响应输出电路105的端子v

cr22

分别与电压输入端子v

cr2

连接。

[0221]

如图7所示,在电压输入端子v

pl

、v

chlg

、v

rd

、v

cr0

、v

cr1

、v

rs

、v

cr2

与端子gnd之间施加对应的电压信号u

pl

、u

chlg

、u

rd

、u

cr0

、u

cr1

、u

rs

、u

cr2

;在电压输入端子v

c1

、v

c2

、v

c3

、v

c4

、v

c5

与端子gnd之间施加对应的电压信号u

c1

或uc、u

c2

或uc、u

c3

或uc、u

c4

或uc、u

c5

或uc。

[0222]

第1响应输出电路105的端子v

r1

、第2响应输出电路105的端子v

r2

输出对应的响应电压u

r1

、u

r2

。

[0223]

如图8所示,所述随机延迟电路101由5个延迟单元202和nmos晶体管204组成;第1延迟单元202的端子out与第2延迟单元202的端子in连接,第2延迟单元202的端子out与第3延迟单元202的端子in连接,第3延迟单元202的端子out与第4延迟单元202的端子in连接,第4延迟单元202的端子out与第5延迟单元202的端子in连接,第5延迟单元202的端子out与nmos晶体管204的漏极连接。

[0224]

如图8所示,第1延迟单元202的端子in与两个延迟电路忆阻器201的端子a

r0

分别连接,两个延迟电路忆阻器201的端子a

r1

与第1延迟电路选通器203的端子1_chan和端子0_chan对应连接;所述第2延迟单元202、第3延迟单元202、第4延迟单元202、第5延迟单元202与第1延迟单元202的结构相同。

[0225]

如图8所示,第1延迟单元202的端子in与随机延迟电路101的端子v

pulse

连接,第m延迟单元202的端子out与随机延迟电路101的端子v

delay

连接;所述第1延迟单元202、第2延迟单元202、第3延迟单元202、第4延迟单元202、第5延迟单元202的端子sel与随机延迟电路101的端子v

cl1

、v

cl2

、v

cl3

、v

cl4

、v

cl5

对应连接。

[0226]

如图3所示,所述第1行控制电路102由第1控制电路选通器301、第2控制电路选通器302和第3控制电路选通器303组成;第1控制电路选通器301的端子out与第2控制电路选通器302的端子1_chan连接,第2控制电路选通器302的端子out与第3控制电路选通器303的端子1_chan连接,第3控制电路选通器303的端子out与第1行控制电路102端子v

out1

连接。

[0227]

如图3所示,第1控制电路选通器301的端子1_chan与gnd连接,第1控制电路选通器301的端子0_chan与第1行控制电路102的端子v

chlg1

连接,第1控制电路选通器301的端子sel与第1行控制电路102的端子v

dly1

连接,第2控制电路选通器302的端子0_chan与gnd连接,第

2控制电路选通器302的端子sel与第1行控制电路102的端子v

c01

连接,第3控制电路选通器303的端子0_chan与第1行控制电路102端子v

rd1

连接,第3控制电路选通器303的端子sel与第1行控制电路102的v

cr01

连接。

[0228]

所述第2行控制电路102、第3行控制电路102、第4行控制电路102、第5行控制电路102均与第1行控制电路102的结构相同。

[0229]

如图4所示,所述第1响应输出电路105的结构是,第1分路器401的端子in与第1响应输出电路105的端子i1连接,第2分路器402的端子in与第1响应输出电路105的端子i2连接,第1分路器401的端子sel和第2分路器402的端子sel分别与第1响应输出电路105的端子v

cr11

连接,第1分路器401的端子1_chan和第2分路器402的端子1_chan分别与第1响应输出电路105的端子v

rs1

连接,第1分路器401的端子0_chan与第1负载电阻406的端子rl

10

连接,第2分路器402的端子0_chan与第2负载电阻403的端子rl

20

连接。

[0230]

如图4所示,第1负载电阻406和第2负载电阻403的端子rl

11

、rl

21

分别与gnd连接;电压比较器404的输入端子v

+

和v-与第1负载电阻406的端子rl

10

和第2负载电阻403的端子rl

20

对应连接,电压比较器404的输出端子vo与输出电路选通器405的端子0_chan连接,输出电路选通器405的端子1_chan与gnd连接,输出电路选通器405端子sel与第1响应输出电路105的端子v

cr21

连接,输出电路选通器405的端子out与第1响应输出电路105的端子v

r1

连接。

[0231]

所述第2响应输出电路105与第1响应输出电路105的结构相同。

[0232]

所述的阵列忆阻器103和延迟电路忆阻器201相同,均为具有阈值电压的忆阻器;阵列忆阻器103和延迟电路忆阻器201的初始状态均处于高阻态。

[0233]

所述忆阻器阵列puf电路的使用方法是:

[0234]

步骤一、所有忆阻器复位

[0235]

在电压输入端子v

c1

、v

c2

、v

c3

、v

c4

、v

c5

与端子gnd之间施加对应的低电平的电压信号uc=0v;在电压输入端子v

cr0

、v

cr1

、v

cr2

、v

rs

与端子gnd之间施加对应的高电平的电压信号u

cr0

=1.8v、u

cr1

=1.8v、u

cr2

=1.8v、u

rs

=2v;其余电压输入端子与端子gnd之间均不施加任何电压信号。

[0236]

在步骤一中,忆阻器阵列104中的所有阵列忆阻器103复位为高阻态:

[0237]

第1行第1列至第5行第1列的阻值依次为1098.6ω、8948.2ω、11829.98ω、10481.38ω、10401.55;

[0238]

第1行第2列至第5行第2列的阻值依次为8690.34ω、8361.73ω、9021.68ω、11434.47ω、11644.38ω;

[0239]

第1行第3列至第5行第3列的阻值依次为10799.53ω、10901.44ω、8920.44ω、10304.10ω、11234.14ω;

[0240]

第1行第4列至第5行第4列的阻值依次为9615.59ω、11954.51ω、8360.69ω、9284.96ω、10046.24ω。

[0241]

步骤二、施加激励

[0242]

在电压输入端子v

pl

、v

chlg

、v

cr0

、v

cr2

与端子gnd之间施加对应的高电平的电压信号u

pl

=2v、u

chlg

=2v、u

cr0

=1.8v、u

cr2

=1.8v;在电压输入端子v

c1

、v

c2

、v

c3

、v

c4

、v

c5

与端子gnd之间施加对应的高电平或低电平的激励电压信号u

c1

=1.8v、u

c2

=0v、u

c3

=1.8v、u

c4

=0v、u

c5

=0v;在电压输入端子v

cr1

与端子gnd之间施加低电平的电压信号u

cr1

=0v,其余电压输入端

子与端子gnd之间均不施加任何电压信号。

[0243]

在步骤二中,忆阻器阵列104中的所有阵列忆阻器103的阻值随机减小,减小后的阻值为:

[0244]

第1行第1列至第5行第1列的阻值依次为7432.5ω、8948.2ω、7715.52ω、10481.38ω、10401.55;

[0245]

第1行第2列至第5行第2列的阻值依次为6478.34ω、8361.73ω、6633.38ω、11434.47ω、11644.38ω;

[0246]

第1行第3列至第5行第3列的阻值依次为7364.27ω、10901.44ω、6586.13ω、10304.10ω、11234.14ω;

[0247]

第1行第4列至第5行第4列的阻值依次为6896.72ω、11954.51ω、6317.54ω、9284.96ω、10046.24ω。

[0248]

步骤三、响应输出

[0249]

在电压输入端子v

rd

与端子gnd之间施加高电平的电压信号u

rd

=1.5v;在电压输入端子v

cr0

、v

cr1

、v

cr2

与端子gnd之间施加对应的低电平的电压信号u

cr0

=0v、u

cr1

=0v、u

cr2

=0v,其余电压输入端子与端子gnd之间均不施加任何电压信号;第1响应输出电路105的端子v

r1

、第2响应输出电路105的端子v

r2

分别输出响应电压。

[0250]

本实例中第1负载电阻406和第2负载电阻403的阻值r

l1

和r

l2

均为500ω。

[0251]

所述忆阻器阵列104位线bl1的电流为:

[0252][0253]

式(1)中:

[0254]ard

表示高电平的电压信号u

rd

的幅值,v;

[0255]ri,1

表示忆阻器阵列104第i行第1列阵列忆阻器103的阻值,ω;

[0256]rl1

表示响应输出电路105中第1负载电阻406的阻值,ω。

[0257]

将步骤二和步骤三中的高电平的电压信号u

rd

的幅值、第1行~第5行的第1列阵列忆阻器103的阻值、响应输出电路105中第1负载电阻406的阻值代入式(1)。

[0258]

则,所述忆阻器阵列104位线bl1上的电流i1=0.0006437a。

[0259]

所述忆阻器阵列104位线bl2的电流为:

[0260][0261]

式(2)中:

[0262]ard

表示高电平的电压信号u

rd

的幅值,v;

[0263]ri,2

表示忆阻器阵列104第i行第2列上阵列忆阻器103的阻值,ω;

[0264]rl2

表示响应输出电路105中第2负载电阻403的阻值,ω。

[0265]

将步骤二和步骤三中的高电平的电压信号u

rd

的幅值、第1行~第5行的第2列阵列忆阻器103的阻值、响应输出电路105中第2负载电阻406的阻值代入式(2)。

[0266]

则,所述忆阻器阵列104位线bl2上的电流i2=0.0006750a。

[0267]

类似地,所述忆阻器阵列104位线bl3、位线bl4的电流依次为i3=0.0006405a、i4=0.0006711a;

[0268]

第1响应输出电路105中电压比较器404的正向输入端子v

+

处的电压为0.3219v,反向输入端子v-处的电压为0.3275v,因此响应电压u

r1

=0v;第2响应输出电路105中电压比较器404的正向输入端子v

+

处的电压为0.3202v,反向输入端子v-处的电压为0.3355v,因此响应电压u

r2

=0v。

[0269]

本具体实施方式具有如下积极效果:

[0270]

本具体实施方式以阵列忆阻器103和延迟电路忆阻器201处于高阻态时阻值分布的随机性作为忆阻器阵列puf电路的熵源,在步骤一时,给行控制电路102和响应输出电路105施加相关电压信号,使忆阻器阵列puf电路中所有忆阻器阵列104中的阵列忆阻器103均复位为高阻态。在步骤二时,忆阻器阵列puf电路根据输入的激励电压信号选中忆阻器阵列104中的部分阵列忆阻器103,对选中的阵列忆阻器103施加对应的高电平的电压信号u

chlg

,且在随机延迟电路101的作用下使得对应的高电平的电压信号u

chlg

施加在阵列忆阻器103上的时间是随机的,最终导致被选中忆阻器阵列104中的阵列忆阻器103在高阻状态下进行一次随机的阻值减小。在步骤三时,给行控制电路102和响应输出电路105施加相关电压信号,并通过比较忆阻器阵列104每列电流流经负载电阻产生的电压大小得出响应。

[0271]

综上所述,本具体实施方式每次产生的响应电压用到了忆阻器阵列puf电路所有的熵源,熵源利用效率高。

[0272]

本具体实施方式在步骤二时,忆阻器阵列puf电路根据施加的激励电压信号选中忆阻器阵列104中的部分阵列忆阻器103,对选中的阵列忆阻器103进行一次随机的阻值减小,激励电压信号不同,所选中的阵列忆阻器103亦不同,选中阵列忆阻器103的阻值减小量也不同;导致激励电压信号不同时,忆阻器阵列104中阵列忆阻器103的阻值不同,即忆阻器阵列puf电路的参数不同,随着激励电压信号的变化电路参数也随之变化,这使机器学习算法难以准确的建立忆阻器阵列puf电路的模型。因而,该忆阻器阵列puf电路具有抗机器学习的能力,且未减少忆阻器阵列puf电路响应的位数。

[0273]

本具体实施方式除了忆阻器阵列104中阵列忆阻器103处于高阻态时阻值分布的随机性作为忆阻器阵列puf电路的熵源外,随机延迟电路101中的延迟电路忆阻器201处于高阻态时阻值分布的随机性也能作为puf的熵源,因此具有双重熵源,故具有良好的核心性能。

[0274]

因此,本具体实施方式具有抗机器学习能力强、熵源利用率高和核心性能指标良好的特点。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1