存储设备的操作方法、主机的操作方法以及存储系统与流程

1.本公开涉及存储器设备,并且尤其涉及存储设备的操作方法、主机的操作方法以及存储系统。

背景技术:

2.存储系统可以包括主机和存储设备。主机通过标准接口连接到存储设备,标准接口诸如是通用闪存(universal flash storage,ufs)、串行高级技术附件(serial advanced technology attachment,sata)、小型计算机小型接口(small computer small interface,scsi)、串行连接scsi(serial attached scsi,sas)和嵌入式多媒体卡(embedded multimedia card,emmc)。

3.在存储系统被初始引导(boot)的情况下,主机发现难以确定连接到主机的存储设备所支持的源电压。在存储系统被初始引导的情况下,存储设备可以被提供有与对应于存储设备的操作电压的电压电平不同的源电压。在每当存储系统被引导时存储设备不支持的源电压被提供给存储设备的情况下,存储设备中包括的元件的可靠性和耐久性可能出现问题。

技术实现要素:

4.本公开提供了一种存储设备的操作方法、主机的操作方法以及包括存储设备和主机的存储系统,其中存储设备在被初始引导时被供应有存储设备的目标电压,并且每当引导时向存储设备提供的高于存储设备的操作电压的源电压被最小化。

5.根据示例实施例的一方面,提供了一种包括非易失性存储器的存储设备的操作方法。该操作方法包括:通过第一电压信号引脚接收第一源电压;基于第一源电压不同于存储设备的目标电压,将第一源电压控制到目标电压;从主机接收指示与存储设备的操作电压相关联的信息请求的命令;通过使用存储设备向主机发送对应于信息请求的响应;通过第一电压信号引脚接收具有不同于第一源电压的电压电平的第二源电压;以及向非易失性存储器提供第二源电压。

6.根据示例实施例的方面,提供了一种包括一次性可编程(otp)存储器和主机寄存器的主机的操作方法。该操作方法包括:向电力管理集成电路提供第一电压控制信号,以控制第一源电压被提供给存储设备;向存储设备发送指示存储设备的特性信息请求的第一命令;从存储设备接收对应于特性信息请求的响应;基于该响应生成连接控制信号以控制主机寄存器和otp存储器设备之间的连接;以及基于主机寄存器和otp存储器设备之间的连接,向电力管理集成电路提供第一电压控制信号和第二电压控制信号之一,以控制电力管理集成电路向存储设备提供具有不同于第一源电压的电压电平的第二源电压。otp存储器设备被配置为存储源电压信息,并且主机寄存器被配置为存储用于控制从电力管理集成电路输出的源电压的第二命令。

7.根据示例实施例的方面,一种存储系统包括:电力管理集成电路,被配置为生成源

电压;存储设备,被配置为从电力管理集成电路接收第一源电压,并将第一源电压控制到存储设备的目标电压;以及主机,被配置为从存储设备接收与存储设备的操作电压相关联的数据,并基于该数据控制电力管理集成电路向存储设备提供具有不同于第一源电压的电压电平的第二源电压。

附图说明

8.从下面结合附图对示例实施例的描述中,上述和其他方面将变得更加明显,其中:

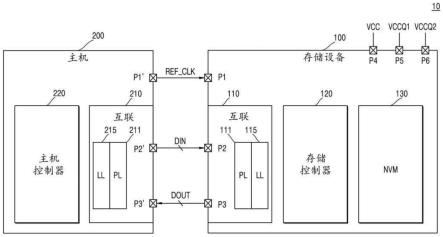

9.图1是示出根据示例实施例的存储系统的框图;

10.图2是示出根据示例实施例的包括电力管理集成电路的存储系统的框图;

11.图3是用于描述根据示例实施例的源电压的图;

12.图4是示出根据示例实施例的电压控制器的图;

13.图5是用于描述根据示例实施例的电压控制器的内部信号的图;

14.图6是示出根据示例实施例的存储设备的操作方法的流程图;

15.图7是示出根据示例实施例的包括一次性可编程(otp)存储器设备的存储系统的框图;

16.图8是用于描述根据示例实施例的otp存储器设备的源电压和连接信号的图;

17.图9是用于描述根据示例实施例的otp存储器设备的源电压和连接信号的图;

18.图10是示出根据示例实施例的主机的操作方法的流程图;

19.图11是用于描述根据示例实施例的通用闪存(ufs)系统的图;

20.图12a至图12c是用于描述ufs卡的形状因子的图;

21.图13是示出根据示例实施例的存储器系统的框图;

22.图14是用于描述根据示例实施例的能够应用于ufs设备的三维(3d)垂直nand(3d vnand)结构的图;并且

23.图15是用于描述根据示例实施例的适用于ufs设备的键合垂直nand(bvnand)结构的图。

具体实施方式

24.在下文中,将参考附图详细描述示例实施例。提供示例实施例使得本公开将是彻底和完整的,并且将向本领域普通技术人员充分传达本发明构思。本发明构思可以被不同地修改。具体描述的示例实施例不限制本发明构思,并且应当理解,本发明构思覆盖了发明构思的思想和技术范围内的所有修改、等同物和替换。

25.图1是示出根据示例实施例的存储系统10的框图。

26.参考图1,存储系统10可以包括存储设备100和主机200。例如,存储设备100可以根据由通用闪存(universal flash storage,ufs)标准定义的接口协议连接到主机200,因此,存储设备100可以包括ufs设备,并且主机200可以包括ufs主机。然而,示例实施例不限于此,并且存储设备100可以根据各种标准接口连接到主机200。

27.主机200可以包括互联210和主机控制器220。主机200可以控制存储设备100上的数据处理操作,并且例如可以控制数据读取操作或数据写入操作。主机200可以表示用于处理数据的数据处理设备,如中央处理单元(central processing unit,cpu)、处理器、微处

理器或应用处理器(application processor,ap)。主机200可以执行操作系统(operating system,os)和/或各种应用。在示例实施例中,存储系统10可以被包括在移动设备中,并且主机200可以用ap来实现。在示例实施例中,主机200可以用片上系统(system-on-a-chip,soc)来实现,并且因此可以嵌入到电子设备中。

28.主机200可以包括生成参考时钟信号ref_clk的参考时钟生成器。参考时钟生成器可以向存储设备100提供参考时钟信号ref_clk,并且可以基于参考时钟信号ref_clk生成用于传输数据的内部时钟信号。

29.主机200还可以包括一次性可编程(one-time-programmable,otp)存储器设备。otp存储器设备可以表示通过一次性编程操作写入数据并且允许多次读取操作的存储器设备。主机200可以基于从存储设备100接收的对应于与操作电压相关联的信息请求的响应来控制otp存储器设备的连接。此外,主机200可以基于otp存储器设备的连接来控制提供给存储器设备100的源电压vcc的电压电平。下面参考图7详细描述包括otp存储器设备的主机200的操作方法。

30.存储设备100可以包括互联110、存储器控制器120和非易失性存储器(nvm)130。存储器控制器120可以响应于来自主机200的写入请求来控制非易失性存储器130将数据写入非易失性存储器130,或者可以响应于来自主机200的读取请求来控制非易失性存储器130读取存储在非易失性存储器130中的数据。

31.非易失性存储器130可以包括多个存储器单元,例如,多个存储器单元可以包括闪存单元。在示例实施例中,多个存储器单元可以包括nand闪存单元。然而,示例实施例不限于此,并且在另一示例实施例中,多个存储器单元可以是电阻式存储器单元,诸如电阻式随机存取存储器(ram)(resistive random access memory,reram)存储器单元、相变ram(phase change ram,pram)存储器单元或磁性ram(magnetic ram,mram)存储器单元。

32.此外,在图1中,示出了互联110和存储器控制器120是分离的元件,但是示例实施例不限于此,并且存储器控制器120可以是包括互联110的元件。除了图1之外,这也可以应用于下面描述的其他附图。例如,当存储器控制器120被实现为一个封装芯片时,互联110可以与其一起被实现在封装芯片中。

33.主机200可以包括第一引脚p1’,并且可以通过第一引脚p1’将参考时钟信号ref_clk发送到存储设备100。存储设备100还可以包括被配置为连接到第一引脚p1’的第一引脚p1,并且可以通过第一引脚p1从主机200接收参考时钟信号ref_clk。

34.主机200可以包括第二引脚p2’和第三引脚p3’,并且存储设备100可以包括被配置为分别连接到第二引脚p2’和第三引脚p3’的第二引脚p2和第三引脚p3。主机200可以通过第二引脚p2’和p2将输入信号din发送到存储设备100,并且因此,第二引脚p2’和p2可以被称为“输入信号引脚”。主机200可以通过第二引脚p2’和p2向存储设备100发送命令。主机200可以通过第二引脚p2’和p2向存储设备100发送命令,该命令包括与存储设备100的操作电压相关联的信息请求。与存储设备100的操作电压相关联的信息可以包括存储设备100的类型和操作电压电平。在一些示例实施例中,输入信号可以是差分输入信号,因此,主机200可以包括两个第二引脚p2’,并且存储设备100可以包括两个第二引脚p2。

35.存储设备100可以通过第三引脚p3’和p3将输出信号dout发送到主机200,因此,第三引脚p3’和p3可以被称为“输出信号引脚”。存储设备100可以通过第三引脚p3’和p3向主

机200发送与主机200的命令相对应的响应。存储设备100可以通过第三引脚p3’和p3向主机200发送响应,该响应对应于与存储设备100的操作电压相关联的信息请求。在一些示例实施例中,输出信号可以是差分输出信号,因此,主机200可以包括两个第三引脚p3’,并且存储设备100可以包括两个第三引脚p3。

36.存储设备100可以包括第四引脚p4至p6。第四引脚p4至p6可以连接到向存储设备100提供电压的电压生成器。根据示例实施例,电压生成器可以是电力管理集成电路(power management integrated circuit,pmic)。pmic可以包括分别对应于第四引脚p4至p6的多个第五引脚,并且可以通过分别连接到第五引脚的第四引脚p4至p6向存储设备100提供电压。

37.存储设备100可以通过第四引脚p4至p6接收电压,因此,第四引脚p4至p6可以被称为“电压信号引脚”。在下文中,第四引脚p4至p6可以分别称为第一电压信号引脚p4、第二电压信号引脚p5和第三电压信号引脚p6。vcc、vccq1和vccq2可以作为源电压输入到存储设备100。vcc可以是用于存储设备100的主源电压,并且可以具有例如2.4v至3.6v的值。vccq1可以是用于供应具有低范围的电压的源电压,并且可以具有例如1.14v至1.26v的值。根据示例实施例,vccq1可以被称为vccq。vccq2可以是用于供应具有低于vcc且高于vccq1的范围的电压的源电压,并且可以具有例如1.7v至1.95v的值。vccq1和vccq2可以被提供给存储设备100。例如,vccq1和vccq2可以被提供给存储器控制器120。

38.vcc可以通过第一电压信号引脚p4提供给存储设备100,vccq1可以通过第二电压信号引脚p5提供给存储设备100,并且vccq2可以通过第三电压信号引脚p6提供给存储设备100。根据示例实施例,可以省略第二电压信号引脚p5和第三电压信号引脚p6中的至少一个。vcc、vccq1和vccq2中的至少一个可以通过包括在存储设备100中的电压控制器来被提供给非易失性存储器130。例如,vcc可以被提供给非易失性存储器130。下面参考图2详细描述电压控制器。

39.互联110和210可以提供用于在主机200和存储设备100之间交换数据的接口。在示例实施例中,互联110可以包括物理层(pl)111和链路层(ll)115,并且物理层111可以连接到第二引脚p2和第三引脚p3。

40.同样,互联210也可以包括物理层211和链路层215,并且物理层211可以连接到第二引脚p2’和第三引脚p3’。物理层111和211中的每个物理层可以包括用于在主机200和存储设备100之间交换数据的物理元件,并且例如可以包括至少一个发送器和至少一个接收器。链路层115和215中的每个链路层可以管理数据的传输和组成,此外,还可以管理数据的错误和完整性。

41.包括在主机200的互联210中的发送器和包括在存储设备100的互联110中的接收器可以配置一个通道。可以在主机200的互联210和存储设备100的互联110之间提供多个通道。多个通道中的每个通道可以是用于承载单向信号、单个信号或信息的传输信道。

42.在示例实施例中,当存储系统10是移动设备时,链路层115和215可以由“unipro”规范定义,并且物理层111和211可以由“m-phy”规范定义。unipro和m-phy各自可以是由移动工业处理器接口(mobile industry processor interface,mipi)联盟提出的接口协议。在这种情况下,链路层115和215可以各自包括物理适配层。物理适配层可以控制物理层111和211,物理层111和211管理数据的符号或管理功率。

43.在一些示例实施例中,存储设备100可以被实现为无dram设备,并且无dram设备可以表示不包括dram缓存的设备。在这种情况下,存储器控制器120可以不包括dram控制器。例如,存储设备100可以使用非易失性存储器130的部分区域作为缓冲存储器。

44.在一些示例实施例中,存储设备100可以是嵌入到电子设备中的内部存储器。例如,存储设备100可以是嵌入式ufs存储器设备、嵌入式多媒体卡(emmc)或固态驱动器(ssd)。然而,示例实施例不限于此,存储设备100可以是非易失性存储器(例如,otp只读存储器(rom)(otprom)、可编程rom(prom)、可擦除可编程rom(eprom)、电可擦除可编程rom(eeprom)、掩模rom和闪存rom)。在一些示例实施例中,存储设备100可以是可拆卸地附接到电子设备的外部存储器。例如,存储设备100可以包括ufs存储卡、压缩闪存(cf)存储卡、安全数字(sd)存储卡、微型安全数字(micro-sd)存储卡、微型安全数字(mini-sd)存储卡、极限数字(xd)存储卡和记忆棒中的至少一种。

45.存储系统10可以用例如电子设备(诸如个人计算机(pc)、膝上型计算机、移动电话、智能电话、平板pc、个人数字助理(pda)、企业数字助理(eda)、数码相机、数码摄像机、音频设备、便携式多媒体播放器(pmp)、个人导航设备或便携式导航设备(pnd)、mp3播放器、手持游戏控制台或电子书)来实现。并且,存储系统10可以用例如各种类型的电子设备(诸如可穿戴设备(诸如手表和头戴式显示器(hmd)))来实现。

46.图2是示出根据示例实施例的包括pmic的存储系统300的框图。

47.参考图2,存储系统300可以包括主机310、存储设备320和pmic 330。图2的存储系统300、主机310和存储设备320可以分别对应于图1的存储系统10、主机200和存储设备100,因此省略对它们的重复描述。

48.pmic 330可以包括pmic控制器331和转换器332。pmic控制器331可以控制pmic 330的整体操作。pmic控制器331可以向转换器332提供pmic控制信号pcs,该pmic控制信号pcs控制由转换器332生成的电压。pmic 330可以连接到外部电力并由其驱动,例如,可以连接到电池电力vbat并由其驱动。pmic 330和主机310可以被配置为一个封装,但是不限于此,并且pmic 330和存储设备320可以被配置为一个封装。

49.转换器332可以接收电池电力vbat以生成具有各种电压电平的源电压vcc、vccq1和vccq2。根据示例实施例,转换器332可以配置有降压调节器,该降压调节器基于电池电力vbat生成低于电池电力vbat的电压电平的源电压vcc1、vcc2、vccq1和vccq2。

50.系统接口333可以连接在pmic 330和主机310之间,并且可以通过系统接口333交换命令、数据和控制信息。主机310可以通过系统接口333向pmic330提供pmic命令pcmd。pmic命令pcmd可以表示用于控制由pmic 330提供给存储设备320的源电压vcc1、vcc2、vccq1和vccq2的电压电平的命令。

51.pmic控制器331可以解码由主机310通过系统接口333提供的pmic命令pcmd,以基于关于命令中包括的电压电平的信息向转换器332提供pmic控制信号pcs。转换器332可以基于pmic控制信号pcs降低或升高电池电力vbat,以生成源电压vcc1、vcc2、vccq1和vccq2。并且,根据示例实施例,转换器332可以基于pmic控制信号pcs来转换源电压vcc的电压电平。

52.存储设备320可以包括电压控制器321和非易失性存储器324。电压控制器321可以包括控制信号生成器322和内部电压电路323。控制信号生成器322可以基于源电压vcc1和

vcc2生成指示是否转换源电压vcc1和vcc2的内部电压控制信号ivcs’、ivcs1和ivcs2。内部电压电路323可以基于内部电压控制信号ivcs’、ivcs1和ivcs2来转换源电压vcc1和vcc2。下面参考图3详细描述电压控制器321的操作。在示例实施例中,电压控制器321可以布置在存储器控制器120的外部。然而,示例实施例不限于此,并且在一些示例实施例中,电压控制器321可以在存储器控制器120中实现。

53.存储设备320可以通过第一电压信号引脚(例如,图1的p4)接收第一源电压vcc1。存储设备320可以从pmic 330接收第一源电压vcc1。第一源电压vcc1可以是存储设备320的主源电压,并且可以表示当存储系统300引导时初始提供给存储设备320的源电压。第一源电压vcc1可以在2.7v至3.6v的范围内。在示例实施例中,第一源电压vcc1可以具有高于存储设备320的操作电压的电压电平。例如,存储设备320的操作电压可以是大约2.5v,并且当引导时初始提供给存储设备320的第一源电压vcc1可以是大约3v。

54.当第一源电压vcc1不同于存储设备320的目标(即,可靠)电压时,存储设备320可以将第一源电压vcc1转换成与存储设备320的目标电压相对应的电压电平。目标电压可以是确保存储设备320的可靠性的电压,并且可以表示用于长时间维持存储设备320中包括的元件的耐久性的电压。目标电压可以是高于或等于存储设备320的操作电压的电压。例如,存储设备320的操作电压可以是大约2.5v,并且目标电压可以在2.5v至2.7v的范围内。

55.控制信号生成器322可以基于第一源电压vcc1生成指示是否转换第一源电压vcc1的初始内部电压控制信号ivcs’。控制信号生成器322可以基于第一源电压vcc1与目标电压的比较来生成内部电压控制信号ivcs’。当第一源电压vcc1高于目标电压时,控制信号生成器322可以生成用于转换第一源电压vcc1的初始内部电压控制信号ivcs’。例如,当第一源电压vcc1的电压电平为大约3v且目标电压的电压电平为大约2.6v时,控制信号生成器322可以生成用于转换第一源电压vcc1的的初始内部电压控制信号ivcs’。

56.内部电压电路323可以基于初始内部电压控制信号ivcs’将第一源电压vcc1的电压电平转换成对应于目标电压的电压电平。例如,当第一源电压vcc1的电压电平为大约2.7v并且目标电压的电压电平为大约2.6v时,内部电压电路323可以基于初始内部电压控制信号ivcs’将第一源电压vcc1的电压电平转换为大约2.6v。

57.内部电压电路323可以将第一源电压vcc1转换成与存储设备320的目标电压相对应的电压电平,并且可以将第一源电压vcc1作为存储器电压v’提供给非易失性存储器324。例如,内部电压电路323可以将第一源电压vcc1的电压电平转换成大约2.6v,并且可以将第一源电压vcc1作为存储器电压v’提供给非易失性存储器324。即使当高于目标电压的第一源电压vcc1被提供给存储设备320时,内部电压电路323也可以将第一源电压vcc1转换成与目标电压相对应的电压电平,因此,与目标电压相对应的电压电平可以被提供给非易失性存储器324。因此,可以增加非易失性存储器324的可靠性。

58.存储设备320可以从主机310接收命令cmd,该命令cmd包括与存储设备320的操作电压相关联的信息请求。存储设备320可以向主机310发送响应res,该响应res对应于与操作电压相关联的信息请求。例如,存储设备320可以从主机310接收包括ufs的版本信息请求的命令cmd,并可向主机310发送对应于ufs版本(即,ufs 3.0版本)的响应res。

59.主机310可以基于从存储设备320接收的响应res生成pmic命令pcmd。详细地,主机控制器311可以基于响应res生成控制pmic 330的pmic命令pcmd,以转换第一源电压vcc1的

电压电平。主机控制器311可以基于响应res生成控制pmic 330的pmic命令pcmd,以生成具有与第一源电压vcc1的电压电平不同的电压电平的第二源电压vcc2。第二源电压vcc2的电压电平可以与存储设备320的操作电压相同。例如,假设第一源电压vcc1的电压电平为大约3v,并且存储设备320的操作电压为大约2.5v,则主机控制器311可以生成控制pmic 330的pmic命令pcmd,以生成对应于大约2.5v的电压电平的第二源电压vcc2。

60.pmic 330可以基于pmic命令pcmd生成第二源电压vcc2而不是第一源电压vcc1。例如,pmic 330可以基于pmic命令pcmd将具有大约3v的电压电平的第一源电压vcc1转换为具有大约2.5v的电压电平的第二源电压vcc2。pmic 330可以通过第一电压信号引脚(例如,图1的p4)向存储设备320提供第二源电压vcc2。

61.控制信号生成器322可以基于第二源电压vcc2生成指示是否转换第二源电压vcc2的内部电压控制信号ivcs1和ivcs2。控制信号生成器322可以基于第二源电压vcc2与目标电压的比较来生成内部电压控制信号ivcs1和ivcs2。

62.当第二源电压vcc2低于或等于目标电压时,控制信号生成器322可以生成用于维持第二源电压vcc2的第一内部电压控制信号ivcs1。例如,假设第二源电压vcc2的电压电平为大约2.5v并且目标电压的电压电平为大约2.6v,控制信号生成器322可以生成第一内部电压控制信号ivcs1。作为另一个示例,假设第二源电压vcc2的电压电平为大约2.6v并且目标电压的电压电平为大约2.6v,控制信号生成器322可以生成第一内部电压控制信号ivcs1。控制信号生成器322可以向内部电压电路323提供第一内部电压控制信号ivcs1。

63.当第二源电压vcc2高于目标电压的电压电平时,控制信号生成器322可以生成用于转换第二源电压vcc2的第二内部电压控制信号ivcs2。例如,假设第二源电压vcc2的电压电平为大约2.7v并且目标电压的电压电平为大约2.6v,则控制信号生成器322可以生成第二内部电压控制信号ivcs2。作为另一个示例,假设第二源电压vcc2的电压电平为大约3v并且目标电压的电压电平为大约2.6v,则控制信号生成器322可以生成第二内部电压控制信号ivcs2。控制信号生成器322可以向内部电压电路323提供第二内部电压控制信号ivcs2。

64.内部电压电路323可以基于第一内部电压控制信号ivcs1和第二内部电压控制信号ivcs2来进行操作。内部电压电路323可以基于第一内部电压控制信号ivcs1被去激活。例如,当第一内部电压控制信号ivcs1被使能时,内部电压电路323可以被去激活,因此,电压控制器321可以将第二源电压vcc2作为存储器电压v’提供给非易失性存储器324,而不经过内部电压电路323。换句话说,当提供给存储设备320的第二源电压vcc2低于或等于目标电压时,第二源电压vcc2可以不被存储设备320转换,并且可以原样提供给非易失性存储器324。

65.内部电压电路323可以基于第二内部电压控制信号ivcs2来转换第二源电压vcc2。当内部电压电路323接收到第二内部电压控制信号ivcs2时,内部电压电路323可以将第二源电压vcc2转换成与目标电压相对应的电压电平。例如,假设第二源电压vcc2为大约2.7v并且目标电压为大约2.6v,则内部电压电路323可以基于第二内部电压控制信号ivcs2将第二源电压vcc2的电压电平转换为大约2.6v。当提供给存储设备320的第二源电压vcc2高于目标电压时,第二源电压vcc2可以被存储设备320转换,并且转换后的第二源电压vcc2可以被提供给非易失性存储器324。

66.在示例实施例中,第一内部电压控制信号ivcs1和第二内部电压控制信号ivcs2可

以具有不同的逻辑电平。例如,当第一内部电压控制信号ivcs1具有逻辑低电平时,第二内部电压控制信号ivcs2可以具有逻辑高电平。当内部电压电路323接收到具有逻辑低电平的内部电压控制信号(即,第一内部电压控制信号ivcs1)时,内部电压电路323的操作可以停止,并且当内部电压电路323接收到具有逻辑高电平的内部电压控制信号(即,第二内部电压控制信号ivcs2)时,内部电压电路323的操作可以改变第二源电压vcc2。初始内部电压控制信号ivcs’、第一内部电压控制信号ivcs1和第二内部电压控制信号ivcs2在逻辑电平和存储设备320接收信号的时序上可以有差异。

67.图3是用于描述根据示例实施例的源电压的图。详细地,图3示出了相对于时间的源电压vcc和存储器电压v’。在下文中,将一起参考图3和图2。

68.在第一引导时段b1的第一时间t1处,存储设备320可以从pmic 330接收第一源电压vcc1。当第一源电压vcc1高于目标电压ev时,控制信号生成器322可以生成初始内部电压控制信号ivcs’。内部电压电路323可以将第一源电压vcc1转换成与目标电压ev相对应的电压电平。内部电压电路323可以向非易失性存储器324提供第一源电压vcc1作为存储器电压v’,第一源电压vc c1具有对应于目标电压ev的电压电平。

69.在第一引导时段b1的第二时间t2处,主机控制器311可以基于存储设备320的响应生成pmic命令pcmd。pmic 330可以基于pmic命令pcmd生成第二源电压vcc2而不是第一源电压vcc1。当第二源电压vcc2低于或等于目标电压时,控制信号生成器322可以生成用于维持第二源电压vcc2的第一内部电压控制信号ivcs1。内部电压电路323可以向非易失性存储器324提供第二源电压vcc2作为存储器电压v’。

70.存储系统300在第一引导时段b1期间的操作可以在第一引导时段b1之后的第二引导时段b2和第三引导时段b3中相同地执行。在图3中,示出了第一引导时段b1至第三引导时段b3,但是在第三引导时段b3之后的引导时段中,存储系统300的操作可以与第一引导时段b1相同地执行。

71.图4是示出根据示例实施例的电压控制器400的图。

72.参考图4,电压控制器400可以包括控制信号生成器410、内部电压电路420、反相器ib和开关元件t。图4的电压控制器400、控制信号生成器410和内部电压电路420可以分别对应于图2的电压控制器321、控制信号生成器322和内部电压电路323,因此省略对它们的重复描述。

73.控制信号生成器410可以接收第一源电压和第二源电压之一作为源电压vcc。例如,控制信号生成器410可以通过第一电压信号引脚(例如,图1的p4)接收源电压vcc,并且可以通过第二电压信号引脚(例如,图1的p5)接收第三源电压vccq1。第三源电压vccq1的电压电平可以不变。控制信号生成器410可以被配置为将源电压vcc与目标电压进行比较。控制信号生成器410可以被配置为将源电压vcc的电压电平与目标电压的电压电平进行比较。

74.控制信号生成器410可以基于源电压vcc生成指示是否转换源电压vcc的内部电压控制信号ivcs’、ivcs1和ivcs2。在示例实施例中,控制信号生成器410可以基于源电压vcc和第三源电压vccq1生成内部电压控制信号ivcs’、ivcs1和ivcs2。例如,控制信号生成器410可以对源电压vcc进行分压,并且可以将分压后的源电压vcc与第三源电压vccq1进行比较,以生成内部电压控制信号ivcs1和ivcs2。当分压后的第一源电压vcc高于第三源电压vccq1时,控制信号生成器410可以生成初始内部电压控制信号ivcs’。

75.当分压后的第二源电压vcc低于或等于第三源电压vccq1时,控制信号生成器410可以生成第一内部电压控制信号ivcs1。当分压后的第二源电压vcc高于第三源电压vccq1时,控制信号生成器410可以生成第二内部电压控制信号ivcs2。例如,假设第二源电压为大约2.5v,分压后的第二源电压vcc为大约1.15v,并且第三源电压vccq1为大约1.2v,在控制信号生成器410接收第二源电压作为源电压vcc的情况下,因为1.15v低于1.2v,所以控制信号生成器410可以生成第一内部电压控制信号ivcs1。假设第二源电压为大约2.7v,分压后的第二源电压vcc为大约1.296v,并且第三源电压vccq1为大约1.2v,因为1.296v高于1.2v,所以控制信号生成器410可以生成第二内部电压控制信号ivcs2。

76.在示例实施例中,控制信号生成器410可以基于第三源电压vccq1生成参考电压,并且可以基于参考电压和源电压vcc生成内部电压控制信号ivcs’、ivcs1和ivcs2。例如,控制信号生成器410可以基于第三源电压vccq1生成参考电压,并且可以将源电压vcc与参考电压进行比较,以生成内部电压控制信号ivcs1和ivcs2。

77.当第一源电压vcc高于参考电压时,控制信号生成器410可以生成初始内部电压控制信号ivcs’。当第二源电压vcc低于或等于参考电压时,控制信号生成器410可以生成第一内部电压控制信号ivcs1。当第二源电压vcc高于参考电压时,控制信号生成器410可以生成第二内部电压控制信号ivcs2。然而,示例实施例不限于此。

78.内部电压控制信号ivcs’、ivcs1和ivcs2可以被提供给反相器ib和内部电压电路420。反相器ib可以输出与内部电压控制信号ivcs’、ivcs1和ivcs2中的每个内部电压控制信号的逻辑电平相反的逻辑电平。

79.内部电压电路420可以基于内部电压控制信号ivcs’、ivcs1和ivcs2来转换源电压vcc。当第一源电压不同于目标电压并且作为源电压vcc被提供给内部电压电路420和控制信号生成器410时,内部电压电路420可以基于初始内部电压控制信号ivcs’将第一源电压的电压电平转换成对应于目标电压的电压电平。

80.当第二源电压等于或低于目标电压并且作为源电压vcc被提供给内部电压电路420和控制信号生成器410时,内部电压电路420可以基于第一内部电压控制信号ivcs1停止其操作,并且可以不输出存储器电压v’。

81.当第二源电压超过目标电压并且作为源电压vcc被提供给内部电压电路420和控制信号生成器410时,内部电压电路420可以基于第二内部电压控制信号ivcs2将第二源电压的电压电平转换成与目标电压相对应的电压电平。

82.开关元件t可以根据内部电压控制信号ivcs’、ivcs1和ivcs2来切换源电压vcc。当内部电压电路420接收到对应于初始内部电压控制信号ivcs’的开关控制信号ts时,开关元件t可以被关断。当内部电压电路420接收到对应于第一内部电压控制信号ivcs1的开关控制信号ts时,开关元件t可以被接通。当内部电压电路420接收到对应于第二内部电压控制信号ivcs2的开关控制信号ts时,开关元件t可以被关断。对应于内部电压控制信号ivcs’、ivcs1和ivcs2的开关控制信号ts可以表示通过使用反相器ib转换内部电压控制信号ivcs’、ivcs1和ivcs2中的每个内部电压控制信号而获得的信号。

83.当开关元件t被接通时,源电压vcc可以通过开关元件t输出到电压控制器400的外部。源电压vcc可以作为存储器电压v’被传送到非易失性存储器。基于内部电压控制信号ivcs’、ivcs1和ivcs2从开关元件t和内部电压电路420之一输出的源电压可以作为存储器

电压v’传送到非易失性存储器。

84.图5是用于描述根据示例实施例的电压控制器的内部信号的图。在下文中,将一起参考图5和图4。

85.可以假设这样的情况,其中第一源电压vcc1具有高于存储设备的目标电压的电压电平,第二源电压vcc2具有与存储设备的操作电压相同的电压电平,并且目标电压高于操作电压。在第一时间t1处,第三源电压vccq1和第一源电压vcc1可以被提供给控制信号生成器410。第一源电压vcc1可以被提供给内部电压电路420和第二开关元件t2。因为第一源电压vcc1高于目标电压ev,所以控制信号生成器410可以生成初始内部电压控制信号ivcs’。初始内部电压控制信号ivcs’可以具有逻辑低电平。初始内部电压控制信号ivcs’可以被传送到内部电压电路420,并且内部电压电路420可以将第一源电压vcc1的逻辑电平转换成与目标电压ev相对应的电压电平。内部电压电路420可以输出具有对应于目标电压ev的电压电平的存储器电压v’。对应于初始内部电压控制信号ivcs’的开关控制信号ts可以具有逻辑高电平,并且开关元件t可以被关断。

86.在第二时间t2处,第二源电压vcc2可以作为源电压vcc被提供给控制信号生成器410。第二时间t2可以表示主机(例如,图2的主机310)基于存储设备(例如,图2的存储设备320)的响应生成用于生成第二源电压vcc2的pmic命令并且pmic(例如,图2的pmic 330)基于pmic命令将第二源电压vcc2作为源电压vcc提供给存储设备的时间。第二源电压vcc2可以被提供给内部电压电路420和第二开关元件t2。第二源电压vcc2可以低于目标电压ev,因此,控制信号生成器410可以生成第一内部电压控制信号ivcs1。第一内部电压控制信号ivcs1可以具有逻辑高电平。第一内部电压控制信号ivcs1可以被传送到内部电压电路420,并且内部电压电路420可以停止操作。内部电压电路420可以不输出存储器电压v’。对应于第一内部电压控制信号ivcs1的开关控制信号ts可以具有逻辑低电平,并且开关元件t可以被接通。第二源电压vcc2可以通过开关元件t输出,并且开关元件t可以输出第二源电压vcc2作为存储器电压v’。可以选择性地从开关元件t和内部电压电路ivc之一提供存储器电压v’。

87.图6是示出根据示例实施例的存储设备的操作方法的流程图。详细地,图6是示出图2的存储设备320的操作方法的流程图。

88.在操作s610中,存储设备可以接收第一源电压。当存储系统被初始引导时,存储设备可以接收第一源电压。存储设备可以从pmic接收第一源电压。根据示例实施例,第一源电压可以具有高于存储设备的操作电压的电压电平。

89.在操作s620中,存储设备可以确定第一源电压是否不同于目标电压的电压电平。当在操作s620中第一源电压不同于目标电压时(是),存储设备可以在操作s621中将第一源电压转换成与目标电压相对应的电压电平。当第一源电压高于目标电压时,存储设备可以生成用于转换第一源电压的初始内部电压控制信号。存储设备可以基于初始内部电压控制信号将第一源电压的电压电平转换成与目标电压相对应的电压电平。当在操作s620中第一源电压不是不同于目标电压时(否),存储设备可以执行操作s622。

90.在操作s622中,存储设备可以从主机接收包括与操作电压相关联的信息请求的命令。在操作s623中,存储设备可向主机发送响应,该响应对应于与操作电压相关联的信息请求。主机可以基于该响应执行控制,使得pmic向存储设备提供第二源电压。

91.在操作s624中,存储设备可以接收第二源电压。存储设备可以从pmic接收第二源电压而不是第一源电压。

92.在操作s630中,存储设备可以确定第二源电压是否低于或等于目标电压。存储设备可以基于第二源电压生成指示是否转换第二源电压的内部电压控制信号。存储设备可以基于第二源电压与目标电压的比较来生成内部电压控制信号。

93.当在操作s630中第二源电压低于或等于目标电压时(是),存储设备可以在操作s631生成第一内部电压控制信号。当第二源电压是存储设备的操作电压时,存储设备可以生成第一内部电压控制信号。例如,假设第二源电压的电压电平为大约2.5v并且目标电压的电压电平为大约2.6v,则存储设备可以生成第一内部电压控制信号ivcs1。

94.在操作s632中,存储设备可以基于第一内部电压控制信号维持第二源电压。存储设备可以基于第一内部电压控制信号不转换第二源电压的电压电平,并且可以将第二源电压提供给存储设备的非易失性存储器。

95.当在操作s630中第二源电压高于目标电压时(否),存储设备可以在操作s633中生成第二内部电压控制信号。例如,假设第二源电压的电压电平为大约2.7v并且目标电压的电压电平为大约2.6v,则存储设备可以生成第二内部电压控制信号。

96.在操作s634中,存储设备可以基于第二内部电压控制信号转换第二源电压。存储设备可以基于第二内部电压控制信号ivcs2将第二源电压的电压电平转换成与目标电压相对应的电压电平。存储设备可以基于第二内部电压控制信号转换第二源电压的电压电平,并且可以将第二源电压提供给存储设备的非易失性存储器。

97.图7是示出根据示例实施例的包括otp存储器设备的存储系统700的框图。

98.参考图7,存储系统700可以包括主机710、存储设备720和pmic 730。图7的存储系统700、主机710、存储设备720和pmic 730可以分别对应于图2的存储系统300、主机310、存储设备320和pmic 330,因此省略对它们的重复描述。

99.主机710可以包括主机控制器711和otp存储器设备713。主机控制器711可以包括主机寄存器712。主机寄存器712可以用作主机控制器711的命令队列cq。

100.主机控制器711可以生成用于控制pmic 730的电压控制信号(例如,第一电压控制信号和第二电压控制信号)pcmd1和pcmd2,使得pmic 730向存储设备720提供源电压。电压控制信号pcmd1和pcmd2可以表示用于控制由pmic 730提供给存储设备720的源电压(例如,第一源电压和第二源电压)vcc1和vcc2的电压电平的pmic命令。第一电压控制信号pcmd1可以表示用于控制pmic 730使得pmic 730向存储设备720提供第一源电压vcc1的命令。第二电压控制信号pcmd2可以表示用于控制pmic 730使得pmic 730向存储设备720提供第二源电压vcc2的命令。

101.第二源电压vcc2可以具有不同于第一源电压vcc1的电压电平。在示例实施例中,第二源电压vcc2的电压电平可以低于第一源电压vcc1。例如,第一源电压vcc1可以是大约2.7v,并且第二源电压vcc2可以是大约2.5v。

102.主机710可以在主机寄存器712中顺序存储要被发送到pmic 730的电压控制信号pcmd1和pcmd2,并且可以将电压控制信号pcmd1和pcmd2发送到pmic 730。当存储系统700被初始引导时,主机710可以生成第一电压控制信号pcmd1。

103.主机710可以向存储设备720发送包括存储设备720的特性信息请求的命令cmd。主

730可以基于第二电压控制信号pcmd2向存储设备720提供第二源电压vcc2。存储设备720可以通过第一电压信号引脚(例如,图1的p4)接收第二源电压vcc2。

113.主机控制器711可以基于状态信号a输出电压控制信号pcmd1和pcmd2,状态信号a指示otp存储器设备713和主机寄存器712之间的连接状态。每当被引导时,状态信号a可以被提供给主机控制器711。例如,当状态信号a处于逻辑高电平时,主机控制器711可以输出第一电压控制信号pcmd1。当状态信号a处于逻辑低电平时,主机控制器711可以输出第二电压控制信号pcmd2。

114.图8和图9是用于描述根据示例实施例的otp存储器设备的源电压和连接信号的图。详细地,图8和图9是示出状态信号a和提供给存储设备的源电压的电压电平的图。在下文中,将一起参考图7、8和9。

115.在图8中,可以假设存储设备720的版本是第二版本的情况。当被初始引导时,otp存储器设备713可以连接到主机寄存器712。状态信号a可以处于逻辑高电平。在第一引导时段b1中,主机710可以生成第一电压控制信号pcmd1。基于第一电压控制信号pcmd1,第一源电压vcc1可以被提供给存储设备720。主机710可以从存储设备720接收响应res,该响应res对应于与操作电压相关联的信息请求。

116.因为存储设备720的版本是第二版本,所以主机控制器711可以生成第二连接控制信号sh2。otp存储器设备713和主机寄存器712之间的连接可以基于第二连接控制信号sh2被断开,并且状态信号a可以处于逻辑低电平。主机控制器711可以向pmic 730提供第二电压控制信号pcmd2。基于第二电压控制信号pcmd2,第二源电压vcc2可以被提供给存储设备720。

117.在第二引导时段b2中,主机控制器711可以输出第二电压控制信号pcmd2。因为otp存储器设备713和主机寄存器712之间的连接在第一引导时段b1中被断开,所以在第一引导时段b1之后的引导中可以维持第一引导时段b1的连接状态。当状态信号a处于逻辑低电平时,主机控制器711可以输出第二电压控制信号pcmd2。基于第二电压控制信号pcmd2,第二源电压vcc2可以被提供给存储设备720。

118.在图9中,可以假设存储设备720的版本是第一版本的情况。当被初始引导时,otp存储器设备713可以连接到主机寄存器712。状态信号a可以处于逻辑高电平。在第一引导时段b1中,主机710可以生成第一电压控制信号pcmd1。基于第一电压控制信号pcmd1,第一源电压vcc1可以被提供给存储设备720。主机710可以从存储设备720接收响应res,该响应res对应于与操作电压相关联的信息请求。

119.因为存储设备720的版本是第一版本,所以主机控制器711可以生成第一连接控制信号sh1。otp存储器设备713和主机寄存器712之间的连接可以基于第一连接控制信号sh1来维持,并且状态信号a可以处于逻辑高电平。主机控制器711可以向pmic 730提供第一电压控制信号pcmd1。基于第一电压控制信号pcmd1,第一源电压vcc1可以被提供给存储设备720。

120.在第二引导时段b2中,主机控制器711可以输出第一电压控制信号pcmd1。otp存储器设备713和主机寄存器712之间的连接可以在第一引导时段b1之后的引导中维持。当状态信号a处于逻辑高电平时,主机控制器711可以输出第一电压控制信号pcmd1。基于第一电压控制信号pcmd1,第一源电压vcc1可以被提供给存储设备720。

121.图10是示出根据示例实施例的主机的操作方法的流程图。详细地,图10是示出图7的主机710的操作方法的流程图。

122.在操作s1010中,主机可以向pmic提供第一电压控制信号。当存储系统被初始引导时,主机可以生成第一电压控制信号。第一电压控制信号可以执行控制,使得pmic向存储设备提供第一源电压。

123.在操作s1020中,主机可以发送包括存储设备的特性信息请求的命令。在操作s1030中,主机可以从存储设备接收对应于特性信息请求的响应。

124.在操作s1040中,主机可以确定存储设备的版本是否是第二版本。主机可以基于存储设备的版本生成连接控制信号。主机可以从存储设备的响应中获得关于存储设备的版本的信息,并且可以基于关于存储设备的版本的信息来检查已经向主机发送响应的存储设备的版本。

125.当在操作s1040中存储设备的版本是第二版本时(是),主机可以在操作s1041生成第二连接控制信号。第二连接控制信号可以执行控制以断开otp存储器设备和主机寄存器之间的连接。基于第二连接控制信号,可以断开otp存储器设备和主机寄存器之间的连接。

126.在操作s1042中,主机可以基于第二连接控制信号向pmic提供第二电压控制信号。第二电压控制信号可以执行控制,使得pmic向存储设备提供第二源电压。第二源电压可以具有不同于第一源电压的电压电平。第二源电压的电压电平可以低于第一源电压。第二源电压可以被提供给存储设备。

127.当在操作s1040中存储设备的版本是第一版本时(否),主机可以在操作s1043中生成第一连接控制信号。第一连接控制信号可以执行控制以维持otp存储器设备和主机寄存器之间的连接。基于第一连接控制信号,可以维持otp存储器设备和主机寄存器之间的连接。

128.在操作s1044中,主机可以基于第一连接控制信号向pmic提供第一电压控制信号。第一电压控制信号可以执行控制,使得pmic向存储设备提供第一源电压。第一源电压可以被提供给存储设备。

129.操作s1010至s1040和操作s1041至s1043可以在存储系统被初始引导时执行,并且可以在初始引导之后的引导中省略。因为在初始引导之后的引导中省略了操作s1010至s1040和操作s1041至s1043,所以可以防止存储设备无论何时在引导时暴露于高源电压。在初始引导之后的引导中,可以基于连接状态输出电压控制信号。

130.图11是用于描述根据示例实施例的ufs系统1000的图。ufs系统1000可以是基于联合电子设备工程委员会(joint electron device engineering council,jedec)定义的ufs标准的系统,并且可以包括ufs主机1100、ufs设备1200和ufs接口1300。图1、2和7的存储系统的描述可以在不与图11的以下描述相冲突的范围内应用于图11的ufs系统1000。

131.参考图11,ufs主机1100可以通过ufs接口1300连接到ufs设备1200。当图1的主机200是ap时,ufs主机1100可以被实现为对应ap的一部分。ufs主机控制器1110可以对应于图1的主机控制器220。ufs设备1200可以对应于图1的存储设备100,并且ufs设备控制器1210和非易失性存储器1220可以分别对应于图1的存储器控制器120和非易失性存储器130。

132.ufs主机1100可以包括ufs主机控制器1110、应用1120、ufs驱动器1130、主机存储器1140和ufs互连uic层1150。ufs设备1200可以包括ufs设备控制器1210、非易失性存储器

1220、存储接口1230、设备存储器1240、uic层1250和调节器1260。非易失性存储器1220可以配置有多个存储器单元1221,并且存储器单元1221中的每个存储器单元可以包括具有2d或3d结构的vnand闪存,但是可以包括不同种类的非易失性存储器,诸如pram和/或rram。ufs设备控制器1210可以通过存储接口1230连接到非易失性存储器1220。存储接口1230可以被实现为遵循诸如toggle或onfi的标准协议。

133.应用1120可以表示期望与ufs设备1200通信以便使用ufs设备1200的功能的程序。应用1120可以向ufs驱动器1130发送输入输出请求ior,用于ufs设备1200上的输入/输出。输入-输出请求ior可以表示数据读取请求、数据写入请求和/或数据丢弃请求,但是示例实施例不限于此。

134.ufs驱动器1130可以通过ufs主机控制器接口(hci)(ufs-hci)管理ufs主机控制器1110。ufs驱动器1130可以将应用1120生成的输入输出请求转换成由ufs标准定义的ufs命令,并且可以将转换后的ufs命令传送到ufs主机控制器1110。一个输入输出请求可以被转换成多个ufs命令。ufs命令可以是基本上由小型计算机系统接口(scsi)标准定义的命令,但也可以是ufs标准专用命令。

135.ufs主机控制器1110可以通过uic层1150和ufs接口1300将通过ufs驱动器1130的转换获得的ufs命令发送到ufs设备1200的uic层1250。在这样的过程中,ufs主机控制器1110的ufs主机寄存器1111可以用作命令队列cq。

136.ufs主机1100的uic层1150可以包括mipi m-phy 1151和mipi unipro1152,并且ufs设备1200的uic层1250可以包括mipi m-phy 1251和mipi unipro 1252。

137.ufs接口1300可以包括传输参考时钟信号ref_clk的线、传输对应于ufs设备1200的硬件复位信号reset_n的线、传输差分输入信号对din_t和din_c的一对线、以及传输差分输出信号对dout_t和dout_c的一对线。

138.ufs接口101可以支持多个通道,并且多个通道中的每个通道可以被实现为差分对。例如,ufs接口101可以包括一个或多个接收通道和一个或多个发送通道。在图11中,传输差分输入信号对din_t和din_c的一对线可以配置接收通道,并且传输差分输出信号对dout_t和dout_c的一对线可以配置发送通道。在图11中,示出了一个发送通道和一个接收通道,但是发送通道和接收通道的数量可以改变。

139.接收通道和发送通道可以基于串行通信方案传输数据,并且ufs主机1100和ufs设备1200之间的全双工通信可以基于接收通道与发送通道分离的结构来实现。也就是说,ufs设备1200可以通过发送通道向ufs主机1100发送数据,同时通过接收通道从ufs主机1100接收数据。此外,诸如从ufs主机1100到ufs设备1200的命令的控制数据以及要由ufs主机1100存储在ufs设备1200的非易失性存储器1220中或者要从非易失性存储器1220中读取的用户数据可以通过相同的通道传输。因此,除了一对接收通道和一对发送通道之外,在ufs主机1100和ufs设备1200之间可以不进一步包括用于传输数据的单独通道。

140.ufs设备1200的ufs设备控制器1210可以总体控制ufs设备1200的操作。ufs设备控制器1210可以通过作为逻辑数据存储单元的逻辑单元(lu)1211来管理非易失性存储器1220。lu 1211的数量可以是八个,但不限于此。ufs设备控制器1210可以包括闪存转换层(flash translation layer,ftl),并且可以通过使用关于ftl的地址映射信息将从ufs主机1100传送的逻辑数据地址(例如,逻辑块地址(logical block address,lba))转换成物

理数据地址(例如,物理块地址(physical block address,pba))。ufs系统1000中用于存储用户数据的逻辑块可以具有在特定范围内的大小。例如,逻辑块的最小大小可以被设置为大约4千字节。

141.当来自ufs主机1100的命令通过uic层1250输入到ufs设备1200时,ufs设备控制器1210可以基于输入到其的命令执行操作,并且当操作完成时,ufs设备控制器1210可以向ufs主机1100发送完成响应。

142.例如,当ufs主机1100期望将用户数据存储在ufs设备1200中时,ufs主机1100可以向ufs设备1200发送数据存储命令。当从ufs设备1200接收到准备好传输用户数据的准备好传送响应时,ufs主机1100可以将用户数据发送到ufs设备1200。ufs设备控制器1210可以将发送的用户数据临时存储在设备存储器1240中,并可以基于关于ftl的地址映射信息将临时存储在设备存储器1240中的用户数据存储在非易失性存储器1220的选定位置。

143.作为另一个示例,当ufs主机1100期望读取存储在ufs设备1200中的用户数据时,ufs主机1100可以向ufs设备1200发送数据读取命令。已经接收到对应命令的ufs设备控制器1210可以基于数据读取命令从非易失性存储器1220读取用户数据,并且可以将读取的用户数据临时存储在设备存储器1240中。在这样的读取过程中,ufs设备控制器1210可以通过使用嵌入式纠错码(error correction code,ecc)引擎来检测和纠正读取的用户数据的错误。更详细地,ecc引擎可以生成与要写入非易失性存储器1220中的写入数据相对应的奇偶校验位,并且以这种方式生成的奇偶校验位可以与写入数据一起存储在非易失性存储器1220中。在从非易失性存储器1220读取数据时,ecc引擎可以通过使用从非易失性存储器1220读取的奇偶校验位以及读取数据来纠正读取数据的错误,并且可以输出纠错后的读取数据。

144.此外,ufs设备控制器1210可以将临时存储在设备存储器1240中的用户数据发送到ufs主机1100。此外,ufs设备控制器1210还可以包括高级加密标准(advanced encryption standard,aes)引擎。aes引擎可通过使用对称密钥算法对输入到ufs设备控制器1210的数据执行加密操作和解密操作中的至少一个。

145.ufs主机1100可以在能够用作命令队列的ufs主机寄存器1111中按顺序存储要发送到ufs设备1200的命令,并且可以按顺序将命令发送到ufs设备1200。在这种情况下,即使当ufs设备1200仍在处理先前发送的命令时(即,在接收到指示ufs设备1200对先前发送的命令的处理完成的通知之前),ufs主机1100也可以向ufs设备1200发送在命令队列中等待的下一个命令,因此,ufs设备1200可以在处理先前发送的命令的同时从ufs主机1100接收下一个命令。能够存储在命令队列中的命令的最大数量(队列深度)可以是例如32。此外,命令队列可以实现为循环队列类型,其中命令列的开始和结束中的每一个通过头指针和尾指针存储在队列中。

146.多个存储器单元1221中的每个存储器单元可以包括存储器单元阵列和控制存储器单元阵列的操作的控制电路。存储器单元阵列可以包括2d存储器单元阵列或3d存储器单元阵列。存储器单元阵列可以包括多个存储器单元,并且存储器单元中的每个存储器单元可以包括存储1位信息的单元(单级单元(slc))或者可以包括存储2位或更多位信息的单元,诸如多级单元(mlc)、三级单元(tlc)和四级单元(qlc)。3d存储器单元阵列可以包括垂直取向使得至少一个存储器单元布置在另一个存储器单元上的垂直nand串。

147.vcc、vccq1和vccq2可以各自作为源电压输入到ufs设备1200。vcc可以是ufs设备1200的主电源电压,并且可以具有例如2.4v至3.6v的值。vccq1可以是用于供应具有低范围的电压的源电压,并且可以具有例如1.14v至1.26v的值。vccq2可以是用于供应具有低于vcc并高于vccq1的范围的电压的源电压,并且可以具有例如1.7v至1.95v的值。源电压可以经由调节器1260供应给ufs设备1200的元件中的每个元件。调节器1260可以被实现为分别连接到上述源电压当中的不同源电压的单位调节器的集合。根据示例实施例,调节器1260可以包括电压控制器(例如,图2的电压控制器321)。

148.图12a至图12c是用于描述ufs卡的形状因子的图。当上面参考图11描述的ufs设备1200被实现为ufs卡2000类型时,ufs卡2000的外部形状可以如图12a至图12c所示。

149.图12a示出了例如ufs卡2000的俯视图。参考图12a,可以检查出ufs卡2000是基于整体具有鲨鱼形状的设计。在图12a中,ufs卡2000可以具有如下表1所示的尺寸。

150.[表1]

[0151]

项目尺寸(毫米)t19.70t215.00t311.00t49.70t55.15t60.25t70.60t80.75t90.80

[0152]

图12b示出了例如ufs卡2000的侧视图。在图12b中,ufs卡2000可以具有如下表2所示的尺寸值。

[0153]

[表2]

[0154][0155][0156]

图12c示出了例如ufs卡2000的仰视图。参考图12c,用于与ufs插槽电接触的多个引脚可以设置在ufs卡2000的底面中,并且将描述多个引脚中的每个引脚的功能。基于ufs卡2000的顶面和底面之间的对称性,以上参考图12a和表1描述的关于尺寸的信息中的一些(例如,t1至t5和t9)可应用于如图12c所示的ufs卡2000的仰视图。

[0157]

用于与ufs主机电连接的多个引脚可以被提供在ufs卡2000的底面中,并且引脚的

数量可以是总共12个,如图12c所示。每个引脚可以具有矩形形状,并且对应于引脚的信号名称如图12c所示。关于每个引脚的信息可以参考下表3。

[0158]

[表3]

[0159][0160][0161]

图13是示出根据示例实施例的存储器系统3000的框图。

[0162]

参考图13,存储器系统3000可以包括存储器设备3200和存储器控制器3100。存储器设备3200可以对应于基于多个通道之一与存储器控制器3100通信的非易失性存储器设备之一。例如,存储器设备3200可以对应于图1的非易失性存储器130,并且存储器控制器3100可以对应于图1的存储器控制器120。

[0163]

存储器设备3200可以包括第一引脚p11至第八引脚p18、存储器接口电路3210、控制逻辑电路3220和存储器单元阵列3230。存储器接口电路3210可以通过第一引脚p11从存储器控制器3100接收芯片使能信号nce。存储器接口电路3210可以基于芯片使能信号nce通过第二引脚p12至第八引脚p18向存储器控制器3100发送信号和从存储器控制器3100接收信号。例如,当芯片使能信号nce处于使能状态(例如,低电平)时,存储器接口电路3210可以通过第二引脚p12至第八引脚p18向存储器控制器3100发送信号和从存储器控制器3100接收信号。

[0164]

存储器接口电路3210可以通过第二引脚p12至第四引脚p14从存储器控制器3100接收命令锁存使能信号cle、地址锁存使能信号ale和写入使能信号nwe。存储器接口电路

3210可以通过第七引脚p17从存储器控制器3100接收数据信号dq,或者可以将数据信号dq发送到存储器控制器3100。可以通过使用数据信号dq来传送命令cmd、地址addr和数据data。例如,数据信号dq可以通过多条数据信号线传输。在这种情况下,第七引脚p17可以包括对应于多个数据信号的多个引脚。

[0165]

存储器接口电路3210可以基于写入使能信号nwe的切换(toggle)定时,从在命令锁存使能信号cle的使能时段(例如,高电平状态)中接收的数据信号dq获得命令cmd。存储器接口电路3210可以基于写入使能信号nwe的切换定时,从在地址锁存使能信号ale的使能时段(例如,高电平状态)中接收的数据信号dq获得地址addr。

[0166]

在示例实施例中,写入使能信号nwe可以保持静态(例如,高电平或低电平),然后可以在高电平和低电平之间切换。例如,写入使能信号nwe可以在发送命令cmd或地址addr的时段中切换。因此,存储器接口电路3210可以基于写入使能信号nwe的切换定时获得命令cmd或地址addr。

[0167]

存储器接口电路3210可以通过第五引脚p15从存储器控制器3100接收读取使能信号nre。存储器接口电路3210可以通过第六引脚p16从存储器控制器3100接收数据选通信号dqs,或者可以将数据选通信号dqs发送到存储器控制器3100。

[0168]

在存储器设备3200的数据data输出操作中,存储器接口电路3210可以在输出数据data之前通过第五引脚p15接收读取使能信号nre切换。存储器接口电路3210可以基于读取使能信号nre的切换生成进行切换的数据选通信号dqs。例如,存储器接口电路3210可以生成数据选通信号dqs,该数据选通信号在相对于读取使能信号nre的切换开始时间的预定延迟(例如,tdqsre)之后开始切换。存储器接口电路3210可以基于数据选通信号dqs的切换定时来发送包括数据data的数据信号dq。因此,数据data可以与数据选通信号dqs的切换定时对准,并且可以被发送到存储器控制器3100。

[0169]

在存储器设备3200的数据data输入操作中,当从存储器控制器3100接收到包括数据data的数据信号dq时,存储器接口电路3210可以从存储器控制器3100接收数据选通信号dqs,其与数据data一起切换。存储器接口电路3210可以基于数据选通信号dqs的切换定时从数据信号dq获得数据data。例如,存储器接口电路3210可以在数据选通信号dqs的上升沿和下降沿对数据信号dq进行采样,以获得数据data。

[0170]

存储器接口电路3210可以通过第八引脚p18向存储器控制器3100发送就绪/忙碌输出信号nr/b。存储器接口电路3210可以通过使用就绪/忙碌输出信号nr/b将关于存储器设备3200的状态信息发送到存储器控制器3100。当存储器设备3200处于忙碌状态时(即,当正在执行存储器设备3200的内部操作时),存储器接口电路3210可以将指示忙碌状态的就绪/忙碌输出信号nr/b发送到存储器控制器3100。当存储器设备3200处于就绪状态时(即,当存储器设备3200的内部操作没有被执行或完成时),存储器接口电路3210可以向存储器控制器3100发送指示就绪状态的就绪/忙碌输出信号nr/b。例如,在存储器设备3200响应于页面读取命令从存储器单元阵列3230读取数据data时,存储器接口电路3210可以向存储器控制器3100发送指示忙碌状态(例如,低电平)的就绪/忙碌输出信号nr/b。例如,当存储器设备3200响应于编程命令正在对存储器单元阵列3230中的数据data进行编程时,存储器接口电路3210可以向存储器控制器3100发送指示忙碌状态的就绪/忙碌输出信号nr/b。

[0171]

控制逻辑电路3220可以总体控制存储器设备3200的各种操作。控制逻辑电路3220

可以接收从存储器接口电路3210获得的命令/地址cmd/addr。控制逻辑电路3220可以根据接收到的命令/地址cmd/addr生成用于控制存储器设备3200的其他元件的控制信号。例如,控制逻辑电路3220可以生成用于将数据data编程到存储器单元阵列3230中或者从存储器单元阵列3230读取数据data的各种控制信号。

[0172]

基于控制逻辑电路3220的控制,存储器单元阵列3230可以存储从存储器接口电路3210获得的数据data。存储器单元阵列3230可以基于控制逻辑电路3220的控制将存储的数据data输出到存储器接口电路3210。

[0173]

存储器单元阵列3230可以包括多个存储器单元。例如,多个存储器单元可以包括闪存单元。然而,示例实施例不限于此,并且存储器单元可以包括电阻ram(reram)单元、铁电ram(fram)单元、相变ram(pram)单元、晶闸管ram(tram)单元和磁性ram(mram)单元。在下文中,将主要描述存储器单元是nand闪存单元的示例实施例。

[0174]

存储器控制器3100可以包括第一引脚p21至第八引脚p28以及控制器接口电路3110。第一引脚p21至第八引脚p28可以对应于存储器设备3200的第一引脚p11至第八引脚p18。控制器接口电路3110可以通过第一引脚p21将芯片使能信号nce发送到存储器设备3200。控制器接口电路3110可以通过第二引脚p22至第八引脚p28向通过芯片使能信号nce选择的存储器设备3200发送信号,以及通过第二引脚p22至第八引脚p28从通过芯片使能信号nce选择的存储器设备3200接收信号。

[0175]

控制器接口电路3110可以通过第二引脚p22至第四引脚p24将命令锁存使能信号cle、地址锁存使能信号ale和写入使能信号nwe发送到存储器设备3200。控制器接口电路3110可以通过第七引脚p27将数据信号dq发送到存储器设备3200,或者可以从存储器设备3200接收数据信号dq。

[0176]

控制器接口电路3110可以将包括命令cmd或地址addr的数据信号dq与写入使能信号nwe切换一起发送到存储器设备3200。控制器接口电路3110可以通过发送具有使能状态的命令锁存使能信号cle来将包括命令cmd的数据信号dq发送到存储器设备3200,并且可以通过发送具有使能状态的地址锁存使能信号ale来将包括地址addr的数据信号dq发送到存储器设备3200。

[0177]

控制器接口电路3110可以通过第五引脚p25将读取使能信号nre发送到存储器设备3200。控制器接口电路3110可以通过第六引脚p26从存储器设备3200接收数据选通信号dqs,或者可以将数据选通信号dqs发送到存储器设备3200。

[0178]

在存储器设备3200的数据data输出操作中,控制器接口电路3110可以生成进行切换的读取使能信号nre,并且可以将读取使能信号nre发送到存储器设备3200。例如,在数据data被输出之前,控制器接口电路3110可以生成从静态(例如,高电平或低电平)变为切换状态的读取使能信号nre。因此,存储器设备3200可以基于读取使能信号nre生成数据选通信号dqs切换。控制器接口电路3110可以从存储器设备3200接收包括数据data的数据信号dq以及进行切换的数据选通信号dqs。控制器接口电路3110可以基于数据选通信号dqs的切换定时从数据信号dq获得数据data。

[0179]

在存储器设备3200的数据data输入操作中,控制器接口电路3110可以生成进行切换的数据选通信号dqs。例如,在发送数据data之前,控制器接口电路3110可以生成从静态(例如,高电平或低电平)变为切换状态的数据选通信号dqs。控制器接口电路3110可以基于

数据选通信号dqs的切换定时将包括数据data的数据信号dq发送到存储器设备3200。

[0180]

控制器接口电路3110可以通过第八引脚p28从存储器设备3200接收就绪/忙碌输出信号nr/b。控制器接口电路3110可以基于就绪/忙碌输出信号nr/b来确定关于存储器设备3200的状态信息。

[0181]

图14是用于描述根据示例实施例的适用于ufs设备的3d vnand结构的图。当ufs设备的存储模块被实现为3d vnand类型的闪存时,配置存储模块的多个存储器块中的每个存储器块可以被表示为图14所示的等效电路。图14中示出的存储器块blki可以表示在衬底上以3d结构形成的3d存储器块。例如,包括在存储器块blki中的多个存储器nand串可以在垂直于衬底的方向上形成。

[0182]

参考图14,存储器块blki可以包括连接在位线bl1至bl3和公共源极线csl之间的多个存储器nand串ns11至ns33。多个存储器nand串ns11至ns33中的每个存储器nand串可以包括串选择晶体管sst、多个存储器单元mc1至mc8和接地选择晶体管gst。在图14中,多个存储器nand串ns11至ns33中的每个存储器nand串被示为包括八个存储器单元mc1至mc8,但是不限于此。

[0183]

串选择晶体管sst可以连接到对应的串选择线ssl1至ssl3。多个存储器单元mc1至mc8中的每个存储器单元可以连接到对应的栅极线gtl1至gtl8。栅极线gtl1至gtl8可以对应于字线,并且栅极线gtl1至gtl8中的一些栅极线可以对应于伪字线。接地选择晶体管gst可以连接到对应的接地选择线gsl1至gsl3。串选择晶体管sst可以连接到对应的位线bl1至bl3,并且接地选择晶体管gst可以连接到公共源极线csl。

[0184]

具有相同高度的字线(例如,wl1)可以公共地连接,并且接地选择线gsl1至gsl3和串选择线ssl1至ssl3可以彼此分离。在图14中,示出了存储器块blk连接到八条栅极线gtl1至gtl8和三条位线bl1至bl3,但是示例实施例不限于此。

[0185]

图15是用于描述根据示例实施例的适用于ufs设备的键合垂直nand(bonding vertical nand,bvnand)结构的图。参考图15,当包括在ufs设备中的非易失性存储器被实现为bvnand型闪存时,非易失性存储器可以具有图15所示的结构。

[0186]

参考图15,存储器设备4000可以具有芯片到芯片(c2c)结构。c2c结构可以表示在第一晶片上制造包括单元区域cell的上部芯片,在不同于第一晶片的第二晶片上制造包括外围电路区peri的下部芯片,并且上部芯片通过键合方式连接到下部芯片。例如,键合方式可以表示形成在上部芯片的最上层金属层中的键合金属电连接到形成在下部芯片的最上层金属层中的键合金属的方式。例如,当键合金属包括铜(cu)时,键合方式可以是cu-cu键合方式,并且键合金属可以包括铝或钨。

[0187]

存储器设备4000的外围电路区域peri和单元区域cell中的每一个可以包括外部焊盘键合区域pa、字线键合区域wlba和位线键合区域blba。

[0188]

外围电路区域peri可以包括第一衬底4110、层间绝缘层4115、形成在第一衬底4110中的多个电路器件4120a、4120b和4120c、分别连接到多个电路器件4120a、4120b和4120c的多个第一金属层4130a、4130b和4130c、以及分别形成在多个第一金属层4130a、4130b和4140c上的多个第二金属层4140a、4140b和4140c。在示例实施例中,第一金属层4130a、4130b和4130c可以包括电阻相对高的钨,并且第二金属层4140a、4140b和4140c可以包括电阻相对低的铜。

[0189]

在本文中,仅示出和描述了第一金属层4130a、4130b和4130c以及第二金属层4140a、4140b和4140c,但是示例实施例不限于此,并且一个或多个金属层可以进一步形成在第二金属层4140a、4140b和4140c上。形成在第二金属层4140a、4140b和4140c上的一个或多个金属层中的至少一些可以包括具有低于包括在第二金属层4140a、4140b和4140c中的铜的电阻的铝。

[0190]

层间绝缘层4115可以布置在第一衬底4110上以覆盖多个电路器件4120a、4120b和4120c、多个第一金属层4130a、4130b和4130c以及多个第二金属层4140a、4140b和4140c,并且可以包括诸如氧化硅或氮化硅的绝缘材料。

[0191]

下键合金属4171b和4172b可以形成在字线键合区域wlba的第二金属层4140b上。在字线键合区域wlba中,外围电路区域peri的下键合金属4171b和4172b可以通过键合方式电连接到单元区域cell的上键合金属4271b和4272b,并且下键合金属4171b和4172b以及上键合金属4271b和4272b可以包括铝、铜或钨。

[0192]

单元区域cell可以提供至少一个存储器块。单元区域cell可以包括第二衬底4210和公共源极线4220。多条字线4231至4238(4230)可以沿垂直于第二衬底4210的顶表面的方向(z轴方向)堆叠在第二衬底4210上。串选择线和接地选择线可以分别布置在字线4230之上和之下,并且多条字线4230可以布置在串选择线和接地选择线之间。

[0193]

在位线键合区域blba中,沟道结构chs可以在垂直于第二衬底4210的顶表面的方向上延伸,并且可以穿过字线4230、串选择线和接地选择线。沟道结构chs可以包括数据存储层、沟道层和掩埋绝缘层,并且沟道层可以电连接到第一金属层4250c和第二金属层4260c。例如,第一金属层4250c可以是位线接触点,并且第二金属层4260c可以是位线。在示例实施例中,位线4260c可以在平行于第二衬底4210的顶表面的第一方向(y轴方向)上延伸。

[0194]

在图15所示的示例实施例中,布置沟道结构chs和位线4260c的区域可以被定义为位线键合区域blba。在位线键合区域blba中,位线4260c可以电连接到在外围电路区域peri中提供页面缓冲器4293的电路器件4120c。例如,位线4260c可以连接到外围电路区域peri中的上键合金属4271c和4272c,并且上键合金属4271c和4272c可以连接到下键合金属4171c和4172c,下键合金属4171c和4172c连接到页面缓冲器4293的电路器件4120c。

[0195]

在字线键合区域wlba中,字线4230可以在平行于第二衬底4210的顶表面的第二方向(x轴方向)上延伸,并且可以连接到多个单元接触插塞4241至4247(4240)。字线4230和单元接触插塞4240可以在焊盘处彼此连接,其中通过在第二方向上将字线4230中的至少一些延伸不同的长度来提供该焊盘。第一金属层4250b和第二金属层4260b可以顺序连接到单元接触插塞4240的上部,其中单元接触插塞4240连接到字线4230。在字线键合区域wlba中,单元接触插塞4240可以通过单元区域cell的上键合金属4271b和4272b以及外围电路区域peri的下键合金属4171b和4172b连接到外围电路区域peri。

[0196]

单元接触插塞4240可以电连接到在外围电路区域peri中提供行解码器4294的电路器件4120b。在示例实施例中,提供行解码器4294的电路器件4120b的操作电压可以不同于提供页面缓冲器4293的电路器件4120c的操作电压。例如,提供页面缓冲器4293的电路器件4120c的操作电压可以高于提供行解码器4294的电路器件4120b的操作电压。

[0197]

公共源极线接触插塞4280可以布置在外部焊盘键合区域pa中。公共源极线接触插

塞4280可以包括诸如金属、金属化合物或多晶硅的导电材料,并且可以电连接到公共源极线4220。第一金属层4250a和第二金属层4260a可以顺序堆叠在公共源极线接触插塞4280上。例如,布置公共源极线接触插塞4280、第一金属层4250a和第二金属层4260a的区域可以被定义为外部焊盘键合区域pa。

[0198]

多个输入/输出(i/o)焊盘(例如,第一i/o焊盘和第二i/o焊盘)4105和4205可以布置在外部焊盘键合区域pa中。参考图15,覆盖第一衬底4110的底表面的下绝缘层4101可以形成在第一衬底4110下方,并且第一i/o焊盘4105可以形成在下绝缘层4101上。第一i/o焊盘4105可以通过第一i/o接触插塞4103连接到布置在外围电路区域peri中的多个电路器件4120a、4120b和4120c中的至少一个,并且可以通过下绝缘层4101与第一衬底4110分离。并且,侧绝缘层可以布置在第一i/o接触插塞4103和第一衬底4110之间,并且可以将第一i/o接触插塞4103与第一衬底4110电断开。

[0199]

参考图15,覆盖第二衬底4210的顶表面的上绝缘层4201可以形成在第二衬底4210上,并且第二i/o焊盘4205可以布置在上绝缘层4201上。第二i/o焊盘4205可以通过第二i/o接触插塞4203连接到布置在外围电路区域peri中的多个电路器件4120a、4120b和4120c中的至少一个。

[0200]

根据示例实施例,第二衬底4210和公共源极线4220可以不布置在第二i/o接触插塞4203所布置的区域中。并且,第二i/o焊盘4205可以不在第三方向上(z轴方向)与字线4230重叠。参考图15,第二i/o接触插塞4203可以在平行于第二衬底4210的顶表面的方向上与第二衬底4210分离,并且此外,可以穿过单元区域cell的层间绝缘层4215,并且可以连接到第二i/o焊盘4205。

[0201]

根据示例实施例,可以可选地形成第一i/o焊盘4105和第二i/o焊盘4205。例如,存储器设备4000可以仅包括布置在第一衬底4110上的第一i/o焊盘4105,或者可以仅包括布置在第二衬底4210上的第二i/o焊盘4205。可替换地,存储器设备4000可以包括所有的第一i/o焊盘4105和第二i/o焊盘4205。

[0202]

在单元区域cell和外围电路区域peri的每一个中包括的外部焊盘键合区域pa和位线键合区域blba的每一个中,最上层金属层的金属图案可以设置为伪图案,或者最上层金属层可以是空的。

[0203]

在存储器设备4000中,在外部焊盘键合区域pa中,基于形成在单元区域cell的最上层金属层中的上金属图案4272a,具有与单元区域cell的上金属图案4272a相同形状的下金属图案4176a可以形成在外围电路区域peri的最上层金属层中。形成在外围电路区域peri的最上层金属层中的下金属图案4176a可以不连接到外围电路区域peri中的单独接触点。类似地,在外部焊盘键合区域pa中,基于在外围电路区域peri的最上层金属层中形成的下金属图案,可以在单元区域cell的最上层金属层中形成与外围电路区域peri的下金属图案具有相同形状的上金属图案。

[0204]

下键合金属4171b和4172b可以形成在字线键合区域wlba的第二金属层4140b上。在字线键合区域wlba中,外围电路区域peri的下键合金属4171b和4172b可以通过键合方式电连接到单元区域cell的上键合金属4271b和4272b。

[0205]

此外,在位线键合区域blba中,基于形成在外围电路区域peri的最上层金属层中的下金属图案4152,具有与外围电路区域peri的下金属图案4152相同形状的上金属图案

4292可以形成在单元区域cell的最上层金属层中。在单元区域cell的最上层金属层中形成的上金属图案4292中可以不形成接触点。

[0206]

根据示例实施例,由如图1、2、4、7、11和13中所示的方框表示的组件、元件、模块或单元中的至少一个可以被实现为执行上述相应功能的各种数量的硬件、软件和/或固件结构。例如,这些组件、元件、模块或单元中的至少一个可以包括晶体管、电容器、逻辑门和其他电路元件以实现上述功能,或者可以使用可以通过一个或多个微处理器或其他控制设备的控制来执行相应的功能的直接电路结构,诸如存储器、处理器、逻辑电路、查找表等。此外,这些组件、元件、模块或单元中的至少一个可以由包含用于执行特定逻辑功能的一个或多个可执行指令并且由一个或多个微处理器或其他控制设备执行的模块、程序或代码的一部分具体体现。此外,这些组件、元件、模块或单元中的至少一个还可以包括处理器(诸如执行相应功能的中央处理单元(cpu)、微处理器等)或者可以由处理器实现。这些组件、元件、模块或单元中的两个或更多个可以组合成一个单个组件、元件、模块或单元,其执行组合的两个或更多个组件、元件、模块或单元的所有操作或功能。此外,这些组件、元件、模块或单元中的至少一个的至少部分功能可以由这些组件、元件、模块或单元中的另一个来执行。此外,尽管在以上框图中未示出总线,但是组件、元件、模块或单元之间的通信可以通过总线来执行。上述示例性实施例的功能方面可以在一个或多个处理器上执行的算法中实现。此外,由块或处理步骤表示的组件、元件、模块或单元可以采用任何数量的用于电子配置、信号处理和/或控制、数据处理等的相关技术。

[0207]

虽然已经具体示出和描述了示例实施例的各个方面,但是应当理解,在不脱离所附权利要求的精神和范围的情况下,可以在形式和细节上进行各种改变。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1