一种基于DFI的PHY低功耗控制模块的制作方法

一种基于dfi的phy低功耗控制模块

技术领域

1.本发明涉及一种基于dfi的phy低功耗控制模块,属于存储器技术领域。

背景技术:

2.当前许多的电路设计当中,减少不必要的能量损耗是一个重要的优化指标,如今伴随着用户要求的提高及计算机的不断发展,ddr的内存容量和频率也在不断提高,与之一起提高的还有ddr的功耗,为此ddr控制器为用户提供了一系列可配置接口来进入不同的低功耗状态。但是缺少一种节省功耗同时又能保证数据高效传输的模块。

技术实现要素:

3.本发明目的是提供了一种基于dfi的phy低功耗控制模块,能在功耗降低的前提下最大程度的满足数据读写的需求。

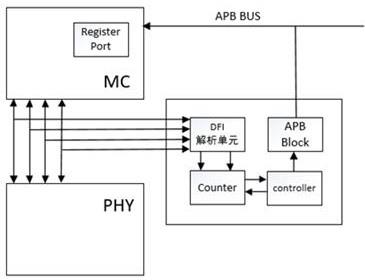

4.本发明为实现上述目的,通过以下技术方案实现:一种基于dfi的phy低功耗控制模块,其特征在于,在mc与phy之间并联一个电路,所述电路包括依次连接的dfi信号解析单元、计数器、可编程控制单元、apb接口控制单元;所述apb接口控制单元通过apb总线连接到mc寄存器;所述dfi信号解析单元用于监测mc和phy之间的读写数据dfi_rddata和dfi_wrdata的数量,并传递给计数器,读数据和写数据都传递给相同的计数器进行计数;所述计数器的计数周期通过可编程控制单元来进行控制,计数器将计数值传递给可编程控制单元;所述可编程控制单元根据传递进来的计数值对mc中相应的低功耗参数进行配置,配置参数通过apb总线传递到mc的寄存器,进而通过dfi接口传递给phy实现对phy的低功耗控制;具体控制方式如下:在mc进入低功耗状态时,若此时计数周期内数据量高于正常工作状态数据量的百分之五十,可编程控制单元通过apb接口为phy配置低于256个时钟周期的唤醒时间;当计数周期内数据量低于正常工作状态数据量的百分之五十时,可编程控制单元通过apb接口为phy配置高于256个时钟周期的唤醒时间;当多个周期内检测不到读写数据的操作时,可编程控制单元控制除dfi解析单元的模块进入低功耗状态,此时dfi模块充当触发器的作用,一旦再次检测到dfi接口上出现读写数据会将整个模块唤醒进入正常工作模式。

5.优选的,所述可编程控制单元中包含了一个时钟控制单元,一个mcu,一个用户接口,以及一个uart串口;所述计数器将信息传递给可编程控制单元内部的mcu,mcu根据计数器传递的数据量信息筛选出对应的低功耗参数:当计数器传递的数值高于正常工作状态数据量的百分之五十,mcu生成低于256个时钟周期的唤醒时间参数;当计数器传递的数值低于正常工作状态数据量的百分之五十,mcu生成高于256个时钟周期的唤醒时间参数,并完成mcu到apb接口控制单元的地址和数据的映射,将映射后的各项低功耗配置参数通过apb接口控制单元传递给apb总线,通过apb总线传递到mc的寄存器。

6.优选的,所述mcu和时钟控制单元之间存在着信号的交互,计数周期内counter的计数值通过信号线传递给时钟控制单元,时钟控制单元根据计数值的大小动态调整mcu的运行频率;当计数器传递的数值低于正常工作状态数据量的百分之五十,当计数值较小时,时钟控制单元会降低mcu运行频率;优选的,所述用户接口,用于修改mcu内部的相关参数;所述uart串口用于完成和上位机的通信。

7.本发明的优点在于:本技术根据某一固定周期内数据传输数量动态调整phy低功耗状态,配合控制器(mc)共同实现ddr的低功耗模式,在节能的同时保证数据的高效传输。

附图说明

8.附图用来提供对本发明的进一步理解,并且构成说明书的一部分,与本发明的实施例一起用于解释本发明,并不构成对本发明的限制。

9.图1为本发明结构示意图。

10.图2为本发明可编程控制单元结构示意图。

具体实施方式

11.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

12.一种基于dfi的phy低功耗控制模块,本模块由以下几个部分组成,dfi信号解析单元、计数器(counter)、可编程控制单元(controller)、apb接口控制单元(apb block)。

13.本文低功耗控制模块在mc和phy之间添加一个额外的电路,首先是一个dfi信号解析单元,dfi信号解析单元能够监测mc和phy之间的读写数据dfi_rddata和dfi_wrdata的数量,并传递给给后方的计数器,读数据和写数据都传递给相同的计数器进行计数,计数器的计数周期是通过可编程控制单元来进行控制的,计数器将计数值传递给可编程控制单元,可编程控制单元根据传递进来的计数值对mc中相应的低功耗参数进行配置,配置参数通过apb总线传递到mc的寄存器,进而通过dfi接口传递给phy实现对phy的低功耗控制:在mc进入低功耗状态时,若此时计数周期内数据量较大,可编程控制单元会通过apb接口为phy配置较短的唤醒时间;当计数周期内数据量较小时,可编程控制单元会通过apb接口为phy配置较长的唤醒时间;当多个周期内检测不到读写数据的操作时,整个低功耗模块除dfi解析单元外都会在可编程控制单元的操作下进入低功耗状态,此时dfi模块充当触发器的作用,一旦再次检测到dfi接口上出现读写数据会将整个模块唤醒进入正常工作模式。为低功耗控制模块本身设置低功耗模式能最大限度的减少整个系统的能量消耗,避免出现ddr已经进入低功耗模式而低功耗模块依然活跃造成不必要的能量消耗的情况。

14.下面对可编程控制单元进行详细的介绍:可编程控制单元中包含了一个时钟控制单元,一个mcu,一个用户接口,以及一个uart串口。计数值从计数器传递给可编程控制单元内部的mcu,mcu根据此值筛选出对应的低功耗参数,然后通过内部逻辑处理来完成mcu到

apb接口控制单元的地址和数据的映射,映射后的各项低功耗配置参数通过apb接口控制单元传递给apb总线,进而传递到mc的寄存器当中;另外mcu和时钟控制单元之间存在着信号的交互,计数周期内counter的计数值通过信号线传递给时钟控制单元,时钟控制单元根据计数值的大小动态调整mcu的运行频率:当计数值较小时,时钟控制单元会降低mcu运行频率以满足整个系统功耗的降低。另外mcu还存在着用户接口(user interface),用户可以通过此接口来对mcu内部的相关参数进行修改:修改低功耗配置具体参数,以及不同的计数值所对应的具体mcu时钟频率等。为了方便操作,在用户接口后额外添加了uart串口,通过此串口可以完成和上位机的通信,即可以直接通过此串口来完成mcu配置命令的输入和mcu内部运行状态的显示。

15.本发明根据dfi规范的框架进行拓展,具有适用性,不同的ddr皆可采用此配置。而且根据周期内数据读写数量动态管理ddr低功耗配置参数,在高效率传输的同时实现功耗降低。低功耗控制电路本身也存在低功耗状态,避免因额外添加低功耗控制电路而造成功耗提高。本发明还为可编程控制单元添加了用户接口和uart串口,方便与上位机进行通信。

16.最后应说明的是:以上所述仅为本发明的优选实施例而已,并不用于限制本发明,尽管参照前述实施例对本发明进行了详细的说明,对于本领域的技术人员来说,其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1