SOT-MRAM单元、存储器及其写入方法与流程

本发明涉及磁性存储器,尤其涉及一种sot-mram单元、存储器及其写入方法。

背景技术:

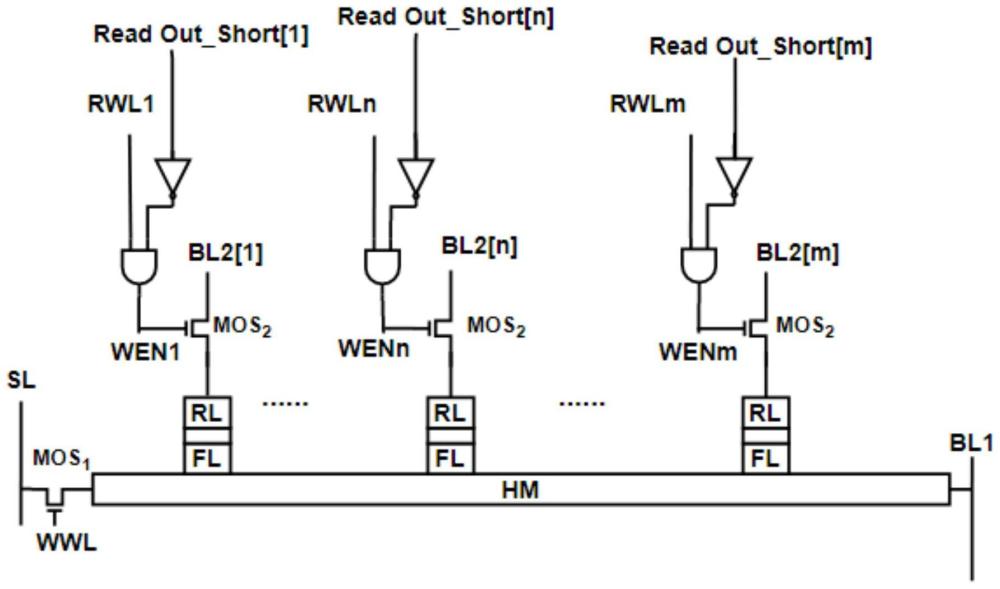

1、mram(magnetoresistive random access memory,磁性随机存储器)为新型的非易失性存储器,mram位元包括1个磁性隧道结(mtj)、1个或多个场效应管(mosfet),其中mtj通常由自由层(fl),参考层(rl)和势垒层(mgo)组成,利用fl和rl磁矩方向平行排列(p态)和反平行排列(ap态)时磁电阻的不同,实现数据存储。为了提高mram的使用寿命,提出了一种基于自旋轨道矩(sot)的mram,sot-mram单元结构如图1所示,其读写通道是分离的:写电流通过重金属层(hm),利用自旋霍尔效应产生自旋流,实现对fl磁矩的翻转;读电流通过mtj,利用tmr效应读取电阻态。因此一个sot-mram单元需要2个mos管,第一mos管mos1的栅极连接wwl(write word line),写操作时wwl施加电压打开该mos管;第二mos管mos2的栅极连接rwl(read word line),读操作时rwl施加电压打开该mos管。该结构中,1个mtj需要2个mos管,这使得单元面积增大,不利于提高阵列密度。

技术实现思路

1、为解决上述问题,本发明提供了一种sot-mram单元、存储器及其写入方法,能够实现高密度的sot-mram。

2、一方面,本发明提供一种sot-mram单元,包括:

3、一条自旋轨道矩提供线;

4、第一mos晶体管,所述第一mos晶体管的栅极与写字线连接,所述自旋轨道矩提供线的一端通过所述第一mos晶体管连接至源线,所述自旋轨道矩提供线的另一端连接至第一位线;

5、位于所述自旋轨道矩提供线上的多个存储位元,每个所述存储位元均包括磁性隧道结和第二mos晶体管,各所述第二mos晶体管的栅极分别连接至不同的读字线,各所述第二mos晶体管的源极分别连接至不同的第二位线,各所述第二mos晶体管的漏极分别连接至不同的所述磁性隧道结。

6、另一方面,本发明提供一种sot-mram存储器,包括:

7、按行排列的多个上述的sot-mram单元;

8、共享的源线和第一位线;

9、各所述sot-mram单元的各所述第一mos晶体管分别连接不同的写字线,在所述自旋轨道矩提供线上处于相同位置的各所述存储位元共享一条读字线。

10、可选地,还包括:

11、读电路,所述读电路包括灵敏放大器,连接于所述第一位线,用于判断各所述sot-mram单元中的各所述磁性隧道结是反平行态或平行态。

12、另一方面,本发明提供一种sot-mram单元,包括:

13、一条自旋轨道矩提供线;

14、第一mos晶体管,所述第一mos晶体管的栅极与写字线连接,所述自旋轨道矩提供线的一端通过所述第一mos晶体管连接至源线,所述自旋轨道矩提供线的另一端连接至第一位线;

15、位于所述自旋轨道矩提供线上的多个存储位元,每个所述存储位元均包括磁性隧道结、第二mos晶体管和逻辑电路,各所述第二mos晶体管的栅极分别对应连接至各所述逻辑电路的输出端,各所述第二mos晶体管的源极分别连接至不同的第二位线,各所述第二mos晶体管的漏极分别连接至不同的所述磁性隧道结,各所述逻辑电路用于根据各自对应的所述磁性隧道结的短路状态值和各条读字线的值产生不同的所述写使能信号。

16、可选地,所述逻辑电路包括:

17、非门,输入端输入所对应的磁性隧道结的短路状态值;

18、与门,一个输入端连接至所对应的读字线,另一个输入端连接至所述非门的输出端,所述与门的输出端输出所述写使能信号至所述第二mos晶体管的栅极。

19、另一方面,本发明提供一种sot-mram存储器,包括:

20、按行排列的多个上述的sot-mram单元;

21、共享的源线和第一位线;

22、各所述sot-mram单元的各所述第一mos晶体管分别连接不同的写字线,在所述自旋轨道矩提供线上处于相同位置的各所述存储位元共享一条读字线。

23、可选地,还包括:

24、读电路,所述读电路包括第一灵敏放大器和第二灵敏器,均连接于所述第一位线,所述第一灵敏放大器用于判断各所述sot-mram单元中的各所述磁性隧道结的短路状态值,所述第二灵敏放大器用于判断各所述sot-mram单元中的各所述磁性隧道结是反平行态或平行态。

25、另一方面,本发明提供一种数据写入方法,应用于上述的sot-mram存储器,所述方法包括:

26、选中目标单元;

27、对于所述目标单元的所有磁性隧道结,实施读短路状态值的操作,所有磁性隧道结的短路状态值初始默认值为0;

28、更新所有磁性隧道结的短路状态值;

29、对于需要写入数据的目标mtj,根据更新后的所有磁性隧道结的短路状态值,实施写操作。

30、可选地,所述方法还包括:

31、若有短路的磁性隧道结,通过ecc进行修复。

32、本发明提供的sot-mram单元、存储器及其写入方法,在一个单元内部,采用多个mtj共用同一条自旋轨道矩提供线(重金属层hm)的结构,若干mtj沉积在同一条自旋轨道矩提供线上,并共享一个第一mos管和一个写字线wwl。每个mtj对应连接一个第二mos管,各第二mos管的栅极分别连接至不同的读字线rwl,用于打开各个mtj的第二位线。相比于现有的sot-mram单元只能存储1bit数据,本发明实施例提供的sot-mram单元可以存储多bit数据,在存储数据量相同的情况下,显然,本发明实施例提供的sot-mram单元降低了所需晶体管的数量,有利于实现高密度阵列。并且,本发明实施例进一步提出了如何避免短路mtj导致sot-mram单元失效的改进方案。

技术特征:

1.一种sot-mram单元,其特征在于,包括:

2.一种sot-mram存储器,其特征在于,包括:

3.根据权利要求2所述的sot-mram存储器,其特征在于,还包括:

4.一种sot-mram单元,其特征在于,包括:

5.根据权利要求4所述的sot-mram单元,其特征在于,所述逻辑电路包括:

6.一种sot-mram存储器,其特征在于,包括:

7.根据权利要求6所述的sot-mram存储器,其特征在于,还包括:

8.一种数据写入方法,应用于如权利要求7所述的sot-mram存储器,其特征在于,所述方法包括:

9.根据权利要求8所述的方法,其特征在于,所述方法还包括:

技术总结

本发明提供一种SOT‑MRAM单元、存储器及其写入方法。所述SOT‑MRAM单元包括:一条自旋轨道矩提供线;第一MOS晶体管,第一MOS晶体管的栅极与写字线连接,自旋轨道矩提供线的一端通过第一MOS晶体管连接至源线,自旋轨道矩提供线的另一端连接至第一位线;位于自旋轨道矩提供线上的多个存储位元,每个存储位元均包括磁性隧道结、第二MOS晶体管和逻辑电路,各第二MOS晶体管的栅极分别对应连接至各所述逻辑电路的输出端,各第二MOS晶体管的源极分别连接至不同的第二位线,各第二MOS晶体管的漏极分别连接至不同的磁性隧道结,各逻辑电路用于根据各自对应的磁性隧道结的短路状态值和各条读字线的值产生不同的写使能信号。

技术研发人员:何世坤,赵建坤,张楠

受保护的技术使用者:浙江驰拓科技有限公司

技术研发日:

技术公布日:2024/4/7

- 还没有人留言评论。精彩留言会获得点赞!