移位寄存器单元及其驱动方法、复位驱动电路、显示装置与流程

1.本公开涉及显示技术领域,特别涉及一种移位寄存器单元及其驱动方法、复位驱动电路、显示装置。

背景技术:

2.有机发光二极管(organic light emitting diode,oled)显示装置是目前显示领域中常见的显示装置之一,具有对比度高、厚度薄和视角广等优点。

3.相关技术中,oled显示装置一般包括:显示面板,以及位于显示面板中的多个像素。每个像素包括像素电路和发光元件。其中,像素电路分别与多个信号端和发光元件耦接,并用于基于该多个信号端提供的信号,向发光元件提供发光驱动信号,以驱动发光元件发光。如,多个信号端至少包括能够提供复位信号的复位信号端和能够提供发光控制信号的发光控制端,且复位信号的脉冲宽度一般需要等于发光控制信号的脉冲宽度,以可靠驱动发光元件发光。

4.但是,因目前复位信号端一般直接通过复位信号线与能够提供复位信号的电源电路耦接,与发光控制信号的提供相互独立,故导致复位信号与发光控制信号的脉冲宽度无法可靠关联,进而导致无法可靠驱动发光元件发光。

技术实现要素:

5.提供一种移位寄存器单元及其驱动方法、复位驱动电路、显示装置,可以解决相关技术中无法可靠驱动发光元件发光的问题。所述技术方案如下:

6.一方面,提供了一种移位寄存器单元,所述移位寄存器单元包括:

7.输入电路,分别与第一时钟端、输入端和上拉节点耦接,并用于响应于所述第一时钟端提供的第一时钟信号,控制所述输入端与所述上拉节点的通断;

8.下拉电路,分别与所述第一时钟端、所述上拉节点、所述输入端、第一电源端、第二电源端、第二时钟端和下拉节点耦接,并用于响应于所述第一时钟信号、所述第二时钟端提供的第二时钟信号、所述输入端提供的输入信号和所述第二电源端提供的第二电源信号,控制所述第一电源端与所述下拉节点的通断,以及响应于所述上拉节点的电位,控制所述第二电源端与所述下拉节点的通断;

9.输出电路,分别与所述上拉节点、所述下拉节点、所述第一电源端、所述第二电源端和输出端耦接,并用于响应于所述上拉节点的电位,控制所述第一电源端与所述输出端的通断,以及响应于所述下拉节点的电位,控制所述第二电源端与所述输出端的通断;

10.其中,所述输出端用于与像素电路的复位信号端耦接,且所述输入信号的脉冲宽度不大于像素电路的发光控制端提供的发光控制信号的脉冲宽度。

11.可选的,所述输入电路包括:串联的第一输入晶体管和第二输入晶体管;

12.其中,所述第一输入晶体管的控制极与所述第二输入晶体管的控制极均与所述第一时钟端耦接,所述第一输入晶体管的第一极与所述输入端耦接,所述第一输入晶体管的

第二极与所述第二输入晶体管的第一极耦接,所述第二输入晶体管的第二极与所述上拉节点耦接。

13.可选的,所述移位寄存器单元还包括:输入控制电路;

14.所述输入控制电路分别与所述上拉节点和所述第一电源端耦接,且还与所述第一输入晶体管和所述第二输入晶体管的串联节点耦接,并用于响应于所述上拉节点的电位,控制所述第一电源端与所述串联节点的通断。

15.可选的,所述输入控制电路包括:输入控制晶体管;

16.所述输入控制晶体管的控制极与所述上拉节点耦接,所述输入控制晶体管的第一极与所述第一电源端耦接,所述输入控制晶体管的第二极与所述串联节点耦接。

17.可选的,所述下拉电路包括:下拉控制子电路和下拉子电路;

18.所述下拉控制子电路分别与所述第一时钟端、所述第二时钟端、所述输入端、所述第一电源端、所述第二电源端和下拉控制节点耦接,并用于响应于所述第一时钟信号,控制所述第一电源端与所述下拉控制节点的通断,以及响应于所述第二时钟信号和所述输入信号,控制所述第二电源端与所述下拉控制节点的通断;

19.所述下拉子电路分别与所述下拉控制节点、所述上拉节点、所述第一电源端、所述第二电源端和所述下拉节点耦接,并用于响应于所述下拉控制节点的电位,控制所述第一电源端与所述下拉节点的通断,以及响应于所述上拉节点的电位,控制所述第二电源端与所述下拉节点的通断。

20.可选的,所述下拉控制子电路包括:第一下拉控制晶体管、第二下拉控制晶体管和第三下拉控制晶体管;

21.所述第一下拉控制晶体管的控制极与所述第一时钟端耦接,所述第一下拉控制晶体管的第一极与所述第一电源端耦接,所述第一下拉控制晶体管的第二极与所述下拉控制节点耦接;

22.所述第二下拉控制晶体管的控制极与所述输入端耦接,所述第二下拉控制晶体管的第一极与所述第二电源端耦接,所述第二下拉控制晶体管的第二极与所述下拉控制节点耦接;

23.所述第三下拉控制晶体管的控制极与所述第二时钟端耦接,所述第二下拉控制晶体管的第一极与所述第二电源端耦接,所述第二下拉控制晶体管的第二极与所述下拉控制节点耦接。

24.可选的,所述下拉子电路包括:第一下拉晶体管和第二下拉晶体管;

25.所述第一下拉晶体管的控制极与所述下拉控制节点耦接,所述第一下拉晶体管的第一极与所述第一电源端耦接,所述第一下拉晶体管的第二极与所述下拉节点耦接;

26.所述第二下拉晶体管的控制极与所述上拉节点耦接,所述第二下拉晶体管的第一极与所述第二电源端耦接,所述第二下拉晶体管的第二极与所述下拉节点耦接。

27.可选的,所述移位寄存器单元还包括:电位调节电路;

28.所述电位调节电路分别与所述下拉控制节点和所述下拉节点耦接,并用于调节所述下拉控制节点的电位和所述下拉节点的电位。

29.可选的,所述电位调节电路包括:第一电容;

30.所述第一电容的第一端与所述下拉控制节点耦接,所述第一电容的第二端与所述

下拉节点耦接。

31.可选的,所述输出电路包括:第一输出子电路和第二输出子电路;

32.所述第一输出子电路分别与所述上拉节点、所述第一电源端和所述输出端耦接,并用于响应于所述上拉节点的电位,控制所述第一电源端与所述输出端的通断;

33.所述第二输出子电路分别与所述下拉节点、所述第二电源端和所述输出端耦接,并用于响应于所述下拉节点的电位,控制所述第二电源端与所述输出端的通断。

34.可选的,所述第一输出子电路包括:第一输出晶体管和第二电容;

35.所述第一输出晶体管的控制极与所述上拉节点耦接,所述第一输出晶体管的第一极与所述第一电源端耦接,所述第一输出晶体管的第二极与所述输出端耦接;

36.所述第二电容的第一端与所述第一输出晶体管的控制极耦接,所述第二电容的第二端与所述第一输出晶体管的第二极耦接。

37.可选的,所述第二输出子电路包括:第二输出晶体管和第三电容;

38.所述第二输出晶体管的控制极与所述下拉节点耦接,所述第二输出晶体管的第一极与所述第二电源端耦接,所述第二输出晶体管的第二极与所述输出端耦接;

39.所述第三电容的第一端与所述第二输出晶体管的控制极耦接,所述第三电容的第二端与所述第二输出晶体管的第一极耦接。

40.另一方面,提供了一种移位寄存器单元的驱动方法,所述方法用于驱动如上述一方面所述的移位寄存器单元,所述方法包括:

41.第一阶段,第一时钟端提供的第一时钟信号的电位为第一电位,第二时钟端提供的第二时钟信号的电位和输入端提供的输入信号的电位为第二电位,输入电路响应于所述第一时钟信号,控制所述输入端与上拉节点导通,下拉控制电路响应于所述第一时钟信号、所述第二时钟信号、所述输入信号和第二电源端提供的第二电源信号,控制第一电源端与下拉节点导通,输出电路响应于所述下拉节点的电位,控制所述第二电源端与输出端导通;

42.第二阶段,所述第一时钟信号的电位和所述输入信号的电位为第一电位,所述第二时钟信号的电位为第二电位,所述输入电路响应于所述第一时钟信号,控制所述输入端与所述上拉节点导通,所述下拉控制电路响应于所述第一时钟信号、所述第二时钟信号、所述输入信号和所述第二电源信号,控制所述第二电源端与下拉节点导通,输出电路响应于所述上拉节点的电位,控制所述第一电源端与所述输出端导通;

43.其中,所述第一电源端提供的第一电源信号的电位为第一电位,所述第二电源信号的电位为第二电位。

44.又一方面,提供了一种复位驱动电路,所述复位驱动电路包括:至少两个级联的如上述一方面所述的移位寄存器单元;

45.其中,第一级移位寄存器单元的输入端与复位开启端耦接,除第一级移位寄存器单元外的其他级移位寄存器单元中,每一级移位寄存器单元的输入端均与级联的上一级移位寄存器单元的输出端耦接。

46.再一方面,提供了一种显示装置,所述显示装置包括:显示面板,以及如上述又一方面所述的复位驱动电路;

47.所述显示面板包括多个像素,所述像素包括像素电路和发光元件,所述像素电路分别与复位信号端、发光控制端和所述发光元件耦接,并用于响应于来自所述复位信号端

的复位信号和来自所述发光控制端的发光控制信号,驱动所述发光元件发光;

48.所述复位驱动电路与所述复位信号端耦接,并用于为所述复位信号端提供复位信号。

49.可选的,所述像素电路包括多个晶体管,且所述多个晶体管均为n型氧化物晶体管。

50.综上所述,本公开实施例提供的技术方案带来的有益效果至少可以包括:

51.提供了一种移位寄存器单元及其驱动方法、复位驱动电路、显示装置。该移位寄存器单元包括输入电路、下拉电路和输出电路。其中,输入电路能够控制输入端与上拉节点的通断,以控制上拉节点的电位。下拉电路能够控制第一电源端和第二电源端与下拉节点的通断,以控制下拉节点的电位。输出电路能够响应于上拉节点的电位,控制第一电源端与输出端的通断,且能够响应于下拉节点的电位,控制第二电源端与输出端的通断,从而向输出端传输第一电位的第一电源信号和第二电位的第二电源信号,输出端用于与复位信号端耦接。如此,能够基于发光控制信号灵活设置输入端提供的输入信号,使得通过该移位寄存器单元向像素电路的复位信号端可靠传输复位信号,从而使得像素电路可靠驱动发光元件发光。

附图说明

52.为了更清楚地说明本公开实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本公开的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

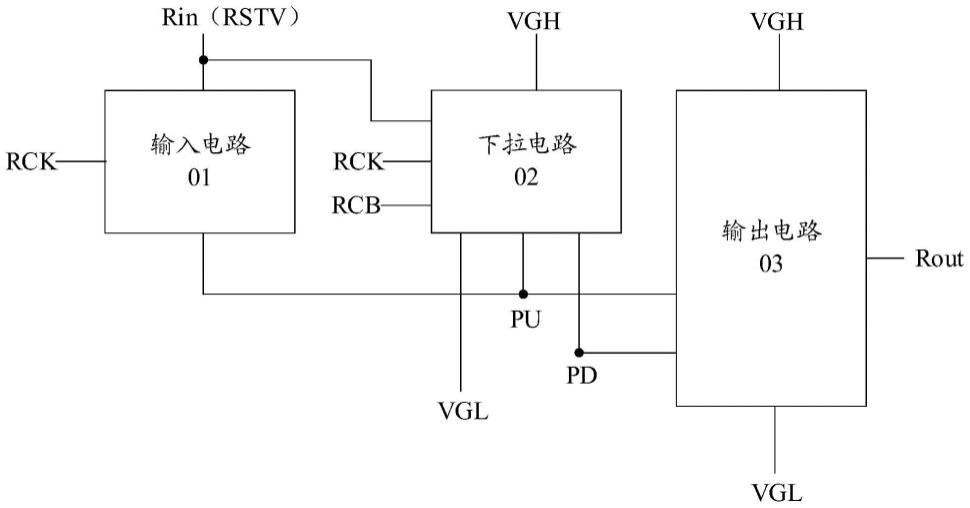

53.图1是本公开实施例提供的一种移位寄存器单元的结构示意图;

54.图2是本公开实施例提供的一种像素电路和发光元件的结构示意图;

55.图3是本公开实施例提供的另一种像素电路和发光元件的结构示意图;

56.图4是本公开实施例提供的一种像素电路的信号端的时序图;

57.图5是本公开实施例提供的另一种移位寄存器单元的结构示意图;

58.图6是本公开实施例提供的又一种移位寄存器单元的结构示意图;

59.图7是本公开实施例提供的再一种移位寄存器单元的结构示意图;

60.图8是本公开实施例提供的再一种移位寄存器单元的结构示意图;

61.图9是本公开实施例提供的再一种移位寄存器单元的结构示意图;

62.图10是本公开实施例提供的再一种移位寄存器单元的结构示意图;

63.图11是本公开实施例提供的一种移位寄存器单元的驱动方法流程图;

64.图12是本公开实施例提供的一种移位寄存器单元的信号端的时序图;

65.图13是图10所示的移位寄存器单元在第一阶段的等效电路图;

66.图14是图10所示的移位寄存器单元在第二阶段的等效电路图;

67.图15是图10所示的移位寄存器单元在第三阶段的等效电路图;

68.图16是图10所示的移位寄存器单元在第四阶段的等效电路图;

69.图17是图10所示的移位寄存器单元在第八阶段的等效电路图;

70.图18是图10所示的移位寄存器单元在第十阶段的等效电路图;

71.图19是本公开实施例提供的一种移位寄存器单元的信号端的时序仿真图;

72.图20是本公开实施例提供的一种复位驱动电路的结构示意图;

73.图21是本公开实施例提供的一种显示装置的结构示意图。

具体实施方式

74.为使本公开的目的、技术方案和优点更加清楚,下面将结合附图对本公开实施方式作进一步地详细描述。

75.本公开所有实施例中采用的晶体管均可以为薄膜晶体管或场效应管或其他特性相同的器件,根据在电路中的作用本公开的实施例所采用的晶体管主要为开关晶体管。由于这里采用的开关晶体管的源极和漏极是对称的,所以其源极、漏极是可以互换的。在本公开实施例中,将其中源极称为第一极,漏极称为第二极。按附图中的形态规定晶体管的中间端为控制极,也可以称为栅极、信号输入端为源极、信号输出端为漏极。此外,本公开实施例所采用的开关晶体管可以包括p型开关晶体管和n型开关晶体管中的任一种,其中,p型开关晶体管在栅极为低电平时导通,在栅极为高电平时截止,n型开关晶体管在栅极为高电平时导通,在栅极为低电平时截止。此外,本公开各个实施例中的多个信号都对应有第一电位和第二电位。第一电位和第二电位仅代表该信号的电位有2个状态量,不代表全文中第一电位或第二电位具有特定的数值。

76.图1是本公开实施例提供的一种移位寄存器单元的结构示意图。如图1所示,该移位寄存器单元包括:输入电路01,下拉电路02和输出电路03。

77.其中,输入电路01分别与第一时钟端rck、输入端rin和上拉节点pu耦接(即,电连接),并用于响应于第一时钟端rck提供的第一时钟信号,控制输入端rin与上拉节点pu的通断。

78.例如,该输入电路01可以用于在第一时钟端rck提供的第一时钟信号的电位为第一电位时,控制输入端rin与上拉节点pu导通。此时,输入端rin提供的输入信号即可以传输(也可以称为“写入”)至上拉节点pu。以及,该输入电路01可以用于在第一时钟信号的电位为第二电位时,控制输入端rin与上拉节点pu断开耦接。

79.可选的,在本公开实施例中,第一电位可以为有效电位,第二电位可以为无效电位。并且,第一电位可以为高电位,第二电位可以为低电位,即第一电位相对于第二电位较大。该电位基础上对应的电路中晶体管可以为n型晶体管。若电路中晶体管为p型晶体管,则第一电位可以为低电位,第二电位可以为高电位,即第一电位相对于第二电位较小。下述实施例不再赘述。

80.下拉电路02分别与第一时钟端rck、上拉节点pu、输入端rin、第一电源端vgh、第二电源端vgl、第二时钟端rcb和下拉节点pd耦接,并用于响应于第一时钟信号、第二时钟端rcb提供的第二时钟信号、输入端rin提供的输入信号、第二电源端vgl提供的第二电源信号,控制第一电源端vgh与下拉节点pd的通断,以及响应于上拉节点pu的电位,控制第二电源端vgl与下拉节点pd的通断。

81.例如,下拉电路02可以在第一时钟信号的电位为第一电位,输入信号的电位为第二电位,第二时钟端rcb提供的第二时钟信号的电位为第二电位时,控制第一电源端vgh与下拉节点pd导通。此时,第一电源端vgh提供的第一电位的第一电源信号即可以传输至下拉

节点pd,以为下拉节点pd充电。以及,下拉电路02可以在第一时钟信号的电位为第二电位,输入信号的电位为第一电位,第二时钟信号的电位为第一电位时,控制第一电源端vgh与下拉节点pd断开耦接。

82.同理,下拉电路02可以在上拉节点pu的电位为第一电位时,控制第二电源端vgl与下拉节点pd导通。此时,第二电源端vgl提供的第二电位的第二电源信号的电位即可以传输至下拉节点pd,以为下拉节点pd降噪。以及,下拉电路02可以在上拉节点pu的电位为第二电位,控制第二电源端vgl与下拉节点pd断开耦接。

83.输出电路03分别与上拉节点pu、下拉节点pd、第一电源端vgh、第二电源端vgl和输出端rout耦接,并用于响应于上拉节点pu的电位,控制第一电源端vgh与输出端rout的通断,以及响应于下拉节点pd的电位,控制第二电源端vgl与输出端rout的通断。

84.例如,输出电路03可以在上拉节点pu的电位为第一电位时,控制第一电源端vgh与输出端rout导通。此时,第一电位的第一电源信号即可以传输至输出端rout。以及,输出电路03可以在上拉节点pu的电位为第二电位时,控制第一电源端vgh与输出端rout断开耦接。

85.同理,输出电路03可以在下拉节点pd的电位为第一电位时,控制第二电源端vgl与输出端rout导通。此时,第二电位的第二电源信号即可以传输至输出端rout。以及,输出电路03可以在下拉节点pd的电位为第二电位时,控制第二电源端vgl与输出端rout断开耦接。

86.即,输出电路03可以向输出端rout传输第一电位的第一电源信号和第二电位的第二电源信号,达到无需新增时钟端即可以向输出端rout可靠传输不同电位的输出信号的目的。

87.需要说明的是,本公开实施例记载的移位寄存器单元的输出端rout用于与像素电路的复位信号端rst1(n)耦接。如此可知,最终向输出端rout传输的第一电位的第一电源信号和第二电位的第二电源信号可以作为复位信号传输至复位信号端rst1(n)。以及,输入信号的脉冲宽度不大于(即,小于或等于)像素电路的发光控制端em(n)提供的发光控制信号的脉冲宽度。

88.示例的,图2示出了一种像素电路的结构示意图。如图2所示,该像素电路p1可以分别与复位信号端rst1(n)和发光控制端em(n)耦接,还可以分别与复位电源端vinit,数据信号端data(n),驱动电源端vdd,发光元件l1的第一极,以及栅极信号端gate(n)和gate(n-1)耦接,发光元件l1的第二极可以与下拉电源端vss耦接。该像素电路p1可以基于所耦接的各信号端提供的信号和驱动电源端vdd提供的信号,向发光元件l1的第一极传输发光驱动信号,使得发光元件l1在发光驱动信号与下拉电源端提供的下拉电源信号的压差作用下发光。其中,复位信号端rst1(n)可以与公开实施例记载的移位寄存器单元的输出端rout耦接,并接收该移位寄存器单元提供的复位信号。相应的,本公开实施例记载的移位寄存器单元也可以称为复位移位寄存器单元。

89.可选的,结合图2还可以看出,目前常用的像素电路一般为7t1c(即,七个晶体管t1至t7和一个电容c0,t1为驱动晶体管)结构的电路,当然,还可以为其他结构,如6t1c。以及,本公开实施例记载的发光元件l1可以为oled,相应的,发光元件l1第一极可以为阳极,第二极可以为阴极,oled的阳极一般采用高功函数的氧化铟锡(indium tin oxide,ito)材料制成。并且,对于oled而言,受工艺特性影响,一般是在完成像素电路p1中晶体管的制造之后,将oled的阳极与像素电路p1耦接。

90.当然,在一些其他实施例中,发光元件l1还可以为图3所示的微型发光二极管(micro light emitting diode,mled)。结合图3,对于mled而言,其阳极一般耦接于像素电路p1中驱动晶体管t1的上方,且该mled的阳极与电源端lvdd耦接,像素电路p1与该mled的阴极耦接,复位电源端标识为ivdd,下拉电源端标识为lvss。此外,无论是何种类型的像素,本公开实施例记载的像素电路p1中,多个晶体管可以均为n型氧化物(oxide)晶体管。

91.示例的,在图2所示结构基础上,图4示出了一种像素电路p1所耦接的各信号端的时序图。参考图4可以看出,在发光阶段t03之前,即发光控制端em提供的发光控制信号的电位为有效电位之前,复位信号端rst1(n)可以一直提供第一电位(即,有效电位)的复位信号,以使得发光元件l1的阳极可以用复位电源端vinit提供的复位电源信号所保持,避免发光元件l1误发光。到发光控制信号的电位跳变为有效电位之后,复位信号端rst1(n)可以停止提供有效电位的复位信号。即,图4示出的输入信号的脉冲宽度等于发光控制信号的脉冲宽度。此处,输入信号的脉冲宽度可以是指:输入信号的电位为有效电位的时长。发光控制信号的脉冲宽度可以是指:发光控制信号的电位为无效电位的时长。如此可知,本公开实施例通过设置移位寄存器单元所耦接的输入端rin提供的输入信号的脉冲宽度不大于像素电路的发光控制端em(n)提供的发光控制信号的脉冲宽度,可以可靠确保在发光阶段之前,持续向复位信号端rst1(n)提供有效电位的复位信号,从而确保发光元件l1可靠发光。

92.此外,图4还示意性示出栅极信号端gate(n)和gate(n-1)提供的栅极驱动信号,以及数据信号端data(n)提供的数据信号。其中,在发光阶段t03之前,还可以包括复位阶段t01和数据写入阶段t02。以及,在复位阶段t01,复位信号端rst1(n)提供的复位信号的电位和栅极信号端gate(n-1)提供的栅极驱动信号的电位均为有效电位,实现对所耦接处的复位。在数据写入阶段t02,栅极信号端gate(n)提供的栅极驱动信号的电位为第一电位,使得数据信号端data(n)提供的数据信号可靠写入所耦接处。最终,实现点亮发光元件l1。

93.需要说明的是,上述n代表第n级,n一般为大于0的整数。在本公开实施例中,其实可以包括级联的多个图1所示的移位寄存器单元,以分别与不同像素电路p1的复位信号端rst1(n)耦接,级联的多个移位寄存器单元也可以称为复位驱动电路,简称rgoa。并且,第一级移位寄存器单元的输入端rin一般与复位开启端rstv耦接,除第一级移位寄存器单元外的其他级移位寄存器单元中,每一级移位寄存器单元的输入端rin均与级联的上一级移位寄存器单元的输出端rout耦接。图4中示出的输入信号即为第一级移位寄存器单元耦接的复位开启端rstv提供的复位开启信号。本公开实施例可以认为是提出一种rgoa,并基于发光控制信号灵活设置复位开启端rstv提供的复位开启信号的脉冲宽度来向像素电路p1的复位信号端rst1(n)提供所需的复位信号。

94.综上所述,本公开实施例提供了一种移位寄存器单元。该移位寄存器单元包括输入电路、下拉电路和输出电路。输入电路能够控制输入端与上拉节点的通断,以控制上拉节点的电位。下拉电路能够控制第一电源端和第二电源端与下拉节点的通断,以控制下拉节点的电位。输出电路能够响应于上拉节点的电位,控制第一电源端与输出端的通断,且能够响应于下拉节点的电位,控制第二电源端与输出端的通断,从而向输出端传输第一电位的第一电源信号和第二电位的第二电源信号,输出端用于与复位信号端耦接。如此,能够基于发光控制信号灵活设置输入端提供的输入信号,使得通过该移位寄存器单元向像素电路的复位信号端可靠传输复位信号,从而使得像素电路可靠驱动发光元件发光。

95.图5是本公开实施例提供的另一种移位寄存器单元的结构示意图。如图5所示,本公开实施例记载的下拉电路02可以包括:下拉控制子电路021和下拉子电路022。

96.其中,下拉控制子电路021可以分别与第一时钟端rck、第二时钟端rcb、输入端rin、第一电源端vgh、第二电源端vgl和下拉控制节点pd_c耦接。下拉控制子电路021可以用于响应于第一时钟信号,控制第一电源端vgh与下拉控制节点pd_c的通断,以及响应于第二时钟信号和输入信号,控制第二电源端vgl与下拉控制节点pd_c的通断。

97.例如,下拉控制子电路021可以在第一时钟信号的电位为第一电位时,控制第一电源端vgh与下拉控制节点pd_c导通。此时,第一电位的第一电源信号可以传输至下拉控制节点pd_c。以及下拉控制子电路021可以在第一时钟信号的电位为第二电位时,控制第一电源端vgh与下拉控制节点pd_c断开耦接。

98.同理,下拉控制子电路021可以在第二时钟信号的电位和/或输入信号的电位为第一电位时,控制第二电源端vgl与下拉控制节点pd_c导通。此时,第二电位的第二电源信号可以传输至下拉控制节点pd_c。以及下拉控制子电路021可以在第二时钟信号的电位或输入信号的电位为第二电位时,控制第二电源端vgl与下拉控制节点pd_c断开耦接。

99.下拉子电路022可以分别与下拉控制节点pd_c、上拉节点pu、第一电源端vgh、第二电源端vgl和下拉节点pd耦接。下拉子电路022可以用于响应于下拉控制节点pd_c的电位,控制第一电源端vgh与下拉节点pd的通断,以及响应于上拉节点pu的电位,控制第二电源端vgl与下拉节点pd的通断。

100.例如,下拉子电路022可以在下拉控制节点pd_c的电位为第一电位时,控制第一电源端vgh与下拉节点pd耦接。此时,第一电位的第一电源信号可以传输至下拉节点pd。以及,下拉子电路022可以在下拉控制节点pd_c的电位为第二电位时,控制第一电源端vgh与下拉节点pd断开耦接。

101.同理,下拉子电路022可以在上拉节点pu的电位为第一电位时,控制第二电源端vgl与下拉节点pd耦接。此时,第二电位的第二电源信号可以传输至下拉节点pd。以及,下拉子电路022可以在上拉节点pu的电位为第二电位时,控制第二电源端vgl与下拉节点pd断开耦接。

102.图6是本公开实施例提供的又一种移位寄存器单元的结构示意图。如图6所示,本公开实施例记载的输出电路03可以包括:第一输出子电路031和第二输出子电路032。

103.其中,第一输出子电路031可以分别与上拉节点pu、第一电源端vgh和输出端rout耦接。第一输出子电路031用于响应于上拉节点pu的电位,控制第一电源端vgh与输出端rout的通断。

104.例如,第一输出子电路031可以在上拉节点pu的电位为第一电位时,控制第一电源端vgh与输出端rout导通。此时,第一电位的第一电源信号可以传输至输出端rout。以及,第一输出子电路031可以在上拉节点pu的电位为第二电位时,控制第一电源端vgh与输出端rout断开耦接。

105.第二输出子电路032可以分别与下拉节点pd、第二电源端vgl和输出端rout耦接。第二输出子电路032可以用于响应于下拉节点pd的电位,控制第二电源端vgl与输出端rout的通断。

106.例如,第二输出子电路032可以在下拉节点pd的电位为第一电位时,控制第二电源

端vgl与输出端rout导通。此时,第二电位的第二电源信号可以传输至输出端rout。以及,第二输出子电路032可以在下拉节点pd的电位为第二电位时,控制第二电源端vgl与输出端rout断开耦接。

107.图7是本公开实施例提供的再一种移位寄存器单元的结构示意图。如图7所示,本公开实施例记载的输入电路01可以包括:串联的第一输入晶体管m1a和第二输入晶体管m1b。通过设置输入电路01包括串联的两个输入晶体管,可以降低输入电路01的漏电流,确保对上拉节点pu的电位的可靠控制。

108.其中,第一输入晶体管m1a的控制极(如,栅极)与第二输入晶体管m1b的控制极可以均与第一时钟端rck耦接,第一输入晶体管m1a的第一极可以与输入端rin耦接,第一输入晶体管m1a的第二极可以与第二输入晶体管m1b的第一极耦接,第二输入晶体管m1b的第二极可以与上拉节点pu耦接。

109.继续参考图7,下拉控制子电路021可以包括:第一下拉控制晶体管m2、第二下拉控制晶体管m3和第三下拉控制晶体管m4。

110.其中,第一下拉控制晶体管m2的控制极可以与第一时钟端rck耦接,第一下拉控制晶体管m2的第一极可以与第一电源端vgh耦接,第一下拉控制晶体管m2的第二极与下拉控制节点pd_c耦接。

111.第二下拉控制晶体管m3的控制极可以与输入端rin耦接,第二下拉控制晶体管m3的第一极可以与第二电源端vgl耦接,第二下拉控制晶体管m3的第二极可以与下拉控制节点pd_c耦接。

112.第三下拉控制晶体管m4的控制极可以与第二时钟端rcb耦接,第二下拉控制晶体管m3的第一极可以与第二电源端vgl耦接,第二下拉控制晶体管m3的第二极可以与下拉控制节点pd_c耦接。

113.可选的,在本公开实施例中,第一下拉控制晶体管m2的电阻可以大于第二下拉控制晶体管m3的电阻,如此,可以使得第一下拉控制晶体管m2和第二下拉控制晶体管m3均开启时,确保是由第二电源端vgl向下拉控制节点pd_c可靠传输第二电位的第二电源信号。

114.继续参考图7,下拉子电路022可以包括:第一下拉晶体管m5和第二下拉晶体管m6。

115.第一下拉晶体管m5的控制极可以与下拉控制节点pd_c耦接,第一下拉晶体管m5的第一极可以与第一电源端vgh耦接,第一下拉晶体管m5的第二极可以与下拉节点pd耦接。

116.第二下拉晶体管m6的控制极可以与上拉节点pu耦接,第二下拉晶体管m6的第一极可以与第二电源端vgl耦接,第二下拉晶体管m6的第二极可以与下拉节点pd耦接。

117.继续参考图7,第一输出子电路031可以包括:第一输出晶体管m7和第二电容c2。

118.其中,第一输出晶体管m7的控制极可以与上拉节点pu耦接,第一输出晶体管m7的第一极可以与第一电源端vgh耦接,第一输出晶体管m7的第二极可以与输出端rout耦接。

119.第二电容c2的第一端可以与第一输出晶体管m7的控制极耦接,第二电容c2的第二端可以与第一输出晶体管m7的第二极耦接。

120.继续参考图7,第二输出子电路032可以包括:第二输出晶体管m8和第三电容c3。

121.其中,第二输出晶体管m8的控制极可以与下拉节点pd耦接,第二输出晶体管m8的第一极可以与第二电源端vgl耦接,第二输出晶体管m8的第二极可以与输出端rout耦接。

122.第三电容c3的第一端可以与第二输出晶体管m8的控制极耦接,第三电容c3的第二

端可以与第二输出晶体管m8的第一极耦接。

123.可选的,在图7所示结构基础上,参考图8,其示出了本公开实施例提供的再一种移位寄存器单元。如图8所示,本公开实施例记载的移位寄存器单元还可以包括:输入控制电路04。

124.输入控制电路04可以分别与上拉节点pu和第一电源端vgh耦接,且还可以与第一输入晶体管m1a和第二输入晶体管m1b的串联节点cbc耦接。输入控制电路04可以用于响应于上拉节点pu的电位,控制第一电源端vgh与串联节点cbc的通断。

125.例如,输入控制电路04可以在上拉节点pu的电位为第一电位时,控制第一电源端vgh与串联节点cbc导通。此时,第一电位的第一电源信号可以传输至串联节点cbc。以及,输入控制电路04可以在上拉节点pu的电位为第二电位时,控制第一电源端vgh与串联节点cbc断开耦接。如此,可以避免串联节点cbc处发生漏电,从而确保对上拉节点pu的可靠充电,即确保上拉节点pu的电位可靠的保持在第一电位。

126.可选的,图9示出了本公开实施例提供的再一种移位寄存器单元的结构示意图。如图9所示,本公开实施例记载的移位寄存器单元还可以包括:电位调节电路05。

127.该电位调节电路05可以分别与下拉控制节点pd_c和下拉节点pd耦接。该电位调节电路05可以用于调节下拉控制节点pd_c的电位和下拉节点pd的电位。如此,可以确保下拉控制节点pd_c和下拉节点pd的电位稳定性。

128.示例的,在图8和图9基础上,图10示出了本公开实施例提供的再一种移位寄存器单元的结构示意图。如图10所示,本公开实施例记载的输入控制电路04可以包括:输入控制晶体管m1c。电位调节电路05可以包括:第一电容c1。

129.其中,输入控制晶体管m1c的控制极可以与上拉节点pu耦接,输入控制晶体管m1c的第一极可以与第一电源端vgh耦接,输入控制晶体管m1c的第二极可以与串联节点cbc耦接。

130.第一电容c1的第一端可以与下拉控制节点pd_c耦接,第一电容c1的第二端可以与下拉节点pd耦接。在此基础上可知,电位调节电路05可以通过其自身具有的自举作用,可靠调节下拉控制节点pd_c和下拉节点pd的电位。

131.需要说明的是,上述图10所示的移位寄存器单元是10t3c(即,包括10个晶体管和3个电容)结构的移位寄存器单元。以及,在上述各实施例中,均是以各个晶体管为n型晶体管,且晶体管为oxide晶体管,且第一电位相对于第二电位为高电位为例进行的说明。

132.综上所述,本公开实施例提供了一种移位寄存器单元。该移位寄存器单元包括输入电路、下拉电路和输出电路。输入电路能够控制输入端与上拉节点的通断,以控制上拉节点的电位。下拉电路能够控制第一电源端和第二电源端与下拉节点的通断,以控制下拉节点的电位。输出电路能够响应于上拉节点的电位,控制第一电源端与输出端的通断,且能够响应于下拉节点的电位,控制第二电源端与输出端的通断,从而向输出端传输第一电位的第一电源信号和第二电位的第二电源信号,输出端用于与复位信号端耦接。如此,能够基于发光控制信号灵活设置输入端提供的输入信号,使得通过该移位寄存器单元向像素电路的复位信号端可靠传输复位信号,从而使得像素电路可靠驱动发光元件发光。

133.图11是本公开实施例提供的一种移位寄存器单元的驱动方法,该方法用于驱动如上述附图所示的移位寄存器单元中。如图11所示,该方法包括:

134.步骤1101、第一阶段,第一时钟端提供的第一时钟信号的电位为第一电位,第二时钟端提供的第二时钟信号的电位和输入端提供的输入信号的电位为第二电位,输入电路响应于第一时钟信号,控制输入端与上拉节点导通,下拉控制电路响应于第一时钟信号、第二时钟信号、输入信号和第二电源端提供的第二电源信号,控制第一电源端与下拉节点导通,输出电路响应于下拉节点的电位,控制第二电源端与输出端导通。

135.步骤1102、第二阶段,第一时钟信号的电位和输入信号的电位为第一电位,第二时钟信号的电位为第二电位,输入电路响应于第一时钟信号,控制输入端与上拉节点导通,下拉控制电路响应于第一时钟信号、第二时钟信号、输入信号和第二电源信号,控制第二电源端与下拉节点导通,输出电路响应于上拉节点的电位,控制第一电源端与输出端导通。

136.其中,第一电源端提供的第一电源信号的电位可以为第一电位,第二电源信号的电位可以为第二电位。

137.可选的,以图10所示的移位寄存器单元,其中输入端rin与输入开启端rstv耦接,各个晶体管为n型晶体管,相应的,第一电位(即,有效电位)为高电位,第二电位(即,无效电位)为低电位为例,详细介绍本公开实施例记载的移位寄存器单元的驱动原理:

138.示例的,图12是本公开实施例提供的一种移位寄存器单元中各信号端的时序图。如图12所示,可以将整个驱动过程划分为1至10共10个阶段。

139.其中,在第一阶段1,第一时钟端rck提供的第一时钟信号的电位为高电位,输入开启端rstv(即,输入端rin)提供的输入信号的电位和第二时钟端rcb提供的第二时钟信号的电位均为低电位。在此基础上,第一输入晶体管m1a,第二输入晶体管m1b和第一下拉控制晶体管m2均开启,第二下拉控制晶体管m3和第三下拉控制晶体管m4均关闭。相应的,其一,输入端rin与上拉节点pu导通,低电位的输入信号可以经开启的第一输入晶体管m1a和第二输入晶体管m1b传输至上拉节点pu,从而为上拉节点pu放电,此时上拉节点pu的电位为低电位。在此基础上,第二下拉晶体管m6,第一输出晶体管m7和输入控制晶体管m1c均关闭。其二,第一电源端vgh与下拉控制节点pd_c导通,高电位的第一电源信号可以经开启的第一下拉控制晶体管m2传输至下拉控制节点pd_c,从而为下拉控制节点pd_c充电,此时下拉控制节点pd_c的电位为高电位。在此基础上,第一下拉晶体管m5开启,第一电源端vgh与下拉节点pd导通。第一电位的第一电源信号还可以经开启的第一下拉晶体管m5传输至下拉节点pd,从而为下拉节点pd充电,此时下拉节点pd的电位为高电位。在此基础上,第二输出晶体管m8开启。相应的,第二电源端vgh与输出端rout导通,第二电位的第二电源信号可以经开启的第二输出晶体管m8传输至输出端rout,从而为输出端rout放电,此时输出端rout的电位为低电位。此外,在第一电容c1的自举作用下,下拉节点pd可以可靠处于高电位。例如,图13示出了移位寄存器单元在第一阶段1的等效电路图。

140.在第二阶段2,第一时钟端rck提供的第一时钟信号的电位为低电位,输入开启端rstv(即,输入端rin)提供的输入信号的电位和第二时钟端rcb提供的第二时钟信号的电位均为高电位。上拉节点pu的电位在第二电容c2的作用下保持为第一阶段1的低电位。在此基础上,第二下拉控制晶体管m3和第三下拉控制晶体管m4均开启。第一输入晶体管m1a,第二输入晶体管m1b,第一下拉控制晶体管m2,输入控制晶体管m1c,第一输出晶体管m7和第二下拉晶体管m6均关闭。相应的,第二电源端vgl与下拉控制节点pd_c导通,第二电位的第二电源信号可以经开启的第二下拉控制晶体管m3和第三下拉控制晶体管m4传输至下拉控制节

点pd_c,从而为下拉控制节点pd_c放电,此时下拉控制节点pd_c的电位为低电位。在此基础上,第一下拉晶体管m5关闭。如此,在第一电容c1的自举作用下,下拉节点pd可以保持为第一阶段1的高电位。在此基础上,第二输出晶体管m8开启。相应的,第二电源端vgh与输出端rout导通,第二电位的第二电源信号可以经开启的第二输出晶体管m8传输至输出端rout,从而为输出端rout继续放电,此时输出端rout的电位为低电位。例如,图14示出了移位寄存器单元在第二阶段2的等效电路图。

141.在第三阶段3,第一时钟端rck提供的第一时钟信号的电位和输入开启端rstv(即,输入端rin)提供的输入信号的电位均为高电位,第二时钟端rcb提供的第二时钟信号的电位为低电位。在此基础上,第一输入晶体管m1a,第二输入晶体管m1b,第一下拉控制晶体管m2和第二下拉控制晶体管m3均开启,第三下拉控制晶体管m4关闭。相应的,其一,第一电源端vgh和第二电源端vgl均与下拉控制节点pd_c导通,但是,因第一下拉控制晶体管m2的电阻大于第二下拉控制晶体管m3的电阻,故可以是第二电位的第二电源信号经开启的第二下拉控制晶体管m3传输至下拉控制节点pd_c,从而为下拉控制节点pd_c放电,此时下拉控制节点pd_c的电位为低电位。在此基础上,第一下拉晶体管m5关闭。其二,输入端rin与上拉节点pu导通,高电位的输入信号可以经开启的第一输入晶体管m1a和第二输入晶体管m1b传输至上拉节点pu,从而为上拉节点pu充电,此时上拉节点pu的电位为高电位。在此基础上,输入控制晶体管m1c,第一输出晶体管m7和第二下拉晶体管m6均开启。相应的,第一电源端vgh与串联节点cbc导通,第一电位的第一电源信号可以经开启的输入控制晶体管m1c传输至串联节点cbc,使得第一输入晶体管m1a和第二输入晶体管m1b可靠开启。第二电源端vgl与下拉节点pd导通,第二电位的第二电源信号可以经开启的第二下拉晶体管m6传输至下拉节点pd,从而为下拉节点pd放电,此时下拉节点pd的电位为低电位。在此基础上,第二输出晶体管m8关闭。以及,第一电源端vgh与输出端rout导通,第一电位的第一电源信号可以经开启的第一输出晶体管m7传输至输出端rout,从而为输出端rout充电,此时输出端rout的电位为高电位。例如,图15示出了移位寄存器单元在第三阶段3的等效电路图。

142.此外,在第三阶段t3,受第二电容c2的自举作用影响,上拉节点pu的电位可以被充电至较高电压。此时,上拉节点pu的电位变化值δv

pu

可以满足:δv

pu

=c20/(cgsm7+c20+c

pu

)*δvrout;c20是指第二电容c2的容值,cgsm7是指第一输出晶体管m7的寄生电容,c

pu

是指除第二电容c2和第一输出晶体管m7的寄生电容外,上拉节点pu处的寄生电容值,δvrout是指输出端rout的电位变化值。这里的变化值是指当前阶段与前一阶段比较的变化值。

143.在第四阶段4,第一时钟端rck提供的第一时钟信号的电位为低电位,输入开启端rstv(即,输入端rin)提供的输入信号的电位和第二时钟端rcb提供的第二时钟信号的电位均为高电位。以及,上拉节点pu的电位在第二电容c2的作用下保持为第三阶段3的高电位。在此基础上,输入控制晶体管m1c,第二下拉控制晶体管m3,第三下拉控制晶体管m4,第二下拉晶体管m6和第一输出晶体管m7均开启。第一输入晶体管m1a,第二输入晶体管m1b和第一下拉控制晶体管m2均关闭。相应的,其一,第一电源端vgh与串联节点cbc导通,第一电位的第一电源信号可以经开启的输入控制晶体管m1c传输至串联节点cbc。其二,第二电源端vgl与下拉控制节点pd_c导通,第二电位的第二电源信号可以经开启的第二下拉控制晶体管m3和第三下拉控制晶体管m4传输至下拉控制节点pd_c,从而为下拉控制节点pd_c放电,此时下拉控制节点pd_c的电位为低电位。在此基础上,第一下拉晶体管m5关闭。其三,第二电源

端vgl与下拉节点pd导通。第二电位的第二电源信号可以经开启的第二下拉晶体管m6传输至下拉节点pd,从而为下拉节点pd放电,此时下拉节点pd的电位为低电位。在此基础上,第二输出晶体管m8关闭。其四,第一电源端vgh与输出端rout导通,第一电位的第一电源信号可以经开启的第一输出晶体管m7传输至输出端rout,从而为输出端rout充电,此时输出端rout的电位为高电位。例如,图16示出了移位寄存器单元在第四阶段4的等效电路图。

144.在第五阶段5,第一时钟端rck提供的第一时钟信号的电位和输入开启端rstv(即,输入端rin)提供的输入信号的电位均为高电位,第二时钟端rcb提供的第二时钟信号的电位为低电位。在此基础上,第一输入晶体管m1a,第二输入晶体管m1b,第一下拉控制晶体管m2,第二下拉控制晶体管m3均开启,第三下拉控制晶体管m4关闭。相应的,其一,第一电源端vgh和第二电源端vgl均与下拉控制节点pd_c导通,但是,因第一下拉控制晶体管m2的电阻大于第二下拉控制晶体管m3的电阻,故可以是第二电位的第二电源信号经开启的第二下拉控制晶体管m3传输至下拉控制节点pd_c,从而为下拉控制节点pd_c放电,此时下拉控制节点pd_c的电位为低电位。在此基础上,第一下拉晶体管m5关闭。其二,输入端rin与上拉节点pu导通,高电位的输入信号可以经开启的第一输入晶体管m1a和第二输入晶体管m1b传输至上拉节点pu,从而为上拉节点pu继续充电,使得上拉节点pu的电位保持为高电位。在此基础上,输出控制晶体管m1c,第一下拉晶体管m6和第一输出晶体管m7均开启。相应的,第一电源端vgh与串联节点cbc导通,第一电位的第一电源信号可以经开启的输入控制晶体管m1c继续传输至串联节点cbc。第二电源端vgl与下拉节点pd导通,第二电位的第二电源信号可以经开启的第二下拉晶体管m6传输至下拉节点pd,从而继续为下拉节点pd放电,此时下拉节点pd的电位为低电位。在此基础上,第二输出晶体管m8关闭。以及,第一电源端vgh与输出端rout导通,第一电位的第一电源信号可以经开启的第一输出晶体管m7传输至输出端rout,从而继续为输出端rout充电,此时输出端rout的电位为高电位。因第五阶段5各晶体管的开关状态与第三阶段3相同,故其等效电路图可以参考图15。

145.在第六阶段6,第一时钟端rck提供的第一时钟信号的电位为低电位,输入开启端rstv(即,输入端rin)提供的输入信号的电位和第二时钟端rcb提供的第二时钟信号的电位均为高电位。以及,上拉节点pu的电位在第二电容c2的作用下保持为第五阶段5的高电位。在此基础上,输入控制晶体管m1c,第二下拉控制晶体管m3,第三下拉控制晶体管m4,第二下拉晶体管m6和第一输出晶体管m7均开启。第一输入晶体管m1a,第二输入晶体管m1b和第一下拉控制晶体管m2均关闭。相应的,其一,第一电源端vgh与串联节点cbc导通,第一电位的第一电源信号可以经开启的输入控制晶体管m1c传输至串联节点cbc。其二,第二电源端vgl与下拉控制节点pd_c导通,第二电位的第二电源信号可以经开启的第二下拉控制晶体管m3和第三下拉控制晶体管m4传输至下拉控制节点pd_c,从而为下拉控制节点pd_c放电,此时下拉控制节点pd_c的电位为低电位。在此基础上,第一下拉晶体管m5关闭。其三,第二电源端vgl与下拉节点pd导通。第二电位的第二电源信号可以经开启的第二下拉晶体管m6传输至下拉节点pd,从而为下拉节点pd放电,此时下拉节点pd的电位为低电位。在此基础上,第二输出晶体管m8关闭。其四,第一电源端vgh与输出端rout导通,第一电位的第一电源信号可以经开启的第一输出晶体管m7传输至输出端rout,从而为输出端rout充电,此时输出端rout的电位为高电位。因第六阶段6各晶体管的开关状态与第四阶段4相同,故其等效电路图可以参考图16。

146.在第七阶段7,第一时钟端rck提供的第一时钟信号的电位和输入开启端rstv(即,输入端rin)提供的输入信号的电位均为高电位,第二时钟端rcb提供的第二时钟信号的电位为低电位。在此基础上,第一输入晶体管m1a,第二输入晶体管m1b,第一下拉控制晶体管m2,第二下拉控制晶体管m3均开启,第三下拉控制晶体管m4关闭。相应的,其一,第一电源端vgh和第二电源端vgl均与下拉控制节点pd_c导通,但是,因第一下拉控制晶体管m2的电阻大于第二下拉控制晶体管m3的电阻,故可以是第二电位的第二电源信号经开启的第二下拉控制晶体管m3传输至下拉控制节点pd_c,从而为下拉控制节点pd_c放电,此时下拉控制节点pd_c的电位为低电位。在此基础上,第一下拉晶体管m5关闭。其二,输入端rin与上拉节点pu导通,高电位的输入信号可以经开启的第一输入晶体管m1a和第二输入晶体管m1b传输至上拉节点pu,从而为上拉节点pu继续充电,使得上拉节点pu的电位保持为高电位。在此基础上,输出控制晶体管m1c,第一下拉晶体管m6和第一输出晶体管m7均开启。相应的,第一电源端vgh与串联节点cbc导通,第一电位的第一电源信号可以经开启的输入控制晶体管m1c继续传输至串联节点cbc。第二电源端vgl与下拉节点pd导通,第二电位的第二电源信号可以经开启的第二下拉晶体管m6传输至下拉节点pd,从而继续为下拉节点pd放电,此时下拉节点pd的电位为低电位。在此基础上,第二输出晶体管m8关闭。以及,第一电源端vgh与输出端rout导通,第一电位的第一电源信号可以经开启的第一输出晶体管m7传输至输出端rout,从而继续为输出端rout充电,此时输出端rout的电位为高电位。因第七阶段7各晶体管的开关状态与第五阶段5相同,第五阶段5各晶体管的开关状态与第三阶段3相同,故其等效电路图可以参考图15。

147.在第八阶段8,第一时钟端rck提供的第一时钟信号的电位和输入开启端rstv(即,输入端rin)提供的输入信号的电位均为低电位,第二时钟端rcb提供的第二时钟信号的电位为高电位。以及,上拉节点pu的电位在第二电容c2的作用下保持为第七阶段7的高电位。在此基础上,第一输入晶体管m1a,第二输入晶体管m1b,第一下拉控制晶体管m2和第二下拉控制晶体管m3均关闭,第三下拉控制晶体管m4,第二下拉晶体管m6和第一输出晶体管m7均开启。相应的,其一,第二电源端vgl与下拉控制节点pd_c导通,第二电位的第二电源信号经开启的第三下拉控制晶体管m4传输至下拉控制节点pd_c,从而为下拉控制节点pd_c放电,此时下拉控制节点pd_c的电位为低电位。在此基础上,第一下拉晶体管m5关闭。其二,第一电源端vgh与串联节点cbc导通,第一电位的第一电源信号可以经开启的输入控制晶体管m1c继续传输至串联节点cbc。其三,第二电源端vgl与下拉节点pd导通,第二电位的第二电源信号可以经开启的第二下拉晶体管m6传输至下拉节点pd,从而继续为下拉节点pd放电,此时下拉节点pd的电位为低电位。在此基础上,第二输出晶体管m8关闭。其四,第一电源端vgh与输出端rout导通,第一电位的第一电源信号可以经开启的第一输出晶体管m7传输至输出端rout,从而继续为输出端rout充电,此时输出端rout的电位为高电位。例如,图17示出了移位寄存器单元在第八阶段8的等效电路图。

148.在第九阶段9,第一时钟端rck提供的第一时钟信号的电位为高电位,输入开启端rstv(即,输入端rin)提供的输入信号的电位和第二时钟端rcb提供的第二时钟信号的电位均为低电位。在此基础上,第一输入晶体管m1a,第二输入晶体管m1b和第一下拉控制晶体管m2均开启,第二下拉控制晶体管m3和第三下拉控制晶体管m4均关闭。相应的,其一,输入端rin与上拉节点pu导通,低电位的输入信号可以经开启的第一输入晶体管m1a和第二输入晶

体管m1b传输至上拉节点pu,从而为上拉节点pu放电,此时上拉节点pu的电位为低电位。在此基础上,第二下拉晶体管m6,第一输出晶体管m7和输入控制晶体管m1c均关闭。其二,第一电源端vgh与下拉控制节点pd_c导通,高电位的第一电源信号可以经开启的第一下拉控制晶体管m2传输至下拉控制节点pd_c,从而为下拉控制节点pd_c充电,此时下拉控制节点pd_c的电位为高电位。在此基础上,第一下拉晶体管m5开启,第一电源端vgh与下拉节点pd导通。第一电位的第一电源信号还可以经开启的第一下拉晶体管m5传输至下拉节点pd,从而为下拉节点pd充电,此时下拉节点pd的电位为高电位。在此基础上,第二输出晶体管m8开启。相应的,第二电源端vgh与输出端rout导通,第二电位的第二电源信号可以经开启的第二输出晶体管m8传输至输出端rout,从而为输出端rout放电,此时输出端rout的电位为低电位。此外,在第一电容c1的自举作用下,下拉节点pd可以可靠处于高电位。因第九阶段9各晶体管的开关状态与第一阶段1相同,故其等效电路图可以参考图13。

149.此外,在第九阶段9,受第二电容c2的自举作用影响,下拉控制节点pd_c的电位可以被充电至较高电压。此时,下拉控制节点pd_c的电位变化值δv

pd_c

可以满足:δv

pd_c

=c10/(cgsm5+c10+c

pd_c

)*δv

pd

;c10是指第一电容c1的容值,cgsm5是指第一下拉晶体管m5的寄生电容,c

pd_c

是指除第一电容c1和第一下拉晶体管m5的寄生电容外,下拉控制节点pd_c处的寄生电容值,δv

pd

是指下拉节点pd的电位变化值。这里的变化值是指当前阶段与前一阶段比较的变化值。

150.在第十阶段10,第一时钟端rck提供的第一时钟信号的电位和输入开启端rstv(即,输入端rin)提供的输入信号的电位均为低电位,第二时钟端rcb提供的第二时钟信号的电位为高电位。以及,上拉节点pu的电位在第二电容c2的作用下保持为第九阶段9的低电位。下拉节点pd的电位在第一电容c1的作用下保持为第九阶段9的高电位。在此基础上,第一输入晶体管m1a,第二输入晶体管m1b,第一下拉控制晶体管m2,第二下拉控制晶体管m3,第一输出晶体管m7,输出控制晶体管m1c和第二下拉晶体管m6均关闭,第三下拉控制晶体管m4和第二输出晶体管m8均开启。相应的,其一,第二电源端vgl与下拉控制节点pd_c导通,低电位的第二电源信号可以经开启的第三下拉控制晶体管m4传输至下拉控制节点pd_c,从而为下拉控制节点pd_c放电,此时下拉控制节点pd_c的电位为低电位。在此基础上,第一下拉晶体管m5关闭。其二,第二电源端vgh与输出端rout导通,第二电位的第二电源信号可以经开启的第二输出晶体管m8传输至输出端rout,从而继续为输出端rout放电,此时输出端rout的电位为低电位。例如,图18示出了移位寄存器单元在第十阶段10的等效电路图。

151.其中,图13至图18中,“虚线标识的

×”

用于指示晶体管关断。此外,图13至图18中还分别标识了高电位和低电位的信号流向。在图12基础上,图19示出了一种信号仿真图,且该仿真图中示出了级联的8个移位寄存器单元00的输出端rout的时序。横坐标是指时间,单位为微秒(μs),横坐标是指电压,单位为伏特(v)。此外,需要说明的是,步骤1101的第一阶段可以是指上述实施例记载的第一阶段1,第二阶段可以是指上述实施例记载的第三阶段3。

152.综上所述,本公开实施例提供了一种移位寄存器单元的驱动方法。该方法中,移位寄存器单元包括的输入电路能够控制输入端与上拉节点的通断,以控制上拉节点的电位。下拉电路能够控制第一电源端和第二电源端与下拉节点的通断,以控制下拉节点的电位。输出电路能够响应于上拉节点的电位,控制第一电源端与输出端的通断,且能够响应于下

拉节点的电位,控制第二电源端与输出端的通断,从而向输出端传输第一电位的第一电源信号和第二电位的第二电源信号,输出端用于与复位信号端耦接。如此,能够基于发光控制信号灵活设置输入端提供的输入信号,使得通过该移位寄存器单元向像素电路的复位信号端可靠传输复位信号,从而使得像素电路可靠驱动发光元件发光。

153.图20是本公开实施例提供的一种复位驱动电路的结构示意图。如图20所示,该复位驱动电路包括:至少两个级联的如上述附图所示的移位寄存器单元00。并且,如上述实施例记载,第一级移位寄存器单元00的输入端rin可以与复位开启端rstv耦接,除第一级移位寄存器单元00外的其他级移位寄存器单元00中,每一级移位寄存器单元00的输入端rin可以均与级联的上一级移位寄存器单元00的输出端rout耦接。

154.图21是本公开实施例提供的一种显示装置的结构示意图。如图21所示,该显示装置包括:显示面板100,以及如图20所示的复位驱动电路000。

155.其中,显示面板100可以包括多个像素,像素可以包括如图2或图3所示的像素电路p1和发光元件l1,像素电路p1可以分别与复位信号端rst1(n)、发光控制端em(n)和发光元件l1耦接,并可以用于响应于来自复位信号端rst1(n)的复位信号和来自发光控制端em(n)的发光控制信号,驱动发光元件l1发光。复位驱动电路000可以与复位信号端rst1(n)耦接,并用于为复位信号端rst1(n)提供复位信号。

156.可选的,如上述实施例记载,像素电路p1可以包括多个晶体管,且该多个晶体管可以均为n型氧化物晶体管。

157.可选的,该显示装置可以为:oled显示装置、电子纸、手机、平板电脑、电视机、显示器、笔记本电脑或导航仪等任何具有显示功能的产品或部件。

158.应当理解的是,本公开的实施方式部分使用的术语仅用于对本公开的实施例进行解释,而非旨在限定本公开。除非另作定义,本公开的实施方式使用的技术术语或者科学术语应当为本公开所属领域内具有一般技能的人士所理解的通常意义。

159.如,本公开专利申请说明书以及权利要求书中使用的“第一”、“第二”或者“第三”以及类似的词语并不表示任何顺序、数量或者重要性,而只是用来区分不同的组成部分。

160.同样,“一个”或者“一”等类似词语也不表示数量限制,而是表示存在至少一个。

[0161]“包括”或者“包含”等类似的词语意指出现在“包括”或者“包含”前面的元件或者物件涵盖出现在“包括”或者“包含”后面列举的元件或者物件及其等同,并不排除其他元件或者物件。

[0162]“上”、“下”、“左”或者“右”等仅用于表示相对位置关系,当被描述对象的绝对位置改变后,则所述相对位置关系也可能相应地改变。“连接”或者“耦接”是指电连接。

[0163]“和/或”,表示可以存在三种关系,例如,a和/或b,可以表示:单独存在a,同时存在a和b,单独存在b这三种情况。字符“/”一般表示前后关联对象是一种“或”的关系。

[0164]

所属领域的技术人员可以清楚地了解到,为描述的方便和简洁,上述描述的复位驱动电路、移位寄存器单元、各电路和各子电路的具体工作过程,可以参考方法实施例中的对应过程,在此不再赘述。

[0165]

以上所述仅为本公开的可选实施例,并不用以限制本公开,凡在本公开的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本公开的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1