半导体存储器件的制作方法

本技术涉及半导体,尤指一种半导体存储器件。

背景技术:

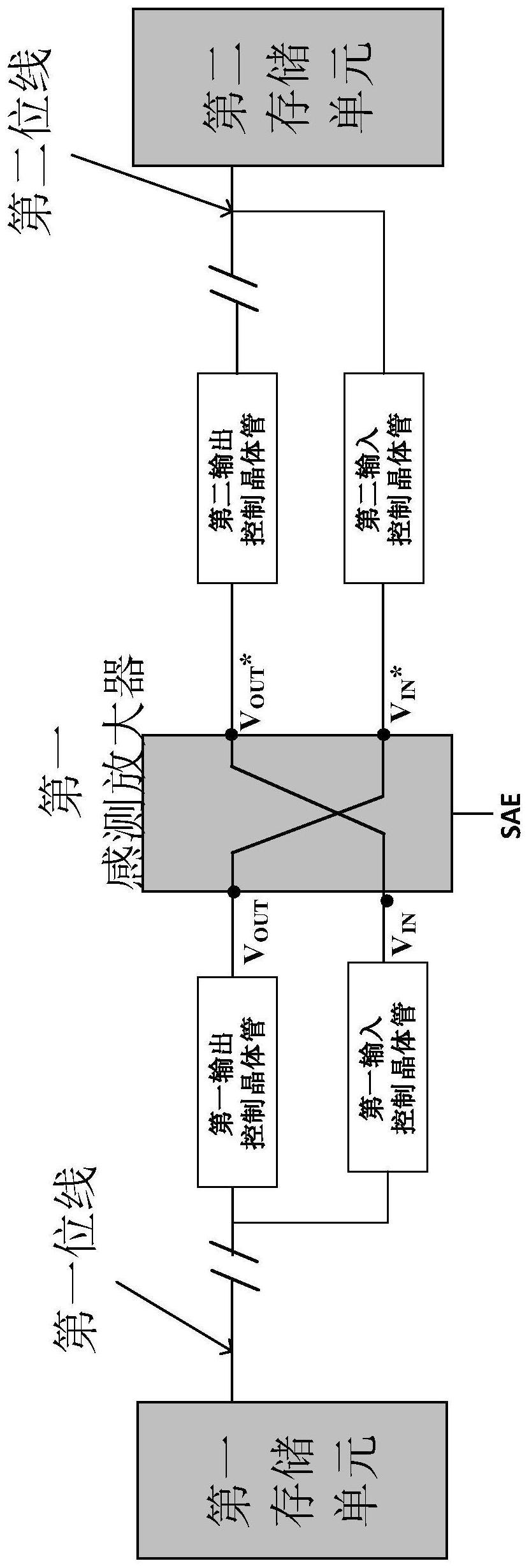

1、用于放大输入数据的放大器电路用在包括通信领域、半导体领域等的各种领域中。例如,dram的半导体存储器件利用位线感测放大器来放大存储单元数据。具体地,如果字线被激活,则与字线连接的多个存储单元的数据被传送到位线,位线感测放大器感测并放大位线对中所包括的两个位线之间的电压差。

2、在1t1c技术中,如图1所示,数据访问是通过感测放大器sa(交叉耦合反相器)进行的。存储单元的电容中存储的数据与感测放大器中产生的信号相同,这样,i/o数据可以通过由列选择线控制的开关晶体管与感测放大器中的输入输出端连接。并且,写操作的输入数据不需要全摆幅信号,因为感测放大器可以帮助产生和放大部分摆幅信号,这将有助于提高写入速度和节省消耗。

3、在2t0c技术中,因为存储在sn(如图2所示)中的数据与在位线bl中产生的信号相反(例如,对于高电平,因为读取晶体管导通,所以bl将为低),这带来了许多访问问题。例如,bl不能连接到sa的输出(与1t1c中的不同)。此外,由于通常需要全摆幅数据来进行写操作,这将降低写入速度,还会导致功耗问题。

技术实现思路

1、本技术提供了一种半导体存储器件,能够实现对2t0c存储单元的存储数据进行放大。

2、本技术提供了一种半导体存储器件,包括:

3、第一位线,所述第一位线与第一存储单元连接;

4、第二位线,所述第二位线与第二存储单元连接;

5、第一感测放大器,所述第一感测放大器设置为当感测到差分输入信号时,放大所述差分输入信号;包括第一输入端、第二输入端、第一输出端和第二输出端,所述第一输入端与所述第二输出端连接,所述第二输入端与所述第一输出端连接;

6、第一输入控制晶体管,设置为控制第一位线上的信号输入或不输入到所述第一感测放大器的第一输入端;

7、第二输入控制晶体管,设置为控制第二位线上的信号输入或不输入到所述第一感测放大器的第二输入端;

8、第一输出控制晶体管,设置为控制第一感测放大器的第一输出端的信号分别输出或不输出到第一位线;

9、第二输出控制晶体管,设置为控制第一感测放大器的第二输出端的信号输出或不输出到第二位线;

10、所述第一存储单元和所述第二存储单元为2t0c存储单元。

11、在一种示例性的实施例中,所述第一输入控制晶体管的第一极与第一位线连接,所述第一输入控制晶体管的第二极与所述第一感测放大器的第一输入端连接;所述第一输出控制晶体管的第一极与所述第一位线连接,所述第一输出控制晶体管的第二极与所述第一感测放大器的第一输出端连接;所述第一输入控制晶体管的栅极与第一输入控制端连接;所述第一输出控制晶体管的栅极与第一输出控制端连接;

12、所述第二输入控制晶体管的第一极与第二位线连接,所述第二输入控制晶体管的第二极与所述第一感测放大器的第二输入端连接;所述第二输出控制晶体管的第一端与所述第二位线连接,所述第二输出控制晶体管的第二极与所述第一感测放大器的第二输出端连接;所述第二输入控制晶体管的栅极与第二输入控制端连接;所述第二输出控制晶体管的栅极与第二输出控制端连接。

13、在一种示例性的实施例中,所述第一感测放大器包括第一pmos晶体管、第二pmos晶体管、第一nmos晶体管、第二nmos晶体管和第一接地控制晶体管;

14、第一pmos晶体管的第二极和第一nmos晶体管的第一极连接;第二pmos晶体管的第二极和第二nmos晶体管的第一极连接;第一pmos晶体管的栅极与所述第二pmos晶体管的第二极连接,第二pmos晶体管的栅极与所述第一pmos晶体管的第二极连接;第一pmos晶体管和第二pmos晶体管的第一极连接后接入vdd;所述第一nmos晶体管和第二nmos晶体管的第二极连接后通过第一接地控制晶体管接地;

15、第一nmos晶体管的栅极作为所述第一感测放大器的第一输入端;第二nmos晶体管的栅极作为所述第一感测放大器的第二输入端;第一pmos晶体管的第二极作为所述第一感测放大器的第一输出端;第二pmos晶体管的第二极作为所述第一感测放大器的第二输出端。

16、在一种示例性的实施例中,所述第一感测放大器包括第三pmos晶体管、第四pmos晶体管、第三nmos晶体管、第四nmos晶体管、第五nmos晶体管、第六nmos晶体管和第二接地控制晶体管;

17、所述第三pmos晶体管、第三nmos晶体管、第四nmos晶体管通过各自的第一极或第二极依次串联;所述第三pmos晶体管和第三nmos晶体管的栅极连接;

18、所述第四pmos晶体管、第五nmos晶体管、第六nmos晶体管通过各自的第一极或第二极依次串联;所述第四pmos晶体管和第五nmos晶体管的栅极连接;

19、第三pmos晶体管和第四pmos晶体管的第一极连接后接入vdd;所述第四nmos晶体管和第六nmos晶体管的第二极连接后通过第二接地控制晶体管接地;

20、所述第四nmos晶体管的栅极作为所述第一感测放大器的第一输入端,所述第六nmos晶体管的栅极作为所述第一感测放大器的第二输入端;所述第三pmos晶体管的第二极与所述第四pmos晶体管的栅极连接作为所述第一感测放大器的第一输出端;所述第四pmos晶体管的第二极与所述第三pmos晶体管的栅极连接作为所述第一感测放大器的第二输出端。

21、在一种示例性的实施例中,还包括与每个存储单元对应的第一列选择单元;每个第一列选择单元包括第一列选择晶体管;每个第一列选择晶体管的第一极与相应的i/o端连接;每个第一列选择晶体管的第二极与所述第一感测放大器相应的输出端连接;每个第一列选择晶体管的栅极与相应的列选择线连接。

22、在一种示例性的实施例中,还包括与第一存储单元对应的第一重启单元和第一预充单元、与第二存储单元对应的第二重启单元和第二预充单元;

23、每个重启单元包括重启晶体管;重启晶体管的第一极分别与对应的存储单元对应的位线连接;每个重启晶体管的第二极与相应的维持电源连接;每个重启晶体管的栅极与相应的重启信号端连接;

24、每个预充单元包括预充晶体管;预充晶体管的第一极与对应的存储单元对应的位线连接;预充晶体管的第二极与相应的预充电源连接;预充晶体管的栅极与相应的预充信号端连接。

25、本技术提供了一种半导体存储器件,包括:

26、第一读位线和第一写位线,所述第一读位线设置为与第三存储单元连接的读晶体管连接;所述第一写位线设置为与第三存储单元的写晶体管连接;

27、第二读位线和第二写位线,所述第二读位线设置为与第四存储单元连接的读晶体管连接;所述第二写位线设置为与第四存储单元的写晶体管连接;

28、第二感测放大器;所述第二感测放大器设置为当感测到差分输入信号时,放大所述差分输入信号;包括第三输入端、第四输入端、第三输出端和第四输出端,所述第三输入端与所述第四输出端连接,所述第四输入端与所述第三输出端连接;

29、所述第三输入端与所述第一读位线连接,所述第三输出端与所述第一写位线连接,所述第四输入端与所述第二读位线连接,所述第四输出端与所述第二写位线连接;

30、第三输入控制晶体管,设置为控制第一读位线上的信号输入或不输入到所述第二感测放大器的第三输入端;

31、第三输出控制晶体管,设置为控制第二感测放大器的第三输出端的信号输出或不输出到第一写位线;

32、第四输入控制晶体管,设置为控制第二读位线上的信号输入或不输入到所述第二感测放大器的第四输入端;

33、第四输出控制晶体管,设置为控制第二感测放大器的第四输出端的信号输出或不输出到第二写位线;

34、所述第三存储单元和所述第四存储单元为2t0c存储单元。

35、在一种示例性的实施例中,所述第三输入控制晶体管的第一极与所述第一读位线连接;所述第三输入控制晶体管的第二极与所述第二感测放大器的第三输入端连接;所述第三输入控制晶体管的栅极与第三输入控制端连接;

36、所述第三输出控制晶体管的第一极与所述第一写位线连接;所述第三输出控制晶体管的第二极与所述第二感测放大器的第三输出端连接;所述第三输出控制晶体管的栅极与第三输出控制端连接;

37、所述第四输入控制晶体管的第一极与所述第二感测放大器的第四输入端连接;所述第四输入控制晶体管的第二极与所述第二读位线连接;所述第四输入控制晶体管的栅极与第四输入控制端连接;

38、所述第四输出控制晶体管的第一极与所述第二感测放大器的第四输出端连接;所述第四输出控制晶体管的第二极与所述第二写位线连接;所述第四输出控制晶体管的栅极与第四输出控制端连接。

39、在一种示例性的实施例中,所述第二感测放大器还包括第七pmos晶体管、第八pmos晶体管、第七nmos晶体管、第八nmos晶体管和第三接地控制晶体管;

40、第七pmos晶体管的第二极和第七nmos晶体管的第一极连接;第八pmos晶体管的第二极和第八nmos晶体管的第一极连接;第七pmos晶体管的栅极与所述第八pmos晶体管的第二极连接,第八pmos晶体管的栅极与所述第七pmos晶体管的第二极连接;第七pmos晶体管和第八pmos晶体管的第一极连接后接入vdd;所述第七nmos晶体管和第八nmos晶体管的第二极连接后通过第一接地控制晶体管接地;

41、第七nmos晶体管的栅极作为所述第二感测放大器的第三输入端;第八nmos晶体管的栅极作为所述第二感测放大器的第四输入端;第七pmos晶体管的第二极作为所述第二感测放大器的第三输出端;第八pmos晶体管的第二极作为所述第二感测放大器的第四输出端。

42、在一种示例性的实施例中,所述第二感测放大器还包括第九pmos晶体管、第十pmos晶体管、第九nmos晶体管、第十nmos晶体管、第十一nmos晶体管、第十二nmos晶体管和第四接地控制晶体管;

43、所述第九pmos晶体管、第九nmos晶体管、第十nmos晶体管通过各自的第一极或第二极依次串联;所述第九pmos晶体管和第九nmos晶体管的栅极连接;

44、所述第十pmos晶体管、第十一nmos晶体管、第十二nmos晶体管通过各自的第一极或第二极依次串联;所述第十pmos晶体管和第十一nmos晶体管的栅极连接;

45、第九pmos晶体管和第十pmos晶体管的第一极连接后接入vdd;所述第十nmos晶体管和第十二nmos晶体管的第二极连接后通过第四接地控制晶体管接地;

46、所述第十nmos晶体管的栅极作为所述第二感测放大器的第三输入端,所述第十二nmos晶体管的栅极作为所述第二感测放大器的第四输入端;所述第九pmos晶体管的第二极与所述第十pmos晶体管的栅极连接作为所述第二感测放大器的第三输出端;所述第十pmos晶体管的第二极与所述第九pmos晶体管的栅极连接作为所述第二感测放大器的第四输出端。

47、在一种示例性的实施例中,还包括与每个存储单元对应的第二列选择单元;每个第二列选择单元包括列选择晶体管;每个列选择晶体管的第一极与相应的i/o端连接;每个列选择晶体管的第二极与所述第二感测放大器相应的输出端连接;每个列选择晶体管的栅极与相应的列选择线连接。

48、在一种示例性的实施例中,还包括与第一读位线对应的第三重启单元和第三预充单元、与第一写位线对应的第四重启单元和第四预充单元、与第二读位线对应的第五重启单元和第五预充单元、以及与第二写位线对应的第六重启单元和第六预充单元;

49、每个重启单元包括重启晶体管;重启晶体管的第一极分别与对应的存储单元对应的读位线连接;重启晶体管的第二极与相应的维持电源连接;重启晶体管的栅极与相应的重启信号端连接;

50、每个预充电单元包括预充晶体管;预充晶体管的第一极与对应的存储单元对应的读位线连接;预充晶体管的第二极与相应的预充电源连接;预充晶体管的栅极与相应的预充信号端连接。

51、本技术的其它特征和优点将在随后的说明书中阐述,并且,部分地从说明书中变得显而易见,或者通过实施本技术而了解。本技术的其他优点可通过在说明书以及附图中所描述的方案来实现和获得。

- 还没有人留言评论。精彩留言会获得点赞!