自适应控制电路的制作方法

本发明涉及控制电路,更具体地,涉及静态随机存取存储器(static randomaccess memory,sram)的自适应控制电路。

背景技术:

1、在传统设计中,如果sram(静态随机存取存储器)的控制电路由可变电源电压供电,则控制电路的相应读取余量(read margin)可能不足。此外,控制电路可能会受到缓慢操作速度的影响。因此,需要提出一种新颖的方案来解决现有技术的问题。

技术实现思路

1、有鉴于此,本发明提供了自适应控制电路用于静态随机存取存储器(sram)。

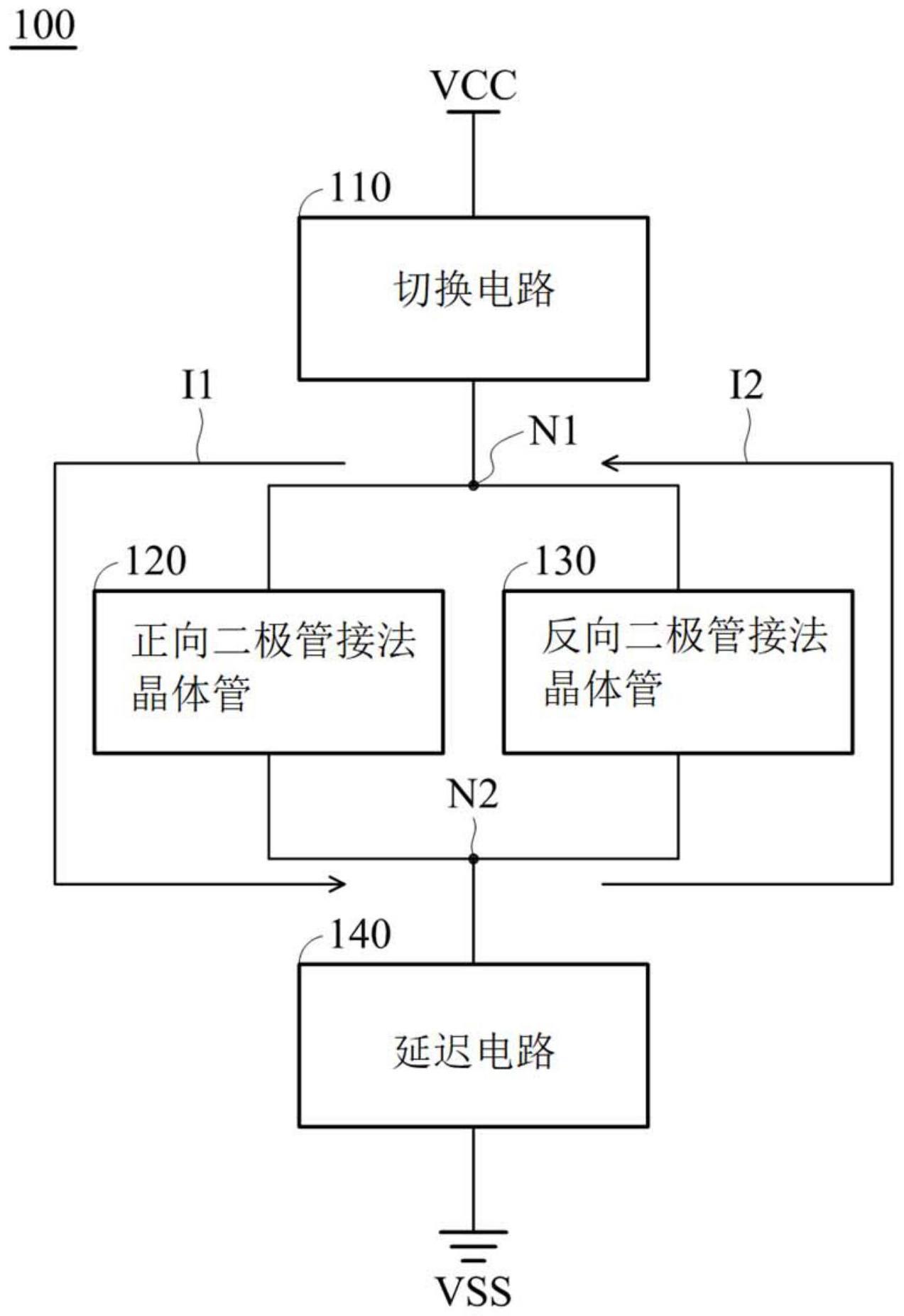

2、在示例性实施例中,用于sram的自适应控制电路包括切换电路、正向二极管接法晶体管、反向二极管接法晶体管和第一延迟电路。切换电路由电源电压供电并耦接至第一节点。反向二极管接法晶体管和正向二极管接法晶体管并联耦接在第一节点和第二节点之间。第一延迟电路耦接于第二节点与接地电压之间。

3、本发明的自适应控制电路不仅提供了可接受的操作速度,而且还保持了足够的读取余量。

4、在阅读了在各种附图示出的优选实施例的以下详细描述之后,本发明的这些和其他目的对于本领域普通技术人员无疑将变得显而易见。

技术特征:

1.一种自适应控制电路,用于静态随机存取存储器sram,所述自适应控制电路包括:

2.如权利要求1所述的自适应控制电路,其中,当所述电源电压高于或等于阈值电压时,所述正向二极管接法晶体管被启用。

3.如权利要求1所述的自适应控制电路,其中,所述切换电路包括:

4.如权利要求3所述的自适应控制电路,其中,所述第一晶体管由p型金属氧化物半导体场效应晶体管pmosfet来实现。

5.如权利要求1所述的自适应控制电路,其中,所述正向二极管接法晶体管为第二晶体管,所述第二晶体管具有耦接至所述第一节点的控制端、耦接至所述第二节点的第一端、以及耦接至所述第一节点的第二端。

6.如权利要求5所述的自适应控制电路,其中,所述第二晶体管由n型金属氧化物半导体场效应晶体管nmosfet来实现。

7.如权利要求1所述的自适应控制电路,其中,所述反向二极管接法晶体管为第三晶体管,所述第三晶体管具有耦接所述第二节点的控制端、耦接所述第一节点的第一端、以及耦接所述第二节点的第二端。

8.如权利要求7所述的自适应控制电路,其中,所述第三晶体管由nmosfet实现。

9.如权利要求1所述的自适应控制电路,其中,所述第一延迟电路为电容元件或电阻元件。

10.如权利要求1所述的自适应控制电路,其中,所述第一延迟电路包括:

11.如权利要求10所述的自适应控制电路,其中,所述第四晶体管由nmosfet实现。

12.如权利要求3所述的自适应控制电路,其中,所述切换电路还包括:

13.如权利要求12所述的自适应控制电路,其中,所述第五晶体管由nmosfet实现。

14.如权利要求1所述的自适应控制电路,还包括:

15.如权利要求14所述的自适应控制电路,其中,所述第二延迟电路包括:

16.如权利要求15所述的自适应控制电路,其中,所述第六晶体管由nmosfet实现。

17.如权利要求14所述的自适应控制电路,还包括:

18.如权利要求17所述的自适应控制电路,其中,所述第三延迟电路包括:

19.如权利要求18所述的自适应控制电路,其中,所述第七晶体管由nmosfet实现。

20.如权利要求1所述的自适应控制电路,还包括:

技术总结

本发明提供了一种静态随机存取存储器(SRAM)的自适应控制电路,包括切换电路、正向二极管接法晶体管、反向二极管接法晶体管和第一延迟电路。切换电路由电源电压供电并耦接至第一节点。反向二极管接法晶体管和正向二极管接法晶体管并联耦接在第一节点和第二节点之间。第一延迟电路耦接于第二节点与接地电压之间。本发明的自适应控制电路不仅提供了可接受的操作速度,而且还保持了足够的读取余量。

技术研发人员:王道平

受保护的技术使用者:联发科技股份有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!