存储电路、存储芯片及电子设备的制作方法

本技术实施例涉及静态随机存取存储器,尤其涉及一种存储电路、存储芯片及电子设备。

背景技术:

1、静态随机存取存储器(static random access memory,sram)是随机存取存储器的一种,其不需要刷新电路即能保存它内部存储的数据,具有较高的性能,可广泛应用于芯片及电子设备生产过程中。

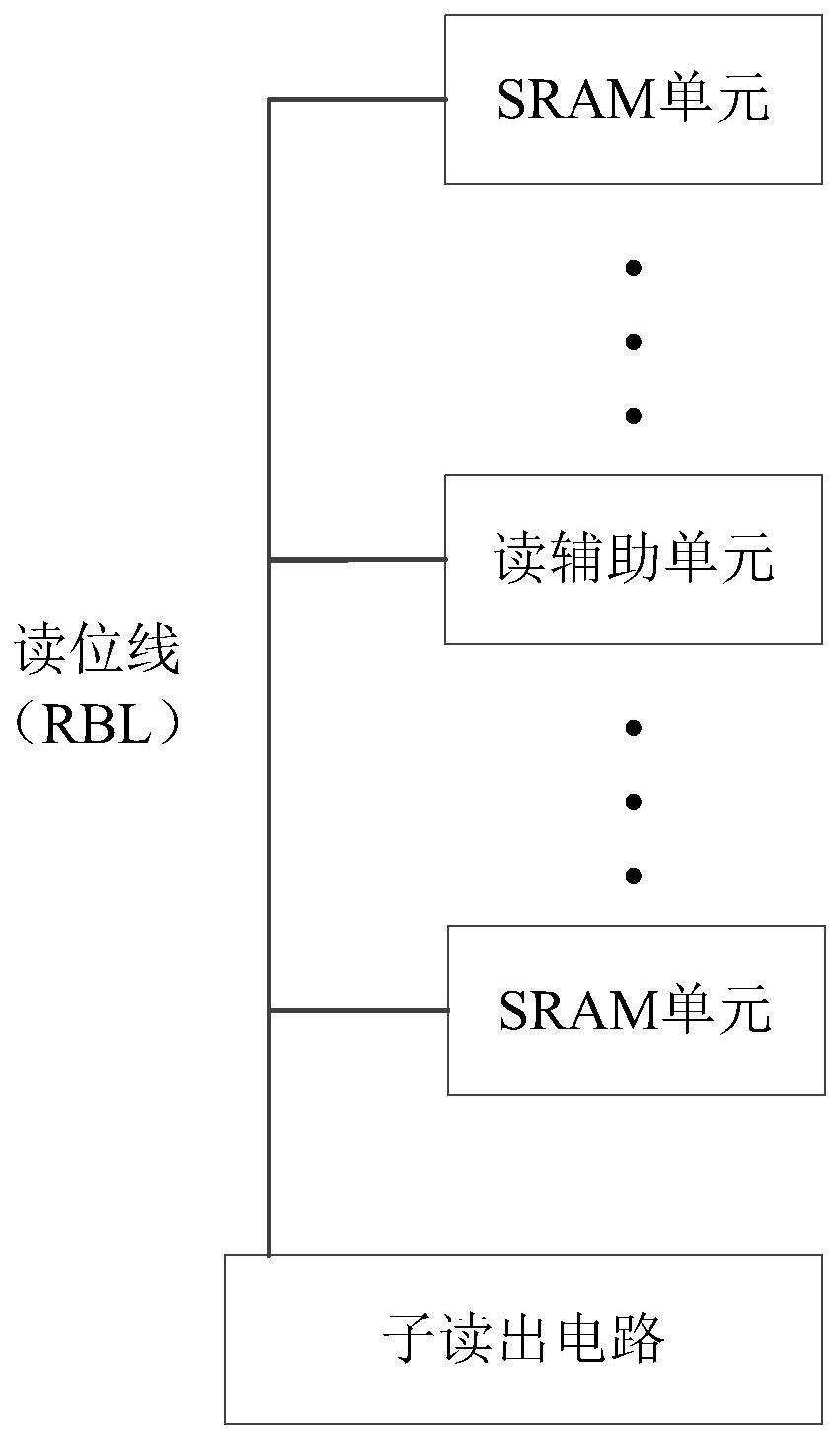

2、图1为现有技术中的一种sram存储电路的示意图。请参见图1,该存储电路包括子读出电路、读位线rbl和多个sram单元。读位线rbl分别与子读出电路和多个sram单元连接;子读出电路可以用于通过多个sram单元进行读操作。在图1中,当sram单元中存储的为1,且需要从该sram单元中读1时,读位线rbl需保持在高电位。然而,与读位线相连的多个sram单元中存储的可能是0,这些存储0的sram单元的读端口电路将产生漏电流。当存储0的sram单元足够多时,漏电流叠加将导致读位线rbl由高电位逐渐下拉至中间电位,从而导致子读出电路从存储1的sram单元读1操作时失败。

3、在相关技术中,可以通过在存储电路外部增加辅助电路的形式,使得读位线始终稳定在高电位,以此来提高读1操作的稳定性。例如,可以通过在存储电路上串联多个n型金属氧化物半导体(n-metal-oxide-semiconductor,nmos),来减弱漏电流现象,从而使读位线稳定在高电位。然而,在上述过程中,随着辅助电路的增加,存储电路的驱动能力减弱,尽管可以提高读1操作的稳定性,但放慢了读0操作的速度,且辅助单元增加将导致边缘单元也随之增加,从而导致存储电路的面积开销过大。

技术实现思路

1、本技术实施例提供一种存储电路、存储芯片及电子设备,通过设置读辅助单元可以调节读位线的电位,提高了读1操作的成功率和加快了读0操作的速度。并且,读辅助单元为对sram单元的电路连接关系进行更新得到的,读辅助单元与sram版图规则兼容,无需在读辅助单元与sram单元之间插入边缘单元,避免了存储电路的面积开销过大。

2、第一方面,本技术实施例提供一种存储电路,包括子读出电路、读位线、至少一个读辅助单元、以及多个静态随机存取存储器sram单元,其中,

3、所述读位线分别与所述子读出电路、所述至少一个读辅助单元和所述多个sram单元连接;

4、所述子读出电路用于通过所述多个sram单元进行读操作;

5、所述读辅助单元为对所述sram单元的电路连接关系进行更新得到的,所述读辅助单元用于调节所述读位线的电位。

6、在一种可能的实施方式中,所述读辅助单元用于上拉所述读位线的电位,或者,所述读辅助单元用于下拉所述读位线的电位。

7、在一种可能的实施方式中,所述读辅助单元用于上拉所述读位线的电位;所述读辅助单元包括第一单元,所述第一单元包括第一开关单元和第二开关单元,其中,

8、所述第一开关单元和所述第二开关单元串联;

9、所述第一开关单元与所述读位线连接,所述第一开关单元用于还与读字线连接;

10、所述第二开关单元还分别用于与所述读字线和第一电源连接,所述第一电源提供的电压大于0。

11、在一种可能的实施方式中,所述第一开关单元为第一nmos管,所述第二开关单元为第二nmos管,其中,

12、所述第一nmos管的栅极用于与所述读字线连接,所述第一nmos管的源级与所述读位线连接,所述第一nmos管的漏级与所述第二nmos管的漏级连接;

13、所述第二nmos管的栅极用于与所述读字线连接,所述第二nmos管的源级用于与所述第一电源连接。

14、在一种可能的实施方式中,所述读辅助单元还包括第二单元,其中,所述第二单元包括第三nmos管、第四nmos管、第五nmos管、第六nmos管、第一pmos管和第二pmos管,其中,

15、所述第一pmos管的源级和所述第二pmos管的源级分别与第二电源连接;

16、所述第一pmos管的栅极、所述第三nmos管的栅极、所述第二pmos管的漏极、所述第四nmos管的漏极和所述第五nmos管的漏级连接;

17、所述第一pmos管的漏级、所述第三nmos管的漏级和所述第六nmos管的漏级连接;

18、所述第六nmos管的源级用于与第一写位线连接,所述第六nmos管的栅极用于与第三电源连接;

19、所述第二pmos管的栅极、所述第四nmos管的栅极、所述第一pmos管的漏极、所述第三nmos管的漏极和所述第六nmos管的漏级连接;

20、所述第五nmos管的栅极用于与第三电源连接,所述第五nmos管的源级用于与第二写位线连接;

21、所述第三nmos管的源级和所述第四nmos管的源级分别与第三电源连接。

22、在一种可能的实施方式中,所述读辅助单元用于下拉所述读位线的电位;所述读辅助单元包括第一单元和第二单元,所述第一单元包括第一开关单元和第二开关单元,其中,

23、所述第一开关单元和所述第二开关单元串联;

24、所述第一开关单元与所述读位线连接,所述第一开关单元还用于与读字线连接,或者,所述第一开关单元还用于与所述第二单元连接;

25、所述第二开关单元还分别用于与所述第二单元和第三电源连接。

26、在一种可能的实施方式中,所述第一开关单元还用于与读字线连接;所述第一开关单元为第一nmos管,所述第二开关单元为第二nmos管,其中,

27、所述第一nmos管的栅极用于与所述读字线连接,所述第一nmos管的源级与所述读位线连接,所述第一nmos管的漏级与所述第二nmos管的漏级连接;

28、所述第二nmos管的栅极用于与所述第二单元连接,所述第二nmos管的源级用于与所述第三电源连接。

29、在一种可能的实施方式中,所述第一开关单元还用于与所述第二单元连接;所述第一开关单元为第一nmos管,所述第二开关单元为第二nmos管,其中,

30、所述第一nmos管的栅极分别用于与所述第二nmos管的栅极和所述第二单元连接,所述第一nmos管的源级与所述读位线连接,所述第一nmos管的漏级与所述第二nmos管的漏级连接;

31、所述第二nmos管的栅极用于与所述第二单元连接,所述第二nmos管的源级用于与所述第三电源连接。

32、在一种可能的实施方式中,所述第二单元包括第三nmos管、第四nmos管、第五nmos管、第六nmos管、第一pmos管和第二pmos管,其中,

33、所述第一pmos管的源级和所述第二pmos管的源级分别与第二电源连接;

34、所述第一pmos管的栅极、所述第三nmos管的栅极、所述第二pmos管的漏极、所述第四nmos管的漏极、所述第五nmos管的漏级、以及第二nmos管的栅极连接;

35、所述第一pmos管的漏级、所述第三nmos管的漏级和所述第六nmos管的漏级连接;

36、所述第六nmos管的源级用于与第一写位线连接,所述第六nmos管的栅极用于与第三电源连接;

37、所述第二pmos管的栅极、所述第四nmos管的栅极分别与读位线连接;

38、所述第五nmos管的栅极用于与第三电源连接,所述第五nmos管的源级用于与第二写位线连接;

39、所述第三nmos管的源级和所述第四nmos管的源级分别与第三电源连接。

40、在一种可能的实施方式中,所述存储电路还包括所述子读出电路对应的第一边缘单元、以及第二边缘单元,其中,

41、所述第一边缘单元与所述子读出电路连接,所述第一边缘单元用于隔离所述子读出电路与所述子读出电路相邻的sram单元;

42、所述第二边缘单元与设置在所述存储电路边缘的sram单元连接。

43、在一种可能的实施方式中,所述至少一个读辅助单元的数量为1。

44、第二方面,本技术实施例提供一种存储芯片,所述存储芯片中包括如第一方面所述存储电路。

45、第三方面,本技术实施例提供一种电子设备,所述电子设备中包括如第二方面所述的存储芯片。

46、本技术实施例提供的存储电路、存储芯片及电子设备,包括子读出电路、读位线、至少一个读辅助单元、以及多个sram单元,其中,读位线分别与子读出单元、至少一个读辅助单元和多个sram单元连接;子读出电路用于通过多个sram单元进行读操作;读辅助单元为对sram单元的电路连接关系进行更新得到的,读辅助单元用于调节读位线的电位。在上述存储电路中,当需要在sram单元中进行读1操作时,通过读辅助单元来上拉读位线的电位,可以避免由于读位线相连的其它存储0的sram单元将读位线的电位下拉的过低,提高了读1操作的成功率;当需要在sram单元中进行读0操作时,通过读辅助单元来下拉读位线的电位,可以加快读位线电位下拉的速度,从而加快了读0的速度。并且,读辅助单元为对sram单元的电路连接关系进行更新得到的,读辅助单元与sram版图规则兼容,无需在读辅助单元与sram单元之间插入边缘单元,避免了存储电路的面积开销过大。

- 还没有人留言评论。精彩留言会获得点赞!