用于提供在非易失性存储器系统中用于擦除或编程操作的高电压的收发器的制作方法

公开了用于提供在非易失性存储器系统中用于擦除或编程操作的高电压的收发器的多个实施方案。

背景技术:

1、非易失性存储器是众所周知的。例如,美国专利5,029,130(″’130专利″),其以引用方式并入本文,公开了分裂栅非易失性存储器单元的阵列,它是一种闪存存储器单元。此类存储器单元110在图1中示出。每个存储器单元110包括形成于半导体衬底12中的源极区14和漏极区16,其间具有沟道区18。浮栅20形成在沟道区18的第一部分上方并且与其绝缘(并且控制其电导率),并且形成在源极区14的一部分上方。字线端子22(其通常被耦接到字线)具有设置在沟道区18的第二部分上方并且与其绝缘(并且控制其电导率)的第一部分,以及向上延伸并且位于浮栅20上方的第二部分。浮栅20和字线端子22通过栅极氧化物与衬底12绝缘。位线24耦接到漏极区16。

2、通过将高的正电压置于字线端子22上来对存储器单元110进行擦除(其中电子从浮栅去除),这导致浮栅20上的电子经由福勒-诺德海姆(fn)隧穿从浮栅20到字线端子22隧穿通过中间绝缘体。

3、通过将正电压置于字线端子22上以及将正电压置于源极区14上来由带有热电子的源极侧注入(ssi)编程存储器单元110(其中电子被置于浮栅上)。电子流将从漏极区16流向源极区14。当电子到达字线端子22和浮栅20之间的间隙时,电子将加速并且变热。由于来自浮栅20的静电引力,一些加热的电子将通过栅极氧化物被注入到浮栅20上。

4、通过将正的读取电压置于漏极区16和字线端子22(其接通沟道区18的在字线端子下方的部分)上来读取存储器单元110。如果浮栅20带正电(即,电子被擦除),则沟道区18的在浮栅20下方的部分也被接通,并且电流将流过沟道区18,该沟道区被感测为擦除状态或″1″状态。如果浮栅20带负电(即,通过电子进行了编程),则沟道区的在浮栅20下方的部分被大部分或完全关断,并且电流将不会(或者有很少的电流)流过沟道区18,该沟道区被感测为编程状态或″0″状态。

5、表1示出可施加到存储器单元110的端子以用于执行读取操作、擦除操作和编程操作的典型电压和电流范围:

6、表1:图1的闪存存储器单元110的操作

7、 wl bl sl 读取 2v-3v 0.6v-2v 0v 擦除 约11v-13v 0v 0v 编程 1v-2v 10.5μa-3μa 9v-10v

8、作为其他类型的闪存存储器单元的其他分裂栅存储器单元配置是已知的。

9、例如,图2示出了四栅极存储器单元210,其包括源极区14、漏极区16、在沟道区18的第一部分上方的浮栅20、在沟道区18的第二部分上方的选择栅22(通常耦接到字线wl)、在浮栅20上方的控制栅28以及在源极区14上方的擦除栅30。这种配置在美国专利6,747,310中有所描述,该专利以引用方式并入本文以用于所有目的。这里,除了浮栅20之外,所有的栅极均为非浮栅,这意味着它们电连接到或能够电连接到电压源。编程由来自沟道区18的将自身注入到浮栅20的加热的电子执行。擦除通过从浮栅20隧穿到擦除栅30的电子来执行。

10、表2示出可施加到存储器单元210的端子以用于执行读取操作、擦除操作和编程操作的典型电压和电流范围:

11、表2:图2的闪存存储器单元210的操作

12、 wl/sg bl cg eg sl 读取 1.0v-2v 0.6v-2v 0v-2.6v 0v-2.6v 0v 擦除 -0.5v/0v 0v 0v/-8v 8v-12v 0v 编程 1v 0.1μa-1μa 8v-11v 4.5v-9v 4.5v-5v

13、图3示出三栅极存储器单元310,其为另一种类型的闪存存储器单元。存储器单元310与图2的存储器单元210相同,不同的是存储器单元310没有单独的控制栅。除了没有施加控制栅偏置,擦除操作(由此通过使用擦除栅进行擦除)和读取操作类似于图2的存储器单元210的操作。在没有控制栅偏置的情况下,编程操作也被完成,并且结果,在编程操作期间必须在源极线上施加更高的电压,以补偿控制栅偏置的缺乏。

14、表3示出可施加到存储器单元310的端子以用于执行读取操作、擦除操作和编程操作的典型电压和电流范围:

15、表3:图3的闪存存储器单元310的操作

16、 wl/sg bl eg sl 读取 0.7v-2.2v 0.6v-2v 0v-2.6v 0v 擦除 -0.5v/0v 0v 11.5v 0v 编程 1v 0.2μa-3μa 4.5v 7v-9v

17、图4示出堆叠栅极存储器单元410,其为另一种类型的闪存存储器单元。存储器单元410与图1的存储器单元110类似,不同的是浮栅20在整个沟道区18上方延伸,并且控制栅22(其在这里将耦接到字线)在浮栅20上方延伸,由绝缘层(未示出)分开。通过电子从fg到衬底的fn隧穿来进行擦除,通过在沟道18与漏极区16之间的区域处的沟道热电子(che)注入、通过电子从源极区14朝向漏极区16流动以及类似于带有较高控制栅电压的图1的存储器单元110的读取操作来进行编程。

18、表4示出可施加到存储器单元410和衬底12的端子以用于对存储器单元410执行读取操作、擦除操作和编程操作的典型电压范围:

19、表4:图4的闪存存储器单元410的操作

20、 cg bl sl 衬底 读取 2v-5v 0.6v-2v 0v 0v 擦除 -8v至-10v/0v flt flt 8v-10v/15v-20v 编程 8v-12v 3v-5v 0v 0v

21、其他非易失性存储器单元是已知的,诸如finfet分裂栅闪存或堆叠栅闪存存储器、nand闪存、sonos(硅-氧化物-氮化物-氧化物-硅,电荷捕获在氮化物中)、monos(金属-氧化物-氮化物-氧化物-硅,金属电荷捕获在氮化物中)、reram(电阻式ram)、pcm(相变存储器)、mram(磁性ram)、feram(铁电ram)、ct(电荷捕获)存储器、cn(碳管)存储器、otp(双电平或多电平一次可编程)和ceram(关联电子ram)等。

22、如上文所展示,非易失性存储器系统通常需要高电压(例如,大于非易失性存储器阵列的核心电压vdd的电压,例如3.3v或5.0v)用于编程和擦除操作。现有技术中存在许多技术,用于在编程或擦除操作期间生成此类高电压且将其提供到适当存储器单元端子。这些技术有时利用高电压生成和收发器电路。高电压生成和收发器电路消耗非易失性存储器系统内的大量功率。

23、需要一种比现有技术电路消耗更少功率的改进的高电压生成和收发器电路。

技术实现思路

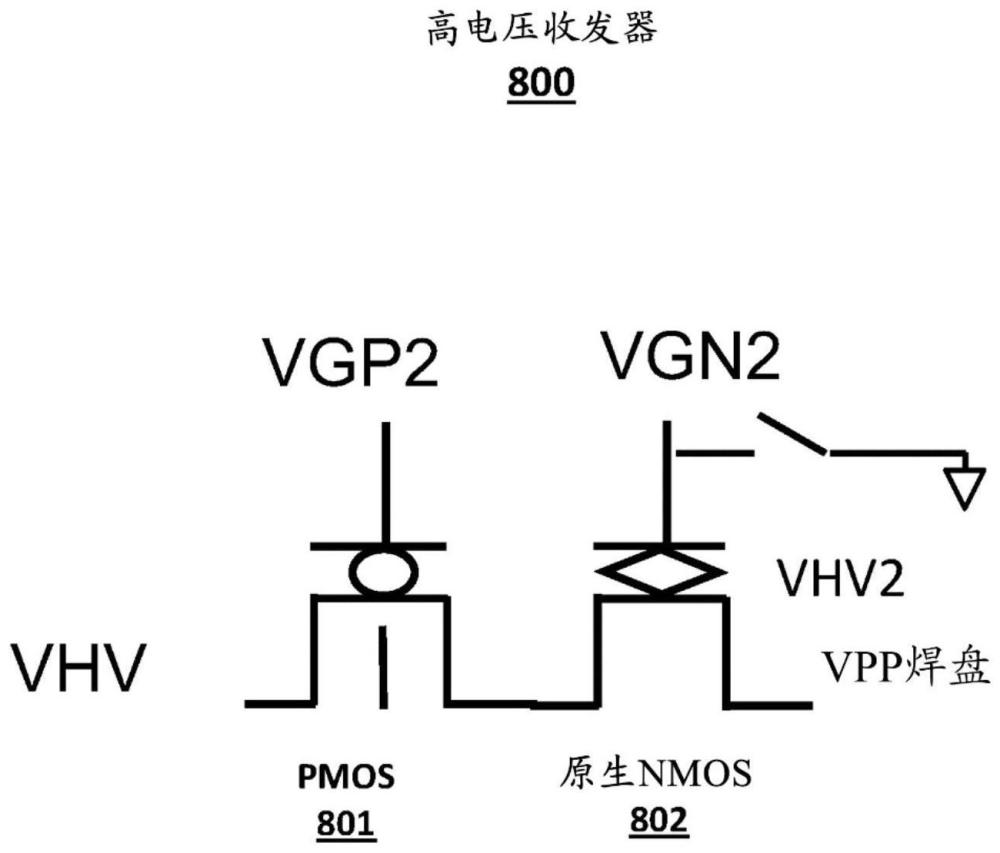

1、公开了用于提供在非易失性存储器系统中擦除或编程操作期间使用的高电压的收发器的多个实施方案。在一个实施方案中,收发器包括pmos晶体管和原生nmos晶体管。在另一实施方案中,收发器包括pmos晶体管、nmos晶体管和原生nmos晶体管。

- 还没有人留言评论。精彩留言会获得点赞!