移位寄存器及其驱动方法、栅极驱动电路和显示面板与流程

本申请属于显示,尤其涉及一种移位寄存器及其驱动方法、栅极驱动电路和显示面板。

背景技术:

1、显示面板通常包括多行栅线和多列数据线。对于栅线的驱动,例如可以采用由多个级联的移位寄存器构成的栅极驱动电路为多行栅线提供扫描驱动信号,从而控制多行栅线依序打开。

2、然而,经本申请的发明人发现,相关技术中的移位寄存器在输出低电平电压信号时,存在输出不稳定的问题。

技术实现思路

1、本申请实施例提供了一种移位寄存器及其驱动方法、栅极驱动电路和显示面板,能够解决移位寄存器在输出低电平电压信号时的输出不稳定的问题。

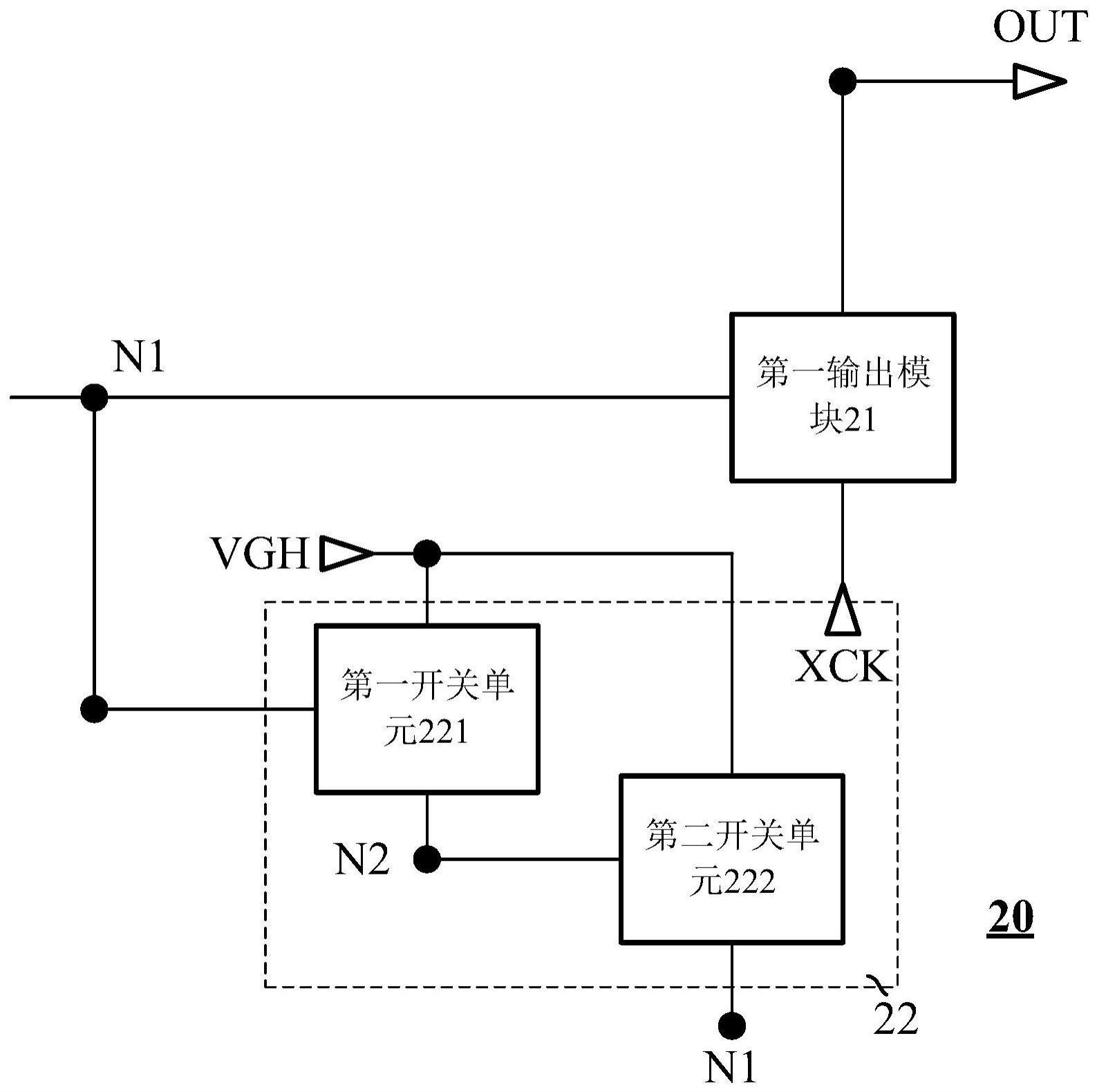

2、第一方面,本申请实施例提供了一种移位寄存器,移位寄存器包括:第一输出模块,第一输出模块的控制端与第一节点电连接,第一输出模块的第一端与第一时钟信号端电连接,第一输出模块的第二端与移位寄存器的输出端电连接;第一节点控制模块,第一节点控制模块包括第一开关单元和第二开关单元,第一开关单元的控制端与第一节点电连接,第一开关单元的第一端与第一电源电压信号端电连接,第一开关单元的第二端与第二节点电连接;第二开关单元的控制端与第二节点电连接,第二开关单元的第一端与第一电源电压信号端电连接,第二开关单元的第二端与第一节点电连接;在低电平输出阶段,第一开关单元在第一节点的控制下导通,将第一电源电压信号端的截止电平写入第二节点,第二开关单元在第二节点的控制下关断。

3、第二方面,本申请实施例提供了一种移位寄存器的驱动方法,移位寄存器包括如第一方面提供的移位寄存器,移位寄存器的驱动方法包括:在低电平输出阶段,向第一节点提供导通电平,以使第一开关单元在第一节点的控制下导通,将第一电源电压信号端的截止电平写入第二节点,第二开关单元在第二节点的控制下关断。

4、第三方面,本申请实施例提供了一种栅极驱动电路,栅极驱动电路包括多个级联的如第一方面提供的移位寄存器。

5、第四方面,本申请实施例提供了一种显示面板,显示面板包括如第三方面提供的栅极驱动电路。

6、本申请实施例的移位寄存器及其驱动方法、栅极驱动电路和显示面板,在低电平输出阶段,第一开关单元响应于第一节点的控制导通,将第一电源电压信号端的截止电平写入第二节点,从而使得第二开关单元在第二节点的控制下关断。这样,一方面可以避免第一电源电压信号端的截止电平通过第二开关单元传输至第一节点而影响第一节点的电位,保证低电平电压信号的稳定输出;另一方面,无论是第一开关单元,还是第二开关单元,均不再与时钟信号端连接,因此可以避免时钟信号端传输的时钟信号跳变对于第一节点的影响,进一步保证低电平电压信号的稳定输出。

技术特征:

1.一种移位寄存器,其特征在于,包括:

2.根据权利要求1所述的移位寄存器,其特征在于,所述第一节点控制模块还包括第三开关单元,所述第三开关单元与所述第二节点电连接;

3.根据权利要求2所述的移位寄存器,其特征在于,所述第三开关单元的控制端和所述第三开关单元的第一端均与第二电源电压信号端电连接,所述第三开关单元的第二端与所述第二节点电连接;

4.根据权利要求3所述的移位寄存器,其特征在于,所述第一开关单元和所述第三开关单元均包括晶体管,所述第一开关单元的沟道区的宽长比大于所述第三开关单元的沟道区的宽长比。

5.根据权利要求4所述的移位寄存器,其特征在于,所述第一开关单元的沟道区的宽长比与所述第三开关单元的沟道区的宽长比的比值大于或等于2:1。

6.根据权利要求2所述的移位寄存器,其特征在于,所述第三开关单元的控制端与第二电源电压信号端电连接,所述第三开关单元的第一端与第二时钟信号端电连接,所述第三开关单元的第二端与所述第二节点电连接;

7.根据权利要求6所述的移位寄存器,其特征在于,在所述低电平输出阶段,所述第三开关单元在所述第二电源电压信号端的控制下导通,将所述第二时钟信号端的截止电平写入所述第二节点。

8.根据权利要求2所述的移位寄存器,其特征在于,所述第三开关单元的控制端与第二时钟信号端电连接,所述第三开关单元的第一端与第二电源电压信号端电连接,所述第三开关单元的第二端与所述第二节点电连接;

9.根据权利要求8所述的移位寄存器,其特征在于,在所述低电平输出阶段,所述第三开关单元在所述第二时钟信号端的控制下关断。

10.根据权利要求1所述的移位寄存器,其特征在于,所述移位寄存器还包括:

11.根据权利要求1所述的移位寄存器,其特征在于,所述第一节点控制模块还包括第四开关单元,所述第四开关单元的控制端与第三时钟信号端电连接,所述第四开关单元的第一端与所述移位寄存器的输入端电连接,所述第四开关单元的第二端与所述第一节点电连接,所述第四开关单元用于在所述第三时钟信号端的控制下,将所述移位寄存器的输入端的导通电平或者截止电平写入所述第一节点。

12.根据权利要求11所述的移位寄存器,其特征在于,所述第四开关单元包括串联的第一子晶体管和第二子晶体管,所述第一子晶体管的栅极和所述第二子晶体管的栅极均与所述第三时钟信号端电连接,所述第一子晶体管的第一极与所述移位寄存器的输入端电连接,所述第一子晶体管的第二极与所述第二子晶体管的第一极电连接,所述第二子晶体管的第二极与所述第一节点电连接。

13.根据权利要求1所述的移位寄存器,其特征在于,所述移位寄存器还包括第一耦合模块,所述第一耦合模块的第一端与所述移位寄存器的输出端电连接,所述第一耦合模块的第二端与所述第一输出模块的控制端电连接。

14.根据权利要求1所述的移位寄存器,其特征在于,所述移位寄存器还包括:

15.根据权利要求14所述的移位寄存器,其特征在于,所述移位寄存器还包括第一存储模块,所述第一存储模块的第一端与所述移位寄存器的输出端电连接,所述第一存储模块的第二端与所述第二输出模块的控制端电连接。

16.一种移位寄存器的驱动方法,其特征在于,所述移位寄存器包括如权利要求1-15中任一项所述的移位寄存器,所述驱动方法包括:

17.根据权利要求16所述的驱动方法,其特征在于,所述第一节点控制模块还包括第三开关单元,所述第三开关单元与所述第二节点电连接;

18.根据权利要求17所述的驱动方法,其特征在于,所述第一节点控制模块还包括第四开关单元,所述第四开关单元的控制端与第三时钟信号端电连接,所述第四开关单元的第一端与所述移位寄存器的输入端电连接,所述第四开关单元的第二端与所述第一节点电连接;

19.根据权利要求18所述的驱动方法,其特征在于,所述高电平输出阶段还包括位于所述低电平输出阶段之后的第二高电平输出阶段、第三高电平输出阶段和第四高电平输出阶段中的至少一个阶段;

20.一种栅极驱动电路,其特征在于,包括多个级联的如权利要求1-15中任一项所述的移位寄存器。

21.一种显示面板,其特征在于,包括如权利要求20所述的栅极驱动电路。

技术总结

本申请实施例提供了一种移位寄存器及其驱动方法、栅极驱动电路和显示面板,移位寄存器包括:第一输出模块,其控制端与第一节点电连接,其第一端与第一时钟信号端电连接,其第二端与移位寄存器的输出端电连接;第一节点控制模块,第一节点控制模块包括第一开关单元和第二开关单元,第一开关单元与第一节点、第一电源电压信号端和第二节点电连接;第二开关单元与第二节点、第一电源电压信号端和第一节点电连接;在低电平输出阶段,第一开关单元在第一节点的控制下导通,将第一电源电压信号端的截止电平写入第二节点,第二开关单元在第二节点的控制下关断。本申请实施例能够解决移位寄存器输出不稳定的问题。

技术研发人员:奚苏萍

受保护的技术使用者:武汉天马微电子有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!