数据写入电路和存储器的制作方法

本发明涉及集成电路,特别是涉及一种数据写入电路和存储器。

背景技术:

1、动态随机存取存储器(英文:dynamic random access memory,简称dram)是一种半导体存储器,主要的作用原理是利用电容内存储电荷的多寡来代表一个二进制比特(英文:bit)是1还是0。

2、dram通常以一个电容和一个晶体管为一个单元排成二维矩阵,基本的操作机制分为读(read)和写(英文:write)。传统技术中,数据写入时需要将列控制信号、写入控制信号、以及数据信号进行时序匹配(英文:timing match),以使得数据可以正确写入存储单元中。

3、然而,考虑到通道走线不同带来的变化,在进行时序匹配的时候能够预留的时序冗余(英文:timing margin)很小。随着dram速度的不断提升以及容量的不断增长,时序匹配越来越难。

技术实现思路

1、基于此,有必要提供一种可以降低时序匹配难度的数据写入电路和存储器。

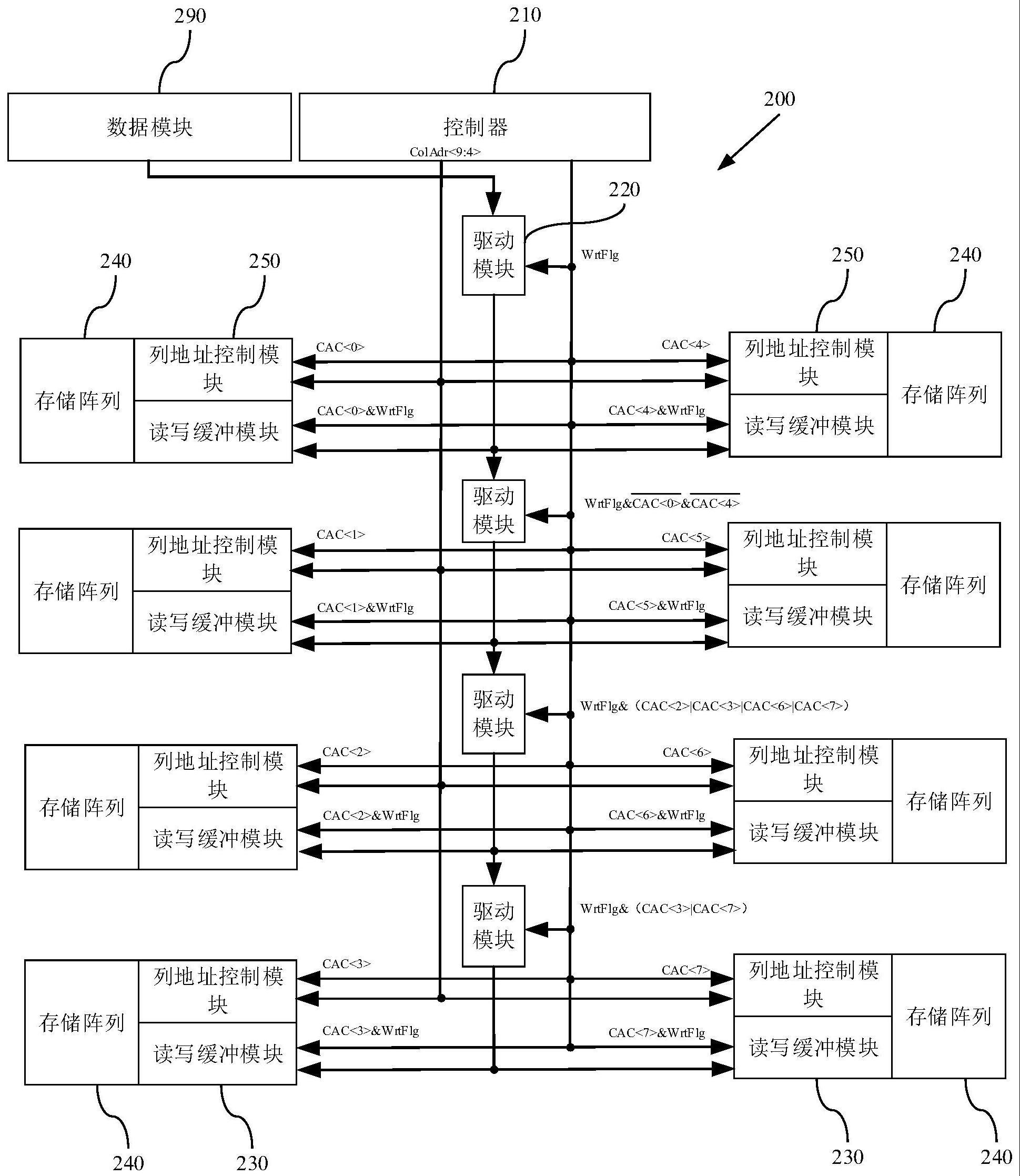

2、第一方面,提供一种数据写入电路,所述电路包括:

3、控制器,用于由写入命令译码得到列地址信号、阵列选择信号和写入标识信号,所述列地址信号包括存储阵列中待写入数据的存储单元的列地址,所述阵列选择信号包括多个所述存储阵列各自的选择标识信号,所述选择标识信号用于表示对应的所述存储阵列是否写入所述数据,所述写入标识信号用于表示所述电路是否写入所述数据;

4、多级驱动模块,每一级所述驱动模块用于连接对应层级的多个所述存储阵列、下一级的所述驱动模块和所述控制器;每一级所述驱动模块用于根据所述写入标识信号或者根据所述写入标识信号和所述阵列选择信号中部分所述存储阵列的所述选择标识信号,驱动所述数据传输至下一级的所述驱动模块中以及传输至对应层级的多个所述存储阵列的数据通道上;

5、多个读写缓冲模块,用于一一对应连接在所述存储阵列和所述存储阵列的所述数据通道之间且分别连接所述控制器;每个所述读写缓冲模块用于根据所述写入标识信号和对应连接的所述存储阵列的所述选择标识信号,将对应连接的所述数据通道上的所述数据传输至对应连接的所述存储阵列中。

6、上述数据写入电路包括控制器、多级驱动模块和多个读写缓冲模块,控制器由写入命令译码得到列地址信号、阵列选择信号和写入标识信号,列地址信号包括存储阵列中待写入数据的存储单元的列地址,阵列选择信号包括多个存储阵列各自的选择标识信号,选择标识信号用于表示对应的存储阵列是否写入数据,写入标识信号用于表示电路是否写入数据,数据写入时只需要阵列选择信号与数据信号进行时序匹配即可,可以有效降低时序匹配的难度。

7、而且每一级驱动模块连接对应层级的多个存储阵列、下一级的驱动模块和控制器,可以根据写入标识信号和阵列选择信号中部分存储阵列的选择标识信号,驱动数据传输至下一级的驱动模块中以及传输至对应层级的多个存储阵列的数据通道上。而多个读写缓冲模块一一对应连接在存储阵列和存储阵列的数据通道之间且分别连接控制器,每个读写缓冲模块可以根据写入标识信号和对应连接的存储阵列的选择标识信号,将对应连接的数据通道上的数据传输至对应连接的存储阵列中。这样在阵列选择信号和写入标识信号的控制下,可以将数据写入目标存储阵列,实现数据的正确写入。

8、在其中一个实施例中,第一级之后的所述驱动模块用于,从所述阵列选择信号中获取对应层级以前或以后的所述存储阵列的所述选择标识信号,并根据获取的所述选择标识信号和所述写入标识信号,驱动所述数据传输至下一级的所述驱动模块中以及传输至对应层级的多个所述存储阵列的所述数据通道上。

9、在其中一个实施例中,第一级之后的所述驱动模块用于,若位于所述多级驱动模块的前半部分,则从所述阵列选择信号中获取对应层级以前的所述存储阵列的所述选择标识信号;若位于所述多级驱动模块的后半部分,则从所述阵列选择信号中获取对应层级以后的所述存储阵列的所述选择标识信号。

10、在其中一个实施例中,前半部分的所述驱动模块用于,将所述写入标识信号与获取的每个所述选择标识信号的反值进行逻辑与,并在逻辑与的结果为目标状态时,驱动所述数据传输至下一级的所述驱动模块中以及传输至对应层级的多个所述存储阵列的所述数据通道上;

11、后半部分的所述驱动模块用于,将所述写入标识信号与获取的每个所述选择标识信号逻辑或的结果进行逻辑与,并在逻辑或的结果为所述目标状态时,驱动所述数据传输至下一级的所述驱动模块中以及传输至对应层级的多个所述存储阵列的所述数据通道上。

12、在其中一个实施例中,每个所述读写缓冲模块用于,接收对应连接的所述存储阵列的所述选择标识信号,将所述写入标识信号与接收到的所述选择标识信号进行逻辑与,并在逻辑与的结果为目标状态时,将对应连接的所述数据通道上的所述数据传输至对应连接的所述存储阵列中。

13、在其中一个实施例中,所述电路还包括:

14、多个列地址控制模块,用于与所述存储阵列一一对应连接且分别连接所述控制器;每个所述列地址控制模块用于接收对应连接的所述存储阵列的所述选择标识信号,并根据接收到的所述选择标识信号,控制所述数据写入对应连接的所述存储阵列中所述列地址信号表征的位线中。

15、第二方面,提供一种数据写入电路,所述电路包括:

16、控制器,用于由写入命令译码得到列地址信号和阵列选择信号,所述列地址信号包括存储阵列中待写入数据的存储单元的列地址,所述阵列选择信号包括多个所述存储阵列各自的选择标识信号,所述选择标识信号用于表示对应的所述存储阵列是否写入所述数据;

17、多级驱动模块,每一级所述驱动模块用于连接对应层级的多个所述存储阵列、下一级的所述驱动模块和所述控制器;第一级的所述驱动模块用于驱动所述数据传输至下一级的所述驱动模块中以及传输至对应层级的多个所述存储阵列的数据通道上;第一级之后的所述驱动模块用于根据所述阵列选择信号中部分所述存储阵列的所述选择标识信号,驱动所述数据传输至下一级的所述驱动模块中以及传输至对应层级的多个所述存储阵列的数据通道上;

18、多个读写缓冲模块,用于一一对应连接在所述存储阵列和所述存储阵列的所述数据通道之间且分别连接所述控制器;每个所述读写缓冲模块用于根据对应连接的所述存储阵列的所述选择标识信号,将对应连接的所述数据通道上的所述数据传输至对应连接的所述存储阵列中。

19、上述数据写入电路包括控制器、多级驱动模块和多个读写缓冲模块,控制器由写入命令译码得到列地址信号和阵列选择信号,列地址信号包括存储阵列中待写入数据的存储单元的列地址,阵列选择信号包括多个存储阵列各自的选择标识信号,选择标识信号用于表示对应的存储阵列是否写入数据,数据写入时只需要阵列选择信号与数据信号进行时序匹配即可,可以有效降低时序匹配的难度。

20、而且每一级驱动模块连接对应层级的多个存储阵列、下一级的驱动模块和控制器,第一级的驱动模块可以驱动数据传输至下一级的驱动模块中以及传输至对应层级的多个存储阵列的数据通道上,第一级之后的驱动模块可以根据阵列选择信号中部分存储阵列的选择标识信号,驱动数据传输至下一级的驱动模块中以及传输至对应层级的多个存储阵列的数据通道上。而多个读写缓冲模块一一对应连接在存储阵列和存储阵列的数据通道之间且分别连接控制器,每个读写缓冲模块可以根据对应连接的存储阵列的选择标识信号,将对应连接的数据通道上的数据传输至对应连接的存储阵列中。这样在阵列选择信号的控制下,可以将数据写入目标存储阵列,实现数据的正确写入。

21、在其中一个实施例中,所述控制器还用于,由写入命令译码得到写入标识信号;或者,

22、根据所述阵列选择信号,生成写入标识信号;

23、其中,所述写入标识信号用于表示所述电路是否写入所述数据;第一级的所述驱动模块用于,根据所述写入标识信号驱动所述数据传输至下一级的所述驱动模块中以及传输至对应层级的多个所述存储阵列的数据通道上。

24、在其中一个实施例中,第一级之后的所述驱动模块用于,从所述阵列选择信号中获取对应层级以前或以后的所述存储阵列的所述选择标识信号,并根据获取的所述选择标识信号和所述写入标识信号,驱动所述数据传输至下一级的所述驱动模块中以及传输至对应层级的多个所述存储阵列的所述数据通道上。

25、第三方面,提供一种存储器,所述存储器包括多个存储阵列和如第一方面或第二方面提供的数据写入电路。

26、上述存储器包括多个存储阵列和上述数据写入电路,可以实现数据的正确写入,并且数据写入时只需要阵列选择信号与数据信号进行时序匹配即可,可以有效降低时序匹配的难度。

- 还没有人留言评论。精彩留言会获得点赞!