半导体存储器的制作方法

实施方式涉及一种半导体存储器。

背景技术:

1、已知有能够将数据非易失地存储的nand(not and,与非)型闪速存储器。

技术实现思路

1、实施方式提供一种能够使读出动作高速化的半导体存储器。

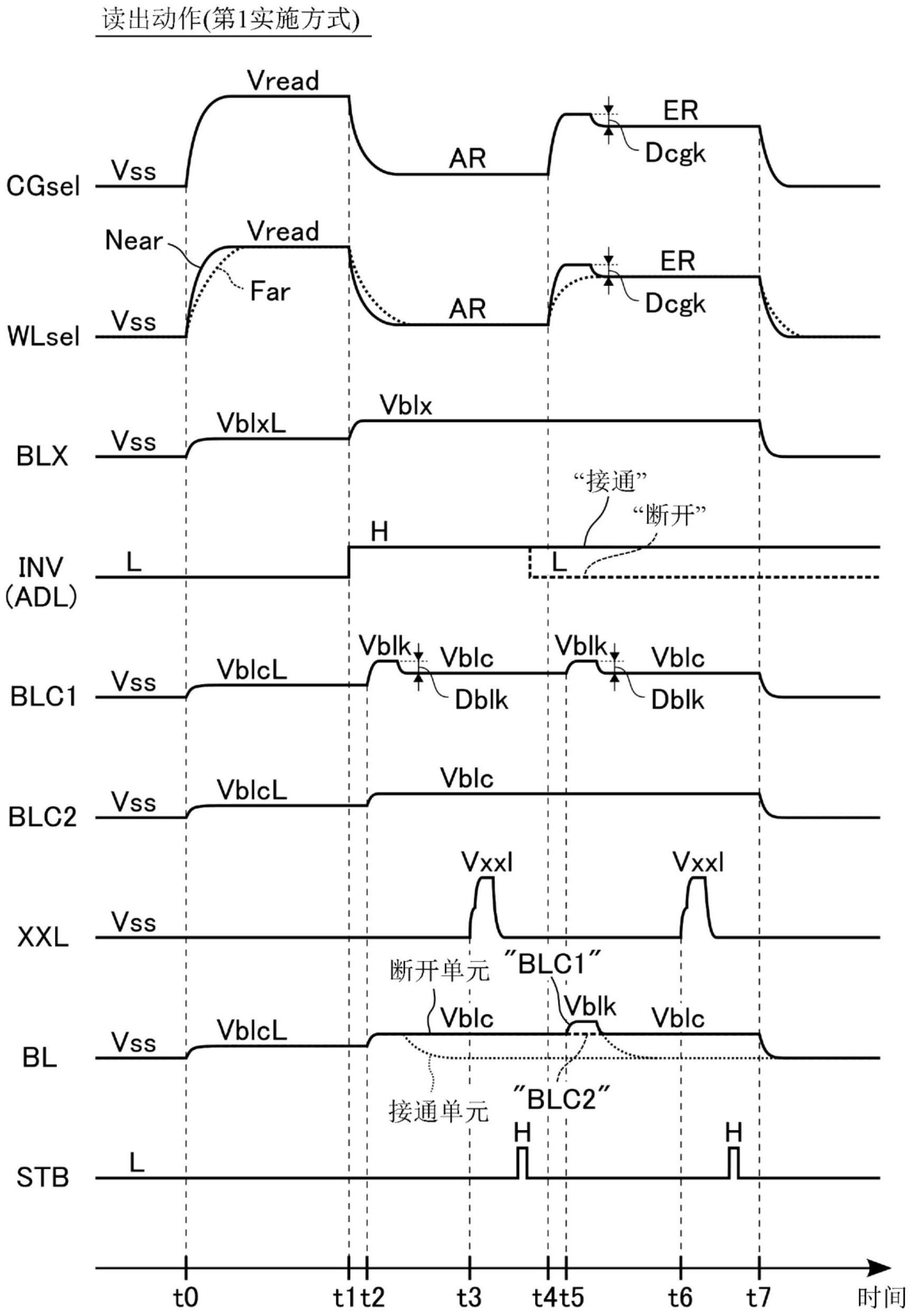

2、实施方式的半导体存储器包含第1及第2存储单元、字线、第1及第2位线、第1及第2感测放大器、以及控制器。第1及第2存储单元分别基于阈值电压存储多比特的数据。字线连接于第1及第2存储单元的各自的栅极。第1及第2位线分别连接于第1及第2存储单元。第1及第2感测放大器分别连接于第1及第2位线。第1及第2感测放大器分别包含第1晶体管、第2晶体管、及第3晶体管。第3晶体管的一端分别电连接于第1晶体管与第2晶体管,另一端连接于对应的位线。在第1及第2存储单元的读出动作中,控制器对字线施加第1读出电压。在控制器施加第1读出电压的第1期间所包含的第1时刻,控制器对第1晶体管施加高于接地电压的第1电压,对第2晶体管施加与第1电压不同的第2电压。在第1时刻,第1感测放大器经由第1晶体管与第3晶体管对第1位线施加电压,第2感测放大器经由第2晶体管与第3晶体管对第2位线施加电压。

技术特征:

1.一种半导体存储器,包括:

2.根据权利要求1所述的半导体存储器,

3.根据权利要求2所述的半导体存储器,

4.根据权利要求3所述的半导体存储器,

5.根据权利要求3所述的半导体存储器,

6.根据权利要求5所述的半导体存储器,

7.根据权利要求3所述的半导体存储器,

8.根据权利要求7所述的半导体存储器,

9.根据权利要求8所述的半导体存储器,

10.根据权利要求1所述的半导体存储器,

11.根据权利要求10所述的半导体存储器,

12.根据权利要求10所述的半导体存储器,

13.根据权利要求12所述的半导体存储器,

14.根据权利要求10所述的半导体存储器,

15.根据权利要求14所述的半导体存储器,

16.根据权利要求15所述的半导体存储器,

17.一种半导体存储器,包括:

18.根据权利要求17所述的半导体存储器,其中,在所述感测放大器的每一者中,所述第1锁存器和所述第2锁存器中的每一者是静态锁存器。

19.根据权利要求17所述的半导体存储器,

20.根据权利要求19所述的半导体存储器,其中,

21.根据权利要求17所述的半导体存储器,其中所述感测放大器中的每一者还包含:

22.根据权利要求21所述的半导体存储器,其中:

23.根据权利要求22所述的半导体存储器,其中:

24.根据权利要求23所述的半导体存储器,其中:

25.根据权利要求24所述的半导体存储器,其中:

26.一种半导体存储器,包括:

27.根据权利要求26所述的半导体存储器,其中,在所述感测放大器的每一者中,所述第1锁存器和所述第2锁存器中的每一者是静态锁存器。

28.根据权利要求26所述的半导体存储器,其中:

29.根据权利要求28所述的半导体存储器,

30.根据权利要求26所述的半导体存储器,其中:

31.根据权利要求30所述的半导体存储器,其中:

32.根据权利要求26所述的半导体存储器,其中所述感测放大器中的每一者还包含第7晶体管,其具有被供给第5控制信号的栅极、电连接于所述第5晶体管的所述另一端的一端、和电连接于所述第6晶体管的所述一端的另一端,以使得所述第5晶体管的所述另一端和所述第6晶体管的所述一端经由所述第7晶体管电连接。

33.根据权利要求32所述的半导体存储器,其中:

34.根据权利要求33所述的半导体存储器,其中:

35.根据权利要求34所述的半导体存储器,其中:

36.根据权利要求34所述的半导体存储器,其中:

37.一种半导体存储器,包括:

38.一种半导体存储器,包括:

39.根据权利要求38所述的半导体存储器,其中,在所述感测放大器单元中的每一者中:

40.根据权利要求38所述的半导体存储器,其中,在所述感测放大器单元中的每一者中:

41.根据权利要求38所述的半导体存储器,其中,在所述感测放大器单元中的每一者中,所述锁存器中的每一者是静态锁存器。

42.根据权利要求38所述的半导体存储器,

43.根据权利要求42所述的半导体存储器,

44.根据权利要求38所述的半导体存储器,其中,在所述感测放大器单元中的每一者中:

45.根据权利要求43所述的半导体存储器,

46.根据权利要求45所述的半导体存储器,其中,当所述控制器执行所述动作时,

47.根据权利要求46所述的半导体存储器,

48.根据权利要求47所述的半导体存储器,

49.根据权利要求48所述的半导体存储器,

50.根据权利要求49所述的半导体存储器,

51.根据权利要求50所述的半导体存储器,

52.一种半导体存储器,包括:

技术总结

本申请涉及半导体存储器。实施方式提供一种能够使读出动作高速化的半导体存储器。实施方式的半导体存储器包含第1及第2存储单元、连接于第1及第2存储单元的字线、分别连接于第1及第2存储单元的第1及第2位线、分别连接于第1及第2位线的第1及第2感测放大器、以及控制器。第1及第2感测放大器分别包含第1至第3晶体管。第3晶体管的一端电连接于第1及第2晶体管,另一端连接于位线。在读出动作中控制器对字线施加读出电压ER。在第1时刻t5,控制器对第1及第2晶体管分别施加第1电压Vblk及第2电压Vblc,第1感测放大器经由第1及第3晶体管对第1位线施加电压,第2感测放大器经由第2及第3晶体管对第2位线施加电压。

技术研发人员:柳平康辅,酒向万里生

受保护的技术使用者:铠侠股份有限公司

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!