一种基于电荷再分配的存内计算电路

本发明属于半导体(semiconductor)和cmos超大规模集成电路(ulsi)中的非挥发性存储器(non-volatile memory)与存内计算(compute-in-memory),具体涉及一种使用非挥发性存储器阵列进行向量矩阵乘法计算(vector matrix multiplication)的计算阵列与外围电路。

背景技术:

1、随着人工智能与深度学习技术的发展,人工神经网络在自然语言处理、图像识别、自动驾驶、图神经网络等领域得到了广泛的应用。然而逐渐增大的网络规模导致数据在内存与传统计算设备如cpu与gpu间的搬运消耗了大量的能量,这被称为冯诺依曼瓶颈。在人工神经网络算法中占据最主要部分的计算为向量矩阵乘法计算(vector matrixmultiplication)。基于非挥发性存储器(non-volatile memory)的存内计算(compute-in-memory),把权重存储在非挥发性存储器单元中,并在阵列中进行模拟向量矩阵乘法计算,避免了数据在内存与计算单元间的频繁搬运,被认为是一种有希望解决冯诺依曼瓶颈的途径。

2、图1为基于非挥发性器件阵列进行向量矩阵乘法的示意图。非挥发性存储器器件如rram、pcram、mram、feram、fefet等在权值写入后,把权值存储在器件的电导值上。器件组织成阵列的形式,从一端输入电压作为向量矩阵乘法的输入,阵列中通过欧姆定律与基尔霍夫定律计算,在阵列的另一端得到的电流为向量矩阵乘法的求和结果。阵列中器件单元可以使用1r器件或1t1r器件。输入可以通过数模转换器(dac)输入多值电压,或通过缓冲器(buffer)输入二值电压。求和结果通常使用模数转换器(adc)读出。由于模数转换器面积与阵列单元面积在长度上不匹配,通常使用多路选择器(mux)让阵列中多个列共用一个模数转换器。由于1t1r器件单元可以避免写串扰的问题,在较大的阵列中通常使用1t1r的器件。在约定的命名方式中,把连接晶体管栅极的线称为字线(word line,wl),连接晶体管源极的线称为源线(source line,sl),连接器件一端的线称为位线(bit line,bl)。

3、两种传统的使用1t1r阵列计算向量矩阵乘法的电路如图2(a)(b)。图2(a)中,输入使用数模转换器输入多值电压或通过缓冲器输入二值电压,输出使用运放钳位位线电压。在位线上根据基尔霍夫定律进行电流求和后,此电流通过运放与电阻组成的跨阻放大器(trans-impedance amplifier,tia)转换成电压,最后通过模数转换器读出。图2(b)中,先把位线(bl)寄生电容预充到固定电压,然后把源线接地,在字线上施加输入脉冲。位线寄生电容上损失的电荷量等于每个器件上流过电荷量之和,所以位线下降电压等于输入乘以权重的向量矩阵乘法计算结果,最后通过模数转换器读出此电压。

4、然而传统的存内计算电路存在以下问题:图2(a)中,由于存在直流过程,在阵列与运放中都有较大电流,影响系统能效进一步提高。图2(b)中,不存在直流过程,因此可以达到较高能效。但由于位线寄生电容通常较小,同时开启行数少,影响计算并行度并增加了模数转换器工作次数。同时由于位线寄生电容小,在不同的输入与权重乘积下不能保持位线上电压稳定,因此计算结果存在非线性。最后图2(b)中由于在晶体管栅极输入,只能输入二值电压,无法通过多值电压高效完成输入。

技术实现思路

1、针对以上现有技术中存在的问题,本发明提出了一种基于电荷再分配的存内计算电路,利用电荷再分配原理实现向量矩阵乘法计算,整个计算过程中只有电荷转移过程且没有直流电流,极大降低计算功耗;设计的存内计算电路同时实现了钳位求和、正负列求差、模拟移位相加与模数转换功能,相比分别独立实现以上模块降低了面积开销。

2、本发明的技术方案如下:

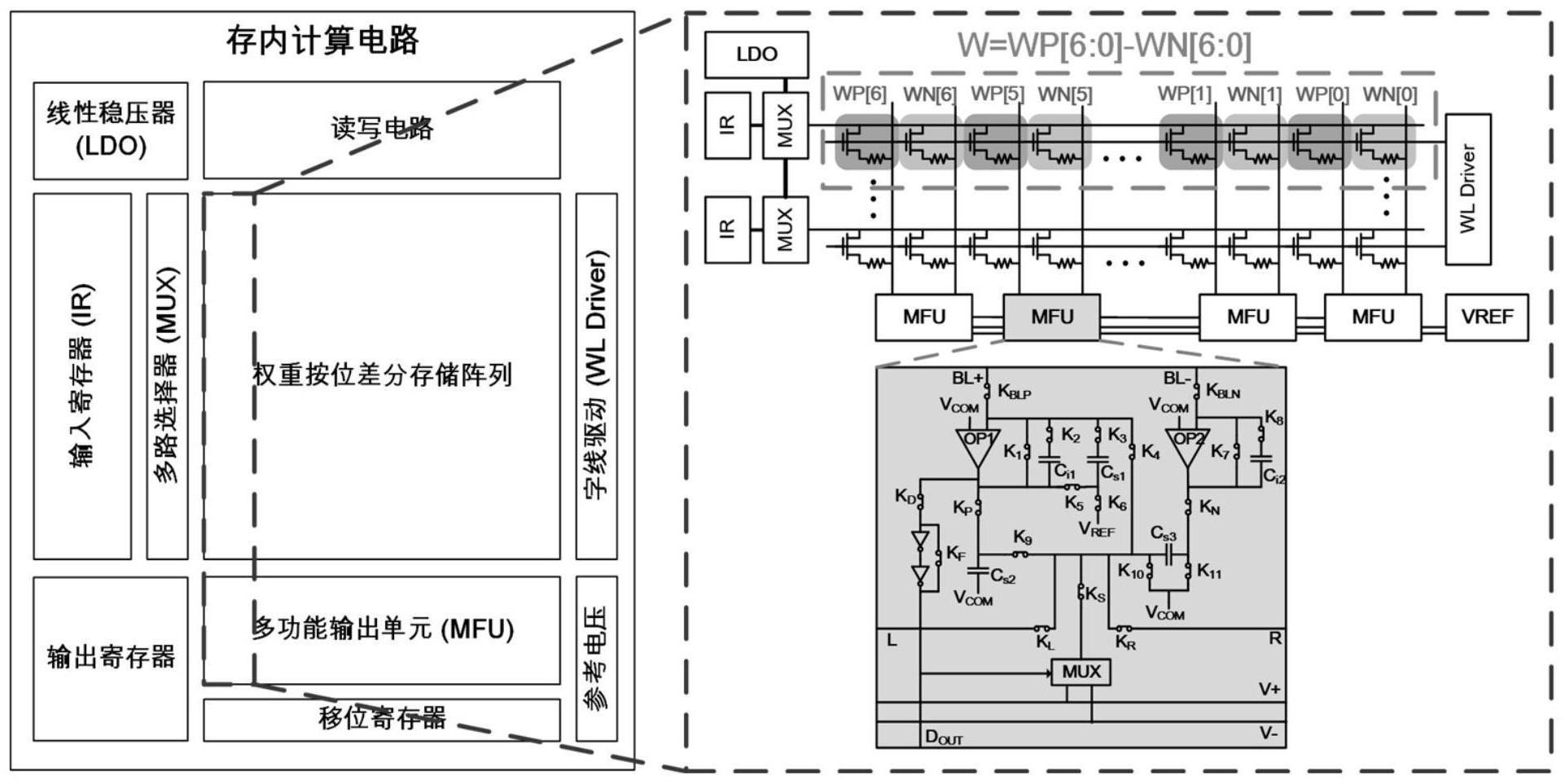

3、一种基于电荷再分配的存内计算电路,包括权重按位差分存储阵列及其外围电路。所述权重按位差分存储阵列采用m行n列非挥发性存储单元构成,将每一行相邻两列的存储单元组成一个按位差分对,把一个x比特有符号权重w表示成两个(x-1)比特无符号权重相减:w=wp[(x-1):0]-wn[(x-1):0],wp与wn是两个(x-1)比特无符号数,分别代表权重的正值与负值,在权重按位差分存储阵列中,wp[0]与wn[0]组成一个按位差分对,存储到一行中相邻的两个存储单元,一行中连续2*(x-1)个存储单元,共分为(x-1)个按位差分对,按低位在右、高位在左的顺序依次存入(x-1)对的无符号权重,一行存储个x比特有符号权重,m行n列阵列共存储个x比特有符号权重,每个差分对列的两条位线bl+、bl-与一个多功能输出单元相连,共需连个多功能输出单元;所述权重按位差分存储阵列每行源线的一端连接一个多路选择器,多路选择器用于选择多值输入电压中的一个电压输入到阵列的源线,源线上存在对地寄生电容csl,csl上存储的电荷量正比于本行源线上的输入电压;所述按位差分存储阵列每行字线都连到同一个字线驱动,字线驱动用于控制阵列中晶体管栅极闭合与断开;所述按位差分存储阵列的权重值通过读写电路写入阵列中存储单元。

4、进一步,所述多功能输出单元包括两个运算放大器op1与op2、五个电容cs1、cs2、cs3、ci1、ci2、两个反相器inv1、inv2、数字输出线dout、一个多路选择器和若干个电路开关,其中五个电容大小关系是:ci1=ci2,cs1=cs2=cs3;其中运算放大器op1与op2与按位差分存储阵列中的差分对两条位线bl+、bl-相连;多功能输出单元通过控制不同的电路开关实现电路的钳位求和功能、正负列结果求差功能、模拟移位相加功能和模数转换功能;多功能输出单元输出的数字转换结果储存在移位寄存器,最后送入输出寄存器。

5、进一步,所述每行源线连接的多路选择器间是串联结构。

6、进一步,所述构成阵列的非挥发性存储单元是rram、pcram、mram、feram、fefet。

7、进一步,所述外围电路包括线性稳压器和输入寄存器,分别与多路选择器连接,线性稳压器用于产生多值输入电压,输入寄存器用于保存多值输入电压。

8、进一步,所述外围电路包括参考电压产生器,用于产生所有多功能输出单元共用的四个电压,参考电压产生器包括线性稳压器和数模转换器,通过线性稳压器产生共模电压vcom与参考电压vref,及通过数模转换器产生差分电压v+与v-。

9、进一步,所述多功能输出单元用于实现位线钳位求和中,操作相关开关,把阵列位线电压钳位在vcom,使向量矩阵乘法过程中位线电压稳定;位线正负列输出电荷存储在运算放大器反馈回路上的电容ci1与ci2上,运算放大器输出电压-vp与-vn正比于ci1与ci2上电荷量,被存储在cs2与cs3,使电荷再分配结果转换成运放输出电压。

10、进一步,所述多功能输出单元实现位线钳位求和后,操作相关开关,使阵列相邻位线的正负列权重对应的输出电压相减(vp-vn),得到一位二进制权重对应的向量矩阵乘法结果,实现位线正负列结果求差。

11、进一步,所述多功能输出单元实现位线正负列结果求差后,操作相邻左右两侧单元中的相关开关,使之与自身左侧或右侧单元连接,使单元中cs2与cs3上电荷发生变化,从而cs2与cs3上极板电压发生变化,从右到左依次执行,以完成不同二进制位间的模拟移位相加功能,实现多位二进制权重的向量矩阵乘法结果的加权求和,得到总的向量矩阵乘法结果,并表示为电容上存储的电压,实现模拟移位相加功能。

12、进一步,所述多功能输出单元在位线钳位求和、位线正负列结果求差或模拟移位相加的过程中,任意时刻对电压进行模数转换时,把待转换电压转移到电容cs1上,运放op1被复用为比较器,比较器输入分别是vcom和cs1上电压加上vref,比较器输出被反相器inv1、inv2组成的锁存器锁存为数字量,经数字输出线dout输出;同时dout也作为多功能输出单元中的二选一多路选择器(mux)的选择线,从差分电压v+与v-中选择一个输入cs2与cs3的上极板,操作相关开关把cs3上电荷转移到cs1,以完成模数转换功能;在差分电压中设置一个固定电压差值vd,用于模数转换的量程,改变多路选择器输入电压v+与v-,后续过程每次数模转换都把vd除以2,分别是vd、vd/2、vd/4……,循环以上过程完成二进制搜索模数转换功能。

13、本发明的技术效果如下:

14、本发明基于电荷再分配的存内计算电路,利用电荷再分配实现向量矩阵乘法计算,整个计算过程中只有电荷转移过程且没有直流电流,极大降低计算功耗;本发明中的多功能输出单元及外围电路,同时具备钳位求和、正负列求差、模拟移位相加与模数转换功能,相比分别独立实现以上模块,降低了系统面积开销。

- 还没有人留言评论。精彩留言会获得点赞!