Norflash的写入方法、装置、编程电路及设备与流程

本申请涉及存储芯片,具体而言,涉及一种nor flash的写入方法、装置、编程电路及设备。

背景技术:

1、nor flash作为一种非易失性存储器芯片,可以对存储器内存储阵列中的存储单元进行擦除(数据擦成“1”)和编程(数据写成“0”)操作。现有的nor flash在每次执行编程操作时,需要将编程数据(包含数据0和数据1,排列顺序对应于存储阵列中的特定区域)写入sram中,然后根据芯片内部的写数据能力分批次写入至存储阵列中,如对于sram大小为256bytes、写数据能力为2bytes的nor flash,其编程操作过程为每次从sram中提取8bytes数据(可以包含数据0和数据1),并分成4次写操作以将8bytes数据写入到存储阵列对应的存储单元中,总的写入次数决定了完成这个编程操作所需的时间;在实际写操作执行过程中,每次写操作的数据中普遍包含多个数据1,芯片的写数据能力未能充分利用而导致编程操作效率受限。

2、针对上述问题,目前尚未有有效的技术解决方案。

技术实现思路

1、本申请的目的在于提供一种nor flash的写入方法、装置、编程电路及设备,以根据sram内数据设定合适的写入操作次数而提高编程操作效率。

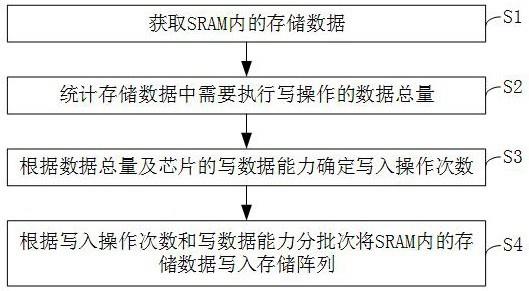

2、第一方面,本申请提供了一种nor flash的写入方法,用于写入数据,所述方法包括以下步骤:

3、获取sram内的存储数据;

4、统计所述存储数据中需要执行写操作的数据总量;

5、根据所述数据总量及芯片的写数据能力确定写入操作次数;

6、根据所述写入操作次数和所述写数据能力分批次将所述sram内的存储数据写入存储阵列。

7、本申请nor flash的写入方法,基于sram内的存储数据统计需要执行写操作的数据总量,并能动态性地根据该数据总量设定合适大小的匹配于写数据能力的写入操作次数以对存储阵列进行分配次的写操作,从而提高了写数据能力的利用率。

8、所述的nor flash的写入方法,其中,所述获取sram内的存储数据的步骤包括:

9、根据预设数据量截取所述sram内的存储数据,所述预设数据量为所述写数据能力的四倍或以上。

10、所述的nor flash的写入方法,其中,所述存储数据的数据量为所述写数据能力的数据量的正整数倍。

11、在该示例中,存储数据的数据量设定为写数据能力的数据量的正整数倍能保证执行最大的写入操作次数时能恰好将存储数据写入至存储阵列对应的存储单元中。

12、所述的nor flash的写入方法,其中,所述数据总量基于计数器遍历计数所述存储数据的数据0进行统计。

13、在该示例中,计数器在每出现一个数据0便计数加1,在每次存储数据截取完后,计数器的计数值便为数据总量的统计结果,以减少了数据总量统计的耗时。

14、所述的nor flash的写入方法,其中,所述根据所述数据总量及芯片的写数据能力确定写入操作次数的步骤包括:

15、计算所述数据总量与所述写数据能力的数据量之间的商获取所述写入操作次数,所述写入操作次数为所述商的上取整值。

16、所述的nor flash的写入方法,其中,所述根据所述写入操作次数和所述写数据能力分批次将所述sram内的存储数据写入存储阵列的步骤包括:

17、根据写数据能力按照数据排列顺序及所述写入操作次数分批提取所述存储数据中需要执行写操作的数据集,并写入存储阵列。

18、所述的nor flash的写入方法,其中,所述根据所述数据总量及芯片的写数据能力确定写入操作次数的步骤包括:

19、将所述存储数据划分为至少一级的多个等大的存储区域,在所述存储数据分为多级存储区域时,每个当前级的存储区域包括多个次一级的存储区域;

20、根据所述数据总量获取每个存储区域中需要执行写操作的数据子量;

21、在所述数据总量小于或等于所述写数据能力的数据量时,所述写入操作次数为一,在所述数据总量大于所述写数据能力的数据量时,获取超过所述写数据能力的数据子量的数量以确定所述写入操作次数,所述写入操作次数为所述数量的加二值。

22、第二方面,本申请还提供了一种nor flash的写入装置,用于写入数据,所述装置包括:

23、获取模块,用于获取sram内的存储数据;

24、统计模块,用于统计所述存储数据中需要执行写操作的数据总量;

25、计算模块,用于根据所述数据总量及芯片的写数据能力确定写入操作次数;

26、写入模块,用于根据所述写入操作次数和所述写数据能力分批次将所述sram内的存储数据写入存储阵列;

27、所述获取sram内的存储数据的步骤包括:

28、根据预设数据量截取所述sram内的存储数据,所述预设数据量为所述写数据能力的四倍或以上。

29、本申请的nor flash的写入装置基于sram内的存储数据统计需要执行写操作的数据总量,并能动态性地根据该数据总量设定合适大小的匹配于写数据能力的写入操作次数以对存储阵列进行分配次的写操作,从而提高了写数据能力的利用率。

30、第三方面,本申请还提供了一种编程电路,与sram和nor flash的存储阵列电性连接,用于运行如上述第一方面提供的所述方法中的步骤以将所述sram内的存储数据写入所述存储阵列。

31、第四方面,本申请还提供了一种电子设备,包括处理器以及存储器,所述存储器存储有计算机可读取指令,当所述计算机可读取指令由所述处理器执行时,运行如上述第一方面提供的所述方法中的步骤。

32、由上可知,本申请提供了一种nor flash的写入方法、装置、编程电路及设备,其中,写入方法基于sram内的存储数据统计需要执行写操作的数据总量,并能动态性地根据该数据总量设定合适大小的匹配于写数据能力的写入操作次数以对存储阵列进行分配次的写操作,从而提高了写数据能力的利用率,并减少了写操作所需要执行的次数,使得编程操作效率得到极大的提升。

技术特征:

1.一种nor flash的写入方法,用于写入数据,其特征在于,所述方法包括以下步骤:

2.根据权利要求1所述的nor flash的写入方法,其特征在于,所述存储数据的数据量为所述写数据能力的数据量的正整数倍。

3.根据权利要求1所述的nor flash的写入方法,其特征在于,所述数据总量基于计数器遍历计数所述存储数据的数据0进行统计。

4.根据权利要求1所述的nor flash的写入方法,其特征在于,所述根据所述数据总量及芯片的写数据能力确定写入操作次数的步骤包括:

5.根据权利要求1所述的nor flash的写入方法,其特征在于,所述根据所述写入操作次数和所述写数据能力分批次将所述sram内的存储数据写入存储阵列的步骤包括:

6.根据权利要求1所述的nor flash的写入方法,其特征在于,所述根据所述数据总量及芯片的写数据能力确定写入操作次数的步骤包括:

7.一种nor flash的写入装置,用于写入数据,其特征在于,所述装置包括:

8.一种编程电路,其特征在于,与sram和nor flash的存储阵列电性连接,用于运行如权利要求1-6任一项所述方法中的步骤以将所述sram内的存储数据写入所述存储阵列。

9.一种电子设备,其特征在于,包括处理器以及存储器,所述存储器存储有计算机可读取指令,当所述计算机可读取指令由所述处理器执行时,运行如权利要求1-6任一项所述方法中的步骤。

技术总结

本发明涉及存储芯片技术领域,具体公开了一种Nor flash的写入方法、装置、编程电路及设备,其中,写入方法包括以下步骤:获取SRAM内的存储数据;统计存储数据中需要执行写操作的数据总量;根据数据总量及芯片的写数据能力确定写入操作次数;根据写入操作次数和写数据能力分批次将SRAM内的存储数据写入存储阵列;该写入方法能动态性地根据该数据总量设定合适大小的匹配于写数据能力的写入操作次数以对存储阵列进行分配次的写操作,从而提高了写数据能力的利用率,并减少了写操作所需要执行的次数,使得编程操作效率得到极大的提升。

技术研发人员:王文静,李佳泽,林杉

受保护的技术使用者:上海芯存天下电子科技有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!