三晶体管嵌入式动态随机访问存储器增益单元的制作方法

本申请概括而言涉及存储器设备的领域,更具体而言,涉及动态随机访问存储器(dynamic random access memory,dram)。

背景技术:

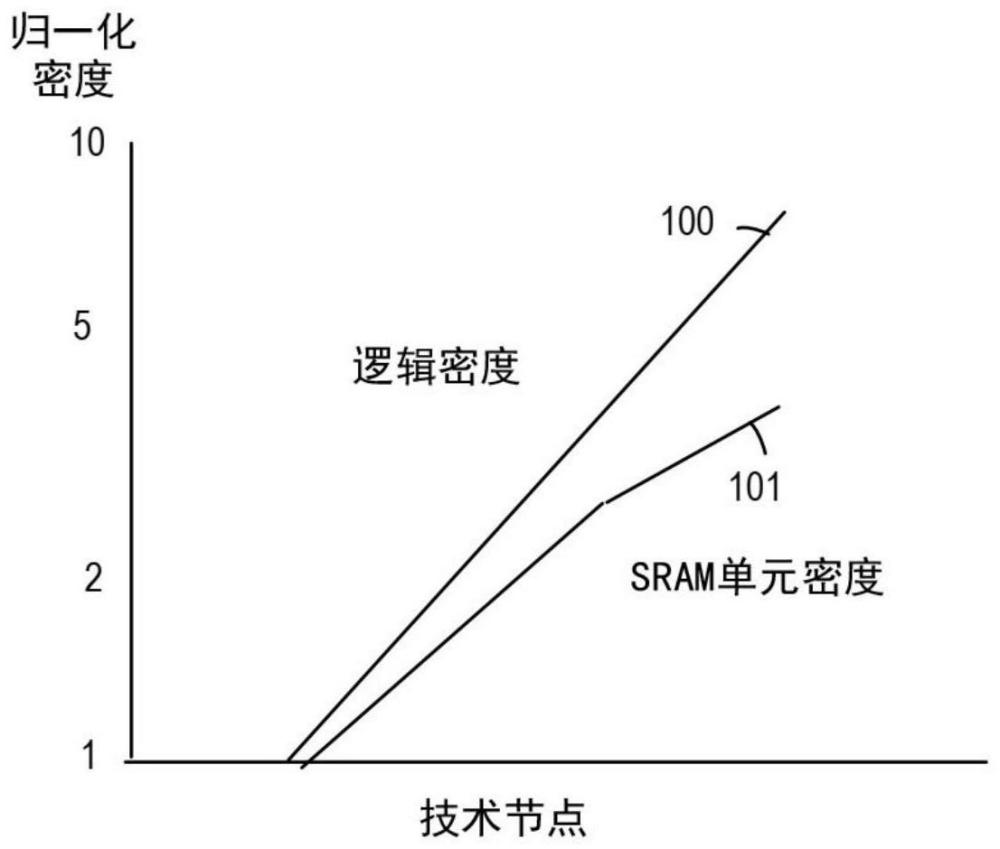

1、存储器设备包括易失性和非易失性存储器。随着例如在高性能处理器中采用更大的管芯上缓存,对存储器的需求在不断增大。静态随机访问存储器(static random accessmemory,sram)是支持这些工作负载和提供片上高密度存储器的默认候选。然而,sram面临着可扩展性问题。dram也被认为提供了对sram的一种更高效的替代。

技术实现思路

1、根据本申请的一方面,提供了一种装置,包括:正面,该正面包括与第二n型金属氧化物半导体(nmos)晶体管串联的第一nmos晶体管,其中,所述第一nmos晶体管的漏极耦合到读取位线;所述正面下方的背面,该背面包括p型金属氧化物半导体(pmos)晶体管和与所述pmos晶体管的漏极耦合的存储节点,其中,所述pmos晶体管的控制栅极耦合到写入字线,并且所述pmos晶体管的源极耦合到写入位线;以及传导路径,该传导路径从所述正面的所述第二nmos晶体管的控制栅极到所述背面的所述存储节点。

2、根据本申请的另一方面,提供了一种装置,包括:第一层面,该第一层面包括n型金属氧化物半导体(nmos)晶体管和与所述nmos晶体管的源极耦合的存储节点;所述第一层面下方的第二层面,所述第二层面包括第一p型金属氧化物半导体(pmos)晶体管,以及与所述第一pmos晶体管串联的第二pmos晶体管;以及传导路径,该传导路径从所述第一层面中的所述存储节点到所述第二层面中的所述第二pmos晶体管的控制栅极。

3、根据本申请的再一方面,提供了一种三晶体管增益单元,包括:布置在p型扩散区域上方的n型扩散区域;所述n型扩散区域中的第一n型金属氧化物半导体(nmos)晶体管和第二nmos晶体管;所述p型扩散区域中的在所述第二nmos晶体管正下方的p型金属氧化物半导体(pmos)晶体管;与所述pmos晶体管的漏极耦合的存储节点;以及从所述第二nmos晶体管的控制栅极到所述存储节点的传导路径。

4、根据本申请的又一方面,提供了一种三晶体管增益单元,包括:布置在p型扩散区域上方的n型扩散区域;所述n型扩散区域中的n型金属氧化物半导体(nmos)晶体管和与所述nmos晶体管的源极耦合的存储节点;所述p型扩散区域中的第一和第二p型金属氧化物半导体(pmos)晶体管;以及从所述存储节点到所述第二pmos晶体管的控制栅极的传导路径。

技术特征:

1.一种装置,包括:

2.如权利要求1所述的装置,其中,所述第一nmos晶体管的源极耦合到所述第二nmos晶体管的漏极,并且所述第二nmos晶体管的源极耦合到地。

3.如权利要求1或2所述的装置,其中:

4.如权利要求1或2所述的装置,其中,所述装置包括三晶体管增益单元,并且根据互补场效应晶体管技术,所述pmos晶体管在所述第二nmos晶体管正下方。

5.如权利要求1或2所述的装置,其中:

6.如权利要求5所述的装置,其中,所述背面包括与所述存储节点耦合的虚设多晶硅层,并且所述传导路径包括通孔,该通孔从所述第二nmos晶体管的控制栅极垂直向下延伸至所述虚设多晶硅层。

7.如权利要求6所述的装置,其中,所述虚设多晶硅层在所述第二nmos晶体管正下方。

8.如权利要求6所述的装置,其中,所述虚设多晶硅层通过背面栅极连接与所述存储节点耦合。

9.如权利要求6所述的装置,其中,所述虚设多晶硅层向所述存储节点的电容添加电容以增加所述存储节点的保持时间。

10.一种装置,包括:

11.如权利要求10所述的装置,其中:

12.如权利要求10或11所述的装置,其中,所述第一pmos晶体管的漏极耦合到所述第二pmos晶体管的漏极,并且所述第二pmos晶体管的源极耦合到电源电压。

13.如权利要求10或11所述的装置,其中:

14.如权利要求10或11所述的装置,其中,所述装置包括三晶体管增益单元,并且根据互补场效应晶体管技术,所述第一pmos晶体管在所述nmos晶体管正下方。

15.如权利要求10或11所述的装置,其中:

16.如权利要求15所述的装置,其中,所述第一层面包括与所述存储节点耦合的虚设多晶硅层,并且所述传导路径包括通孔,该通孔从所述第二pmos晶体管的控制栅极垂直向上延伸至所述虚设多晶硅层。

17.一种三晶体管增益单元,包括:

18.如权利要求17所述的三晶体管增益单元,其中,所述传导路径从所述控制栅极向下延伸至与所述存储节点耦合的虚设节点。

19.如权利要求18所述的三晶体管增益单元,其中,所述虚设节点通过背面栅极连接与所述存储节点耦合。

20.如权利要求17或18所述的三晶体管增益单元,其中,所述传导路径从所述控制栅极向上延伸至金属层并且从所述金属层向下延伸至所述存储节点。

21.一种三晶体管增益单元,包括:

22.如权利要求21所述的三晶体管增益单元,其中,所述传导路径包括:从所述存储节点向上延伸至金属层的通孔,以及从所述金属层向下延伸至所述第二pmos晶体管的控制栅极的通孔。

23.如权利要求21或22所述的三晶体管增益单元,其中,所述传导路径包括:通过背面栅极连接与所述存储节点耦合的虚设节点,以及从所述虚设节点向下延伸至所述第二pmos晶体管的控制栅极的通孔。

技术总结

本申请涉及三晶体管嵌入式动态随机访问存储器增益单元。本文的实施例涉及三晶体管增益单元,该三晶体管增益单元被利用互补场效应晶体管器件来提供以实现缩放。该单元包括布置在p型层上方的n型层。在一种实现方式中,两个nMOS晶体管被布置在一个pMOS晶体管上方,并且提供了传导路径来将nMOS晶体管之一的栅极连接到p型层中的存储节点,其中存储节点耦合到pMOS晶体管的漏极。在另一种实现方式中,一个nMOS晶体管被布置在两个pMOS晶体管上方,并且提供了传导路径来将pMOS晶体管之一的栅极连接到n型层中的存储节点,其中存储节点耦合到nMOS晶体管的源极。

技术研发人员:查尔斯·奥古斯丁,西尼瓦桑·苏布拉马尼亚姆,帕特里克·莫罗,穆罕默德·M·凯拉

受保护的技术使用者:英特尔公司

技术研发日:

技术公布日:2024/5/16

- 还没有人留言评论。精彩留言会获得点赞!