新兴非易失存算一体系统及其电压降影响补偿方法、电路

本发明属于存算一体,更具体地,涉及新兴非易失存算一体系统及其电压降影响补偿方法、电路。

背景技术:

1、新兴非易失存算一体系统,即基于新兴非易失存储器件(emerging nonvolatilememory,envm)的存算一体(processing in memory,pim)系统可进行数据存储和计算操作,目前获得了越来越广泛的应用,其计算和存储的核心结构如图1所示,主要包括由envm单元组成的阵列,与字线相连的开关电路和字线驱动器,与源线相连的开关电路和源线驱动器,以及与位线相连的开关电路和模数转换器;其中,由envm单元组成的阵列是完成存算一体的主要结构,最终各位线上的计算结果经模数转换器转换后输出。此外,新兴非易失存算一体系统还包括处理单元(processingelement,pe)级缓存和控制器。

2、新兴非易失存算一体系统的计算受到envm单元本身编程周期间变化性(cycletocycle variation,c2c variation)的影响以及模数转换器(analog to digitalconverter,adc)转换开销的限制,表现为计算准确度低、计算开销大。

3、编程周期间变化性影响是envm单元固有的属性,是指envm单元的写入阻值具有变化性,即将同一个单元多次编程为相同的数据,每次编程后,该单元的电阻值均不完全相同,具有较小的差异值,该差异值呈对数正态分布。c2c variation对envm阵列的计算结果具有累积性的影响。对于阵列的某一列,假设有n个单元,开始时需要将所有envm单元编程为数值“1”,也即低电阻状态(low resistance state,lrs),对于其中的任意一个envm单元,由于c2c variation现象的影响,其电导值为gmax+δg,其中,gmax表示envm单元在低阻态下的电导值,δg表示由于c2c variation导致的电导变化量。假设该单元被激活参与计算,并且输入数据为“1”,此时该单元两端会添加大小为v的电压,因此该单元计算的输出电流为v*(gmax+δg)。对于该列上的所有单元,其电导值均有一定概率被编程为gmax+δg,如果这些单元的输入数据也为“1”,该列理论输出电流经adc转换后的结果为n,但是最终该列输出电流为n*v*(gmax+δg),这个电流可能比(n+1)*v*gmax,也即理论结果为n+1对应的电流还要大,这就会导致adc错误的将该列计算结果转换成n+1而非n。

4、adc转换开销是指adc转换输出结果时会存在一定开销。对于128×128的阵列大小,8位adc需要在1个计算周期内转换128列的输出结果,现有工作表明这在实践中是不可行的。

5、为了解决上述两个问题,现有工作多将阵列在逻辑上进一步划分为多个计算单元(operation unit,ou),以计算单元为粒度计算,由此能够限制每次计算激活的行、列数目,使得envm单元的计算结果不受其编程周期间变化性的影响。同时,现有工作通过使用更多但更小、采样率更高的adc来转换每个ou的输出结果,在相同adc面积开销的前提下,减小adc转换开销。

6、然而本发明发现,以ou为粒度计算受到互连线寄生电阻带来的严重的电压降(irdrop)影响,电压降影响会导致在新兴非易失存算一体系统上进行计算的准确度下降40%以上。针对电压降影响计算结果准确性的问题,现有工作提出利用补偿模块对整个阵列受到的电压降影响进行缓解,然而,本发明进一步发现,以ou为粒度进行计算,计算单元受到的电压降影响与整个阵列受到的影响不同,并且这个影响具有ou差异性,也即是说,不同位置的ou所受到的电压降影响不同。图2展示了该差异性,图2中,(a)表示电压降对阵列中不同位置的计算单元两端电压的影响,(b)表示电压降对整个阵列的影响,图中的横、纵坐标分别表示阵列中的位线序号和字线序号。因此,现有的补偿方法并不能准确地补偿各个ou所受到的电压降影响,理论上分析,在现有的补偿方案的基础上,可通过调节补偿模块以适应ou之间的电压降差异性,但是,在实际计算过程中,若采用该方法,则需要频繁调节补偿模块,这会引入显著的开销。此外,现有的补偿电压降影响的方案多针对神经网络等特定应用提出,具有应用局限性。

技术实现思路

1、针对现有技术的缺陷和改进需求,本发明提供了新兴非易失存算一体系统及其电压降影响补偿方法、电路,其目的在于,充分考虑电压降影响的ou差异性,计算不同位置ou所受到的电压降影响并进行补偿,以提高新兴非易失存算一体系统的计算准确度。

2、为实现上述目的,按照本发明的一个方面,提供了一种新兴非易失存算一体系统的电压降影响补偿方法,新兴非易失存算一体系统中,阵列在逻辑上被划分为大小为a*b的计算单元;电压降影响补偿方法包括:

3、对于当前被激活的计算单元oux,计算其左侧互连线电阻rl以及其下侧互连线电阻rd所引起的电压降对计算单元oux中各列输出结果造成的误差δoj,并按照所计算的误差对计算单元oux中各列输出结果进行补偿;

4、对于计算单元oux中的第q列,该误差的计算公式如下:

5、

6、其中,a和b分别表示计算单元包含的行数和列数;oj表示计算单元oux中第j列的输出结果,oq表示计算单元oux中第q列的输出结果,gq表示计算单元oux中第q列envm单元的电导之和,s表示输入数据中“1”的数量。

7、进一步地,

8、r1=b·c·rw

9、rd=a·r·rw

10、其中,r和c分别表示计算单元oux的行号和列号;rw表示每一段互连线电阻的大小。

11、进一步地,

12、gq=xq·gmax+(a-xq)·gmin

13、其中,xq表示计算单元oux中第q列中低阻态的envm单元的数目,gmax和gmin分别表示envm单元在低阻态和高阻态下的电导值。

14、进一步地,

15、

16、

17、其中,gmax表示envm单元在低阻态下的电导值,rw表示每一段互连线电阻的大小;δ表示使得envm单元的计算结果不受其编程周期间变化性影响时,计算单元所包含行数的最大值;min()表示求最小值。

18、按照本发明的又一个方面,提供了一种新兴非易失存算一体系统的电压降影响补偿设备,包括:

19、计算机可读存储介质,用于存储计算机程序;

20、以及处理器,用于读取计算机可读存储介质中的计算机程序,执行本发明提供的新兴非易失存算一体系统的电压降影响补偿方法。

21、按照本发明的又一个方面,提供了一种新兴非易失存算一体系统的电压降影响补偿电路,新兴非易失存算一体系统中,阵列在逻辑上被划分为大小为a*b的计算单元,a和b分别表示计算单元所包含的行数和列数;电压降影响补偿电路包括:

22、乘法器m1,其第一输入端用于接收参数a,其第二输入端用于接收当前被激活的计算单元oux的列号r,其用于计算a·r;

23、乘法器m2,其第一输入端用于接收每一段互连线电阻的大小rw,其第二输入端连接至乘法器m1的输出端,其用于计算oux下侧互连线电阻为rd=a·r·rw;

24、乘法器m3,其第一输入端用于接收参数b,其第二输入端用于接收计算单元oux的列号c,其用于计算b·c;

25、乘法器m4,其第一输入端用于接收每一段互连线电阻的大小rw,其第二输入端连接至乘法器m3的输出端,其用于计算oux左侧互连线电阻为rl=b·c·rw;

26、乘法器m5,其第一输入端用于接收计算单元oux中第q列的输出结果oq,其第二输入端连接至乘法器m3的输出端,其用于计算oq·rd;

27、累加器acc,其输入端连接用于接收计算单元oux中各列的输出结果oj,其用于计算

28、除法器d,其第一输入端连接至累加器的输出端,其第二输入端用于接收参数s,其用于计算s表示输入数据中“1”的数量;

29、乘法器m6,其第一输入端连接至除法器d的输出端,其第二输入端连接至乘法器m4的输出端,其用于计算

30、加法器a1,其第一输入端连接至乘法器m6的输出端,其第二输入端连接至乘法器m5的输出端,其用于计算

31、乘法器m7,其第一输入端用于接收计算单元oux中第q列中低阻态的envm单元的数目xq,其第二输入端用于接收envm单元处于低阻态下的电导值gmax,其用于计算xq·gmax;

32、减法器s,其第一输入端用于接收参数a,其第二输入端用于接收计算单元oux中第q列中低阻态的envm单元的数目xq,其用于计算a-xq;

33、乘法器m8,其第一输入端用于接收envm单元在高阻态下的电导值gmin,其第二输入端连接至减法器s的输出端,其用于计算(a-xq)·gmin;

34、加法器a2,其第一输入端连接至乘法器m8的输出端,其第二输出端连接至乘法器m7的输出端,其用于计算计算单元oux中第q列envm单元的电导之和gq=xq·gmax+(a-xq)·gmin;

35、乘法器m9,其第一输入端连接至加法器a1的输出端,其第二输入端连接至加法器a2的输出端,其用于计算oux左侧互连线电阻r1以及下侧互连线电阻rd所引起的电压降对计算单元oux中第q列的输出结果oq造成的误差

36、加法器a3,其第一输入端用于接收计算单元oux中第q列的输出结果oq,其第二输入端连接至乘法器a9的输出端,其用于执行oq+δoq,以对计算单元oux中第q列的输出结果oq进行补偿。

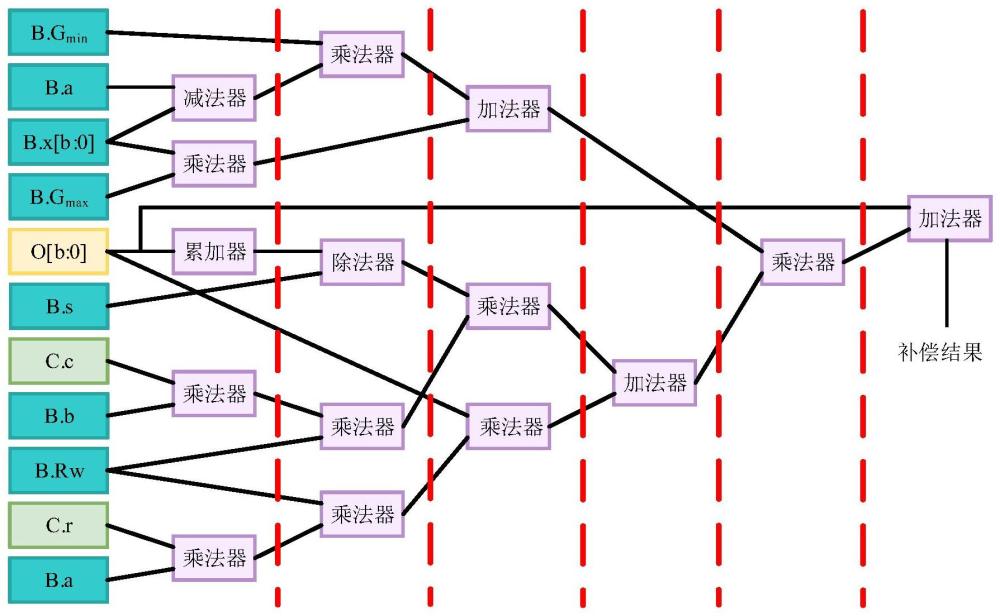

37、进一步地,本发明所提供的新兴非易失存算一体系统的电压降影响补偿电路,为流水线结构,被划分为了6个流水线阶段,其中:

38、乘法器m1、乘法器m3、累加器acc、乘法器m7以及减法器s被划分至第1个流水线阶段;

39、乘法器m2、乘法器m4、除法器d以及乘法器m8被划分至第2个流水线阶段;

40、乘法器m5、乘法器m6以及加法器a2被划分至第3个流水线阶段;

41、加法器a1被划分至第4个流水线阶段;

42、乘法器m9被划分至第5个流水线阶段;

43、加法器a3被划分至第6个流水线阶段。

44、按照本发明的又一个方面,提供了一种新兴非易失存算一体系统,其模数转换器及移位累加器之间包括本发明提供的新兴非易失存算一体系统的电压降影响补偿电路。

45、进一步地,本发明提供的新兴非易失存算一体系统,还包括输入计数器,用于采集输入数据中“1”的数量s;

46、并且,电压降影响补偿电路的输入中,s由输入计数器提供;gmax、gmin、a、b、xq和rw均存储于处理单元级缓存中;r和c由处理单元级控制器提供;计算单元oux中各列的输出结果来自于模数转换器。

47、总体而言,通过本发明所构思的以上技术方案,能够取得以下有益效果:

48、(1)本发明发现,与被激活的计算单元相同的行线上位于计算单元左侧,以及列线上位于计算单元下侧的导线电阻是导致计算单元受到电压降影响的主要因素,因此,本发明在计算当前被激活的计算单元中各列输出结果所受的电压降影响时,仅考虑该计算单元左侧互连线电阻以及其下侧互连线电阻所引起的电压降,同时对于不同位置的ou,其左侧互连线电阻以及下侧互连线电阻大小不同,本发明按照ou位置计算当前被激活的计算单元左侧互连线电阻以及其下侧互连线电阻,由此能够充分考虑计算单元在阵列中的位置导致的电压降影响差异性,实现对不同计算单元受到的电压降影响进行精确的补偿,在具体计算过程中,还考虑了输入模式(即输入数据中“1”的数量)以及ou数据模式(即计算单元中各列低阻态envm单元的数目),因此,本发明能够充分考虑不同位置的计算单元所受到的电压降影响的主要因素,实现精确补偿,有效提高新兴非易失存算一体系统的计算精度。

49、(2)本发明按照rl=b·c·rw、rd=a·r·rw计算当前被激活的计算单元左侧互连线电阻以及其下侧互连线电阻,该计算方式进一步考虑了计算单元大小与计算单元所受电压降影响间的关系,由此能够进一步提高补偿精度。

50、(3)在本发明的优选方案中,按照对划分所得计算单元的大小进行限制,能够使得计算单元内部的寄生线电阻可忽略,同时计算单元内envm单元的编程周期间变化性对计算结果的影响可以忽略,进一步提高了补偿的精度。

51、(4)本发明所提供的新兴非易失存算一体系统的电压降影响补偿电路,其中仅包含乘法器、加法器、触发器、累加器这些器件,能够实现对计算单元中各列计算结果的精确补偿,不需要额外配置电路的帮助,相比于现有工作,有效减少了补偿电路时间、面积和功耗。在其进一步优选的方案中,将补偿电路流水化,进一步提高了补偿电路吞吐率。

52、总的来说,本发明以计算单元为粒度,分析了计算单元所受电压降影响的主要因素,能够充分考虑电压降影响的ou差异性,实现精确补偿,实验表明,相比于未进行电压降补偿的计算结果,本发明可有效提高3%~40%的计算准确度。同时,相关的计算与上层应用无关,因此,可以适用于多种应用。本发明进一步提出了相应的补偿电路,并将补偿电路流水化,减小了补偿电路的开销,相比于现有mirrored、memcmos等补偿方案,本发明在补偿时间、补偿电路面积以及功耗上可分别减小1.3~13倍、1.5~33.1倍、1.4~8.4倍;流水化电路吞吐率与原生阵列计算吞吐率近似。

- 还没有人留言评论。精彩留言会获得点赞!