存储器测试系统和多个被测设备存储器的同时测试方法与流程

本发明涉及用于易失性和非易失性存储器的动态重构半导体测试器的设备、系统和方法,尤其涉及存储器测试设备和多个被测设备的并行测试方法。

背景技术:

1、计算机系统利用易失性和非易失性存储器来存储和检索数据。易失性存储器是有利的,因为相比于传统的硬盘驱动器(hard disk drive,hdd)或固态驱动器(solid statedrive,ssd)设备,它们实现了更快的访问时间。通常,易失性存储器的访问时间比传统hdd或ssd设备快至少一个数量级。易失性存储器通常用于存储和检索较短持续时间的数据,因为它们在失去/移除电源时会丢失数据。

2、非易失性存储器的优势在于,即使在失去/移除电源后,它们仍能保留数据。因此,非易失性存储器通常用于存储和检索更长持续时间的数据,并允许其他计算机系统访问数据。

3、由于当前对更高访问速度的持续需求,大多数计算机系统利用易失性存储器临时存储数据,和非易失性存储器在更长的时间段(包括例如,秒、分钟、小时、天、月甚至年)内存储和检索数据的组合。

4、易失性和非易失性存储器通常由特定光刻工艺制造的半导体晶片的单个裸片(die)组装而成。通常,根据给定的电压(直流(direct current,dc)电平)和定时(交流(alternating current,ac)电平)参数规范,测试这些晶片及其裸片的适当的电气操作和功能。一旦在晶片内识别出一个或更多个已知良好的裸片,则这些裸片将通过封装工艺,从而可以使用单个易失性和非易失性存储器设备封装构建最终产品。

5、易失性和非易失性存储器都可以使用单个裸片,也可以使用双裸片、四裸片和八裸片以及更多进行封装和组装。在某些情况下,封装包括布置在子系统中的单片的或多个裸片。

6、制造商和供应商希望易失性和/或非易失性存储器在产品的使用寿命内都是可靠、稳健和可操作的。为了帮助确保这些质量,存储器部件通常要经过严格的测试。考虑到易失性和非易失性封装的复杂性,可以想象稳健性测试对于构建子系统和最终完全组装的系统的重要性。

7、许多公司提供通用半导体测试设备,所述设备定制使用专用集成电路(application-specific integrated circuit,asic)或现场可编程门阵列(fieldprogrammable gate arrays,fpga)测试特定存储器的电压、频率和温度。

8、一般而言,此类通用测试器仅限于测试易失性存储器或非易失性存储器,但不能同时测试两者。通用测试人员也受到限制,因为他们只能使用自动测试模式生成(automatic test pattern generation,atpg)模式根据现有行业标准实现固定的功能测试模式。总之,这些限制是有问题的,因为在运行终端用户软件的终端用户产品中没有测试过存储器。它们也不能复制终端用户产品中发生存储器故障的情况。因此,没有办法使用通用测试器来有效地预测终端用户的需求,或者修复许多终端用户的问题。

9、volkerink的us 7,707,468描述了一种测试设备,其中存储器控制器呈星形布置,其中多个接口板中的每一个并行工作以测试多个存储器模块。该布置允许以不同的操作速率同时测试各种存储器模块,但该专利对关于易失性和/或非易失性存储器的同时测试保持沉默。此外,接口板不是智能的,因此它们不能根据从存储器控制器下载的多个不同测试模式运行。在存储器模块运行应用软件时,也没有教导、建议或动机来测试存储器模块。

10、因此,存在对半导体测试系统的需求(1)能够测试易失性和非易失性存储器设备,(2)在封装中具有一个或多个裸片,以及(3)在精密模拟终端用户的主机系统(即个人计算机(personal computer,pc)、笔记本电脑、服务器、云等)和软件的测试环境中。理想情况下,这样的系统将提供详细的ac和dc电平测试覆盖范围,以及在正常运行温度、高温和低温、高标称低电压电平和高标称低工作频率下的功能测试,以在主机系统的运行速度下充分应力、锻炼和执行真实世界的功能测试。这样的系统应该能够在能够执行一个或多个应用程序的本地操作系统(operating system,os)上运行终端客户应用程序,以模拟目标主机应用程序环境。

技术实现思路

1、本文描述的本发明主题为易失性和非易失性存储器阵列提供了动态实时测试。在所设想的设备、系统和方法中,存储器测试器单元能够动态地重新配置(a)其输入和输出(input and output,i/o)引脚电压电平,以及(b)其工作频率,而无需任何系统重新启动要求,并且针对不同的易失性产品系列和/或不同的非易失性产品系列执行不同的实时测试模式。

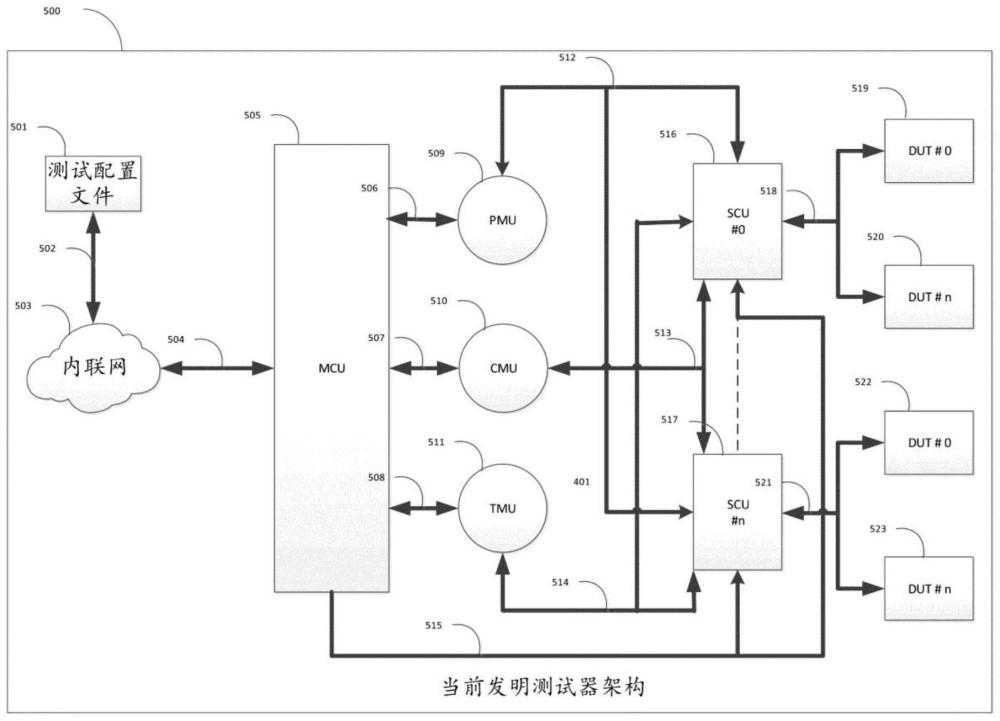

2、预期的存储器测试器单元包括如下所述的几个部件。主控制器单元(mastercontroller unit,mcu)管理能够测试易失性和非易失性存储器的一个或更多个从控制器单元(slave controller unit,scu)。每一个scu能够在相同或不同类型存储器的一个或更多个完全隔离的存储器通道上执行一个或更多个不同的实时测试模式。通过利用这种模块化方法,mcu可以并行地编程一个或更多个scu,以对一个或更多个存储器设备执行成组(gang)/并行测试,这提高了生产率和测试速度,并降低了总测试成本。单个操作员可以将适当的测试模式加载到一个mcu中,并且mcu可以将测试模式上传到一个或更多个scu中,每一个scu以所需的实时测试模式运行,并且每一个scu存储器通道测试一个或更多个存储器设备,而不管被测试的单个存储器是否具有单片、双片、四片、八片或其他数量的裸片。

3、如本文所述,mcu可以通过传统的有线或无线方法连接到每一个scu,以编程和初始化scu单元。mcu可以有利地使用智能的、全自动的扫描器方法来自动加载适当的mcu程序以加载和执行每一个scu。该自动化过程旨在进一步提高利用率,减少人为错误,并改善总体测试成本。

4、如上所述,每一个存储器测试器单元可以具有一个或更多个mcu,其中每一个mcu连接到一个或更多个scu,并且每一个scu可以寻址一个或更多个存储器通道。还可以设想,每一个存储器通道可以具有一个或更多个被测设备板(device under test,dut),其中dut中的每一个具有一个或更多个插口以测试易失性存储器或者非易失性存储器的单个存储器封装。对于具有该领域专业知识的人来说,在了解本应用程序后,显而易见的是,可以使用单个扫描程序在任何给定时间测试数百个存储器封装。

5、mcu可以连接到电源管理单元(power management unit,pmu),该电源管理单元被配置为增加和减少scu i/o引脚、dut存储器插口的电压轨以及电路的其余部分的输入电压和电流。这种灵活性允许mcu能够使同一生态系统测试需要不同工作电压电平的不同存储器设备封装。(即,动态随机存取存储器(dynamic random access memory,dram)5.0v、同步动态随机存储器(synchronous dynamic random access memory,sdram)3.3v、ddr(doubledata rate sdram)-i 2.5v、ddr-ii 1.8v、ddr-iii 1.5v、ddr-iv 1.2v等)

6、mcu也可以连接到时钟管理单元(clock management unit,cmu),该时钟管理单元被配置为与scu i/o引脚和dut存储器插口的时钟引脚一起为scu核心频率运行提供宽时钟间隔范围。该功能允许scu支持需要不同工作频率的许多不同存储器技术。(即,sdram100mhz、ddr-i 200mhz、ddr-ii 400mhz、ddr-iii 800mhz和ddr-iv 1600mhz)

7、mcu也可以被配置为对板载温度管理单元(temperature management unit,tmu)室进行编程,以提供标称室温、低温和高温(即,-50℃至+155℃),来进一步对被测设备施加压力,从而更好地分选和分离测试中的良好的设备和边缘设备。

8、mcu也可以被配置为改变电压、频率和温度,以在应用客户存储器测试模式时执行固态三角测试(solid 3corner testing),并在类似目标客户系统等实时操作下运行dut设备。

9、mcu也可以被配置为现成的个人计算机(pc)或嵌入式pc来执行其任务。运行mcu的软件可以有利地与scu一起执行控制电压、频率、温度的所有任务管理。在一些实施例中,mcu可以是由一个或更多个微控制器、微处理器或处理器单元组成的专用处理单元(processing unit,pu),具有或不具有运行一个或更多个固件(firmware,fw)以共同控制scu、pmu、cmu和tmu单元的操作系统(os)。

10、scu可以以多种方式配置,包括scu可以使用pc上运行的软件、asic上运行的硬件或fpga上运行的动态硬件的任何组合的实施例。scu可以被配置为具有固态模拟和数字逻辑、有限状态机(finite state machine,fsm)、一个或更多个处理单元(即微控制器、微处理器、处理器等)或这些方法中的一个或更多个的组合。

11、在一些实施例中,scu 516、521被配置为运行一个或更多个fw,以管理每一个scu的一个或更多个通道上的一个或更多个任务,这些scu可以连接到一个或更多个dut,并将一个或更多个系列的易失性和/或非易失性存储器测试模式应用到连接到每一个dut单元的一个或更多个插口。这种配置共同地允许scu在每个scu通道上完全执行到每个连接的dut的每个连接的插口的参数测试、功能测试。

12、在根据本发明主题的一个实施例中,scu具有用于测试易失性存储器设备的dut和插口。

13、在根据本发明主题的另一实施例中,scu具有用于测试非易失性存储器设备的dut和插口。

14、在根据本发明主题的又一实施例中,scu具有用于测试易失性双列直插式存储器模块(dual inline memory modules,dimm)设备的dut和插口。

15、在根据本发明主题的再一实施例中,scu具有用于测试非易失性模块设备的dut和插口。

16、预期的scu处理单元可以使用任何独立裸机(bare metal)固件(fw)、迷你操作系统、成熟的(full blow)嵌入式操作系统或实时操作系统(real-time operating system,rtos)运行一个或更多个微控制器、微处理器或处理器。在scu处理单元上运行的固件可以作为一个或更多个编程代码系列,也可以作为单个固件程序,或者作为模块化方法来完成,以提供预期功能的有效和高效执行。fw可以使用低级编程语言(如汇编语言或机器代码)或如c语言(即,c、c++、c#等)的更高抽象级别或面向对象编程(object-orientedprogramming,oop)完成。

17、本发明提供了一种存储器测试系统,包括:

18、主控制器单元mcu,被配置为向至少第一从控制器单元scu和第二从控制器单元scu中的每一个提供测试模式;其中,第一scu被配置为使用测试模式来测试至少第一存储器和第二存储器,同时第二scu使用测试模式测试至少第三存储器和第四存储器;以及其中,第一scu和第二scu中的每一个被配置为在独立配置中操作。

19、本发明还提供了一种多个被测设备dut的存储器的同时测试方法,包括:

20、将测试协议从主控制单元mcu传送到至少第一从控制单元和第二从控制单元scu;利用第一scu的独立操作来针对存储器中的至少第一存储器和第二存储器执行测试协议,同时利用第二scu的独立操作来针对存储器中的至少第三存储器和第四存储器执行测试协议。

21、本文所述的发明主题旨在通过将一种配置加载到mcu中以动态编程和执行一个或许多个scu、pmu、cmu和tmu,来解决动态编程高度灵活的测试器单元以测试半导体易失性和非易失性存储器的整个生态系统。所设想的设备、系统和方法创建了一种完全灵活的、动态的、可编程的半导体测试系统,以在不同电压、不同频率和不同热振荡下测试不同代的易失性和非易失性存储器以充分施压。定制的全功能测试可与实时应用程序一起运行,使用户能够检测整个可接受电压、温度和频率范围内的任何ac和dc电平参数,包括标准现成半导体测试器无法检测到的错误。

22、总的来说,这些功能将帮助用户降低操作成本、减少人为错误、提高产量、减少系统错误和提高系统性能。

- 还没有人留言评论。精彩留言会获得点赞!