存储器及其数据读取方法、存储系统与流程

本技术涉及存储,特别涉及一种存储器及其数据读取方法、存储系统。

背景技术:

1、动态随机存取存储器(dynamic random access memory,dram)中的存储单元一般包括晶体管和电容器。其中,晶体管分别与字线(word line,wl)、位线(bit line,bl)和电容器连接,晶体管能够在wl的控制下,控制bl与电容器的通断,以调整电容器中存储的电荷的电荷量。并且,电容器中存储的电荷的电荷量即可反映存储单元中存储的数据。

2、感测放大(sense amplifier,sa)电路是dram中实现数据读取的关键电路,通过sa电路读取存储单元中存储的数据的过程包括:首先,对待读取的存储单元所连接的位线,以及与该位线相邻的互补位线进行预充电。然后,通过wl将该存储单元中的晶体管导通,以使存储单元中的电容器与位线进行电荷共享(charge share)。由于电荷共享的操作会改变位线的电平,因此sa电路可以感测并放大该位线与互补位线之间的电平差,从而实现对存储单元的数据读取。

3、但是,在上述预充电阶段中,sa电路中会存在漏电流,影响存储器性能。

技术实现思路

1、本技术提供了一种存储器及其数据读取方法、存储系统,可以解决sa电路在预充电阶段中存在漏电流而影响存储器性能的技术问题。所述技术方案如下:

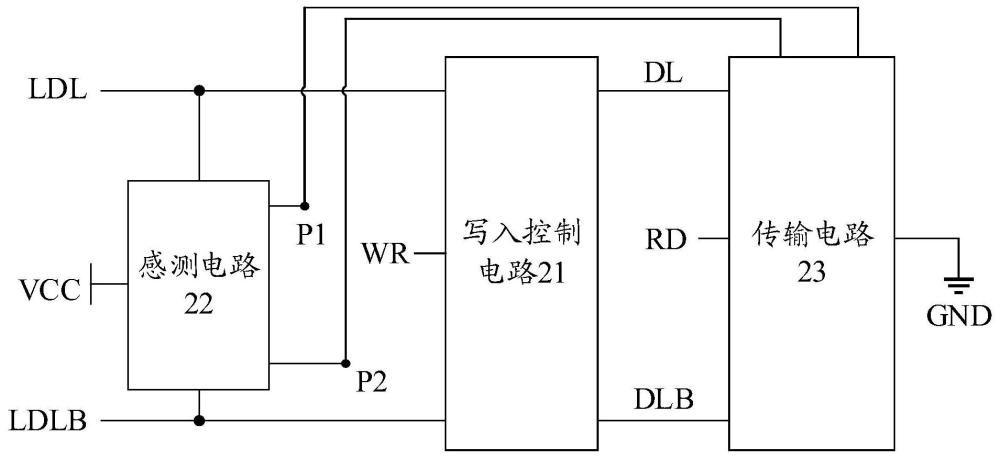

2、第一方面,提供了一种存储器,所述存储器包括:存储阵列和感测放大电路,所述感测放大电路包括:写入控制电路、感测电路和传输电路;

3、所述存储阵列包括多个存储单元,所述多个存储单元至少与第一本地数据线和第二本地数据线连接;

4、所述写入控制电路分别与写入控制线、所述第一本地数据线、所述第二本地数据线、第一数据线和第二数据线连接,并用于基于所述写入控制线提供的写入控制信号,控制所述第一本地数据线与所述第一数据线的通断,以及控制所述第二本地数据线与所述第二数据线的通断;

5、所述感测电路分别与电源端、所述第一本地数据线、所述第二本地数据线、第一节点和第二节点连接,并用于基于所述第一本地数据线的电平,控制所述电源端与所述第一节点的通断,以及基于所述第二本地数据线的电平,控制所述电源端与所述第二节点的通断;

6、所述传输电路分别与读取控制线、所述第一节点、所述第二节点、所述第一数据线、所述第二数据线和接地端连接,并用于基于所述第一节点的电平和所述读取控制线传输的读取控制信号,控制所述第一数据线与所述接地端的通断,以及基于所述第二节点的电平和所述读取控制信号,控制所述第二数据线与所述接地端的通断。

7、可选地,所述传输电路包括:第一传输子电路、第二传输子电路和第三传输子电路;

8、所述第一传输子电路的第一端分别与所述第一节点和所述第二节点连接,所述第二传输子电路的第一端和所述第三传输子电路的第一端均与所述读取控制线连接;

9、所述第一传输子电路的第二端与所述第一数据线连接,第三端与所述第二数据线连接,第四端与所述第二传输子电路的第二端连接,第五端与所述第二传输子电路的第三端连接,所述第二传输子电路的第四端和第五端均与所述第三传输子电路的第二端连接;或者,所述第二传输子电路的第二端与所述第一数据线连接,第三端与所述第二数据线连接,第四端与所述第一传输子电路的第二端连接,第五端与所述第一传输子电路的第三端连接,所述第一传输子电路的第四端和第五端均与所述第三传输子电路的第二端连接;

10、其中,所述第一传输子电路用于基于所述第一节点的电平,控制其第二端与第四端的通断,并基于所述第二节点的电平,控制其第三端与第五端的通断;所述第二传输子电路用于基于所述读取控制信号,控制其第二端与第四端的通断,并控制其第三端与第五端的通断;所述第三传输子电路的第三端与接地端连接,并用于基于所述读取控制信号,控制其第二端与第三端的通断。

11、可选地,所述第一传输子电路包括:第一晶体管和第二晶体管;

12、所述第一晶体管的栅极与所述第一节点连接,所述第一晶体管的第一极与所述第二传输子电路连接,所述第一晶体管的第二极与所述第一数据线或所述第三传输子电路连接;

13、所述第二晶体管的栅极与所述第二节点连接,所述第二晶体管的第一极与所述第二传输子电路连接,所述第二晶体管的第二极与所述第二数据线或所述第三传输子电路连接。

14、可选地,所述第二传输子电路包括:第三晶体管和第四晶体管;

15、所述第三晶体管的栅极与所述读取控制线连接,所述第三晶体管的第一极与所述第一传输子电路连接,所述第三晶体管的第二极与所述第三传输子电路或所述第一数据线连接;

16、所述第四晶体管的栅极与所述读取控制线连接,所述第四晶体管的第一极与所述第一传输子电路连接,所述第四晶体管的第二极与所述第三传输子电路或所述第二数据线连接。

17、可选地,所述第三传输子电路包括:第五晶体管;

18、所述第五晶体管的栅极与所述读取控制线连接,所述第五晶体管的第一极与所述第一传输子电路或所述第二传输子电路连接,所述第五晶体管的第二极与所述接地端连接。

19、可选地,所述感测电路包括:第六晶体管和第七晶体管;

20、所述第六晶体管的栅极与所述第一本地数据线连接,所述第六晶体管的第一极与所述电源端连接,所述第六晶体管的第二极与所述第一节点连接;

21、所述第七晶体管的栅极与所述第二本地数据线连接,所述第七晶体管的第一极与所述电源端连接,所述第七晶体管的第二极与所述第二节点连接。

22、可选地,所述写入控制电路包括:第八晶体管和第九晶体管;

23、所述第八晶体管的栅极与所述写入控制线连接,所述第八晶体管的第一极与所述第一本地数据线连接,所述第八晶体管的第二极与所述第一数据线连接;

24、所述第九晶体管的栅极与所述写入控制线连接,所述第九晶体管的第一极与所述第二本地数据线连接,所述第九晶体管的第二极与所述第二数据线连接。

25、可选地,所述写入控制电路、所述感测电路和所述传输电路中包括的晶体管均为n型晶体管。

26、可选地,所述感测放大电路还包括:预充电电路;

27、所述预充电电路分别与预充控制线、所述电源端、所述接地端、所述第一本地数据线、所述第二本地数据线、所述第一数据线、所述第二数据线、所述第一节点和所述第二节点连接;

28、所述预充电电路用于在所述预充控制线提供的预充控制信号的控制下,通过所述电源端分别为所述第一本地数据线、所述第二本地数据线、所述第一数据线和所述第二数据线进行预充电,以及通过所述接地端下拉所述第一节点和所述第二节点的电平。

29、可选地,所述预充电电路包括:第一预充电子电路和第二预充电子电路;

30、所述第一预充电子电路分别与所述电源端、所述预充控制线、所述第一本地数据线、所述第二本地数据线、所述第一数据线和所述第二数据线连接,并用于基于所述预充控制信号,分别控制所述电源端与所述第一本地数据线、所述第二本地数据线、所述第一数据线和所述第二数据线的通断;

31、所述第二预充电子电路分别与所述接地端、所述预充控制线、所述第一节点和所述第二节点连接,并用于基于所述预充控制信号,分别控制所述接地端与所述第一节点和所述第二节点的通断。

32、可选地,所述第一预充电子电路包括:第十晶体管、第十一晶体管、第十二晶体管和第十三晶体管;

33、所述第十晶体管、所述第十一晶体管、所述第十二晶体管和所述第十三晶体管的栅极均与所述预充控制线连接,第一极均与所述电源端连接;

34、所述第十晶体管的第二极与所述第一本地数据线连接,所述第十一晶体管的第二极与所述第二本地数据线连接,所述第十二晶体管的第二极与所述第一数据线连接,所述第十三晶体管的第二极与所述第二数据线连接。

35、可选地,所述第二预充电子电路包括:第十四晶体管和第十五晶体管;

36、所述第十四晶体管和所述第十五晶体管的栅极均与所述预充控制线连接,第一极均与所述接地端连接;

37、所述第十四晶体管的第二极与所述第一节点连接,所述第十五晶体管的第二极与所述第二节点连接。

38、可选地,所述感测放大电路还包括:读写开关电路;

39、所述多个存储单元通过第一位线和第二位线与所述读写开关电路连接;

40、所述读写开关电路还分别与读写控制线、所述第一本地数据线和所述第二本地数据线连接,并用于基于所述读写控制线提供的读写控制信号,控制所述第一位线与所述第一本地数据线的通断,以及控制所述第二位线与所述第二本地数据线的通断。

41、可选地,所述读写开关电路包括:第十六晶体管和第十七晶体管;

42、所述第十六晶体管的栅极与所述读写控制线连接,第一极与所述第一位线连接,第二极与所述第一本地数据线连接;

43、所述第十七晶体管的栅极与所述读写控制线连接,第一极与所述第二位线连接,第二极与所述第二本地数据线连接。

44、第二方面,提供了一种存储器的数据读取方法,应用于如上述方面提供的存储器,所述方法包括:

45、在预充电阶段,将第一本地数据线、第二本地数据线、第一数据线和第二数据线预充电至第一电平,将第一节点和第二节点的电平下拉至第二电平,并控制传输电路断开所述第一数据线与所述接地端的连接,以及断开所述第二数据线与所述接地端的连接,所述第一电平相对于所述第二电平为高电平;

46、在数据读取阶段,控制所述传输电路导通所述第一数据线与所述接地端的连接,并导通所述第二数据线与所述接地端的连接,以及控制写入控制电路断开所述第一本地数据线与所述第一数据线的连接,并断开所述第二本地数据线与所述第二数据线的连接,以使感测电路感测所述第一本地数据线和所述第二本地数据线的电平。

47、可选地,所述方法还包括:在所述预充电阶段,向所述存储器中的目标字线加载关断电平,以关断所述目标字线所连接的待读取存储单元与所述第一本地数据线的连接;

48、在所述数据读取阶段,向所述目标字线加载启用电平,以导通所述待读取存储单元与所述第一本地数据线的连接。

49、可选地,所述方法还包括:在所述预充电阶段,控制所述传输电路中的第二传输子电路和第三传输子电路均保持关断状态;

50、在所述数据读取阶段,控制所述传输电路中的第二传输子电路和第三传输子电路均保持导通状态。

51、可选地,所述方法还包括:在所述预充电阶段,控制所述写入控制电路断开所述第一本地数据线与所述第一数据线的连接,并断开所述第二本地数据线与所述第二数据线的连接。

52、可选地,所述方法还包括:在所述预充电阶段,控制读写开关电路断开第一位线与所述第一本地数据线的连接,并断开第二位线与所述第二本地数据线的连接;

53、在所述数据读取阶段,控制所述读写开关电路导通所述第一位线与所述第一本地数据线的连接,并导通所述第二位线与所述第二本地数据线的连接。

54、第三方面,提供了一种存储系统,所述存储系统包括:存储器控制器,以及至少一个如上述方面提供的存储器。

55、本技术提供的技术方案至少可以包括以下有益效果:

56、本技术提供了一种存储器及其数据读取方法、存储系统。本技术提供的存储器中的感测放大电路包括写入控制电路、感测电路和传输电路,且该写入控制电路和传输电路分别由写入控制线和读取控制线控制。由此,在预充电阶段能够通过写入控制线和读取控制线断开本地数据线与接地端之间的连接,以避免感测放大电路产生漏电流。并且,在数据读取阶段,能够通过写入控制电路断开本地数据线与数据线之间的连接,以避免该数据线的电平影响本地数据线的电平,进而可以确保数据读取的可靠性。

- 还没有人留言评论。精彩留言会获得点赞!