一种基于10TSRAM单元的存内计算和CAM电路

本发明属于集成电路电路,具体为一种基于10t sram单元的存内计算和cam电路。

背景技术:

1、长期以来,存算分离的冯诺伊曼架构被认为是一个主流的计算范式。然而,随着机器学习和人工智能等数据密集型应用程序的快速发展,计算单元和存储单元之间的频繁数据传输导致了功耗增加和吞吐量减小,产生了存储墙和带宽墙的瓶颈。为了解决这一瓶颈,提出了存内计算架构。存内计算结构因有望成为突破冯诺依曼架构的瓶颈而受到学术界和工业界的青睐。

2、目前许多工作支持存内逻辑运算和cam搜索。agrawal等人提出了一种以8t sram单元改进的x-sram电路结构,可以实现存内布尔运算(包括nand、nor等);s.jeloka等人也提出了分离字线的6t sram单元,实现了布尔逻辑运算和cam搜索。然而,现有的sram大多只能支持单向数据写入,对基于sram的存内计算和cam电路不兼容。而且现有的基于sram的存内计算电路功能较为单一,只能支持简单的布尔运算,通用性较差。

技术实现思路

1、本发明的目的在于:为了解决上述提出多行激活时的读干扰问题,数据单向写入和搜索方式不兼容的问题和现有的存内计算电路功能单一的问题,提供一种基于10t sram单元的存内计算和cam电路。

2、本发明采用的技术方案如下:。

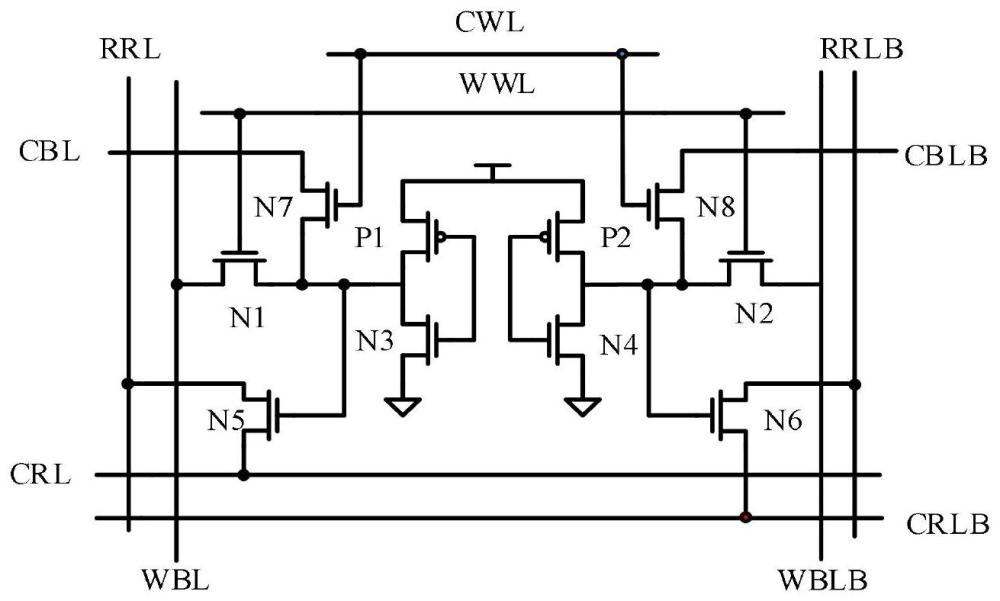

3、一种基于10t sram单元的存内计算和cam电路,包括一个4t sram组成的存储部分、2个nmos晶体管组成的行写入部分、2个nmos晶体管组成的列写入部分和2个nmos晶体管组成的计算部分,其特征在于:

4、所述的一个4t sram,包括nmos晶体管n3、nmos晶体管n4、pmos晶体管p1、pmos晶体管p2;

5、所述的2个nmos组成的行写入部分,包括nmos晶体管n1、nmos晶体管n2;

6、所述的2个nmos组成的列写入部分,包括nmos晶体管n7、nmos晶体管n8;

7、所述的2个nmos组成的计算部分,包括nmos晶体管n5、nmos晶体管n6;

8、在一优选的实施方式中,

9、1、本发明采用解耦的读端口进行存内计算和读取,保证存储数据的独立性,提高单元的抗干扰能力。

10、2、本发明提出了一种计算外设和适用于该计算外设的算法,实现了更为复杂的存内加法、减法和乘法等算数运算。

11、3、本发明提出了一种水平和垂直方向的写入和读取方案,具有非常好的对称特性,使得存内逻辑运算、算数运算、矩阵转置和cam搜索都呈现双向操作的优势。

12、通过采用上述技术方案,pmos晶体管p1的源极、pmos晶体管p2的源极与电源电连接;nmos晶体管n3的源极、nmos晶体管n4的源极与地电连接;

13、pmos晶体管p1的漏极与nmos晶体管n3的漏极电连接于节点q,pmos晶体管p2的漏极与nmos晶体管n4的漏极电连接于节点qb;

14、nmos晶体管n1的源极与线wbl电连接,nmos晶体管n2的源极与线wblb电连接;

15、nmos晶体管n1的栅极、nmos晶体管n2的栅极与线wwl电连接;

16、nmos晶体管n1的漏极与nmos晶体管n3的漏极电连,nmos晶体管n2的漏极与nmos晶体管n2的漏极电连接;

17、nmos晶体管n7的源极与线cbl电连接,nmos晶体管n8的源极与线cblb电连接;

18、nmos晶体管n7的栅极、nmos晶体管n8的栅极与线cwl电连接;

19、nmos晶体管n7的漏极与nmos晶体管n3的漏极电连,nmos晶体管n8的漏极与nmos晶体管n4的漏极电连接;

20、nmos晶体管n5的栅极与nmos晶体管n1的源极电连接,nmos晶体管n6的栅极与nmos晶体管n2的源极电连接;

21、nmos晶体管n5的源极与线rrl电连接、nmos晶体管n6的源极与线rrlb电连接;

22、nmos晶体管n5的漏极与线crl电连接、nmos晶体管n6的漏极与线crlb电连接;

23、在进行行与行之间的逻辑运算时,被选中的行的线crl和线crlb的信号从高电平变化到低电平,未被选中的行的线crl和线crlb的信号保持高电平,线rrl上的电压和线rrlb的电压代表逻辑运算结果,可用灵敏放大器读出;

24、在进行列与列之间的逻辑运算时,被选中的行的线rrl和线rrlb的信号从高电平变化到低电平,未被选中的行的线rrl和线rrlb的信号保持高电平,线crl上的电压和线crlb的电压代表逻辑运算结果,可用灵敏放大器读出;

25、本发明还提出一种计算外设,其包括一个可配置的灵敏放大器、一个带两级延迟的全加器、一个用于选择不同运算类型的mux和一个存储乘数的触发器链;

26、本发明基于上述的计算外设,提出一种适用于sram的算法,实现了存内的加法、减法和乘法等算数运算。

27、综上所述,由于采用了上述技术方案,本发明的有益效果是:

28、本发明中,

29、1、本发明采用解耦的读端口进行存内计算和读取,保证存储数据的独立性,提高单元的抗干扰能力。

30、2、本发明提出了一种计算外设和适用于该计算外设的算法,实现了更为复杂的存内加法、减法和乘法等算数运算。

31、3、本发明提出了一种水平和垂直方向的写入和读取方案,具有非常好的对称特性,使得存内逻辑运算、算数运算、矩阵转置和cam搜索都呈现双向操作的优势。

技术特征:

1.一种基于10t sram单元的存内计算和cam电路,包括一个4tsram组成的存储部分、2个nmos晶体管组成的行写入部分、2个nmos晶体管组成的列写入部分和2个nmos晶体管组成的计算部分,其特征在于所述的一个4t sram,包括nmos晶体管n3、nmos晶体管n4、pmos晶体管p1、pmos晶体管p2;所述的2个nmos组成的行写入部分,包括nmos晶体管n1、nmos晶体管n2;所述的2个nmos组成的列写入部分,包括nmos晶体管n7、nmos晶体管n8;所述的2个nmos组成的计算部分,包括nmos晶体管n5、nmos晶体管n6。

2.如权利要求1所述的一种基于10t sram单元的存内计算和cam电路,其特征在于:pmos晶体管p1的源极、pmos晶体管p2的源极与电源电连接;nmos晶体管n3的源极、nmos晶体管n4的源极与地电连接。

3.如权利要求1所述的一种基于10t sram单元的存内计算和cam电路,其特征在于:pmos晶体管p1的漏极与nmos晶体管n3的漏极电连接于节点q,pmos晶体管p2的漏极与nmos晶体管n4的漏极电连接于节点qb。

4.如权利要求1所述的一种基于10t sram单元的存内计算和cam电路,其特征在于:nmos晶体管n1的源极与线wbl电连接,nmos晶体管n2的源极与线wblb电连接;nmos晶体管n1的栅极、nmos晶体管n2的栅极与线wwl电连接。

5.如权利要求1所述的一种基于10t sram单元的存内计算和cam电路,其特征在于:nmos晶体管n1的漏极与nmos晶体管n3的漏极电连,nmos晶体管n2的漏极与nmos晶体管n2的漏极电连接。

6.如权利要求1所述的一种基于10t sram单元的存内计算和cam电路,其特征在于:nmos晶体管n7的源极与线cbl电连接,nmos晶体管n8的源极与线cblb电连接;nmos晶体管n7的栅极、nmos晶体管n8的栅极与线cwl电连接;nmos晶体管n7的漏极与nmos晶体管n3的漏极电连,nmos晶体管n8的漏极与nmos晶体管n4的漏极电连接。

7.如权利要求1所述的一种基于10t sram单元的存内计算和cam电路,其特征在于:nmos晶体管n5的栅极与nmos晶体管n1的源极电连接,nmos晶体管n6的栅极与nmos晶体管n2的源极电连接。

8.如权利要求1所述的一种基于10t sram单元的存内计算和cam电路,其特征在于:nmos晶体管n5的源极与线rrl电连接、nmos晶体管n6的源极与线rrlb电连接;nmos晶体管n5的漏极与线crl电连接、nmos晶体管n6的漏极与线crlb电连接。

技术总结

本发明涉及集成电路电路领域,公开了一种基于10T SRAM单元的存内计算和CAM电路。本发明中,本发明公开了一种新型的10T SRAM,和基于10T SRAM的存内运算和CAM电路。10T SRAM具有行和列访问晶体管,支持跨行和列的写操作。所提出的SRAM具有水平和垂直的读取端口,利用双向的读取端口可以实现双向的逻辑操作、搜索操作和矩阵转置,显著提高了计算的灵活性。读写端口的分离解决了多行激活时的读干扰问题,提高了单元的抗干扰能力。此外,外围的计算外设支持阵列进行加法、乘法等复杂的算数运算。

技术研发人员:张章,陈志豪

受保护的技术使用者:合肥工业大学智能制造技术研究院

技术研发日:

技术公布日:2024/5/12

- 还没有人留言评论。精彩留言会获得点赞!