内埋元件封装结构及其制造方法与流程

1.本发明是有关于一种元件封装结构及其制造方法,且特别是有关于一种内埋元件封装结构及其制造方法。

背景技术:

2.在系统级封装结构中,将半导体芯片埋入封装基板中的内埋元件技术(semiconductor embedded in substrate,简称sesub),因为具有降低封装基板产品受到噪声干扰及产品尺寸减小的优点,近年来已成为本领域制造商的研发重点。为了提高生产的良率,内埋元件必须固定在介电结构内,以利于后续制作的图案化导电层能与内埋元件电性连接。

3.然而,目前覆盖内埋元件的介电结构为树脂片,树脂片的厚度最多仅有80微米,因而无法提供更厚的介电结构。为了确保芯片被树脂完全覆盖,现今的做法是将芯片磨薄,但当芯片磨薄之后,芯片会有翘曲(warpage)问题,造成后续制程的困难。

技术实现要素:

4.本发明是有关于一种内埋元件封装结构及其制造方法,以封胶材料取代传统的树脂片,以提高介电结构的厚度及/或不减少半导体芯片的厚度,以防止芯片翘曲问题。此外,在后续开孔制程中,对封胶材料进行干式喷砂,以显露出半导体芯片的电性接垫。

5.根据本发明的一方面,提出一种内埋元件封装结构,包括一介电结构、一半导体芯片以及一图案化导电层。半导体芯片内埋于介电结构中,介电结构包覆半导体芯片且具有一第一厚度,半导体芯片具有一第二厚度,第一厚度大于第二厚度,且第一厚度与第二厚度的比值介于1.1~28.4之间。图案化导电层覆盖介电结构的一上表面并延伸于介电结构的一第一开孔中,第一开孔露出半导体芯片的一电性接垫,图案化导电层与半导体芯片的电性接垫电性连接。

6.根据本发明的一方面,提出一种内埋元件封装结构,包括一介电结构、一半导体芯片以及一图案化导电层。介电结构为一热固型封胶材料。半导体芯片内埋于介电结构中,介电结构包覆半导体芯片。图案化导电层覆盖介电结构的一上表面并延伸于介电结构的一第一开孔中,第一开孔露出半导体芯片的一电性接垫,图案化导电层与半导体芯片的电性接垫电性连接,其中第一开孔以喷砂形成。

7.根据本发明的一方面,提出一种内埋元件封装结构的制造方法,包括下列步骤。提供一半导体芯片于一载体上。提供一介电结构于载体上以包覆半导体芯片,介电结构以一模具热固成型。对介电结构进行干式喷砂,形成一第一开孔露出半导体芯片的一电性接垫。形成一图案化导电层于介电结构的一上表面并延伸于第一开孔中,图案化导电层与半导体芯片的电性接垫电性连接。

附图说明

8.为让本发明的上述目的、特征和优点能更明显易懂,以下结合附图对本发明的具体实施方式作详细说明,其中:

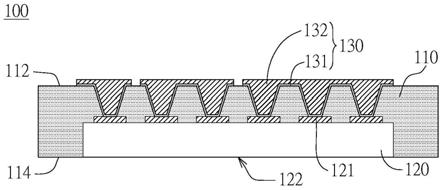

9.图1a至1d绘示依照本发明一实施例的内埋元件封装结构的制造方法的示意图。

10.图2至图6绘示依照本发明不同实施例的内埋元件封装结构的示意图。

11.图7a至7i绘示依照本发明一实施例的内埋元件封装结构的制造方法的示意图。

12.图8a至8l绘示依照本发明另一实施例的内埋元件封装结构的制造方法的示意图。

13.图9a至9l绘示依照本发明又一实施例的内埋元件封装结构的制造方法的示意图。

14.图10a至10l绘示依照本发明又一实施例的内埋元件封装结构的制造方法的示意图。

15.图中元件标号说明:

16.100:内埋元件封装结构

17.102:载体

18.104:离形膜

19.106:图案化耐喷砂光阻

20.110:介电结构

21.111:第一开孔

22.112:上表面

23.113:第二开孔

24.114:下表面

25.115:盲孔

26.116、118:焊罩层

27.120:半导体芯片

28.121:电性接垫

29.122:背面

30.124:散热片

31.125:芯片粘贴膜

32.126:电路层

33.130:图案化导电层

34.131:种子层

35.132:电镀铜层

36.133:接合垫

37.134:导电柱

38.140:第一线路结构

39.141:上介电层

40.142:上导电层

41.143:开口

42.144:种子层

43.145:电镀铜层

44.146:接合垫

45.150:第二线路结构

46.151:下介电层

47.152:下导电层

48.153:焊球

49.154:接合垫

50.160:无源元件

51.170:特殊应用集成电路芯片

52.172:封胶

53.173:侧面

54.h1:第一厚度

55.h2、h2’:第二厚度

具体实施方式

56.以下提出实施例进行详细说明,实施例仅用以作为范例说明,并非用以限缩本发明欲保护的范围。以下是以相同/类似的符号表示相同/类似的元件做说明。以下实施例中所提到的方向用语,例如:上、下、左、右、前或后等,仅是参考所附附图的方向。因此,使用的方向用语是用来说明并非用来限制本发明。

57.依照本发明的一实施例,提出一种内埋元件封装结构及其制造方法。请参照图1a至1d,其绘示依照本发明一实施例的内埋元件封装结构100的制造方法的示意图。首先,形成一介电结构110以包覆半导体芯片120。接着,对介电结构110进行干式喷砂,形成一第一开孔111露出半导体芯片120的电性接垫121。接着,形成一图案化导电层130于介电结构110的一上表面112并延伸于第一开孔111中,且图案化导电层130与半导体芯片120的电性接垫121电性连接。在图1d中,此制造方法更可对半导体芯片120的背面122进行研磨,以使半导体芯片120的厚度减少。

58.请参照图1a,介电结构110具有一第一厚度h1,半导体芯片120具有一第二厚度h2。第一厚度h1大于第二厚度h2,且第一厚度h1与第二厚度h2的比值介于1.1~28.4之间。在一实施例中,第一厚度h1例如介于110-1420微米之间,第二厚度h2例如介于100-50微米之间或更高。第一厚度h1与第二厚度h2之间的差值例如介于10-1370微米之间。

59.本实施例的介电结构110是以封胶材料(epoxy molding compound,emc)取代传统的树脂片,传统的树脂片与封胶的主成份都是环氧树脂及填充物,但填充物的成份及重量百分比不同,因此特性也会不同。传统的树脂片的填充物的重量百分比只有60~85wt%,而封胶的填充物的重量百分比大于85wt%(例如87wt%)。有关封胶的特性请参照表1及表2的说明。

60.在一实施例中,由于封胶材料的厚度(介于110-1420微米之间)远大于树脂片的厚度限制(小于80微米),因此可提高介电结构110的厚度及电绝缘性。此外,封胶材料例如为一热固型环氧树脂,其放置于一模具中并热固成型以包覆半导体芯片120,不限定为片状,亦可为液态状或融熔状。待封胶材料脱模之后,可在高热环境中,对封胶材料进行后烘烤(post-mold cure)制程,可使封胶材料完全固化,且固化后的封胶材料可防止半导体芯片

120翘曲。相对于传统做法需将半导体芯片以树脂片固定在载板上,再以另一树脂片包覆半导体芯片,本实施例只需进行封胶制程,且介电结构110的厚度可根据封装结构100的整体厚度大幅增加,以克服传统树脂片的厚度限制的问题。

61.请参照图1b,对介电结构110进行干式喷砂,以形成多数个第一开孔111,每一第一开孔111露出相对应的电性接垫121。介电结构110的厚度越高,相对需要更多喷砂数才能形成预定的开孔深度。此外,电性接垫121的尺寸较佳小于60微米,因此喷砂制程形成的第一开孔111的孔径较佳小于40微米。另外,干式喷砂之后,还可针对介电结构110的孔壁进行精细化表面处理,以避免产生颗粒化粗糙表面。在一实施例中,可选择颗粒尺寸小的填充物(例如sio2)并加入介电结构110中,填充物的颗粒尺寸例如介于5~15微米之间,较佳介于5~10微米之间,对于后续喷砂制程显露的填充物而言,不会因颗粒太大而导致孔壁表面粗糙度过大而影响后续无电电镀的种子层与封胶材料的结合性。

62.请参照图1c,图案化导电层130例如包括一无电电镀的种子层131以及一电镀铜层132,电镀铜层132可覆盖在无电电镀的种子层131上,并经由局部蚀刻电镀铜层132及种子层131而形成图案化导电层130。请参照图1c,介电结构110的下表面114可切齐半导体芯片120的背面122,且介电结构110可露出半导体芯片120的背面122。

63.请参照图1d,对半导体芯片120的背面122及部分介电结构110进行研磨,以减少半导体芯片120及介电结构110的厚度,例如半导体芯片120的第二厚度h2’减少为第二厚度h2的2/3或更少,使研磨后的半导体芯片120的第二厚度h2’介于50~100微米之间。

64.请参照图2至图6,其分别绘示依照本发明不同实施例的内埋元件封装结构的示意图。图2至图6中各实施例皆以图1c之内埋元件封装结构100为主要架构,后续再根据不同需求增加其他次要结构。请参照图2,此封装结构更可包括一第一线路结构140,其设置于介电结构110的上表面112,例如是覆铜基板(copper clad laminate)制成。第一线路结构140可包括一介电层141,此介电层141例如由积层膜(abf,ajinomoto build-up film)、预浸渍复合纤维、聚酰亚胺或聚丙烯制成。有关图2的封装结构的制作方法,请参照图8a至8l,稍后再说明。

65.请参照图3a及图3b,此封装结构更可包括第一线路结构140以及第二线路结构150,第一线路结构140与第二线路结构150分别覆盖介电结构110的上表面112及相对的下表面114,例如是覆铜基板制成。第一线路结构140及第二线路结构150可分别包括一介电层141、151,此二介电层141、151例如由积层膜(abf)、预浸渍复合纤维、聚酰亚胺或聚丙烯制成。有关图3a及图3b的封装结构的制作方法,请参照图9a至9l及图10a至10l,稍后再说明。

66.请参照图3a及图3b,此封装结构更可包括贯穿介电结构110的至少一导电柱134。导电柱134电性连接第一线路结构140及第二线路结构150。上述形成导电柱134的方法包括喷砂,且导电柱134可与第一线路结构及第二线路结构的制程一起形成。

67.请参照图4a至4b,此封装结构更可包括二焊罩层116、118,其分别覆盖介电结构110的上表面112及下表面114,且半导体芯片120的背面122露出于焊罩层118。在图4b中,封装结构更可包括一线路结构150,其设置于介电结构110的下方,且介电结构110下方的焊罩层116用以形成焊罩开口显露出接合垫154,以供焊球153电性连接接合垫154。

68.请参照图4c,其与图4b的封装结构相似,差异在于:此封装结构更可包括一散热片124,设置于介电结构110的上方并与半导体芯片120的背面122热接触。散热片124用以吸收

半导体芯片120的废热,以降低半导体芯片120的温度。

69.请参照图5a及图5b,其与图3a及图3b的封装结构相似,差异在于:此封装结构更可包括二焊罩层116、118,其分别覆盖第一线路结构140及第二线路结构150的上方及下方,且封装结构100的介电结构110下方的焊罩层118用以形成焊罩开口显露出接合垫154,以供焊球153电性连接接合垫154。此外,在图5b中,半导体芯片120更可包括一芯片粘贴膜125(die attach film)以及一电路层126内埋于芯片粘贴膜125中。电路层126预先形成于芯片粘贴膜125中,并显露于介电结构110的表面。后续再形成一第一线路结构140于介电结构110上,以使电路层126与其上方的第一线路结构140电性连接。

70.请参照图6,其与图5b的封装结构相似,差异在于:此封装结构更可包括一无源元件160以及一特殊应用集成电路(asic)芯片170,设置于第一线路结构140上方并与第一线路结构140或芯片粘贴膜125中的电路层126电性连接。在一实施例中,无源元件160例如为电容、电感或电阻等,asic芯片170可与半导体芯片120配合或独自运作,以提高芯片的整体效能。此外,此封装结构更包括一封胶172,包覆无源元件160以及特殊应用集成电路芯片170,且封胶172的侧面173例如切齐封装结构100的侧面。请参照表1,封胶172的主成份为环氧树脂及填充物,填充物的重量百分比为87wt%或89wt%,平均尺寸14或17微米,筛网尺寸55或75微米。请参照表2,介电结构110的主成份为环氧树脂及填充物,不同在于:填充物的重量百分比为89wt%,平均尺寸5微米,筛网尺寸25微米。

71.请参照图7a至7i,其绘示依照本发明一实施例的内埋元件封装结构的制造方法的示意图。首先,在图7a及图7b中,在载体102上形成一离形膜104。将半导体芯片120设置于离形膜104上,以使半导体芯片120暂时设置于载体102上。载体102例如是一刚性基板,例如金属板或塑胶板。离形膜104具有粘性并与半导体芯片120相粘合,以定位半导体芯片120。在图7c中,提供一介电结构110于载体102上以包覆半导体芯片120,介电结构110以一模具热固成型。也就是说,介电结构110为一热固型封胶材料,与传统的树脂片的材质及厚度不同。此外,相对于传统做法,不需将半导体芯片120以树脂片固定在载板上,只需使用可移除的离形膜104,以简化制程及节省成本。在图7d中,形成一图案化耐喷砂光阻106于介电结构110上。在图7e中,对介电结构110的部分上表面112进行干式喷砂,以形成凹陷于介电结构110的第一开孔111,且第一开孔111显露出半导体芯片120的电性接垫121。接着,在图7f及图7g中,形成一图案化导电层130于介电结构110的上表面112并延伸于第一开孔111中,图案化导电层130与半导体芯片120的电性接垫121电性连接。图案化导电层130例如包括一无电电镀的种子层131以及一电镀铜层132,电镀铜层132可覆盖在无电电镀的种子层131上,并经由局部蚀刻电镀铜层132及种子层131而形成图案化导电层130。在图7h中,移除载体102及离形膜104。在图7i中,形成二焊罩层116、118于介电结构110的上表面112及下表面114,并可显露出半导体芯片120的背面122及图案化导电层130的接合垫133。

72.请参照图8a至8l,其绘示依照本发明另一实施例的内埋元件封装结构的制造方法的示意图。图8a至8g的步骤已于上述实施例中提及,在此不再赘述。在图8h中,形成一介电层141于介电结构110上,并压合一上导电层142(例如铜箔)在介电层141上,再加热固化介电层141。介电层141例如由积层膜(abf,ajinomoto build-up film)、预浸渍复合纤维、聚酰亚胺或聚丙烯制成。在图8i中,形成多个开口143于介电层141中,接着,在图8j中,形成一无电电镀的种子层144于上导电层142的上表面及开口143中,再形成一电镀铜层145于种子

层144上,以使上导电层142与图案化导电层130之间电性连接。在图8k中,经由蚀刻上导电层142、种子层144及电镀铜层145,以形成图案化线路,如此,第一线路结构140完成。在图8l中,形成二焊罩层116、118于介电结构110及第一线路结构140的上方及下方,并可显露出半导体芯片120的背面122及第一线路结构140的接合垫146。

73.请参照图9a至9l,其绘示依照本发明另一实施例的内埋元件封装结构的制造方法的示意图。图9a至9g的步骤已于上述实施例中提及,在此不再赘述。在图9h中,形成一上介电层141及一下介电层151于介电结构110的上方及下方,并压合一上导电层142及一下导电层152(例如铜箔)在上介电层141及下介电层151上,再加热固化上介电层141及下介电层151。在图9i中,形成贯穿介电结构110、上介电层141及下介电层151的至少一第二开孔113。上述形成第二开孔113的方法包括喷砂。在图9j中,形成一无电电镀的种子层144于上导电层142和下导电层152上及第二开孔113中,再形成一电镀铜层145于种子层144上,以使上导电层142与下导电层152之间经由第二开孔113中的导电柱134电性连接。在图9k中,经由蚀刻上导电层142、种子层144、电镀铜层145及下导电层152,以形成图案化线路,如此,第一线路结构140及第二线路结构150完成。在图9l中,形成二焊罩层116、118于第一线路结构140及第二线路结构150的上方及下方,并可显露出第一线路结构140的接合垫146及第二线路结构150的接合垫154。

74.请参照图10a至10l,其绘示依照本发明又一实施例的内埋元件封装结构的制造方法的示意图。图10a至10g的步骤与图9a至9g的步骤相似,相同之处不再赘述,差异在于,在图10e中,更包括形成贯穿介电结构110的至少一第二开孔113。因此,后续在图10i中,仅形成贯穿第一介电层141及第二介电层151的二盲孔115。上述形成第二开孔113及盲孔115的方式包括喷砂。图10j至10l的步骤与图9j至9l的步骤相似,用以形成第一线路结构140及第二线路结构150于介电结构110的上方及下方,在此不再赘述。

75.根据本发明上述实施例,由于传统树脂片的厚度最多仅有80微米,因而无法提供更厚的介电结构110以覆盖半导体芯片120。在本实施例中,以封胶材料取代传统的树脂片,以使介电结构110的厚度介于110-1420微米之间。只要半导体芯片120的厚度小于介电结构110的厚度即可,不需将芯片磨薄,因此,可解决因芯片磨薄而翘曲(warpage)的问题。同时,在第五代移动通信技术(5g)上,介电结构110的厚度例如750微米以上,介电结构110与半导体芯片120的厚度比大于2或3,可有效减少电感耦合的干扰,提高封装结构100的电绝缘性,以符合市场的需求。

76.请参照表1,本实施例图6的封胶172例如以四方扁平封装(qfn)结构所使用的封胶为例,其具有良好的热硬度、吸水性低、粘度低、导热率低及抗弯强度高等,适合用于元件封装结构中。有关封胶172的材料特性及参数如下:

77.表1

78.[0079][0080]

请参照表2,本实施例的介电结构110以覆晶球格阵列(flip chip ball grid array,bga)结构所使用的封胶材料为例,其具有良好的热硬度、吸水性低、粘度低、导热率低,且相对于传统的树脂片的填充物含量较高因而具有更高的抗弯强度,适合用于内埋元件封装结构中。有关介电结构110的封胶材料特性及参数如下:

[0081]

表2

[0082]

[0083][0084]

在一实施例中,可选择颗粒尺寸小的填充物(例如al2o3/sio2)并加入介电结构110中,填充物的颗粒尺寸例如介于5~15微米之间,较佳介于5~10微米之间。填充物的重量百分比例如89%,含量越高,热膨胀系数越高,以使介电结构110与半导体芯片120的热膨胀系数相匹配。此外,填充物的颗粒尺寸越小时,在后续开孔制程中,对封胶材料进行干式喷砂时,不会因颗粒太大而导致孔壁表面粗糙度过大而影响后续无电电镀的种子层与封胶材料的结合性。

[0085]

虽然本发明已以较佳实施例揭示如上,然其并非用以限定本发明,任何本领域技术人员,在不脱离本发明的精神和范围内,当可作些许的修改和完善,因此本发明的保护范围当以权利要求书所界定的为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1