具有用于2晶体管垂直存储器单元的共享读取/写入存取线的存储器装置的制作方法

具有用于2晶体管垂直存储器单元的共享读取/写入存取线的存储器装置

1.优先权申请

2.本技术案主张2018年12月26日申请的序列号为62/785,136的美国临时申请案的优先权权益,所述申请案的全部内容以引用的方式并入本文中。

背景技术:

3.存储器装置广泛用于计算机及许多其它电子产品中来存储信息。存储器装置大体上分为两种类型:易失性存储器装置及非易失性存储器装置。易失性存储器装置的实例包含动态随机存取存储器(dram)装置。非易失性存储器装置的实例包含闪存装置(例如闪存棒)。存储器装置通常具有众多存储器单元来存储信息。在易失性存储器装置中,如果电源与存储器装置断开,那么存储于存储器单元中的信息丢失。在非易失性存储器装置中,即使电源与存储器装置断开,但存储于存储器单元中的信息留存。

4.本文的描述涉及易失性存储器装置。大多数常规易失性存储器装置以电荷的形式将信息存储于包含于存储器单元中的电容器结构中。随着对装置存储密度的要求提高,许多常规技术提供缩小存储器单元的大小以提高给定装置面积的装置存储密度的方式。然而,如果要将存储器单元大小缩小到某一尺寸,那么物理限制及制造约束会对此类常规技术提出挑战。与一些常规存储器装置不同,本文描述的存储器装置包含可克服常规技术面临的挑战的特征。

附图说明

5.图1展示根据本文描述的一些实施例的呈包含易失性存储器单元的存储器装置的形式的设备的框图。

6.图2展示根据本文描述的一些实施例的包含2晶体管(2t)存储器单元的存储器阵列的存储器装置的一部分的示意图。

7.图3展示根据本文描述的一些实施例的包含在存储器装置的读取操作期间使用的实例电压的图2的存储器装置。

8.图4展示根据本文描述的一些实施例的包含在存储器装置的写入操作期间使用的实例电压的图2的存储器装置。

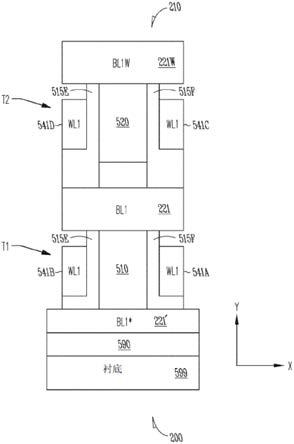

9.图5到图10展示根据本文描述的一些实施例的图2的存储器装置的结构的不同视图。

10.图11a、图11b及图11c展示根据本文描述的一些实施例的包含多个层面的存储器单元的存储器装置的结构的不同视图。

具体实施方式

11.本文描述的存储器装置包含易失性存储器单元,其中存储器单元中的每一者可包含两个晶体管(2t存储器单元)。两个晶体管中的一者具有电荷存储结构,其可形成存储器

单元的存储器元件来存储信息。本文描述的存储器装置可具有允许存储器装置的大小相对小于类似常规存储器装置的大小的结构(例如4f2单元占据面积)。下文参考图1到图10论述所描述的存储器装置及其变体的其它改进及益处。

12.图1展示根据本文描述的一些实施例的呈包含易失性存储器单元的存储器装置100的形式的设备的框图。存储器装置100包含存储器阵列101,其可含有存储器单元102。存储器装置100是易失性存储器装置(例如dram装置),使得存储器单元102是易失性存储器单元。因此,如果电源(例如供应电压vcc)与存储器装置100断开,那么存储于存储器单元102中的信息会丢失(例如无效)。在下文中,vcc被称为表示一些电压电平,然而,其不限于存储器装置(例如存储器装置100)的供应电压(例如vcc)。举例来说,如果存储器装置(例如存储器装置100)具有基于vcc产生内部电压的内部电压产生器(图1中未展示),那么可使用此内部电压来代替vcc。

13.在存储器装置100的物理结构中,存储器单元102中的每一者可包含在存储器装置100的衬底(例如半导体衬底)上方垂直形成于不同层级中(例如,在不同层中彼此上下堆叠)的晶体管(例如两个晶体管)。包含存储器单元102的存储器阵列101的结构可包含下文参考图2到图10描述的存储器阵列101及存储器单元102的结构。

14.如图1中展示,存储器装置100可包含存取线104(例如“字线”)及数据线(例如位线)105。存储器装置100可使用存取线104上的信号(例如字线信号)来存取存储器单元102及使用数据线105来提供存储(例如,写入)于存储器单元102中或从存储器单元102读取(例如,感测)的信息(例如数据)。

15.存储器装置100可包含地址寄存器106以接收线(例如地址线)107上的地址信息addr(例如行地址信号及列地址信号)。存储器装置100可包含行存取电路系统(例如x解码器)108及列存取电路系统(例如y解码器)109,其可操作以解码来自地址寄存器106的地址信息addr。基于经解码地址信息,存储器装置100可确定在存储器操作期间将存取哪些存储器单元102。存储器装置100可执行写入操作以将信息存储于存储器单元102中及执行读取操作以读取(例如,感测)存储器单元102中的信息(例如先前存储的信息)。存储器装置100还可执行操作(例如刷新操作)以刷新存储于存储器单元102中的信息的值(例如,使其保持有效)。存储器单元102中的每一者可经配置以存储可表示至多一个位(例如具有二进制0(“0”)或二进制1(“1”)的单个位)或一个以上位(例如具有至少两个二进制位的组合的多个位)的信息。

16.存储器装置100可分别在线130及132上接收包含供应电压vcc及vss的供应电压。供应电压vss可以接地电势操作(例如,具有约零伏的值)。供应电压vcc可包含从外部电源(例如电池或交流到直流(ac

‑

dc)转换器电路系统)供应到存储器装置100的外部电压。

17.如图1中展示,存储器装置100可包含存储器控制单元118(其包含电路系统(例如硬件组件))以基于线(例如控制线)120上的控制信号来控制存储器装置100的存储器操作(例如读取及写入操作)。线120上的信号的实例包含行存取选通信号ras*、列存取选通信号cas*、写入启用信号we*、芯片选择信号cs*、时钟信号ck及时钟启用信号cke。这些信号可为提供到dram装置的信号的部分。

18.如图1中展示,存储器装置100可包含可携载信号dq0到dqn的线(例如全局数据线)112。在读取操作中,提供到线112(以信号dq0到dqn的形式)的信息(从存储器单元102读取)

的值(例如“0”或“1”)可基于数据线105上的信号的值。在写入操作中,提供到数据线105(存储于存储器单元102中)的信息的值(例如“0”或“1”)可基于线112上的信号dq0到dqn的值。

19.存储器装置100可包含感测电路系统103、选择电路系统115及输入/输出(i/o)电路系统116。列存取电路系统109可基于地址信号addr选择性激活线114(例如选择线)上的信号。选择电路系统115可响应线114上的信号来选择数据线105上的信号。数据线105上的信号可表示存储于存储器单元102中的信息的值(例如,在写入操作期间)或从存储器单元102读取(例如,感测)的信息的值(例如,在读取操作期间)。

20.i/o电路系统116可操作以将从存储器单元102读取的信息提供到线112(例如,在读取操作期间)及将来自线112(例如,由外部装置提供)的信息提供到数据线105以存储于存储器单元102中(例如,在写入操作期间)。线112可包含存储器装置100内的节点或存储器装置100可驻留于其中的封装上的引脚(或焊球)。存储器装置100外部的其它装置(例如硬件存储器控制器或硬件处理器)可通过线107、112及120与存储器装置100通信。

21.存储器装置100可包含图1中未展示以免模糊本文描述的实例实施例的其它组件。存储器装置100的至少一部分(例如存储器阵列101的一部分)可包含与下文参考图2到图10描述的存储器装置中的任何者类似或等同的结构及操作。

22.图2展示根据本文描述的一些实施例的包含存储器阵列201的存储器装置200的一部分的示意图。存储器装置200可对应于图1的存储器装置100。举例来说,存储器阵列201可形成图1的存储器阵列101的部分。如图2中展示,存储器装置200可包含作为易失性存储器单元(例如dram单元)的存储器单元210到215。为简单起见,存储器单元210到215当中的类似或等同元件被给予相同元件符号。

23.存储器单元210到215中的每一者可包含两个晶体管t1及t2。因此,存储器单元210到215中的每一者可被称为2t存储器单元(例如2t增益单元)。晶体管t1及t2中的每一者可包含场效晶体管(fet)。晶体管t1可包含基于电荷存储的结构(例如,基于浮动栅极)。如图2中展示,存储器单元210到215中的每一者可包含电荷存储结构202,其可包含晶体管t1的浮动栅极(例如浮动栅极202)。电荷存储结构202可形成存储器单元210到215当中的相应存储器单元的存储器元件。电荷存储结构202可存储电荷。存储于存储器单元210到215当中的特定存储器单元中的信息的值(例如“0”或“1”)可基于所述特定存储器单元的电荷存储结构202中的电荷量。

24.如图2中展示,存储器单元210到215当中的特定存储器单元的晶体管t2(例如晶体管t2的沟道区)可电耦合到(例如,直接耦合到)所述特定存储器单元的电荷存储结构202。因此,在存储器装置200的操作(例如写入操作)期间,可直接在特定存储器单元的晶体管t2与所述特定存储器单元的电荷存储结构202之间形成电路路径(例如电流路径)。

25.存储器单元210到215可布置成存储器单元群组2010及2011。图2展示两个存储器单元群组(例如2010及2011)作为实例。然而,存储器装置200可包含两个以上存储器单元群组。存储器单元群组2010及2011可包含相同数目个存储器单元。举例来说,存储器单元群组2010可包含存储器单元210、212及214,且存储器单元群组2011可包含存储器单元211、213及215。图2展示存储器单元群组2010及2011中的每一者中的三个存储器单元作为实例。存储器单元群组2010及2011中的存储器单元的数目可不同于三个。

26.存储器装置200可执行写入操作以将信息存储于存储器单元210到215中及执行读

取操作以从存储器单元210到215读取(例如,感测)信息。存储器装置200可经配置以操作为dram装置。然而,与将信息存储于例如电容器的容器的结构中的一些常规dram装置不同,存储器装置200可以电荷的形式将信息存储于电荷存储结构202(其可为浮动栅极结构)中。如上文提及,电荷存储结构202可为晶体管t1的浮动栅极(例如浮动栅极202)。因此,存储器装置200可被称为基于浮动栅极的dram装置。

27.如图2中展示,存储器装置200可包含存取线(例如字线)241、242及243,其可携载相应信号(例如字线信号)wl1、wl2及wl3。存取线241、242及243可用于存取存储器单元群组2010及2011两者。存取线241、242及243中的每一者可经构造为至少一个导电线(一个导电线或可彼此电耦合(例如,短路)的多个导电线)。可在存储器装置200的操作(例如读取或写入操作)期间选择性激活存取线241、242及243(例如,一次激活一个)以存取存储器单元210到215当中的一选定存储器单元(或多个选定存储器单元)。选定单元可称为目标单元。在读取操作中,可从一选定存储器单元(或多个选定存储器单元)读取信息。在写入操作中,信息可为一选定存储器单元(或多个选定存储器单元)中的存储信息。

28.在存储器装置200中,单个存取线(例如单个字线)可用于在存储器装置200的读取或写入操作期间控制(例如,接通或关断)相应存储器单元的晶体管t1及t2。两个单独存取线可用于在读取及写入操作期间的相应存储器单元的存取期间控制相应晶体管t1及t2。然而,使用存储器装置200中的单个存取线(例如共享存取线)来控制相应存储器单元的晶体管t1及t2两者可节省空间且简化存储器装置200的操作。

29.在存储器装置200中,晶体管t1及t2中的每一者的栅极可为相应存取线(例如相应字线)的部分。如图2中展示,存储器单元210的晶体管t1及t2中的每一者的栅极可为存取线241的部分。存储器单元211的晶体管t1及t2中的每一者的栅极可为存取线241的部分。

30.存储器单元212的晶体管t1及t2中的每一者的栅极可为存取线242的部分。存储器单元213的晶体管t1及t2中的每一者的栅极可为存取线242的部分。

31.存储器单元214的晶体管t1及t2中的每一者的栅极可为存取线243的部分。存储器单元215的晶体管t1及t2中的每一者的栅极可为存取线243的部分。

32.存储器装置200可包含可携载相应信号(例如读取位线信号)bl1、bl1*、bl2及bl2*的数据线(例如读取位线)221、221'、221w、222、222'及222w及可携载相应信号(例如写入位线信号)bl1w及bl2w的数据线(例如写入位线)221w及222w。在读取操作期间,存储器装置200可使用数据线221及221'来获得从存储器单元群组2010的选定存储器单元读取(例如,感测)的信息及使用数据线222及222'来从存储器单元群组2011的选定存储器单元读取信息。在写入操作期间,存储器装置200可使用数据线221w来提供存储于存储器单元群组2010的选定存储器单元中的信息及使用数据线222w来提供存储于存储器单元群组2011的选定存储器单元中的信息。

33.存储器装置200可包含读取路径(例如电路路径)。在读取操作期间从选定存储器单元读取的信息可通过耦合到选定存储器单元的读取路径获得。在存储器单元群组2010中,特定存储器单元(例如210、212或214)的读取路径可包含通过所述特定存储器单元的晶体管t1的沟道区及数据线221及221'的电流路径(例如读取电流路径)。在存储器单元群组2011中,特定存储器单元(例如221、213或215)的读取路径可包含通过所述特定存储器单元的晶体管t1的沟道区及数据线222及222'的电流路径(例如读取电流路径)。由于晶体管t1

可在读取路径中用于在读取操作期间从相应存储器单元读取信息,因此晶体管t1可被称为读取晶体管且晶体管t1的沟道区可被称为读取沟道区。

34.存储器装置200可包含写入路径(例如电路路径)。在写入操作期间存储于选定存储器单元中的信息可通过耦合到选定存储器单元的写入路径提供到选定存储器单元。在存储器单元群组2010中,特定存储器单元的写入路径可包含通过所述特定存储器单元的晶体管t2的沟道区及数据线221w的电流路径(例如写入电流路径)。在存储器单元群组2011中,特定存储器单元(例如221、213或215)的写入路径可包含通过所述特定存储器单元的晶体管t2的沟道区及数据线222w的电流路径(例如写入电流路径)。由于晶体管t2可在写入路径中用于在写入操作期间将信息存储于相应存储器单元中,因此晶体管t2可被称为写入晶体管且晶体管t1的沟道区可被称为写入沟道区。

35.晶体管t1及t2中的每一者可具有阈值电压(vt)。晶体管t1具有阈值电压vt1。晶体管t2具有阈值电压vt2。阈值电压vt1及vt2的值可不同(不相等值)。举例来说,阈值电压vt2的值可大于阈值电压vt1的值。阈值电压vt1及vt2的值的差允许在不影响(例如,不接通)写入路径(例如通过晶体管t2的路径)上的晶体管t2的情况下读取(例如,感测)存储于读取路径上的晶体管t1中的电荷存储结构202中的信息。这可防止电荷通过写入路径的晶体管t2从电荷存储结构202泄漏。

36.在存储器装置200的结构中,晶体管t1及t2可经形成(例如,设计)使得晶体管t1的阈值电压vt1可小于零伏(例如,vt1<0v)(不管晶体管t1的电荷存储结构202存储的信息的值为何(例如“0”或“1”))且vt1<vt2。当具有值“0”的信息存储于电荷存储结构202中时,电荷存储结构202可处于状态“0”。当具有值“1”的信息存储于电荷存储结构202中时,电荷存储结构202可处于状态“1”。因此,在此结构中,阈值电压vt1及vt2的值之间的关系可表示如下:状态“0”下的vt1<状态“1”下的vt1<0v,且vt2=0v(或替代地,vt2>0v)。

37.在存储器装置200的替代结构中,晶体管t1及t2可经形成(例如,设计)使得状态“0”下的vt1<状态“1”下的vt1,其中状态“0”下的vt1<0v(或替代地,状态“0”下的vt1=0v),状态“1”下的vt1>0v,且vt1<vt2。

38.在另一替代结构中,晶体管t1及t2可经形成(例如,设计)使得vt1(状态“0”下)<vt1(状态“1”下),其中状态“0”下的vt1=0v(或替代地,状态“0”下的vt1>0v,且vt1<vt2)。

39.在存储器装置200的读取操作期间,一次仅选择同一存储器单元群组的一个存储器单元以从选定存储器单元读取信息。举例来说,存储器单元群组2010的存储器单元210、212及214可在读取操作期间一次选择一个以从选定存储器单元读取信息(例如,在此实例中,存储器单元210、212及214中的一者)。在另一实例中,存储器单元群组2011的存储器单元212、213及215可在读取操作期间一次选择一个以从选定存储器单元读取信息(例如,在此实例中,存储器单元212、213及215中的一者)。

40.在读取操作期间,可同时选择(或替代地,可循序选择)共享同一存取线(例如存取线241、242或243)的不同存储器单元群组(例如存储器单元群组2010及2011)的存储器单元。举例来说,可在读取操作期间同时选择存储器单元210及211以从存储器单元210及211读取(例如,同时读取)信息。可在读取操作期间同时选择存储器单元212及213以从存储器单元212及213读取(例如,同时读取)信息。可在读取操作期间同时选择存储器单元214及215以从存储器单元214及215读取(例如,同时读取)信息。

41.在读取操作期间从存储器单元群组2010的选定存储器单元读取的信息的值可基于从包含选定存储器单元(例如存储器单元210、212或214)的晶体管t1及数据线221及221'的读取路径(如上文描述)检测(例如,感测)的电流的值来确定。在读取操作期间从存储器单元群组2011的选定存储器单元读取的信息的值可基于从包含选定存储器单元(例如存储器单元211、213或215)的晶体管t1及数据线222及222'的读取路径检测(例如,感测)的电流的值来确定。

42.存储器装置200可包含检测电路系统(未展示),其可在读取操作期间操作以检测(例如,感测)包含数据线221及221'的读取路径上的电流(例如电流i1,未展示)及检测包含数据线222及222'的读取路径上的电流(例如电流i2,未展示)。检测到的电流的值可基于存储于选定存储器单元中的信息的值。举例来说,取决于存储于存储器单元群组2010的选定存储器单元中的信息的值,数据线221与221'之间的检测到的电流的值(例如电流i1的值)可为零或大于零。类似地,取决于存储于存储器单元群组2011的选定存储器单元中的信息的值,数据线222与222'之间的检测到的电流的值(例如电流i2的值)可为零或大于零。存储器装置200可包含电路系统(未展示)以将检测到的电流的值转译为存储于选定存储器单元中的信息的值(例如“0”、“1”,或多位值的组合)。

43.在存储器装置200的写入操作期间,一次仅可选择同一存储器单元群组的一个存储器单元以将信息存储于选定存储器单元中。举例来说,存储器单元群组2010的存储器单元210、212及214可在写入操作期间一次选择一个以将信息存储于选定存储器单元(例如,在此实例中,存储器单元210、212及214中的一者)中。在另一实例中,存储器单元群组2011的存储器单元212、213及215可在写入操作期间一次选择一个以将信息存储于选定存储器单元(例如,在此实例中,存储器单元211、213及215中的一者)中。

44.在写入操作期间,可同时选择(或替代地,可循序选择)共享同一存取线(例如存取线241、242或243)的不同存储器单元群组(例如存储器单元群组2010及2011)的存储器单元。举例来说,可在写入操作期间同时选择存储器单元210及211以将信息存储(例如,同时存储)于存储器单元210及211中。可在写入操作期间同时选择存储器单元212及213以将信息存储(例如,同时存储)于存储器单元212及213中。可在写入操作期间同时选择存储器单元214及215以将信息存储(例如,同时存储)于存储器单元214及215中。

45.在写入操作期间存储于存储器单元群组2010的选定存储器单元中的信息可通过包含数据线221w及选定存储器单元(例如存储器单元210、212或214)的晶体管t2的写入路径来提供。在写入操作期间存储于存储器单元群组2011的选定存储器单元中的信息可通过包含数据线222w及选定存储器单元(例如存储器单元212、213或215)的晶体管t2的写入路径来提供。如上文描述,存储于存储器单元210到215当中的特定存储器单元中的信息的值(例如二进制值)可基于所述特定存储器单元的电荷存储结构202中的电荷量。

46.在写入操作中,可通过在包含选定存储器单元的晶体管t2及耦合到所述特定存储器单元的数据线(例如数据线221w或222w)的写入路径上施加电压来改变所述特定存储器单元的电荷存储结构202中的电荷量(以反映存储于选定存储器单元中的信息的值)。举例来说,如果存储于存储器单元210、212及214当中的选定存储器单元中的信息具有一个值(例如“0”),那么可在数据线221w上施加具有一个值(例如0v)的电压(例如,将0v提供到信号bl1)。在另一实例中,如果存储于存储器单元210、212及214当中的选定存储器单元中的

信息具有另一值(例如“1”),那么可在数据线221上施加具有另一值的电压(例如正电压)(例如,将正电压提供到信号bl1)。因此,可通过在特定存储器单元的写入路径(其包含晶体管t2)上提供待存储的信息(例如,以电压的形式)来将信息存储(例如,直接存储)于所述特定存储器单元的电荷存储结构202中。

47.图3展示根据本文描述的一些实施例的包含在存储器装置200的读取操作期间使用的实例电压v0、v1、v2及v3的图2的存储器装置200。图3的实例假设存储器单元210是读取(例如,感测)存储(例如,先前存储)于存储器单元210中的信息的读取操作期间的选定存储器单元(例如目标存储器单元)。假设存储器单元212到215是未选定存储器单元。这意味着在图3的实例中,当从存储器单元210读取信息时,不存取存储器单元212到215且不读取存储于存储器单元212到215中的信息。

48.在图3中,电压v0、v1、v2、v3、v4及v5可表示在存储器装置200的读取操作期间施加到相应存取线241、242及243及数据线221、221'、221w、222、222'及222w的不同电压。作为实例,电压v0、v1、v2、v3、v4及v5可分别具有0v(例如接地)、0.5v、0v、0.5v、0v及2v的值。这些值是实例值。可使用不同值。

49.如图3中展示,数据线222及222'中的每一者可施加有电压v4或被置于“浮动”条件。在特定操作期间将特定导电线(例如数据线222或222')置于浮动条件可包含允许所述特定导电线上的电势变化或“浮动”(例如,通过不将所述特定导电线耦合到固定电势(例如接地或其它电压)。在图3的实例读取操作中,图3中的数据线222及222'中的每一者可通过例如使数据线222及222'中的每一者与接地或固定正电压源解耦来置于浮动条件。这允许数据线222及222'中的每一者上的电势在从存储器单元210(此实例中的选定存储器单元)读取信息的操作期间变化(例如,“浮动”)。

50.在图3中展示的读取操作中,电压v1可具有值(电压值)以接通存储器单元210(此实例中的选定存储器单元)的晶体管t1且关断(或保持关断)存储器单元210的晶体管t2。这允许从存储器单元210读取信息。电压v0及v2可具有值,使得存储器单元211到215(此实例中的未选定存储器单元)中的每一者的晶体管t1及t2被关断(例如,保持关断)。电压v3可具有值,使得电流(例如读取电流)可形成于包含数据线221及221'及存储器单元210的晶体管t1的读取路径上。这允许检测耦合到存储器单元210的读取路径上的电流。存储器装置200的检测电路系统(未展示)可操作以将检测到的电流的值(在从选定存储器单元读取信息期间)转译为从选定存储器单元读取的信息的值(例如“0”、“1”,或多位值的组合)。在图3的实例中,可将数据线221及221'上的检测到的电流的值转译为从存储器单元210读取的信息的值。

51.在图3中展示的读取操作中,施加到相应存取线241、242及243的电压可致使除存储器单元210的晶体管t1之外的存储器单元212到215中的每一者的晶体管t1及t2关断(或保持关断)。取决于存储器单元210的晶体管t1的阈值电压vt1的值,存储器单元210的晶体管t1可或可不接通。举例来说,如果存储器装置200的存储器单元(例如210到215)中的每一者的晶体管t1经配置(例如,构造)使得晶体管t1的阈值电压小于零(例如,vt1<0v)(不管存储于相应存储器单元210中的信息的值(例如状态)为何),那么在此实例中,存储器单元210的晶体管t1可接通且在数据线221与221'之间传导电流(通过存储器单元210的晶体管t1)。存储器装置200可基于读取数据线221与221'之间的电流的值来确定存储于存储器单元210

中的信息的值。如上文描述,存储器装置200可包含检测电路系统以在读取操作期间测量数据线221与221'之间(或数据线222与222之间)的电流的值。

52.图4展示根据本文描述的一些实施例的包含在存储器装置200的写入操作期间使用的实例电压v5、v6、v7及v8的图2的存储器装置200。图4的实例假设存储器单元210及211是将信息存储于存储器单元210及211中的写入操作期间的选定存储器单元(例如目标存储器单元)。假设存储器单元212到215是未选定存储器单元。这意味着在图4的实例中,当将信息存储于存储器单元210及211中时,不存取存储器单元212到215且所存储的信息不存储于存储器单元212到215中。

53.在图4中,电压v5、v6、v7及v8可表示在存储器装置200的写入操作期间施加到相应存取线241、242及243及数据线221w及222w的不同电压。作为实例,电压v5及v6可分别具有值2.5v及0v。取决于存储于存储器单元210及211中的信息的值(例如“0”或“1”),电压v7及v8中的每一者的值可小于、等于或大于电压v5的值。此描述中使用的特定电压值仅为实例值。可使用不同值。

54.取决于存储于存储器单元210及211中的信息的值(例如“0”或“1”),电压v7及v8的值可相同或不同。举例来说,如果存储器单元210及211将存储具有相同值的信息,那么电压v7及v8的值可相同(例如,v7=v8)。作为实例,如果存储于每一存储器单元210及211中的信息为“0”,那么v7=v8=0v且v5=2.5v,及如果存储于每一存储器单元210及211中的信息为“1”,那么v7=v8=1v到3v且v5=2.5v。

55.在另一实例中,如果存储器单元210及211将存储具有不同值的信息,那么电压v7及v8的值可不同(例如,v7≠v8)。作为实例,如果“0”将存储于存储器单元210中且“1”将存储于存储器单元211中),那么v7=0v,v8=1v到3v,且v5=2.5v。作为另一实例,如果“1”将存储于存储器单元210中且“0”将存储于存储器单元211中),那么v7=1v到3v,v8=0v,且v5=2.5v。

56.本文使用1v到3v的电压范围作为实例。可使用不同电压范围。此外,不是将0v(例如,v7=0v或v8=0v)施加到特定写入数据线(例如数据线221w或222w)来将具有值“0”的信息存储到耦合到所述特定写入数据线的存储器单元(例如存储器单元210或211),而是可将正电压(例如,v7>0v或v8>0v)施加到所述特定数据线。

57.在图4的存储器装置200的写入操作中,电压v6可具有值,使得存储器单元212到215(此实例中的未选定存储器单元)中的每一者的晶体管t1及t2被关断(例如,保持关断)。电压v5可具有值以接通存储器单元210及211中的每一者(此实例中的选定存储器单元)的晶体管t2且在存储器单元210的电荷存储结构202与数据线221w之间形成写入路径及在存储器单元211的电荷存储结构202与数据线222w之间形成写入路径。可在存储器单元210的电荷存储结构202与数据线221w之间形成电流(例如写入电流)。此电流可影响(例如,改变)存储器单元210的电荷存储结构202上的电荷量以反映存储于存储器单元210中的信息的值。可在存储器单元211的电荷存储结构202与数据线222w之间形成电流(例如另一写入电流)。此电流可影响(例如,改变)存储器单元211的电荷存储结构202上的电荷量以反映存储于存储器单元211中的信息的值。

58.在图4的实例写入操作中,电压v7的值可致使存储器单元210的电荷存储结构202放电或充电,使得存储器单元210的电荷存储结构202上的所得电荷(例如在放电或充电动

作之后剩余的电荷)可反映存储于存储器单元210中的信息的值。类似地,在此实例中,电压v8的值可致使存储器单元211的电荷存储结构202放电或充电,使得存储器单元211的电荷存储结构202上的所得电荷(例如在放电或充电动作之后剩余的电荷)可反映存储于存储器单元211中的信息的值。

59.图4的实例写入操作假设选择(例如,同时选择)存储器单元210及211来存储(例如,同时存储)信息。在另一写入操作中,可选择存储器单元210或存储器单元211来存储信息。举例来说,在另一写入操作中,可选择存储器单元210,且存储器单元211到215可为未选定存储器单元。在此写入操作中,可向电压v8施加电压(例如写入抑制电压(例如,v8=v5)),使得当将信息存储于存储器单元210(选定存储器单元)中时,抑制存储器单元211存储信息。类似地,如果选择存储器单元211来存储信息,且存储器单元210及212到215是未选定存储器,那么可向电压v7施加电压(例如写入抑制电压(例如,v7=v5)),使得当将信息存储于存储器单元211(选定存储器单元)中时,抑制存储器单元210存储信息。

60.图5到图10展示根据本文描述的一些实施例的图2的存储器装置200的结构关于x、y及z方向的不同视图。图5展示存储器装置200关于x

‑

z方向的侧视图。图6、图7、图8、图9及图10分别展示沿图5的线6

‑

6、7

‑

7、8

‑

8、9

‑

9及10

‑

10截取的视图。

61.为简单起见,图5到图10聚焦于存储器单元210及211的结构。图2的存储器装置200的其它存储器单元(例如存储器单元212、213、214及215)的结构可类似于或等同于图5中展示的存储器单元210及211的结构。在图5到图10(其展示存储器装置200的物理结构)及图2(其以电路示意形式展示存储器装置200)中,相同元件被给予相同元件符号。

62.以下描述参考图5到图10。为简单起见,图5到图10的描述中不重复相同元件的详细描述。同样为简单起见,从图5到图10中展示的元件省略横截面线(例如剖面线)。存储器装置200的一些元件可从图式的特定图省略以免模糊所述特定图中描述的元件的描述。图5到图10中所展示的元件的尺寸未按比例绘制。

63.如图5中展示,存储器装置200可包含其上方可形成存储器单元210及211(例如,关于衬底599垂直形成)的衬底599。衬底599可为半导体衬底(例如基于硅的衬底)或其它类型的衬底。z方向可为垂直于衬底599的方向(例如相对于衬底599的垂直方向)。x方向及y方向彼此垂直且垂直于z方向。

64.如图5中展示,存储器装置200可包含电介质526以使存储器单元210及211彼此电分离。电介质526可包含二氧化硅。

65.数据线221、221'、221w、222、222'及222w(分别与信号bl1、bl1*、blw、bl2、bl2*、bl2w相关联)中的每一者可具有y方向上的长度、x方向上的宽度及z方向上的厚度。数据线221、221'、221w、222、222'及222w中的每一者可包含可经构造为导电线(例如导电区)的导电材料(或材料的组合)。用于数据线221、221'、221w、222、222'及222w的实例材料包含金属、导电掺杂多晶硅或其它导电材料。

66.如图5中展示,数据线221、221'及221w可包含位于存储器装置200的不同层级(关于z方向)中且彼此电分离的相应导电区。举例来说,数据线221'可包含位于衬底599上方的层级中的导电区(形成数据线221'的导电材料的部分)。数据线221可包含位于数据线221'的导电区上方的层级中的导电区(形成数据线221的导电材料的部分)。数据线221w可包含位于数据线221的导电区上方的层级中的导电区(形成数据线221w的导电材料的部分)。

67.类似地,数据线222、222'及222w可包含位于存储器装置200的不同层级(关于z方向)中且彼此电分离的相应导电区。举例来说,数据线222'可包含位于衬底599上方的层级(其是与数据线221'相同的层级)中的导电区(形成数据线222'的导电材料的部分)。数据线222可包含位于数据线222'的导电区上方的层级(其是与数据线221相同的层级)中的导电区(形成数据线222的导电材料的部分)。数据线222w可包含位于数据线222的导电区上方的层级(其是与数据线221w相同的层级)中的导电区(形成数据线222w的导电材料的部分)。

68.存取线241(与信号wl1相关联)可由部分541a、541b、541c及541d的组合构造(可包含部分541a、541b、541c及541d的组合)。部分541a、541b、541c及541d中的每一者可包含导电材料(或材料的组合),其可经构造为具有在x方向上连续延伸的长度的导电线(例如导电区)。在图5中,部分541a、541b、541c及541d经部分展示以免妨碍存储器装置200的其它元件的一些部分。

69.部分541a、541b、541c及541d中的每一者可包含一片(例如一层)导电材料(例如金属、导电掺杂多晶硅或其它导电材料)。部分541a、541b、541c及541d中的每一者可具有在x方向上连续延伸的长度(图5中展示)、z方向上的宽度(图5中展示)及y方向上的厚度(图6及图8中展示)。

70.部分541a、541b、541c及541d可彼此电耦合。举例来说,如图5中展示,存取线241可包含可将部分541a电耦合到部分541b的部分541e及可将部分541c电耦合到部分541d的部分541f。

71.部分541a到541f也可彼此电耦合。举例来说,存储器装置200可包含可将部分541e电耦合到部分541f的导电材料(例如,未展示),使得部分541a到541f彼此电短路且相同(例如信号wl1)可同时施加到部分541a到541f。

72.在存储器装置200的替代结构中,可省略部分541a、541c及541e的组合或部分541b、541d及541f的组合,使得存取线241可仅包含部分541a、541c及541e的组合或部分541b、541d及541f的组合。

73.如图5中展示,存储器装置200可包含形成于衬底599的一部分上方的电介质590及形成于电介质590上方的电介质591。电介质590及591中的每一者可包含氧化硅。电介质590可电分离数据线221'及222'与衬底599。图5将电介质590及591展示为分离电介质。然而,电介质590及591可为相同电介质(例如单个电介质)。

74.存储器装置200可包含部分502a及502b。部分502a及502b中的每一者可包含一片(例如一层)半导体材料(例如掺杂或未掺杂多晶硅)、一片(例如一层)金属或可俘获电荷的一片材料(或材料)。如上文参考图2描述,存储器单元210到215中的每一者可包含电荷存储结构202,其可形成相应存储器单元的存储器元件。在图5中,部分502a及502b是存储器单元210的电荷存储结构202(图2)的部分。因此,部分502a及502b是存储器单元210的存储器元件的部分。类似地,存储器装置200可包含作为存储器单元211的存储器元件的部分的部分503a及503b。

75.图5展示其中部分502a、502b、503a及503b中的每一者(例如部分502a、502b、503a及503b中的每一者的底部边缘)接触电介质591(例如,延伸到且触碰电介质591的顶面)的实例。然而,在替代结构中,部分502a、502b、503a及503b中的每一者(例如部分502a、502b、503a及503b中的每一者的底部边缘)可不接触电介质591(例如,可不触碰电介质591的顶

面)。在此替代结构中,部分502a、502b、503a及503b中的每一者(例如部分502a、502b、503a及503b中的每一者的底部边缘)可通过额外电介质来与电介质591分离(例如,与介电591的表面分离)(例如,额外电介质可在部分502a、502b、503a及503b中的每一者的底部边缘与电介质591的顶面之间)。

76.图5展示其中部分502a、502b、503a及503b中的每一者的底部边缘与部分541a及541b中的每一者的顶部边缘相距一特定距离(例如图5中展示的距离)的实例。然而,部分502a、502b、503a及503b中的每一者的底部边缘与部分541a及541b中的每一者的顶部边缘之间的距离可变化。

77.存储器装置200可包含电耦合到(例如,直接耦合到(接触))数据线221w且电耦合到(例如,直接耦合到)部分502a及502b(其形成存储器单元210的电荷存储结构202)的材料520。材料520可形成存储器单元210的晶体管t2的源极(例如源极端子)、漏极(例如漏极端子)及源极与漏极之间沟道区(例如写入沟道区)。因此,如图5中展示,存储器单元210的晶体管t2的源极、沟道区及漏极可由例如材料520的相同材料的单个片(例如单个层)(或替代地,相同材料组合的单个片)形成。因此,存储器单元210的晶体管t2的源极、漏极及沟道可由相同导电类型(例如n型或p型)的相同材料(例如材料520)形成。

78.存储器装置200可包含电耦合到(例如,直接耦合到(接触))数据线222w且电耦合到(例如,直接耦合到)部分503a及503b(其形成存储器单元210的电荷存储结构202)的材料521。材料521可形成存储器单元211的晶体管t2的源极(例如源极端子)、漏极(例如漏极端子)、源极与漏极之间沟道区(例如写入沟道区)。因此,如图5中展示,存储器单元211的晶体管t2的源极、沟道区及漏极可由例如材料521的相同材料的单个片(例如单个层)(或替代地,相同材料组合的单个片)形成。

79.材料520及521可相同。举例来说,材料520及521中的每一者可包含一片(例如一层)半导体材料。所述一片半导体材料可包含一片氧化物材料。用于材料520及521的氧化物材料的实例包含半导电氧化物材料、透明导电氧化物材料及其它氧化物材料。

80.作为实例,材料520及521中的每一者可包含以下中的至少一者:氧化锌锡(zto)、氧化铟锌(izo)、氧化锌(zno

x

)、氧化铟镓锌(igzo)、氧化铟镓硅(igso)、氧化铟(ino

x

、in2o3)、氧化锡(sno2)、氧化钛(tio

x

)、氮氧化锌(zn

x

o

y

n

z

)、氧化镁锌(mg

x

zn

y

o

z

)、氧化铟锌(in

x

zn

y

o

z

)、氧化铟镓锌(in

x

ga

y

zn

z

o

a

)、氧化锆铟锌(zr

x

in

y

zn

z

o

a

)、氧化铪铟锌(hf

x

in

y

zn

z

o

a

)、氧化锡铟锌(sn

x

in

y

zn

z

o

a

)、氧化铝锡铟锌(al

x

sn

y

in

z

zn

a

o

d

)、氧化硅铟锌(si

x

in

y

zn

z

o

a

)、氧化锌锡(zn

x

sn

y

o

z

)、氧化铝锌锡(al

x

zn

y

sn

z

o

a

)、氧化镓锌锡(ga

x

zn

y

sn

z

o

a

)、氧化锆锌锡(zr

x

zn

y

sn

z

o

a

),及氧化铟镓硅(ingasio),及磷化镓(gap)。

81.在存储器装置200中使用上列材料为存储器装置200提供改进及益处。举例来说,在从选定存储器单元(例如存储器单元210或211)读取信息的读取操作期间,来自选定存储器单元的电荷存储结构202的电荷可泄漏到选定存储器单元的晶体管t2。针对晶体管t2的沟道区(其由材料520或521形成)使用上列材料可减少或防止此泄漏。这提高从选定存储器单元读取的信息的准确性且改进存储于本文描述的存储器装置(例如存储器装置200)的存储器单元中的信息的留存性。

82.上列材料是用于材料520及521的实例。然而,可使用与上列材料不同的其它材料(例如相对较高带隙材料)。

83.在图5中,材料520及存储器单元210的电荷存储结构202(其包含部分502a及502b)及材料520可彼此电耦合(例如,直接耦合),使得材料520可接触存储器单元210的电荷存储结构202,且存储器单元210的电荷存储结构202与材料520之间无中间材料。在另一实例中,材料520可电耦合到存储器单元210的电荷存储结构202,使得材料520不直接耦合到(不接触)存储器单元210的电荷存储结构202,但材料520通过存储器单元210的电荷存储结构202与材料520之间的中间材料(例如导电材料,图5中未展示)来耦合到(例如,间接接触)存储单元210的电荷存储结构202。

84.如图5中展示,存储器单元210可包含电耦合到数据线221及221'的部分510。部分510可包含一片(例如一层)半导体材料或一片(例如一层)金属。用于部分510的实例半导体材料包含多晶硅(例如未掺杂或掺杂多晶硅)、锗、硅锗或其它半导体材料。

85.如上文参考图2描述,存储器单元210的晶体管t1包含可为存储器单元210的读取路径的部分的沟道区(例如读取沟道区)。在图5中,部分510可为存储器单元210的晶体管t1的沟道区。因此,部分510可为存储器单元210的读取路径的部分且可在从存储器单元210读取信息的读取操作期间携载电流(例如读取电流)。举例来说,在从存储器单元210读取信息的读取操作期间,部分510可在数据线221与221'之间传导电流(例如读取电流)。

86.存储器单元210可包含电分离材料520与数据线221及部分510的电介质(例如二氧化硅材料)515。如图5中展示,部分502a通过电介质515的部分与部分510的一侧(例如图5的视图中的x方向上的左侧)相邻及电分离。部分502b通过电介质515的另一部分与部分510的另一侧(例如图5的视图中的x方向上的右侧)相邻及电分离。

87.如图5中展示,部分541a的部分可横跨(例如y方向上的前侧)部分510的部分(存储器单元210的晶体管t1的读取沟道区的部分)。部分541b的部分可横跨(例如y方向上的后侧(与前侧相对))部分510的部分。部分541a的部分还可横跨(例如y方向上的前侧)部分511的部分(存储器单元211的晶体管t1的读取沟道区的部分)。部分541b的部分也可横跨(例如y方向上的后侧(与前侧相对))部分511的部分。

88.部分541c的部分可横跨(例如y方向上的前侧)材料520的部分(存储器单元210的晶体管t2的导线沟道区的部分)。部分541d的部分可横跨(例如y方向上的后侧(与前侧相对))材料520的部分。部分541a的部分还可横跨(例如y方向上的前侧)材料的部分(存储器单元211的晶体管t2的写入沟道区的部分)。部分541d的部分还可横跨(例如y方向上的后侧(与前侧相对))材料521的部分。

89.如图6到图10中展示,存储器装置200可包含电介质515e及515f(例如栅极氧化物区)以电分离存取线241的部分541a到541d(在y方向上)与存储器单元210及211的其它元件。

90.如图10中展示,部分541a及541b可为存储器单元210的部分510(例如晶体管t1的读取沟道)的相邻相应侧(例如x方向上的左侧及右侧),部分541c及541d可为存储器单元210的材料520(例如晶体管t2的写入沟道)的相邻相应侧(例如x方向上的左侧及右侧)。举例来说,部分541a可相邻于部分510的一侧(例如图10的视图中的x方向上的右侧),且部分541b可相邻于部分510的另一侧(例如图10的视图中的x方向上的左侧)。在另一实例中,部分541c可相邻于材料520的一侧(例如图10的视图中的x方向上的右侧),且部分541d可相邻于材料520的另一侧(例如图10的视图中的x方向上的左侧)。

91.以上描述聚焦于存储器单元210的结构。存储器单元211可包含以与上文描述的存储器单元210的元件类似或等同的方式构造的元件。举例来说,如图5到图7中展示,存储器单元211可包含电荷存储结构202、沟道区(例如写入沟道区)521、部分511a、511b及511c(例如读取沟道区)及电介质525a、525b及525c。

92.图11a、图11b及图11c展示根据本文描述的一些实施例的包含多个层面的存储器单元的存储器装置1100的结构的不同视图。图11a展示存储器装置1100的分解图(例如,在z方向上)。图11b展示存储器装置110在x方向及z方向上的侧视图(例如横截面图)。图11c展示存储器装置1100在y方向及z方向上的侧视图(例如横截面图)。

93.如图11a中所展示,存储器装置1100可包含在分解图中彼此分离展示以帮助容易地观看存储器装置1100的层面结构的层面(存储器单元的层面)11050、11051、11052及11053。实际上,层面11050、11051、11052及11053可以一布置彼此附接,其中在衬底(例如半导体(例如硅)衬底)1199上方层面可彼此上下形成(例如,堆叠)。举例来说,如图11a中展示,层面11050、11051、11052及11053可在垂直于衬底1199的z方向上形成(例如,在关于衬底1199的z方向上垂直形成)。

94.如图11a中展示,层面11050、11051、11052及11053中的每一者可具有在x方向及y方向上布置的存储器单元(例如,在x方向上布置成行及在y方向上布置成列)。举例来说,层面11050可包含存储器单元11100、11110、11120及11130(例如,布置成行)、存储器单元11200、11210、11220及11230(例如,布置成行)及存储器单元11300、11310、11320及11330(例如,布置成行)。

95.层面11051可包含存储器单元11101、11111、11121及11131(例如,布置成行)、存储器单元11201、11211、11221及11231(例如,布置成行)及存储器单元11301、11311、11321及11331(例如,布置成行)。

96.层面11052可包含存储器单元11102、11112、11122及11132(例如,布置成行)、存储器单元11202、11212、11222及11232(例如,布置成行)及存储器单元11302、11312、11322及11332(例如,布置成行)。

97.层面11053可包含存储器单元11103、11113、11123及11133(例如,布置成行)、存储器单元11203、11213、11223及11233(例如,布置成行)及存储器单元11303、11313、11323及11333(例如,布置成行)。

98.如图11a中展示,层面11050、11051、11052及11053可分别位于(例如,在z方向上垂直形成于)存储器装置1100的层级(例如部分)1150、1151、1152及1153上。层面11050、11051、11052及11053的布置形成存储器装置1100的存储器单元的3维(3d)结构,其中存储器装置1100的存储器单元的不同层级可位于(例如,形成于)存储器装置1100的不同层级(例如不同垂直部分)1150、1151、1152及1153中。

99.层面11050、11051、11052及11053可一次一个层面形成。举例来说,层面11050、11051、11052及11053可依层面11050、11051、11052及11053的顺序依次形成(例如,首先形成层面11051且最后形成层面11053)。在此实例中,一个层面(例如层面11051)的存储器单元可在形成另一层面(例如层面11050)的存储器单元之后或在形成另一层面(例如层面11052)的存储器单元之前形成。替代地,层面11050、11051、11052及11053可同时(例如,一齐)形成,使得层面11050、11051、11052及11053的存储器单元可同时形成。举例来说,存储器装置1100的

层级1150、1151、1152及1153中的存储器单元可同时形成。

100.层面11050、11051、11052及11053中的每一者的存储器单元的结构可包含上文参考图1到图10描述的存储器单元的结构。举例来说,层面11050、11051、11052及11053的存储器单元的结构可包含存储器装置200的存储器单元的结构。

101.存储器装置1100可包含数据线(例如位线)及存取线(例如字线)以存取层面11050、11051、11052及11053的存储器单元。为简单起见,从图11a省略存储器单元的数据线及存取线。然而,存储器装置1100的数据线及存取线可分别类似于上文参考图1到图10描述的存储器装置的数据线及存取线。

102.图11a展示包含四个层面(例如11050、11051、11052及11053)作为实例的存储器装置1100。然而,层面的数目可不同于四个。图11a展示包含一个层级(例如层)的存储器单元作为实例的层面11050、11051、11052及11053中的每一者。然而,层面中的至少一者(例如层面11050、11051、11052及11053中的一或多者)可具有两个(或更多个)层级的存储器单元。图11a展示其中层面11050、11051、11052及11053中的每一者在x方向上包含四个存储器单元(例如,呈一行)及在y方向上包含三个存储器单元(例如,呈一列)的实例。然而,一行、一列或两者中的存储器单元的数目可变化。

103.设备(例如存储器装置100、200及1100)及方法(例如存储器装置100及200的操作)的说明希望提供各种实施例的结构的大体理解,且不希望提供可利用本文描述的结构的设备的所有元件及特征的完整描述。本文的设备例如指代装置(例如存储器装置100、200及1100中的任何者)或系统(例如可包含存储器装置100、200及1100中的任何者的电子产品)。

104.上文参考图1到图10描述的组件中的任何者可以各种方式实施,其包含经由软件模拟。因此,设备(例如存储器装置100、200及1100)或上述这些存储器装置中的每一者的部分全部可在本文中特性化为“多个模块”(或“模块”)。此类模块可根据各种实施例的特定实施方案的期望及/或需要来包含硬件电路系统、单处理器及/或多处理器电路、存储器电路、软件程序模块及对象及/或固件及其组合。举例来说,此类模块可包含于系统操作模拟封装中,例如软件电信号模拟封装、电力使用及范围模拟封装、电容

‑

电感模拟封装、电力/散热模拟封装、信号传输

‑

接收模拟封装及/或用于操作或模拟各种潜在实施例的操作的软件及硬件的组合。

105.本文描述的存储器装置(例如存储器装置100及200)可包含于例如高速计算机、通信及信号处理电路系统、单处理器或多处理器模块、单个嵌入式处理器或多个嵌入式处理器、多核处理器、消息信息交换机及专用模块(包含多层、多芯片模块)的设备(例如电子电路系统)中。此类设备可进一步作为子组件包含于各种其它设备(例如电子系统)内,例如电视、蜂窝电话、个人计算机(例如膝上型计算机、桌上型计算机、手持计算机、平板计算机等)、工作站、无线电、视频播放器、音频播放器(例如mp3(动画专家群组、音频层3)播放器)、交通工具、医疗装置(例如心脏监护仪、血压监护仪等)、机顶盒及其它。

106.上文参考图1到图10描述的实施例包含设备及形成设备的方法。设备中的一者包含:第一导电区,其位于衬底上方;第二导电区,其位于第一导电区上方;第三导电区,其位于第二导电区上方,第一、第二及第三导电区彼此电分离;及存储器单元,其耦合到第一、第二及第三区。存储器单元包含:第一材料,其在第一与第二导电区之间且电耦合到第一及第二导电区;第二材料,其位于第一导电区及第一材料上方;及存储器元件。第二材料与第一

材料电分离且电耦合到第三导电区。存储器元件电耦合到第二材料且与第一材料及第一及第二导电区电分离。描述包含额外设备及方法的其它实施例。

107.在具体实施方式及权利要求书中,关于两个或更多个元件(例如材料)使用的术语“在

…

上”(一者“在另一者上”)意味着元件之间(例如材料之间)存在至少一些接触。术语“在

…

上方”意味着元件(例如材料)紧密接近,但可能具有一或多个额外中介元件(例如材料),使得可能但非必需接触。“在

…

上”及“在

…

上方”均不暗示本文使用的任何方向性,除非如此说明。

108.在具体实施方式及权利要求书中,由术语

“…

中的至少一者”接合的项目列表可意味着列项的任一组合。举例来说,如果列出项目a及b,那么短语“a及b中的至少一者”意味着仅a、仅b或a及b。在另一实例中,如果列出项目a、b及c,那么短语“a、b及c中的至少一者”意味着仅a、仅b、仅c、a及b(排除c)、a及c(排除b)、b及c(排除a)或a、b及c所有。项目a可包含单个元件或多个元件。项目b可包含单个元件或多个元件。项目c可包含单个元件或多个元件。

109.在具体实施方式及权利要求书中,由术语

“…

中的一者”接合的项目列表可意味着列表项目中的仅一者。举例来说,如果列出项目a及b,那么短语“a及b中的一者”意味着仅a(排除b)或仅b(排除a)。在另一实例中,如果列出项目a、b及c,那么短语“a、b及c中的一者”意味着仅a、仅b或仅c。项目a可包含单个元件或多个元件。项目b可包含单个元件或多个元件。项目c可包含单个元件或多个元件。

110.上文描述及图式说明本发明标的物的一些实施例以使所属领域的技术人员能够实践本发明标的物的实施例。其它实施例可并入结构、逻辑、电气、过程及其它改变。实例仅代表可能变化。一些实施例的部分及特征可包含于其它实施例的部分及特征中或替代其它实施例的部分及特征。所属领域的技术人员将在阅读及理解上文描述之后明白许多其它实施例。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1