半导体模块、其制造方法以及半导体模块的安装体与流程

1.本发明涉及半导体模块、其制造方法以及半导体模块的安装体。

背景技术:

2.以往,作为存储装置,已知有dram(dynamicrandom access memory:动态随机存取存储器)等易失性存储器。对于dram,要求其大容量化而能够足以承受运算装置(以下称为逻辑芯片)的高性能化和数据量的增大。因此,一直在通过存储器(存储单元阵列、存储芯片)的微细化以及单元的平面增设来谋求大容量化。另一方面,由于微细化导致对噪声的脆弱性、管芯(die)面积的增加等,这种大容量化达到了极限。

3.因此,最近开发了层叠多个平面式存储器来进行三维化(3d化)从而实现大容量化的技术。此外,提出了通过重叠配置多个芯片来减小多个芯片的设置面积的半导体模块(例如参考专利文献1)。

4.现有技术文献

5.专利文献

6.专利文献1:美国专利申请公开第2015/0255411号说明书。

技术实现要素:

7.发明要解决的问题

8.在专利文献1中,露出了有效表面(active surface)的第二芯片配置在封装基板的第一面上。此外,在专利文献1中,第一芯片被配置成有效表面与封装基板的第一面和第二芯片的有效表面相向。而且,在专利文献1中,第一芯片与封装基板的第一面和第二芯片的有效表面电连接。

9.像这样,专利文献1公开的半导体模块能够大容量化。另一方面,专利文献1公开的半导体模块由于使用封装基板,因此制造成本比较高。因此,如果能够降低制造成本则更优选。

10.本发明的目的在于,提供能够降低制造成本的半导体模块、其制造方法以及半导体模块的安装体。

11.用于解决问题的方案

12.本发明涉及一种具有层叠的多个管芯的半导体模块,其包括:第一管芯;第二管芯,其在与层叠方向交叉的方向与所述第一管芯排列设置;第三管芯,其横跨所述第一管芯和所述第二管芯在层叠方向上配置,并且与相向的所述第一管芯和第二管芯的布线面电连接;突出端子,其从所述第一管芯和所述第二管芯的布线面突出,并且在与层叠方向交叉的方向上与所述第三管芯的至少一个侧面相邻的空间区域中突出;再布线层,其与所述突出端子重叠配置。

13.此外,优选所述第二管芯是供电管芯,其将由所述突出端子供给的电力供给至所述第三管芯。

14.此外,优选所述第二管芯在与层叠方向交叉的方向夹着所述第一管芯成对配置,所述第三管芯横跨所述第一管芯和所述成对配置的所述第二管芯成对配置。

15.此外,优选所述第三管芯具有在层叠方向与所述第二管芯重叠的阵列部和在层叠方向与所述第一管芯重叠的接口部。

16.此外,优选半导体模块还具有作为所述第三管芯的散热路径与所述第三管芯重叠的散热部。

17.此外,优选半导体模块还具有在层叠方向排列设置在所述再布线层的多个外部端子,所述外部端子具有连接端子和非连接端子,所述连接端子隔着所述再布线层与所述突出端子电连接,所述非连接端子在层叠方向上配置在与所述第三管芯重叠的位置且不与所述突出端子电连接。

18.此外,优选所述散热部包括在所述再布线层中且与所述第三管芯重叠的重合部和所述非连接端子。

19.此外,优选所述重合部具有断续地重叠的金属层以及连接相邻的所述金属层之间的散热导孔。

20.此外,优选所述散热部具有贯通所述再布线层的热扩散用构件。

21.此外,本发明涉及一种半导体模块的安装体,其具有上述的半导体模块以及安装基板,所述安装基板具有在层叠方向贯通的多个贯通端子,所述贯通端子与所述外部端子分别连接。

22.此外,本发明涉及一种半导体模块的制造方法,用于制造具有层叠的多个管芯的半导体模块,包括:在第一管芯和第二管芯的一个面形成突出端子的工序;将所述第一管芯和所述第二管芯排列设置在支承基板的工序;横跨所述第一管芯和所述第二管芯来配置第三管芯的工序;将所述第一管芯、所述第二管芯、所述第三管芯、以及所述突出端子塑封的工序;形成再布线层的工序,所述再布线层横跨所述第三管芯的露出面配置,并且与所述突出端子电连接;去除所述支承基板的工序。

23.此外,优选在将所述第一管芯和所述第二管芯排列设置在所述支承基板的工序中,在所述支承基板中配置所述第一管芯和所述第二管芯的多个组。

24.此外,优选在半导体模块的制造方法中,在所述塑封工序之后、所述形成再布线层的工序之前,还包括使所述第三管芯和所述突出端子露出的抛光工序。

25.此外,优选半导体模块的制造方法还包括将贯通所述再布线层的热扩散用构件配置在与所述第三管芯重叠的位置的工序。

26.发明效果

27.根据本发明,能够提供一种能够降低制造成本的半导体模块、其制造方法以及半导体模块的安装体。

附图说明

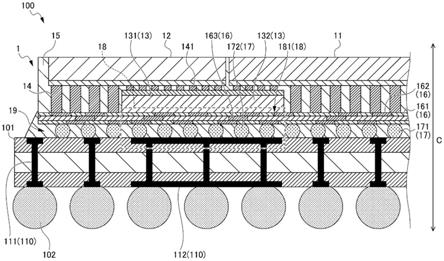

28.图1是表示本发明的第一实施方式涉及的半导体模块以及半导体模块的安装体的概略剖视图。

29.图2是表示第一实施方式的半导体模块的制造途中的概略剖视图。

30.图3是表示第一实施方式的半导体模块的制造途中的概略剖视图。

31.图4是表示第一实施方式的半导体模块的制造途中的概略立体图。

32.图5是表示第一实施方式的半导体模块的制造途中的概略剖视图。

33.图6是表示第一实施方式的半导体模块的制造途中的概略剖视图。

34.图7是表示第一实施方式的半导体模块的制造途中的概略剖视图。

35.图8是表示本发明的第二实施方式的半导体模块的散热部的概略结构图。

36.图9是表示本发明的第三实施方式的半导体模块的散热部的概略剖视图。

37.图10是表示本发明的变形例涉及的半导体模块的散热部的概略剖视图。

具体实施方式

38.下面,参照图1至图9来说明本发明的各实施方式涉及的半导体模块1、其制造方法以及半导体模块1的安装体100。

39.各实施方式涉及的半导体模块1例如是将运算装置(第一管芯11,以下称为逻辑芯片)和作为包含单层或层叠型ram的ram模块的ram部13配置在再布线层16上的sip(system in a package:系统级封装)。虽然不是特别限定,但半导体模块1是在具有焊球102的安装基板101上安装的半导体模块的安装体100,其配置在基板(未图示的主板等)上,使用焊球102(电源球等)而被电连接。或者,半导体模块1也可以不经由安装基板101和焊球102而直接配置在基板上。半导体模块1从基板得到电力,并且能够在基板之间收发数据。另外,在以下各实施方式中,将半导体模块1的层叠方向(厚度方向)作为层叠方向c进行说明。此外,沿着半导体模块1的层叠方向c,将配置有基板的一侧作为下方进行说明。沿着半导体模块1的层叠方向c,将配置有第一管芯11的一侧作为上方进行说明,

40.[第一实施方式]

[0041]

下面,参照图1至图7来说明第一实施方式涉及的半导体模块1、其制造方法以及半导体模块1的安装体100。

[0042]

首先,对本实施方式涉及的半导体模块1的结构进行说明。

[0043]

半导体模块1具有层叠的多个管芯。如图1所示,半导体模块1具有第一管芯11、第二管芯12、第三管芯13、突出端子14、塑封材料15、再布线层16、外部端子17以及散热部18。

[0044]

第一管芯11例如是逻辑芯片(mpu)。在本实施方式中,第一管芯11构成为例如正视呈矩形。第一管芯11配置成布线面(未图示)朝向下方。

[0045]

第二管芯12例如是供电用的管芯。第二管芯12在与层叠方向交叉的方向与第一管芯11排列设置。在本实施方式中,第二管芯12例如以正视呈矩形而构成。此外,在本实施方式中,第二管芯12在与层叠方向交叉的方向夹着第一管芯11成对配置。第二管芯12与第一管芯11相同地,配置成布线面(未图示)朝向下方。第二管芯12将由后述的突出端子14供给的电力供给至后述的第三管芯13。

[0046]

第三管芯13例如是dram。第三管芯13横跨第一管芯11和第二管芯12在层叠方向上配置。第三管芯13配置成布线面(未图示)朝向上方。第三管芯13与相向的第一管芯11以及第二管芯12的布线面电连接。第三管芯13例如通过从第一管芯11和第二管芯12各自的布线面延伸的连接端子141连接。具体地,第三管芯13使用从第一管芯11和第二管芯12各自的布线面延伸的柱(cu柱)、凸块等来连接。在本实施方式中,第三管芯13具有阵列部131和接口部132。

[0047]

阵列部131是第三管芯13的一部分,是配置有存储单元阵列的部位。在本实施方式中,阵列部131在层叠方向上配置在与第二管芯12重叠的位置。具体地,阵列部131在层叠方向上配置在能够接收来自第二管芯12的电力的位置。

[0048]

接口部132是第三管芯13的一部分,是配置有存储器接口的部位。在本实施方式中,接口部132在层叠方向上配置在与第一管芯11重叠的位置。具体地,接口部132在层叠方向上配置在能够接收来自第一管芯11的电力的位置。此外,接口部132在层叠方向经由连接端子141与第一管芯11直接连接。

[0049]

突出端子14是从第一管芯11和第二管芯12各自的布线面突出的导电性端子。突出端子14例如从第一管芯11和第二管芯12各自的布线面中不与第三管芯13重叠的平面区域突出。换言之,突出端子14在与层叠方向交叉的方向上与第三管芯13的至少一个侧面相邻的空间区域中突出。突出端子14具有从第一管芯11或第二管芯12的布线面延伸至与第三管芯13的上表面的高度相同或大致相同的高度的长度。突出端子14作为第一管芯11和第二管芯12的信号线、供电线或接地线发挥功能。在本实施方式中,突出端子14在围绕第三管芯13的四周的侧面的空间区域内从第一管芯11和第二管芯12的布线面突出。

[0050]

塑封材料15例如是环氧树脂。塑封材料15在与层叠方向c交叉的方向覆盖第一管芯11、第二管芯12、第三管芯14以及突出端子14。

[0051]

再布线层16例如是与突出端子14重叠配置的层。再布线层16例如在由二氧化硅、氮化硅、聚酰亚胺等形成的多个绝缘层的各自的内部配置导电性的布线、导孔来构成。再布线层16例如具有如下结构:在绝缘层161的内部配置有贯通再布线层16且与突出端子14电连接的导电导孔162。在本实施方式中,再布线层16横跨突出端子14的突出方向的顶端面和第三管芯的布线面(未图示)相反侧的露出面配置。此外,在本实施方式中,再布线层16具有如下结构:在与第三管芯13重叠的位置配置有在层叠方向c贯通的散热用的散热导孔163。

[0052]

外部端子17例如由多个凸块、多个焊球构成。外部端子17在层叠方向c与再布线层16排列设置。在本实施方式中,外部端子17具有连接端子171和非连接端子172。

[0053]

连接端子171配置在再布线层16的导电导孔162的露出位置。由此,连接端子171隔着再布线层16与突出端子14电连接。连接端子171例如作为信号端子、供电端子或接地端子发挥功能。

[0054]

非连接端子172在层叠方向上配置在与第三管芯13重叠的位置。非连接端子172不与突出端子14连接,作为第三管芯13的散热端子发挥功能。

[0055]

散热部18被设计成用于第三管芯13的散热。散热部18构成为作为第三管芯13的散热路径与第三管芯13重叠。在本实施方式中,散热部18由再布线层16中与第三管芯13重叠的重合部181、以及外部端子17的非连接端子172构成。

[0056]

下面,对本实施方式的半导体模块1的安装体100的结构进行说明。

[0057]

半导体模块1的安装体100具有半导体模块1、安装基板101以及焊球102。另外,在半导体模块1的安装体100中,在连接端子171的位置配置有密封连接端子171的底部填充胶19。

[0058]

安装基板101例如是有机基板。在本实施方式中,安装基板101构成为在与层叠方向c交叉的方向具有比半导体模块1大的面积。安装基板101的一个面与连接端子171连接。在安装基板101中,配置有在层叠方向c贯通的多个贯通端子110。具体地,安装基板101配置

有在层叠方向c贯通且与连接端子171连接的贯通导电端子111、以及在层叠方向c贯通且与非连接端子172连接的贯通散热端子112。

[0059]

焊球102配置在安装基板101的另一个面。焊球102与贯通端子110连接。

[0060]

下面,对本实施方式的半导体模块1以及半导体模块1的安装体100的工作进行说明。

[0061]

将经由贯通导电端子111和连接端子171供给的电力和信号,经由再布线层16和突出端子14供给至第一管芯11和第二管芯12。第一管芯11基于供给的信号工作,并且将电力和信号供给至第三管芯13的接口部132。此外,第二管芯12将经由突出端子14供给的电力供给至第三管芯13的阵列部131。

[0062]

第三管芯13通过由第一管芯11和第二管芯12供给的电力而发热。散热部18经由贯通散热端子112,将第三管芯13产生的热向安装基板101的外部散热。

[0063]

下面,对半导体模块1以及半导体模块1的安装体100的制造方法进行说明。

[0064]

首先,制造半导体模块1。半导体模块1的制造方法包括:在第一管芯11和第二管芯12形成突出端子14的工序;将第一管芯11和第二管芯12排列设置在支承基板200的工序;配置第三管芯13的工序;塑封工序;抛光工序;形成再布线层16的工序;配置外部端子17的工序;去除支承基板200的工序。

[0065]

首先,如图2所示,实施在第一管芯11和第二管芯12形成突出端子14的工序。在形成突出端子14的工序中,在第一管芯11和第二管芯12的一个面形成突出端子14。突出端子14例如从第一管芯11和第二管芯12的布线面突出而形成。此外,第一管芯11和第二管芯12与第三管芯13的连接端子141在形成突出端子14时一并形成。

[0066]

接着,实施配置第一管芯11和第二管芯12的工序。第一管芯11和第二管芯12隔着临时粘接层201将与布线面相反的面在与层叠方向c交叉的方向排列设置在支承基板200。在此,支承基板200例如是晶圆、面板等。在本实施方式中,在配置第一管芯11和第二管芯12的工序中,在支承基板200上配置第一管芯11和第二管芯12的多个组。

[0067]

接着,实施配置第三管芯13的工序。如图3和图4所示,在配置第三管芯13的工序中,第三管芯13横跨第一管芯11和第二管芯12配置。在配置第三管芯13的工序中,第三管芯13配置在与突出端子14相邻的空间区域,并且经由连接端子141与第一管芯11和第二管芯12电连接。

[0068]

接着,实施塑封工序。在塑封工序中,通过塑封材料15对第一管芯11、第二管芯12、第三管芯13以及突出端子14进行塑封。在塑封工序中,例如用塑封材料15覆盖第一管芯11、第二管芯12、第三管芯13以及突出端子14。

[0069]

接着,实施抛光工序。在抛光工序中,对配置在第三管芯13和突出端子14的突出方向的顶端侧的塑封材料15进行抛光。在抛光工序中,例如使用磨光机对配置在突出端子14的突出方向的顶端侧塑封材料15以及与第三管芯13的布线面相反侧的面进行抛光。其结果是,如图5所示,在抛光工序中,第三管芯13和突出端子14在层叠方向c上露出。

[0070]

接着,实施形成再布线层16的工序。如图6所示,在形成再布线层16的工序中形成再布线层16。在形成再布线层16的工序中,交替地反复形成绝缘层161和导孔。由此,形成与突出端子14连接的导孔。

[0071]

接着,实施配置外部端子17的工序。如图7所示,通过配置外部端子17的工序,在再

布线层16的露出面配置外部端子17。外部端子17与再布线层16的导孔连接。具体地,连接端子171配置在层叠方向c上与突出端子14重叠的位置。另一方面,在与第三管芯13重叠的位置配置非连接端子172。

[0072]

接着,实施去除支承基板200的工序。由此,形成半导体模块1。

[0073]

下面,对半导体模块1的安装体100的制造方法进行说明。

[0074]

半导体模块1的安装体100的制造方法包括连接安装基板101的工序以及配置焊球102的工序。

[0075]

首先,实施连接安装基板101的工序。在连接安装基板101的工序中,安装基板101的一个面与外部端子17连接。具体地,在连接安装基板101的工序中,在安装基板101的一个面侧露出的贯通导电端子111以及贯通散热端子112与外部端子17连接。另外,在连接安装基板101的工序中,在外部端子17的位置配置底部填充胶19。

[0076]

接着,实施配置焊球102的工序。在配置焊球102的工序中,在安装基板101的另一个面侧配置焊球102。具体地,在配置焊球102的工序中,在从安装基板101的另一个面露出的贯通导电端子111和贯通散热端子112配置焊球102。

[0077]

以上,本实施方式涉及的半导体模块1、其制造方法以及半导体模块1的安装体100获得以下的效果。

[0078]

(1)一种具有层叠的多个管芯的半导体模块1,包括:第一管芯11;第二管芯12,其在与层叠方向c交叉的方向与第一管芯11排列设置;第三管芯13,其横跨第一管芯11和第二管芯12在层叠方向c上配置,并且与相向的第一管芯11和第二管芯12的布线面电连接;突出端子14,其从第一管芯11和第二管芯12的布线面突出,并且在与层叠方向c交叉的方向上与第三管芯13的至少一个侧面相邻的空间区域中突出;再布线层16,其与突出端子14重叠配置。取代现有的封装基板,通过再布线层16构成半导体模块1。由此,与使用封装基板的情况相比能够降低成本。此外,由于第一管芯11与第三管芯13临近地电连接,因此能够提高在第一管芯11和第三管芯13之间收发的信号的带宽。进而,由于第一管芯11和第二管芯12载置

·

固定在支承基板200,因此能够提高与第三管芯13的对位精度,并且通过缩短与第三管芯13的连接端子141的间距来增加端子的数量。

[0079]

(2)第二管芯12是供电管芯,其将由突出端子14供给的电力供给至第三管芯13。由此,与仅从第一管芯11向第三管芯13供电的情况相比,因为还能够从第二管芯12供电,能够更稳定地向第三管芯13供电。

[0080]

(3)第二管芯12在与层叠方向c交叉的方向夹着第一管芯11成对配置,第三管芯13横跨第一管芯11和成对配置的第二管芯12成对配置。由此,能够将多个第三管芯13与第一管芯11连接,因此能够容易地实现大容量化。

[0081]

(4)第三管芯13具有在层叠方向c与第二管芯12重叠的阵列部131、以及在层叠方向c与第一管芯11重叠的接口部132。由此,能够从第二管芯12直接对更需要电力的阵列部131供电,另一方面,对于与阵列部131相比小电力即可的接口部132,由作为逻辑芯片的第一管芯11进行供电。因此,与仅从第一管芯11向第三管芯13供电的情况相比,能够更稳定地供电。此外,因为接口部132由作为通信对象的第一管芯11进行供电,能够提高信号电压电平的整合性和信号质量。

[0082]

(5)半导体模块1还具有作为第三管芯13的散热路径而与第三管芯13重叠的散热

部18。由此,由于能够形成与在基板101的近侧配置的第三管芯13对应的散热部18,能够使第三管芯13更稳定地工作。

[0083]

(6)半导体模块1还具有:在层叠方向c上排列设置在再布线层16的多个外部端子17,外部端子17具有隔着再布线层16与突出端子14电连接的连接端子171以及在层叠方向c配置在与第三管芯13重叠的位置且不与突出端子14电连接的非连接端子172。由此,能够在再布线层16上同样地配置连接端子171和非连接端子172。因此,能够在半导体模块1配置散热部18的同时降低制造成本。

[0084]

(7)散热部18由再布线层16中与第三管芯13重叠的重合部181和非连接端子172构成。由此,通过再布线层16和外部端子17能够兼具布线和散热的结构。因此,能够降低制造半导体模块1的成本。

[0085]

(8)一种半导体模块1的安装体100,其具有上述的半导体模块1以及安装基板101,安装基板101具有在层叠方向c贯通的多个贯通端子110,贯通端子110与外部端子17分别连接。由此,能够容易地将半导体模块1安装在主板等基板。

[0086]

(9)一种具有层叠的多个管芯的半导体模块1的制造方法,包括:在第一管芯11和第二管芯12的一个面形成突出端子14的工序;将第一管芯11和第二管芯12排列设置在支承基板200的工序;横跨第一管芯11和第二管芯12来配置第三管芯13的工序;将第一管芯11、第二管芯12、第三管芯13以及突出端子14塑封的工序;形成再布线层16的工序,再布线层16横跨第三管芯13的露出面而配置,并且与突出端子14电连接;去除支承基板200的工序。由此,由于能够使用再布线层16形成半导体模块1,能够降低半导体模块1的制造成本。

[0087]

(10)在将第一管芯11和第二管芯12排列设置在支承基板200的工序中,在基板200配置第一管芯11和第二管芯12的多个组。由此,与在每个封装基板形成半导体模块1的情况相比,能够一次制造多个半导体模块1。因此,能够降低半导体模块1的制造成本。

[0088]

(11)在半导体模块1的制造方法中,在塑封工序之后、形成再布线层16的工序之前,还包括使第三管芯13和突出端子14露出的抛光工序。因此,在塑封之后,能够使突出端子14的突出方向的顶端与第三管芯13的露出面的高度相同或大致相同。因此,能够容易地形成与突出端子14电连接的再布线层16,并且能够降低半导体封装100的制造成本。

[0089]

[第二实施方式]

[0090]

下面,参照图8来说明本发明的第二实施方式涉及的半导体模块1、其制造方法以及半导体模块1的安装体100。在说明第二实施方式时,对与前述实施方式相同的构件使用相同附图标记,并且省略或简化其说明。

[0091]

第二实施方式涉及的半导体模块1中的散热部18的重合部181的结构与第一实施方式的不同。

[0092]

如图8所示,重合部181具有金属层183、绝缘层161以及散热用导孔184。重合部181在层叠方向c隔着散热用芯片粘接材料182配置在第三管芯13。

[0093]

金属层183例如是铜层,在层叠方向c断续地配置。金属层183例如沿着层叠方向c与后述的绝缘层161交错配置。在本实施方式中,金属层183例如形成为正视矩形,在层叠方向c上,形成为与第三管芯13的重叠的面相同或大致相同的大小。

[0094]

绝缘层161是例如由二氧化硅、氮化硅、聚酰亚胺等形成的层。绝缘层161沿着层叠方向c与金属层183交错配置。

[0095]

散热用导孔184是贯通绝缘层161的导孔。散热用导孔184在层叠方向c与金属层183连接。在本实施方式中,散热用导孔184呈正视矩阵状配置。由此,与将重合部181整体作为金属层183的情况相比,即使重合部181因热而膨胀也能够提高半导体模块1的稳定性。

[0096]

以上,本实施方式涉及的半导体模块1、其制造方法以及半导体模块1的安装体100获得以下的效果。

[0097]

(12)重合部181具有断续地重叠的金属层183以及连接相邻的金属层183之间的散热用导孔184。由此,能够提高第三管芯13的散热效率,并且,即使重合部181因而热膨胀,也能够提高稳定性。

[0098]

[第三实施方式]

[0099]

下面,参照图9来说明本发明的第三实施方式涉及的半导体模块1、其制造方法以及半导体模块1的安装体100。在说明第三实施方式时,对与前述实施方式相同的构件使用相同附图标记,并且省略或简化其说明。

[0100]

第三实施方式涉及的半导体模块1与第一实施方式和第二实施方式的不同之处在于,散热部18具有热扩散用构件185来代替重合部181。并且,再布线层16形成为贯通与第三管芯13重叠的位置。此外,第三实施方式涉及的半导体模块1的制造方法与第一实施方式和第二实施方式的不同之处在于,还包括配置热扩散用构件185的工序。

[0101]

热扩散用构件185可以是例如散热用芯片粘接材料182。热扩散用构件185在层叠方向c配置在与第三管芯13的布线面相反的面与安装基板101的一个表面之间。具体地,热扩散用构件185在层叠方向c与第三管芯13的布线面相反的面和安装基板101的一个面接触配置。

[0102]

在配置热扩散用构件185的工序中,贯通再布线层16的热扩散用构件185配置在与第三管芯13重叠的位置。配置热扩散用构件185的工序在抛光的工序后实施。

[0103]

上面说明的本实施方式所涉及的半导体模块1、其制造方法以及半导体模块1的安装体100获得以下的效果。

[0104]

(13)散热部18具有贯通再布线层16的热扩散用构件185。由此,在第三管芯13中产生的热能够经由热扩散用构件185传递至安装基板101。由于在沿着层叠方向c的方向上,在与第三管芯13的布线面相反的面重叠的位置整体配置热扩散用构件185,因此能够进一步提高散热效率。

[0105]

(14)半导体模块1的制造方法还包括将贯通再布线层16的热扩散用构件185配置在与第三管芯13重叠的位置的工序。由于仅将热扩散用构件185配置在与没有形成再布线层16的第三管芯13重叠的位置,因此能够进一步降低半导体模块1的制造成本。

[0106]

上面对本发明的半导体模块、其制造方法以及半导体模块的安装体的优选的各实施方式进行了说明,但是本发明不限于上述实施方式,能够适当变化。

[0107]

例如,如图10所示,在上述第二实施方式中,可以配置热扩散用构件185来代替非连接端子172。通过使用热扩散用构件185,与非连接端子172相比增大了与重合层接触的面积,因此能够提高散热效率。

[0108]

此外,在上述实施方式中,将第一管芯设为逻辑芯片,将第三管芯设为dram,反之亦可。即,也可以构成为将一个dram与多个逻辑芯片连接。此外,此处也可以将一个dram设为例如接口。即,也可以构成为将一个接口与多个逻辑芯片连接。

[0109]

此外,上述实施方式中,第一管芯11可以广泛地应用于所有逻辑芯片,第三管芯13不限于dram,可以广泛地应用于包括非易失性ram(例如mram、reram、feram等)的所有ram(random access memory:随机存取存储器)。

[0110]

附图标记说明

[0111]

1:半导体模块;

[0112]

11:第一管芯;

[0113]

12:第二管芯;

[0114]

13:第三管芯;

[0115]

14:突出端子;

[0116]

16:再布线层;

[0117]

17:外部端子;

[0118]

18:散热部;

[0119]

100:半导体模块的安装体;

[0120]

101:安装基板;

[0121]

102:焊球;

[0122]

110:贯通端子;

[0123]

131:阵列部;

[0124]

132:接口部;

[0125]

171:连接端子;

[0126]

172:非连接端子;

[0127]

181:重合部;

[0128]

183:金属层;

[0129]

184:散热用导孔;

[0130]

185:热扩散用构件;

[0131]

200:支承基板;

[0132]

c:层叠方向。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1