一种半导体器件的形成方法与流程

1.本发明涉及半导体技术领域,特别涉及一种半导体器件的形成方法。

背景技术:

2.在半导体制造工艺中,通过光刻和刻蚀的步骤将掩膜上的图案转印到半导体芯片上是非常重要且复杂的过程。

3.光刻后特定图案尺寸的大小通过显影后的特征尺寸(after develop inspection critical dimension,adi cd)来表征,并且adi cd的大小直接影响着刻蚀后的特征尺寸(after etch inspection critical dimension,aei cd)。而在刻蚀之前,需要沉积介质层和平坦层,并在平坦层上形成图形化的光刻胶层,然后以图形化的光刻胶层刻蚀平坦层进而介质层。

4.而平坦层下方形成于介质层中的源漏插塞槽的密度是不同的,使得介质层中会形成源漏插塞槽稀疏区和源漏插塞槽密集区。源漏插塞槽密集区由于源漏插塞槽较为密集所以平坦层材料沉积时在介质层上形成的平坦层较薄(平坦层沉积时部分平坦层材料进入源漏插塞槽内),源漏插塞槽稀疏区由于源漏插塞槽较为稀疏所以平坦层材料在沉积时,在介质层上形成的平坦层较厚。因此,由于平坦层厚度不均匀,并且由于形成栅极插塞槽的工艺窗口不足,在刻蚀形成栅极插塞槽时,会存在过刻蚀或刻蚀不足的问题。

5.上述过刻蚀和刻蚀不足均会影响半导体器件的均匀性,由此,器件的性能也会下降。

技术实现要素:

6.本发明的目的在于解决现有技术中,在刻蚀形成栅极插塞槽时,会存在过刻蚀或刻蚀不足的问题,影响半导体器件的性能。

7.本发明提供了一种半导体器件的形成方法,可避免在刻蚀形成栅极插塞槽时,存在的过刻蚀或刻蚀不足的问题。

8.为解决上述技术问题,本发明的实施方式公开了一种半导体器件的形成方法,包括:

9.提供基底;

10.提供器件版图,所述器件版图包括源漏插塞槽图形和初始栅极插塞槽图形;

11.在所述基底上形成栅极结构和覆盖所述栅极结构顶部和侧部的介质层,所述介质层中具有位于所述栅极结构两侧的对应所述源漏插塞槽图形的源漏插塞槽;

12.在所述源漏插塞槽中和所述介质层上形成平坦层,所述介质层上的所述平坦层厚度具有差异;

13.在所述器件版图上,分别对各所述初始栅极插塞槽图形周围阈值区域内的所述源漏插塞槽图形进行扫描,从而获得各所述初始栅极插塞槽图形的密度参数;

14.根据所述密度参数,分别对各所述初始栅极插塞槽图形进行补偿,得到栅极插塞

槽修正图形,所述栅极插塞槽修正图形的特征尺寸随所述密度参数的增大而减小;

15.基于所述栅极插塞槽修正图形,在所述平坦层上形成图形化的光刻胶层;

16.以所述图形化的光刻胶层为掩模刻蚀所述平坦层和所述介质层,在所述介质层中形成位于所述栅极结构上的栅极插塞槽。

17.可选的,分别对各所述初始栅极插塞槽图形周围阈值区域内的所述源漏插塞槽图形进行扫描,从而获得各所述初始栅极插塞槽图形的密度参数的方法包括:

18.以所述初始栅极插塞槽图形的各边缘点为扫描中心,以阈值扫描半径,对所述初始栅极插塞槽图形阈值区域内的所述源漏插塞槽图形进行扫描,以获取对应各所述初始栅极插塞槽图形的扫描源漏插塞槽图形;

19.根据各所述扫描源漏插塞槽图形的面积与对应的阈值区域的面积的比值,得到各所述初始栅极插塞槽图形的密度参数。

20.可选的,

21.其中,d

i

为第i个初始栅极插塞槽图形的密度参数,i为大于等于2的整数;

22.为第i个初始栅极插塞槽图形对应的扫描源漏插塞槽图形的面积,n为大于等于1的整数;

23.d

total

i为第i个初始栅极插塞槽图形对应的阈值区域的面积;

24.所述第i个初始栅极插塞槽图形对应的扫描源漏插塞槽图形包括n个子扫描源漏插塞槽;f(k)

i

为第i个初始栅极插塞槽图形对应的第k个子扫描源漏插塞槽的面积,k为大于等于1且小于等于n的整数。

25.可选的,当第i个初始栅极插塞槽图形在所述基底的投影形状为正方形时,可选的,当第i个初始栅极插塞槽图形在所述基底的投影形状为正方形时,

26.其中,r为阈值扫描半径;

27.为第i个初始栅极插塞槽图形的特征尺寸。

28.可选的,根据所述密度参数,分别对各所述初始栅极插塞槽图形进行补偿,得到所述栅极插塞槽修正图形的方法包括:

29.根据不同区域所述初始栅极插塞槽图形的密度参数,获取各所述初始栅极插塞槽图形的补偿量;

30.根据各所述初始栅极插塞槽图形和对应的补偿量,获得所述栅极插塞槽修正图形;

[0031][0032]

其中,

[0033]

为第i个初始栅极插塞槽图形的特征尺寸,

[0034]

d

i

为第i个初始栅极插塞槽图形的密度参数,

[0035]

f(d

i

)为第i个初始栅极插塞槽图形对应的补偿量,

[0036]

为第i个栅极插塞槽修正图形的特征尺寸,i为大于等于2的整数。

[0037]

可选的,根据不同区域所述初始栅极插塞槽图形的密度参数,获取各所述初始栅极插塞槽图形的补偿量的方法包括:

[0038]

获取不同区域的所述初始栅极插塞槽图形的密度参数随着所述初始栅极插塞槽图形的位置变化的曲线函数中的斜率;

[0039]

在不同区域的所述初始栅极插塞槽图形中获取零补偿初始栅极插塞槽图形;

[0040]

获取所述零补偿初始栅极插塞槽图形对应的零补偿点密度参数;

[0041]

根据所述斜率、各所述初始栅极插塞槽图形的密度参数、以及所述零补偿区密度参数,获取各所述初始栅极插塞槽图形的补偿量;

[0042]

f(d

i

)=-|k|(d

i-d

i0

)

[0043]

其中,k为斜率,d_i0为零所述补偿点密度参数。

[0044]

可选的,获取所述零补偿初始栅极插塞槽图形的方法包括:

[0045]

提供测试基底;

[0046]

在所述测试基底上形成测试栅极结构和覆盖测试栅极结构顶部和侧部的测试介质层,所述测试介质层中具有位于所述测试栅极结构两侧的测试源漏插塞槽;

[0047]

在所述测试源漏插塞槽中和所述测试介质层上形成测试平坦层,所述测试介质层上的所述测试平坦层厚度具有差异;

[0048]

基于所述初始栅极插塞槽图形,在所述测试平坦层上形成测试光刻胶层;

[0049]

以所述测试光刻胶层为掩模刻蚀所述测试平坦层和所述测试介质层,在所述测试介质层中形成位于所述测试栅极结构上的测试栅极插塞槽;

[0050]

根据不同区域的所述测试栅极插塞槽的形貌,获取零补偿测试栅极插塞槽;

[0051]

根据所述零补偿测试栅极插塞槽,获取对应的零补偿初始栅极插塞槽图形。

[0052]

可选的,以所述测试光刻胶层为掩模刻蚀所述测试平坦层和所述测试介质层的刻蚀条件,与以所述图形化的光刻胶层为掩模刻蚀所述平坦层和所述介质层的刻蚀条件一致。

[0053]

可选的,以所述测试光刻胶层为掩模刻蚀所述测试平坦层和所述测试介质层的工艺为各向异性干法刻蚀工艺,以所述图形化的光刻胶层为掩模刻蚀所述平坦层和所述介质层的工艺为各向异性干法刻蚀工艺;

[0054]

所述刻蚀条件包括刻蚀气体、气体流量、腔室压强、源射频功率和偏置功率。

[0055]

可选的,所述初始栅极插塞槽图形在所述基底的投影形状为多边形、椭圆形、矩形中的任意一种。

[0056]

本发明的有益效果是:

[0057]

在器件版图上,分别对各初始栅极插塞槽图形周围阈值区域内的源漏插塞槽图形进行扫描,从而获得各初始栅极插塞槽图形的密度参数。然后根据密度参数,分别对各初始栅极插塞槽图形进行补偿,得到栅极插塞槽修正图形。且栅极插塞槽修正图形的特征尺寸随密度参数的增大而减小。然后根据该栅极插塞槽修正图形形成图形化的光刻胶层,并对平坦层和介质层进行刻蚀,以形成栅极插塞槽。也就是说,源漏插塞槽的密度较大的区域,通过将栅极插塞槽修正图形的特征尺寸减小,可以减小刻蚀介质层和平坦层的速率,从而能够避免在刻蚀形成栅极插塞槽时出现过刻蚀的问题。而在源漏插塞槽的密度较小的区域,通过将栅极插塞槽修正图形的特征尺寸增大,可以增大刻蚀介质层和平坦层的速率,从而能够避免在刻蚀形成栅极插塞槽时出现刻蚀不足的问题。由此,尽管源漏插塞槽的密度较大的区域与源漏插塞槽的密度较小的区域的介质层上的平坦层厚度具有差异,但刻蚀的

介质层和平坦层的终点相同。这会使得最终形成的栅极插塞槽的形貌更均匀,半导体器件的性能更好。

附图说明

[0058]

图1和图2是一种半导体器件的结构示意图;

[0059]

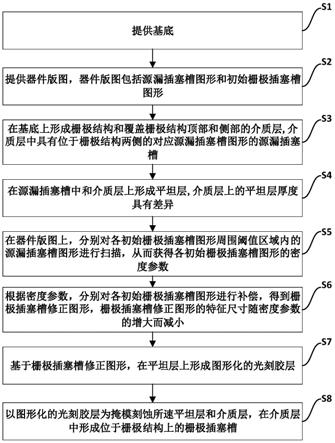

图3是本发明实施例提供的半导体器件的形成方法的流程图;

[0060]

图4和图5是本发明实施例提供的半导体器件的形成方法对应的器件版图的结构示意图;

[0061]

图6至图7是本发明实施例提供的半导体器件的形成方法对应的结构示意图;

[0062]

图8至图9是本发明实施例提供的半导体器件的形成方法对应的另一结构示意图。

具体实施方式

[0063]

以下由特定的具体实施例说明本发明的实施方式,本领域技术人员可由本说明书所揭示的内容轻易地了解本发明的其他优点及功效。虽然本发明的描述将结合较佳实施例一起介绍,但这并不代表此发明的特征仅限于该实施方式。恰恰相反,结合实施方式作发明介绍的目的是为了覆盖基于本发明的权利要求而有可能延伸出的其它选择或改造。为了提供对本发明的深度了解,以下描述中将包含许多具体的细节。本发明也可以不使用这些细节实施。此外,为了避免混乱或模糊本发明的重点,有些具体细节将在描述中被省略。需要说明的是,在不冲突的情况下,本发明中的实施例及实施例中的特征可以相互组合。

[0064]

应注意的是,在本说明书中,相似的标号和字母在下面的附图中表示类似项,因此,一旦某一项在一个附图中被定义,则在随后的附图中不需要对其进行进一步定义和解释。

[0065]

在本实施例的描述中,需要说明的是,术语“上”、“下”、“内”、“底”等指示的方位或位置关系为基于附图所示的方位或位置关系,或者是该发明产品使用时惯常摆放的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制。

[0066]

术语“第一”、“第二”等仅用于区分描述,而不能理解为指示或暗示相对重要性。

[0067]

在本实施例的描述中,还需要说明的是,除非另有明确的规定和限定,术语“设置”、“相连”、“连接”应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或一体地连接;可以是机械连接,也可以是电连接;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通。对于本领域的普通技术人员而言,可以具体情况理解上述术语在本实施例中的具体含义。

[0068]

正如背景技术所述,现有的半导体器件受到过刻蚀和刻蚀不足的影响较大。

[0069]

比如图1和图2所示的半导体器件中,在基底1上形成有栅极结构4,覆盖栅极结构4的顶部和侧部形成有介质层2,介质层2中具有位于栅极结构4两侧的对应源漏插塞槽图形的源漏插塞槽6。在源漏插塞槽6中和介质层2上形成平坦层3。平坦层3上形成有图形化的光刻胶层5。需要说明的是,介质层2上的平坦层3厚度有差异。

[0070]

具体的,介质层2上平坦层3的厚度差异是由于平坦层3下方形成于介质层2中的源漏插塞槽6的密度是不同的,使得介质层2中会形成源漏插塞槽稀疏区和源漏插塞槽密集

区。如图1所示,源漏插塞槽密集区由于源漏插塞槽较为密集所以平坦层材料沉积时在介质层2上形成的平坦层3较薄(平坦层3沉积时部分平坦层材料进入源漏插塞槽6内);如图2所示,源漏插塞槽稀疏区由于源漏插塞槽较为稀疏,所以平坦层材料在沉积时,在介质,2上形成的平坦层3较厚。因此,平坦层3厚度不均匀。

[0071]

也是因为平坦层3的厚度存在差异,在以图形化的光刻胶层5为掩模刻蚀平坦层3和介质层2,在介质层2中形成位于栅极结构4上的栅极插塞槽时,较薄的平坦层3对应的区域,刻蚀速度较快,会存在过刻蚀的情况,而在较厚的平坦层3对应的区域,刻蚀速度较慢,会出现刻蚀不足的情况。

[0072]

同一器件中既出现了过刻蚀,又出现了刻蚀不足的问题,会导致形成的栅极插塞槽的均匀性较差,半导体器件的性能也不佳。

[0073]

需要说明的是,介质层2中位于栅极结构4顶部的位置还形成有覆盖栅极结构4顶部,以及向栅极结构4两侧延伸的保护层21。进一步地,至少部分源漏插塞槽6贯穿该保护层21。

[0074]

为解决现有技术中在刻蚀形成栅极插塞槽时,会存在过刻蚀或刻蚀不足的问题,影响半导体器件的性能,本发明提供一种半导体器件的形成方法。具体的,如图3所示,本发明提供的半导体器件的形成方法,包括:

[0075]

步骤s1:提供基底;

[0076]

步骤s2:提供器件版图,器件版图包括源漏插塞槽图形和初始栅极插塞槽图形;

[0077]

步骤s3:在基底上形成栅极结构和覆盖栅极结构顶部和侧部的介质层,介质层中具有位于栅极结构两侧的对应源漏插塞槽图形的源漏插塞槽;

[0078]

步骤s4:在源漏插塞槽中和介质层上形成平坦层,介质层上的平坦层厚度具有差异;

[0079]

步骤s5:在器件版图上,分别对各初始栅极插塞槽图形周围阈值区域内的源漏插塞槽图形进行扫描,从而获得各初始栅极插塞槽图形的密度参数;

[0080]

步骤s6:根据密度参数,分别对各初始栅极插塞槽图形进行补偿,得到栅极插塞槽修正图形,栅极插塞槽修正图形的特征尺寸随密度参数的增大而减小;

[0081]

步骤s7:基于栅极插塞槽修正图形,在平坦层上形成图形化的光刻胶层;

[0082]

步骤s8:以图形化的光刻胶层为掩模刻蚀平坦层和介质层,在介质层中形成位于栅极结构上的栅极插塞槽。

[0083]

上述方法在源漏插塞槽的密度较大的区域,通过将栅极插塞槽修正图形的特征尺寸减小,可以减小刻蚀介质层和平坦层的速率,从而能够避免在刻蚀形成栅极插塞槽时出现过刻蚀的问题。而在源漏插塞槽的密度较小的区域,通过将栅极插塞槽修正图形的特征尺寸增大,可以增大刻蚀介质层和平坦层的速率,从而能够避免在刻蚀形成栅极插塞槽时出现刻蚀不足的问题。由此,尽管源漏插塞槽的密度较大的区域与源漏插塞槽的密度较小的区域的介质层上的平坦层厚度具有差异,但刻蚀的介质层和平坦层的终点相同。这会使得最终形成的栅极插塞槽的形貌更均匀,半导体器件的性能更好。

[0084]

为使本发明的目的、技术方案和优点更加清楚,下面将结合附图对本发明的实施方式作进一步地详细描述。

[0085]

下面结合附图4至9具体描述本发明实施例提供的工艺窗口的调节方法。

[0086]

首先参考图6和图7,提供基底1。

[0087]

本实施例中的基底1的材料包括但不限于硅、锗或者锗化硅等,本实施例对此不做具体限定。此外,在基底1中还可以形成有隔离结构或者其他结构,本实施例对此也不做具体限定。

[0088]

参考图4,提供器件版图7,器件版图7包括源漏插塞槽图形61和初始栅极插塞槽图形41。

[0089]

参考图6和图7,在基底1上形成栅极结构4和覆盖栅极结构4顶部和侧部的介质层2,介质层2中具有位于栅极结构4两侧的对应源漏插塞槽图形61的源漏插塞槽6。

[0090]

优选的,本实施例中的介质层2是氧化层,具体可以是氧化硅、二氧化硅等材料,本实施例对此不做具体限定。

[0091]

继续参考图6和图7,在源漏插塞槽6中和介质层2上形成平坦层3,且介质层2上的平坦层3厚度具有差异。

[0092]

具体地,本实施例中平坦层3为旋涂碳层(soc),本领域技术人员还可以根据实际需要选择其他平坦层材料,本实施例对此不做具体限定。

[0093]

且介质层2上的平坦层3厚度有差异具体是指,源漏插塞槽6稀疏的区域和源漏插塞槽6密集的区域对应的平坦层3的厚度不同。例如图6中,源漏插塞槽6密集,平坦层3较薄,图7中源漏插塞槽6稀疏,平坦层3较厚。

[0094]

参考图5,在器件版图7上,分别对各初始栅极插塞槽图形41周围阈值区域内的源漏插塞槽6图形进行扫描,从而获得各初始栅极插塞槽图形41的密度参数。

[0095]

具体地,本实施例中初始栅极插塞槽图形41的密度参数是指,在初始栅极插塞槽图形41周围阈值区域内,源漏插塞槽图形的面积总和占阈值区域面积的比例。

[0096]

阈值区域的大小本领域技术人员可以根据实际需求确定,对于不同尺寸的器件,阈值区域大小不同。

[0097]

需要说明的是,图4和图5的上半部分示意的是源漏插塞槽6密度较大的区域a,图4的下半部分示意的是源漏插塞槽6密度较小的区域b。

[0098]

还需要说明的是,图4和图5中仅仅是示意性地以一个初始栅极插塞槽图形41为例,来说明本实施例提供的半导体器件的形成方法,事实上,在该器件版图7内可以包括多个初始栅极插塞槽图形41,且对各初始栅极插塞槽图形41的方法都相同。

[0099]

此外,本实施例中,本实施例中仅仅是示意性地示出了初始栅极插塞槽图形41为正方形,且在本实施例中,均以初始栅极插塞槽图形41为正方形为例进行说明。事实上,在本发明的其他实施例中,初始栅极插塞槽图形41在基底1的投影形状为多边形、椭圆形、或矩形。

[0100]

更具体的,本实施例中,分别对各初始栅极插塞槽图形41周围阈值区域内的源漏插塞槽图形61进行扫描,从而获得各初始栅极插塞槽图形41的密度参数的方法包括以下步骤:

[0101]

首先,以初始栅极插塞槽图形41的各边缘点为扫描中心,以阈值扫描半径,对初始栅极插塞槽图形41阈值区域内的源漏插塞槽图形61进行扫描,以获取对应各初始栅极插塞槽图形41的扫描源漏插塞槽图形61a;

[0102]

然后,根据各扫描源漏插塞槽图形61a的面积与对应的阈值区域的面积的比值,得

到各初始栅极插塞槽图形41的密度参数。

[0103]

更具体的,其中,d

i

为第i个初始栅极插塞槽图形41的密度参数,i为大于等于2的整数。

[0104]

为第i个初始栅极插塞槽图形41对应的扫描源漏插塞槽图形61a的面积,n为大于等于1的整数。

[0105]

d

total

i为第i个初始栅极插塞槽图形41对应的阈值区域的面积。

[0106]

第i个初始栅极插塞槽图形41对应的扫描源漏插塞槽图形61a包括n个子扫描源漏插塞槽6;f(k)

i

为第i个初始栅极插塞槽图形41对应的第k个子扫描源漏插塞槽的面积,k为大于等于1且小于等于n的整数。

[0107]

且当第i个初始栅极插塞槽图形41在基底1的投影形状为正方形时,且当第i个初始栅极插塞槽图形41在基底1的投影形状为正方形时,

[0108]

其中,r为阈值扫描半径;

[0109]

为第i个初始栅极插塞槽图形41的特征尺寸。

[0110]

需要说明的是,当初始栅极插塞槽图形41在基底1的投影形状为其他形状时,仅仅是阈值区域的面积大小与投影形状为正方形时有差异。例如,当初始栅极插塞槽图形41在基底1的投影形状为长方形时,阈值区域的大小为可以分解为四个长方形的面积与一个椭圆形的面积;当初始栅极插塞槽图形41在基底1的投影形状为圆形时,阈值区域的大小为圆形周侧的圆环的面积。本领域技人员可以根据不同的形状计算得到阈值区域的大小,本实施例在此不再赘述。

[0111]

继续参考图5,根据密度参数,分别对各初始栅极插塞槽图形41进行补偿,得到栅极插塞槽修正图形42,栅极插塞槽修正图形42的特征尺寸随密度参数的增大而减小。

[0112]

也就是说,在阈值区域内,源漏插塞槽图形61面积占比越大,意味着源漏插塞槽6的密度越大,且平坦层3较薄。平坦层3较薄,刻蚀所需的时间就越短,容易在刻蚀形成栅极插塞槽时出现过刻蚀的问题。因此,将栅极插塞槽修正图形42的特征尺寸减小,可以延长刻蚀介质层2、平坦层3的时间,由此能够避免在刻蚀形成栅极插塞槽时出现过刻蚀的问题。

[0113]

进一步地,在阈值区域内,源漏插塞槽图形61面积占比越小,意味着源漏插塞槽6的密度越小、越稀疏,且平坦层3较厚。平坦层3较厚,刻蚀所需的时间就越长,容易在刻蚀形成栅极插塞槽时出现刻蚀不足的问题。因此,将栅极插塞槽修正图形42的特征尺寸增大,可以缩短刻蚀介质层2、平坦层3的时间,由此能够避免在刻蚀形成栅极插塞槽时出现刻蚀不足的问题。

[0114]

具体的,本实施例中,根据密度参数,分别对各初始栅极插塞槽图形41进行补偿,得到栅极插塞槽修正图形42的方法包括以下步骤:

[0115]

首先,根据不同区域初始栅极插塞槽图形41的密度参数,获取各初始栅极插塞槽图形41的补偿量。

[0116]

具体地,补偿量可以理解为初始栅极插塞槽图形41与栅极插塞槽修正图形42的面积之差,在图5中初始栅极插塞槽图形41周侧的阴影部分。

[0117]

然后,根据各初始栅极插塞槽图形41和对应的补偿量,获得栅极插塞槽修正图形42。

[0118]

更具体地,其中,为第i个初始栅极插塞槽图形41的特征尺寸,d

i

为第i个初始栅极插塞槽图形41的密度参数,f(d

i

)为第i个初始栅极插塞槽图形41对应的补偿量,为第i个栅极插塞槽修正图形42的特征尺寸,i为大于等于2的整数。

[0119]

还需要说明的是,本实施例中,根据不同区域初始栅极插塞槽图形41的密度参数,获取各初始栅极插塞槽图形41的补偿量的方法包括以下步骤:

[0120]

首先,获取不同区域的初始栅极插塞槽图形的密度参数随着初始栅极插塞槽图形的位置变化的曲线函数中的斜率。

[0121]

其次,在不同区域的初始栅极插塞槽图形41中获取零补偿初始栅极插塞槽图形。

[0122]

然后,获取零补偿初始栅极插塞槽图形对应的零补偿点密度参数。

[0123]

之后,根据斜率、各初始栅极插塞槽图形41的密度参数、以及零补偿区密度参数,获取各初始栅极插塞槽图形41的补偿量。

[0124]

具体地,f(d

i

)=-|k|(d

i-d

i0

),其中,k为斜率,d

i0

为零补偿点密度参数。

[0125]

还需要说明的是,本实施例中,获取零补偿初始栅极插塞槽图形的方法包括:

[0126]

提供测试基底。

[0127]

具体地,测试基底的材料和结构与基底1的材料和结构没有本质区别,本实施例在此不再赘述。

[0128]

在测试基底上形成测试栅极结构和覆盖测试栅极结构顶部和侧部的测试介质层,测试介质层中具有位于测试栅极结构两侧的测试源漏插塞槽。

[0129]

在测试源漏插塞槽中和测试介质层上形成测试平坦层,测试介质层上的测试平坦层厚度具有差异。

[0130]

基于初始栅极插塞槽图形,在测试平坦层上形成测试光刻胶层。

[0131]

以测试光刻胶层为掩模刻蚀测试平坦层和测试介质层,在测试介质层中形成位于测试栅极结构上的测试栅极插塞槽。

[0132]

根据不同区域的测试栅极插塞槽的形貌,获取零补偿测试栅极插塞槽;

[0133]

根据零补偿测试栅极插塞槽,获取对应的零补偿初始栅极插塞槽图形。

[0134]

具体的,以测试光刻胶层为掩模刻蚀测试平坦层和测试介质层的刻蚀条件,与以图形化的光刻胶层为掩模刻蚀平坦层3和介质层2的刻蚀条件一致。

[0135]

以测试光刻胶层为掩模刻蚀测试平坦层和测试介质层的工艺为各向异性干法刻蚀工艺,以图形化的光刻胶层5为掩模刻蚀平坦层3和介质层2的工艺为各向异性干法刻蚀工艺。

[0136]

优选的,本实施例中的刻蚀条件包括刻蚀气体、气体流量、腔室压强、源射频功率和偏置功率。

[0137]

参考图4、图5、图6和图7,基于栅极插塞槽修正图形42,在平坦层3上形成图形化的光刻胶层5。

[0138]

进一步地,以图形化的光刻胶层5为掩模刻蚀平坦层3和介质层2,在介质层2中形成位于栅极结构4上的栅极插塞槽。

[0139]

需要说明的是,本实施例中,如图8和图9所示,介质层2中,覆盖栅极结构4还形成

有保护层21。

[0140]

进一步地,源漏插塞槽6贯穿保护层21,以及形成的栅极插塞槽也可以贯穿该保护层21。

[0141]

优选的,本实施例中的保护层21的材料可以是氮化硅或其他材料,本实施例对此不做具体限定。

[0142]

采用上述方案,在器件版图上,分别对各初始栅极插塞槽图形周围阈值区域内的源漏插塞槽图形进行扫描,从而获得各初始栅极插塞槽图形的密度参数。通过获得密度参数,就可以得知在阈值区域内源漏插塞槽图形的面积总和占阈值区域的面积的比值。然后根据密度参数,分别对各初始栅极插塞槽图形进行补偿,得到栅极插塞槽修正图形。且栅极插塞槽修正图形的特征尺寸随密度参数的增大而减小。然后根据该栅极插塞槽修正图形形成图形化的光刻胶层,并对平坦层和介质层进行刻蚀,以形成栅极插塞槽。也就是说,源漏插塞槽的密度较大的区域,通过将栅极插塞槽修正图形的特征尺寸减小,可以减小刻蚀介质层和平坦层的速率,从而能够避免在刻蚀形成栅极插塞槽时出现过刻蚀的问题。而在源漏插塞槽的密度较小的区域,通过将栅极插塞槽修正图形的特征尺寸增大,可以增大刻蚀介质层和平坦层的速率,从而能够避免在刻蚀形成栅极插塞槽时出现刻蚀不足的问题。由此,尽管源漏插塞槽的密度较大的区域与源漏插塞槽的密度较小的区域的介质层上的平坦层厚度具有差异,但刻蚀的介质层和平坦层的终点相同。这会使得最终形成的栅极插塞槽的形貌更均匀,半导体器件的性能更好。

[0143]

虽然通过参照本发明的某些优选实施方式,已经对本发明进行了图示和描述,但本领域的普通技术人员应该明白,以上内容是结合具体的实施方式对本发明所作的进一步详细说明,不能认定本发明的具体实施只局限于这些说明。本领域技术人员可以在形式上和细节上对其作各种改变,包括做出若干简单推演或替换,而不偏离本发明的精神和范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1