内埋组件的基板结构及其制造方法与流程

1.本发明有关于一种基板结构及其制造方法,且特别是一种内埋组件的基板结构及其制造方法。

背景技术:

2.由于社会型态的快速发展及改变,不仅使得民众的生活方式伴随改变,也促使应用在不同领域例如物联网(internet of things,iot)、5g行动通讯(5thgeneration mobile networks,5th generation wireless systems,5g)、生物科技、人工智能芯片(artificial intelligence chip,ai芯片)等电子产业迅速成长。这些迅速成长的电子产业通过内部设置的许多部件的相互运作所带来的效能提升,以创造出许多具有更多先进功能、更好使用质量的电子产品,以提升民众生活质量、便利性或串联相关服务网络。

3.电子产品中的部件通常由一个或多个芯片组合而成,这些芯片内设置有一个或多个的电子组件或者一个或多个的处理器,然后将这些部件相互电连接并进行组装以完成电子产品。以目前部件的制作来说,一般是将芯片设置在载板结构的顶面上,于载板结构及芯片上设置保护层,以包覆芯片及载板结构的顶面,再通过雷射钻孔设备于保护层上钻设出许多对应芯片的多个接点的雷射穿孔,并且在这些雷射穿孔中制作连接芯片的接点以及暴露保护层的多个接脚,通过这些接脚与其它芯片的接脚或者部件上的线路电连接,以完成部件的制作。

4.在设计芯片时为了能够让芯片的效能提升,会在有限的尺寸下设置更多的电子组件或者处理器以使芯片的效能提升,伴随设置许多电子组件或者处理器的情况下,芯片需要设置许多用于与其它芯片或者部件上的线路讯号连接的暴露的接点。然而,由于芯片的尺寸有限所以暴露的接点在排列上非常紧密,此外,受限于雷射钻孔设备的精度限制及热扩孔的影响,使得雷射穿孔的孔径及位置不稳定而易与相邻雷射穿孔相互影响。如此一来,不仅在设置接脚的过程中可能发生相邻接脚相互连接而发生短路的问题,也可能造成接脚未确实与接点连接而发生空接的问题,造成使用可靠性降低。

5.其中,如中国台湾专利公告第twi545997号专利(以下简称文件1)所揭示的一种中介基板及其制法所揭示,于具有线路层的承载板上形成绝缘层,接着于所述绝缘层及所述线路层上形成电连接的线路增层结构,而后形成外接柱于所述线路增层结构上并电连接。但文件1并没有揭示设置于载板结构上的芯片怎么制作对应的接点而与其它芯片连接的内容。

6.又如中国台湾专利公告第twi418265号专利(以下简称文件2)所揭示的一种封装结构,包括承载板,其具有贯穿开口与覆于开口一侧的金属层,半导体芯片收纳于开口中且设于金属层上,钉头凸块设于半导体芯片上,介电层覆盖在承载板及半导体芯片上且包覆钉头凸块,线路层设置在介电层上并电连接钉头凸块,保护层设在介电层与线路层上,通过钉头凸块作为传输讯号的组件。但是文件2没有揭示设置于载板结构上的芯片怎么制作对应的接点而与其它芯片连接的内容。

技术实现要素:

7.有鉴于上述现有技术所存在的问题,本发明的主要目的是提供一种内埋组件的基板结构及其制造方法,通过将预先制作好导线件的芯片设置于载板结构上,以当覆盖介电层后,仅需让导线件露出介电层即可用于以其它的芯片连接。由于不需要额外通过雷射钻孔于介电层上再制作用来设置导线件的雷射穿孔,故可改善因雷射钻孔的精度限制及热扩孔的影响,使相邻导线件相互连接而短路或者导线件空接的问题,借此达到提升基板结构的使用可靠性以及稳定性的目的。

8.为了达成上述目的所采取的主要技术手段,是令前述内埋组件的基板结构包括以下结构。

9.载板结构,具有相对的顶部及底部以及多个第一线路及多个第二线路,所述载板结构的顶部内凹形成容槽,所述第一线路及所述第二线路设置在所述载板结构内,所述第二线路分别具有相对的第一端部及第二端部,所述第二线路的第一端部外露于所述载板结构的顶部,所述第二线路的第二端部外露于所述载板结构的底部。

10.第一介电层,设置于所述载板结构的底部上,并且使所述载板结构的第二线路的第二端部外露于所述第一介电层。

11.预设有多个导线件的芯片结构,设置在所述容槽内。

12.第二介电层,设置于所述芯片结构及所述载板结构的顶部上,并且使所述芯片结构的导线件以及所述第二线路的第一端部外露于所述第二介电层。

13.第一线路增层结构,设置在所述第二介电层上、所述芯片结构的导线件上以及所述第二线路的第二端部上,且分别与所述芯片结构上对应的导线件、所述载板结构上对应的第二线路的第一端部电连接。

14.第二线路增层结构,设置在所述载板结构的底部,且分别与所述载板结构上对应的第二线路的第二端部电连接。

15.可选地,所述芯片结构包括架桥芯片以及导线件结构。所述架桥芯片具有相对的顶部及底部以及多个线路及多个接点,所述线路设置在所述架桥芯片内,所述接点间隔设置在所述架桥芯片的顶部上。所述导线件结构具有固定层以及上述所述导线件,所述固定层具有相对的顶部及底部,所述导线件分别具有相对的第一端部及第二端部,且分别外露于所述固定层的顶部及底部,所述导线件结构的底部设置在所述架桥芯片的顶部上,且使所述导线件的第二端部分别与所述架桥芯片上对应的接点电连接。

16.可选地,更包括黏着层,其设置在所述容槽内且位于所述芯片结构与所述载板结构之间。

17.可选地,更包括电连接层,设置在所述第一线路增层结构上,并且经由所述第一线路增层结构分别与所述第二线路上对应的第一端部以及所述芯片结构上对应的导线件电连接。

18.可选地,于所述基板结构的载板结构的顶部上进一步设置至少一个芯片,所述芯片具有多个接点,并设置在所述载板结构的顶部上,所述芯片的接点经由所述电连接层分别与对应的第二线路以及所述芯片结构上对应的导线件电连接。

19.根据上述结构可知,借由将通过半导体制程方法预先设置、制作预设有导线件的芯片结构固设在载板结构的容槽内,并且于所述载板结构的顶部上设置第二介电层以保护

芯片结构,并使芯片结构的导线件暴露于所述第二介电层即可。由于不需通过雷射钻孔于载板结构的顶部的介电层上制作对应的雷射穿孔,故可改善因雷射钻孔的精度限制及热扩孔的影响,使相邻导线件连接而短路或导线件空接的问题,借此达到提升基板结构的使用可靠性以及稳定性的目的。

20.为了达成上述目的所采取的另一主要技术手段,是令前述内埋组件的基板结构的制造方法,包括以下步骤。

21.于载板结构的顶部内凹形成容槽,且该载板结构内具有多个第一线路及多个第二线路,使所述第二线路的第一端部外露于该载板结构的顶部,以及使所述第二线路的第二端部外露于该载板结构的底部。

22.于所述载板结构的底部设置第一介电层。

23.于所述载板结构的容槽内设置预设有多个导线件的芯片结构。

24.于所述载板结构的顶部及所述芯片结构上设置第二介电层。

25.使所述芯片结构的导线件及所述载板结构的第二线路的第一端部外露于所述第二介电层,并于所述第二介电层上、所述芯片结构的导线件上以及所述载板结构的第二线路的第一端部上设置第一线路增层结构,且与所述芯片结构上对应的导线件、所述载板结构上对应的第二线路的第一端部电连接。

26.使所述载板结构的第二线路的第二端部外露于所述第一介电层,并于所述第一介电层、所述载板结构的第二线路的第二端部上设置第二线路增层结构,且与所述载板结构上对应的第二线路的第二端部电连接。

27.可选地,所述芯片结构包括架桥芯片以及导线件结构,所述架桥芯片具有相对的顶部及底部以及多个线路及多个接点,所述线路设置在所述架桥芯片内,所述接点间隔设置在所述架桥芯片的顶部上,所述导线件结构具有固定层以及上述所述导线件。形成所述芯片结构的步骤包括:于载件上设置所述固定层,且形成贯穿所述固定层的顶部及底部的多个穿孔;于所述固定层的多个穿孔内设置所述导线件,且所述导线件的第一端部分别接触所述载件,所述导线件的第二端部分别外露于所述固定层的底部;将所述架桥芯片的顶部设置在所述固定层的底部上,且使所述导线件的第二端部分别与所述架桥芯片上对应的接点电连接;移除所述载件;移除所述固定层的顶部,露出所述导线件的第一端部。

28.可选地,于所述载板结构的容槽内设置所述芯片结构之前,于所述容槽内先设置黏着层再将所述芯片结构设置在所述容槽内的黏着层上。

29.可选地,进一步在所述第一线路增层结构上设置电连接层。

30.可选地,于所述基板结构的载板结构的顶部上进一步设置至少一个芯片,所述芯片具有多个接点,设置所述芯片的步骤包括:将所述芯片设置在所述载板结构的顶部上,且使所述芯片的接点经由所述电连接层分别与所述载板结构上对应的第二线路的第一端部以及所述芯片结构上对应的导线件电连接。

31.根据上述方法可知,借由将通过半导体制程方法预先设置、制作预设有导线件的芯片结构固设在载板结构的容槽内,并且于所述载板结构的顶部上设置第二介电层以保护芯片结构,并使芯片结构的导线件外露于所述第二介电层即可。由于不需通过雷射钻孔于载板结构的顶部的介电层上制作对应的雷射穿孔,故可降低因雷射钻孔的精度限制及热扩孔的影响,使相邻导线件连接而短路或导线件空接的问题,借此达到提升基板结构的使用

可靠性以及稳定性的目的。

32.为使能更进一步了解本发明的特征及技术内容,请参阅以下有关本发明的详细说明与附图,但是此等说明与所附附图仅是用来说明本发明,而非对本发明的权利范围作任何的限制。

附图说明

33.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动性的前提下,还可以根据这些附图获得其他的附图。

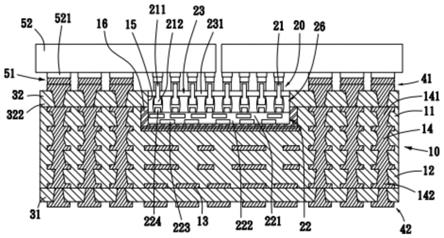

34.图1是本发明的内埋组件的基板结构的示意图;

35.图2是本发明的内埋组件的基板结构的制造方法的流程示意图;

36.图3是本发明的载板结构的示意图;

37.图4是本发明于载板结构上设置芯片结构以及第一介电层的示意图;

38.图5是本发明形成芯片结构的流程示意图;

39.图6是本发明的芯片结构的第一制作流程示意图;

40.图7是本发明的芯片结构的第二制作流程示意图;

41.图8是本发明的芯片结构的第三制作流程示意图;

42.图9是本发明的芯片结构的第四制作流程示意图;

43.图10是本发明的芯片结构的第五制作流程示意图;

44.图11是本发明的芯片结构的第六制作流程示意图;

45.图12是本发明的芯片结构的第七制作流程示意图;

46.图13是本发明的芯片结构的第八制作流程示意图;

47.图14是本发明的芯片结构的第九制作流程示意图;

48.图15是本发明于载板结构以及芯片结构上设置第二介电层的示意图;

49.图16是本发明于载板结构上设置第一线路增层结构及第二线路增层结构的示意图。

50.附图标记

51.10 载板结构

52.11 顶部

53.12 底部

54.13 第一线路

55.14 第二线路

56.15 容槽

57.16 黏着层

58.141 第一端部

59.142 第二端部

60.20 芯片结构

61.21 导线件

62.211 第一端部

63.212 第二端部

64.22 架桥芯片

65.221 顶部

66.222 底部

67.223 线路

68.224 接点

69.23 导线件结构

70.231 固定层

71.2311 顶部

72.2312 底部

73.2313 穿孔

74.24 载件

75.25 光阻遮蔽层

76.26 导电连接层

77.261 电性连接件

78.262 绝缘保护层

79.31 第一介电层

80.311 孔洞

81.32 第二介电层

82.321 顶部

83.322 底部

84.323 孔洞

85.41 第一线路增层结构

86.42 第二线路增层结构

87.51 电连接层

88.52 芯片

89.521 接点

90.s61、s62、s63、s64、s65、s66 步骤

91.s71、s72、s73、s74、s75 步骤

具体实施方式

92.关于本发明所示的附图均为载板结构的局部剖面图,附图中所呈现的相关结构的数量、尺寸大小仅供参考说明,并非在于限制本发明的载板结构的具体结构。此外,本发明中所描述到的方向关系是依据附图中所表示的方向进行说明并非是加以限制。

93.关于本发明内埋组件的基板结构的实施例,请参考图1所示,包括载板结构10、预设有多个导线件21的芯片结构20、第一介电层31、第二介电层32、第一线路增层结构41以及第二线路增层结构42。所述载板结构10具有相对的顶部11及底部12,所述芯片结构20、所述第二介电层32以及所述第一线路增层结构41设置在所述载板结构10的顶部11上,所述第一

deposition/coating)、蒸镀(deposition)或电镀)制作而成。其中所述导线件21的形状以图9的方向来说呈t型,但以图1的方向来说为倒t型,仅为方向改变但不影响实际功用。当制作完成所述导线件21及所述固定层231之后即完成所述导线件结构23的制作,并且如图10所示,将所述光阻遮蔽层25移除。

100.请参考图5、11及12所示,将所述架桥芯片22与所述导线件结构23相结合,其中如步骤s73所示,将所述架桥芯片22的顶部221设置在所述固定层231的底部2312上,使所述导线件21的第二端部212与所述架桥芯片22上对应的接点224电连接。其中为了提升所述架桥芯片22与所述导线件结构23的结合强度并且提供足够的支撑,进一步于所述架桥芯片22与所述导线件结构23之间设置导电连接层26,所述导电连接层26包括多个电性连接件261及绝缘保护层262,所述电性连接件261分别与所述导线件23上对应的第二端部212以及所述架桥芯片22上对应的接点224电连接,所述绝缘保护层262顶撑在所述架桥芯片22与所述导线件结构23之间。

101.进一步,如图5、13所示,如步骤s74所示,移除所述载件24,其中移除所述载件24的方式可以通过例如掀离制程(lift off)方式如雷射、蚀刻方式等。请再参考图5、14所示,于移除所述载件24之后,如步骤s75所示,移除所述固定层231的顶部2311,以露出所述导线件21的第一端部211,其中可通过干蚀刻或者湿蚀刻的方式移除所述固定层231的顶部2311。借由上述步骤s71至s75所示的半导体制程方法完成所述芯片结构20的制作,以预先制作、设置有导线件21的所述芯片结构20,可以有效提升本发明的基板结构制作效率、精准度以及可靠度。

102.根据上述对于所述芯片结构20的制作说明后,在本实施例中,请参考图2、15所示,于步骤s64中,于所述载板结构10的顶部11上以及所述芯片结构20上设置所述第二介电层32,以通过所述第二介电层32覆盖于所述载板结构10的第二线路14的第一端部141以及所述芯片结构20,借此达到保护的效果之外,还强化所述芯片结构20与所述载板结构10的结合强度。

103.在本实施例中,所述第二介电层32可为介电材质氧化膜(如二氧化硅等)、环氧树脂等,并且通过薄膜制作方法(例如溅镀(sputter deposition/coating)、蒸镀(deposition)或涂布(coating))制作而成。

104.于设置所述第二介电层32之后,为了让所述载板结构10的第二线路14的第一端部141、所述芯片结构20的导线件21暴露,以便于与其它外部的组件连接,请参考图2、15、16所示。所述第二介电层32具有相对的顶部321及底部322,并且请参考步骤s65所示,移除所述第二介电层32的顶部321,并且于所述第二介电层32的底部322上形成对应所述载板结构10的第二线路14的第一端部141的多个孔洞323,使所述芯片结构20的导线件21暴露于所述第二介电层32,以及通过所述孔洞323暴露出所述载板结构10的第二线路14的第一端部141。于所述第二介电层32的底部322及孔洞323、所述芯片结构20的导线件21设置所述第一线路增层结构41,且所述第一线路增层结构41与所述芯片结构20的导线件21、所述载板结构10上对应的第二线路14的第一端部141电连接。在本实施例中,是通过干蚀刻或湿蚀刻的方式先移除所述第二介电层32的顶部321之后,再通过雷射钻孔的方式于所述第二介电层32的底部322上形成对应所述载板结构10的第二线路14的第一端部141的孔洞323。

105.于完成第一线路增层结构41的制作后,进一步的请参考图2、16所示,如步骤s66所

示,于所述第一介电层31上形成多个对应所述载板结构10的第二线路14的第二端部142的孔洞311,通过所述孔洞311暴露出所述载板结构10的第二线路14的第二端部142。然后于所述孔洞311设置所述第二线路增层结构42,且所述第二线路增层结构42与所述载板结构10上对应的第二线路14的第二端部142电连接。所述第二线路增层结构42经由所述载板结构10的第二线路14与所述第一线路增层结构41电连接。根据上述本发明的制作方法的步骤s61至s66以完成本发明的基板结构的制作。

106.在本实施例中,请参考图1所示,进一步于所述载板结构10与所述芯片结构20上设有电连接层51,所述电连接层51与所述载板结构10上对应的第二线路14的第一端部141电连接以及与所述芯片结构20上对应的导线件21电连接,以供后续与其它组件电连接。在本实施例中,所述电连接层51是包括多个焊点。

107.当完成本发明的基板结构的制作之后,若要与外部的组件电连接时,请参看图1所示,于所述基板结构的载板结构10的顶部11上进一步设置至少一个芯片52,于本实施例中是设置二个芯片52进行说明但并非以此为限。所述芯片52分别具有多个接点521,其中一个芯片52中的部分接点521经由对应的电连接层51与所述芯片结构20上对应的导线件21电连接,其余部分的接点521经由对应的电连接层51与所述载板结构10上对应的第二线路14的第一端部141电连接。另外一个芯片中的部分接点521经由对应的电连接层51与所述芯片结构20上对应的导线件21电连接,其余部分的接点521经由对应的电连接层51与所述载板结构10上对应的第二线路14的第一端部141电连接。其中,所述芯片52可为发光二极管(light emitting diode,led)、集成电路等。

108.根据上述内容,借由将通过半导体制程方法预先设置、制作导线件21的芯片结构20固设在载板结构10的容槽15内,并且于所述载板结构10的顶部11上设置第二介电层32以保护芯片结构20,并使芯片结构20的导线件21暴露于所述第二介电层32即可。由于不需通过雷射钻孔于载板结构10的顶部11的第二介电层32上制作对应的雷射穿孔,故可改善因雷射钻孔的精度及热扩孔的限制,使相邻导线件连接而短路或导线件空接的问题,借此达到提升可靠性以及稳定性的目的。

109.以上所述仅为本发明的实施例,其并非用以局限本发明的专利范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1