一种硅基背照PIN器件结构的制备方法与流程

一种硅基背照pin器件结构的制备方法

技术领域

[0001]

本发明涉及半导体光电技术领域,具体是一种硅基背照pin器件结构的制备方法。

背景技术:

[0002]

耗尽型光电探测器pin光电二极管经常被使用在激光方位探测中,之所以这种器件叫做pin 光电二极管,主要就是因为有一层本征层(i 层)在p

--

n结之间。

[0003]

pin结构光电探测器具有高灵敏度和高分辨率、低功耗、响应速度快等特点,广泛应用于光通信、其他快速光电自动控制装备系统领域;pin光敏二极管由于其结构的优越性和良好的光电响应特性,在光通信、光测距、光度测量及光电控制等方面有着重要的应用。

[0004]

为了更好地改善波长范围和频响,往往对控制本征层的厚度进行有效地控制,这样减少其和反偏压下耗尽层宽度的差距。器件的灵敏度和频响在很大程度上取决于pin光电二极管中的本征层。这主要是因为本征层和p区n区比较是高阻区,本征层是反向偏压比较集中的区域,也正是因为如此,高电场区就在这个区间形成,而高电场区的电阻大,故而减小了暗电流。本征层引入之后能够加大耗尽层区,因此光电转换的有效区域得以增加,从而明显提高了其灵敏性。

[0005] p区非常薄,加之本征层的作用,所以在本征层内入射光子就能都被吸收,这样也就形成了电子

--

空穴对。在强电场作用下,光生载流子加速运动,这就缩短了截流子的渡越时间。由于加宽了耗尽层,导致结电容c

d 减小,从而电容时间常数也相应地减小,这样就使光电二极管的频响得到了很好地改善。若是光电二极管的性能良好,则其一般会有10-10

s量级的扩散与漂移时间,故而电路时间常数是影响光电二极管频响的主因,一般来讲,光电二极管的结电容通常为几个皮法。如果将反向偏压适当增大的话,还会使减小。为了得到高响应频率性能,在实际的应用中,需要注意的就是合理选择负载电阻 。

[0006]

目前,诸多pin光电探测器件得到了广泛应用,现有的pin光电探测器都是前照式,通过各组件组装而成,体积大,已经不能适应复杂环境下的应用。

技术实现要素:

[0007]

本发明的目的在于提供一种硅基背照pin器件结构的制备方法,该方法通过背照pin结构植球压焊方式将pin光电探测器组件体积至少减小三分之二,实现pin光电探测器p+与n+处于横向互连,基于背照pin结构,完成了pin结构光电探测器系统集成一体化,同时满足光电性能要求。

[0008]

本发明解决其技术问题所采用的技术方案是:一种硅基背照pin器件结构的制备方法,包括以下步骤:s1、取p型硅晶圆片作为基片;s2、清洗基片,去除基片表面污垢;s3、通过光刻工艺在基片正面进行p+光刻;s4、在p+光刻区域进行p+离子注入;

s5、通过氧化扩散进行p+离子主扩;s6、在基片表面生长外延层;s7、在外延层表面进行初始氧化,得到氧化层;s8、通过光刻工艺进行p阱光刻,p阱光刻位置与p+光刻位置相对应;s9、在p阱光刻位置进行p阱注入与推阱;s10、通过光刻工艺进行n环光刻,形成n保护环区图形;s11、通过离子注入技术进行n环注入;s12、通过光刻工艺进行p隔离光刻,形成p隔离区图形;s13、在p隔离区进行p隔离注入与推进;s14、通过光刻工艺进行n-光敏区光刻,形成n-光敏区图形;s15、进行n-光敏区注入与n-氧化;s16、通过光刻工艺进行孔光刻,形成引线孔图形;s17、正面金属化,利用溅射和光刻工艺,在引线孔图形位置形成铝引线,实现器件结构的自连与互连;s18、对基片背面进行减薄;s19、在基片背面沉积抗反射膜;s20、对背面金属化处理,将光敏区进行四象限隔离,得到所述硅基背照pin器件。

[0009]

进一步的,步骤s1基片选择为p型(100)6寸硅晶圆片,电阻率为8ω.cm~13ω.cm,厚度675μm

±

15μm。

[0010]

进一步的,步骤s3所述p+光刻按照以下步骤执行:s31、匀胶,选用正性光刻胶,先在硅片表面用hmds进行增粘处理,然后旋转涂胶,胶厚(1.0

±

0.1)μm;s32、前烘,将涂覆好光刻胶的硅片放热板上,温度设置为(100

±

5)℃,时间为1min;s33、曝光,用光刻掩模版在光刻机上进行图形套准曝光,套准精度为

±

0.5μm;s34、显影,显影温度20

±

)℃;显影时间1

±

0.1min;去离子水冲洗离心干燥,去离子水电阻率≥18mω.cm;s35、后烘,将显影后的硅片放入充氮烘箱中,温度120

±

5℃,时间为30

±

2min。

[0011]

进一步的,步骤s4所述p+离子注入利用离子注入技术,注入剂量为3e15的硼杂质,注入能量为70kev。

[0012]

进一步的,步骤s15所述n-光敏区注入利用离子注入技术,注入剂量为7e12的p

31+

杂质,注入能量为250kev。

[0013]

进一步的,步骤s18将基片减薄至200μm

±

10μm。

[0014]

本发明的有益效果是,将传统的pin光电探测器组件大体积组装进行微系统化集成,通过背照pin结构植球压焊方式将pin光电探测器组件体积至少减小三分之二,实现pin光电探测器p+与n+处于横向互连,基于背照pin结构,完成了pin结构光电探测器系统集成一体化,同时其光电性能参数满足设计要求。

附图说明

[0015]

下面结合附图和实施例对本发明进一步说明:

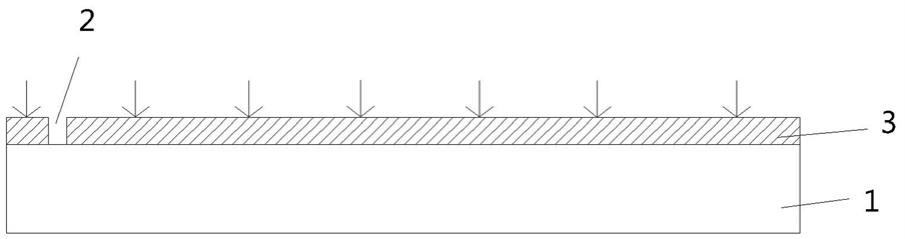

图1是本发明步骤s1的示意图;图2是本发明步骤s3的示意图;图3是本发明步骤s4与s5的示意图;图4是本发明步骤s6的示意图;图5是本发明步骤s7的示意图;图6是本发明步骤s8的示意图;图7是本发明步骤s9的示意图;图8是本发明步骤s10与s11的示意图;图9是本发明步骤s12的示意图;图10是本发明步骤s13的示意图;图11是本发明步骤s14的示意图;图12是本发明步骤s15的示意图;图13是本发明步骤s16的示意图;图14是本发明步骤s17的示意图;图15是本发明步骤s18的示意图;图16是本发明步骤s19的示意图;图17是本发明步骤s20的示意图。

具体实施方式

[0016]

本发明提供一种硅基背照pin器件结构的制备方法,包括以下步骤:s1、如图1所示,取p型硅晶圆片作为基片1;选择p型(100)6寸硅晶圆片,电阻率为8ω.cm~13ω.cm,厚度675μm

±

15μm;s2、清洗基片1,去除基片表面污垢;采用标准rca清洗,可以有效的去除晶圆表面的杂质污染物,可以有效的提高晶圆氧化层质量;rca清洗过程中化学试剂的配比与环境温度:1、名称:sc-1,rca-1,化学成分:nh4oh:h2o2:h2o,配比:1:2:12.5,65℃;2、名称:sc-2,rca-2,化学成分:hcl:h2o2:h2o,配比:1:2:12.5,65℃;3、名称:spm,化学成分:h2so4:h2o2,配比:4:1,65℃;4、名称:稀释hf,化学成分:hf:h2o,配比:1:100,23℃;s3、结合图2所示,通过光刻工艺在基片1正面进行p+光刻,形成p+图形2;p+光刻按照以下步骤执行:s31、匀胶,选用正性光刻胶3,先在硅片表面用hmds进行增粘处理,然后旋转涂胶,胶厚(1.0

±

0.1)μm;s32、前烘,将涂覆好光刻胶的硅片放热板上,温度设置为(100

±

5)℃,时间为1min;s33、曝光,用光刻掩模版在光刻机上进行图形套准曝光,套准精度为

±

0.5μm;s34、显影,显影温度20

±

)℃;显影时间1

±

0.1min;去离子水冲洗离心干燥,去离子水电阻率≥18mω.cm;s35、后烘,将显影后的硅片放入充氮烘箱中,温度120

±

5℃,时间为30

±

2min;

s4、结合图3所示,在p+光刻区域进行p+离子4的注入;利用离子注入技术,注入剂量为3e15的硼杂质,注入能量为70kev;s5、通过氧化扩散进行p+离子主扩;在氧化扩散炉800℃~1130℃~800℃的升温降温条件下,采用50min(n2+o2)升温并稳定,再经过60minn2+5mino2+n2(降温至800℃),使注入的硼杂质再分布到一定的结深;s6、结合图4所示,在基片表面生长外延层5;利用hcl抛光腐蚀硅50~100nm,生长参数为ρ:>8000ω.cm,w:厚度80μm

±

5μm;s7、结合图5所示,在外延层5表面进行初始氧化,得到so2氧化层6;氧化温度控制在920

±

0.5℃,氧化时间:5分钟(干氧)+30分钟(dce+o2)+5分钟(干氧);氧化层厚度50

±

5nm;s8、结合图6所示,通过光刻工艺进行p阱光刻,p阱光刻区域7与p+光刻位置相对应;s9、结合图7所示,在p阱光刻位置进行p阱8的注入与推阱;采用阶梯式离子注入,即注入能量为800kev,2e14,+能量为120kev,5e15;在氧化扩散炉温度为800℃~1180℃~800℃的升温降温条件下,采用(n2+o2)升温,再经过10mino2+840minn2+n2降温(至800℃),使注入的硼杂质再分布扩散,形成一定结深;s10、结合图8所示,通过光刻工艺进行n环光刻,形成n保护环区图形9;s11、通过离子注入技术进行n环注入;利用离子注入技术,注入剂量为4e15的p31

+

杂质,注入能量为120kev;s12、结合图9所示,通过光刻工艺进行p隔离光刻,形成p隔离区图形10;s13、结合图10所示,在p隔离区进行p隔离注入与推进,得到n+保护环11;利用离子注入技术,注入剂量为2.5e15的b

11+

杂质,注入能量为50kev;在氧化扩散炉温度为800℃~1130℃~920℃~800℃升温降温条件下,采用(n2+o2)升温+1h 再n2+80minn2(降温至920℃)然后+10mino2+50min(h2+o2)+10mino2+15min n

2 ,再 n2降温(至800℃)使注入的n+保护环以及p+隔离杂质激活并形成一定结深;s14、结合图11所示,通过光刻工艺进行n-光敏区光刻,形成n-光敏区图形11;s15、结合图12所示,进行n-光敏区注入与n-氧化,得到n-光敏层13;利用离子注入技术,注入剂量为7e12的p

31+

杂质,注入能量为250kev;在氧化扩散炉温度为800℃~920℃~800℃的升温降温条件下,采用(n2+o2)升温,然后+10mino2+10min(dce+o2)+10mino2+50min(dce+o2)+10mino2+15min n

2 ,再 n2降温(至800℃);使注入的n-杂质激活并形成一定结深,同时形成光敏区氧化膜;s16、结合图13所示,通过光刻工艺进行孔光刻,形成引线孔图形14;s17、结合图14所示,正面金属化,利用溅射和光刻工艺,在引线孔图形位置形成铝引线15,实现器件结构的自连与互连;s18、结合图15所示,对基片1背面进行减薄;将基片减薄至200μm

±

10μm;s19、结合图16所示,在基片背面沉积抗反射膜16;用于提高光电转化效率;s20、结合图17所示,对背面金属化处理,通过al隔离层17将光敏区进行四象限隔离,得到所述硅基背照pin器件。

[0017]

以上所述,仅是本发明的较佳实施例而已,并非对本发明作任何形式上的限制;任何熟悉本领域的技术人员,在不脱离本发明技术方案范围情况下,都可利用上述揭示的方

法和技术内容对本发明技术方案做出许多可能的变动和修饰,或修改为等同变化的等效实施例。因此,凡是未脱离本发明技术方案的内容,依据本发明的技术实质对以上实施例所做的任何简单修改、等同替换、等效变化及修饰,均仍属于本发明技术方案保护的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1