多芯片封装件及其制造方法与流程

1.本发明涉及半导体封装件及其制造方法,且特别是涉及一种多芯片封装件及其制造方法。

背景技术:

2.为了使半导体封装件同时具有轻薄体积以及高性能,目前的封装技术已尝试将多个半导体芯片整合于单一半导体封装件中而形成多芯片封装件或是以3维堆叠技术堆叠多个半导体封装件而形成堆叠式封装件(package on package,pop)结构。然而,现有的多芯片封装件中的多个半导体芯片之间的信号沟通速度受限,因此半导体封装件的整体效能仍有待进一步的提升。

技术实现要素:

3.本发明之目的是提供一种效能良好的多芯片封装件。

4.本发明提供一种多芯片封装件,包括重配置线路结构、第一半导体芯片、第二半导体芯片及第一包封体。所述第一半导体芯片具有第一主动(有源)面及与所述第一主动面相对的第一背面。所述第一主动面上配置有第一导电柱。所述第一半导体芯片配置在所述重配置线路结构上,且所述第一背面面向所述重配置线路结构。所述第二半导体芯片配置在所述第一半导体芯片上方且具有第二主动面。所述第二主动面上配置有第一导体。所述第一导体在与所述第二主动面垂直的方向上与所述第一半导体芯片交叠。所述第一包封体配置于所述重配置线路结构上且至少包封所述第一半导体芯片,其中所述第一导电柱与所述第一导体彼此对准并接合以电连接所述第一半导体芯片与所述第二半导体芯片。

5.本发明提供一种多芯片封装件,包括第一重配置线路结构、多个下部半导体芯片、上部半导体芯片、第一包封体以及第二包封体。所述多个下部半导体芯片分别具有第一主动面及与所述第一主动面相对的第一背面,所述第一主动面上配置有第一导体,所述多个下部半导体芯片并排地配置在所述第一重配置线路结构上,且所述第一背面面向所述第一重配置线路结构。所述上部半导体芯片配置在所述多个下部半导体芯片上方且具有配置有第一导电柱的第二主动面。所述上部半导体芯片的所述第一导电柱与所述多个下部半导体芯片的所述第一导体对准且接合。所述第一导体在与所述第二主动面垂直的方向上与所述上部半导体芯片交叠。所述第一包封体配置于所述第一重配置线路结构上且包封所述多个下部半导体芯片的至少部分。所述第二包封体配置于所述第一包封体上且包封所述上部半导体芯片。

6.本发明提供一种多芯片封装件,包括中介连接结构、导电柱、第一下部半导体芯片、第二下部半导体芯片、第一上部半导体芯片以及第二上部半导体芯片。所述中介连接结构具有第一表面以及与所述第一表面相对的第二表面且包括导电图案。所述导电柱位于所述中介连接结构的所述第一表面上且电连接至所述导电图案。所述第一下部半导体芯片以及所述第二下部半导体芯片并排地位于所述中介连接结构的所述第一表面上且电连接至

所述导电图案。所述第一上部半导体芯片以及所述第二上部半导体芯片并排地位于所述中介连接结构的所述第二表面上且电连接至所述导电图案。所述第一上部半导体芯片在与所述中介连接结构的所述第一表面垂直的方向上与所述第一下部半导体芯片以及所述导电柱交叠,且所述第二上部半导体芯片在与所述中介连接结构的所述第一表面垂直的方向上同时与所述第一下部半导体芯片以及所述第二下部半导体芯片交叠。

7.本发明提供一种制造多芯片封装件的方法,包括以下步骤。在重配置线路结构上设置第一半导体芯片使得所述第一半导体芯片的第一主动面与所述第一半导体芯片的紧邻所述重配置线路结构的表面相对。所述第一半导体芯片的第一主动面上配置有第一导电柱。在所述重配置线路结构上设置第一包封体以包封所述第一半导体芯片。移除部分第一包封体以使所述第一导电柱自所述第一包封体暴露出来。在所述第一半导体芯片上方设置第二半导体芯片以使得所述第二半导体芯片的第二主动面上的第一导体与所述第一导电柱对准且接合,其中所述第一导体在与所述第二主动面垂直的方向上与所述第一半导体芯片交叠。

8.本发明提供一种制造多芯片封装件的方法,包括以下步骤。于载体基板上设置第一半导体芯片使得所述第一半导体芯片的第一主动面与所述第一半导体芯片的紧邻所述载体基板的表面相对。所述第一半导体芯片的第一主动面上配置有第一导体与第二导体。在所述载体基板上设置第一包封体以包封所述第一半导体芯片。移除部分第一包封体以使所述第一导体与所述第二导体自所述第一包封体暴露出来。在所述第一半导体芯片上方设置第二半导体芯片以使得所述第二半导体芯片的第二主动面上的第一导电柱与所述第一导体对准且接合,所述第一导体在与所述第二主动面垂直的方向上与所述第二半导体芯片交叠。在所述第一包封体与所述第二半导体芯片的所述第二主动面之间设置底胶以包封所述第一导电柱。在所述第一包封体上设置第二包封体以包封所述第二半导体芯片。移除部分所述第二包封体以暴露出所述第二半导体芯片的与所述第二主动面相对的表面。在所述第二包封体上设置重配置线路结构。最后移除所述载体基板。

9.基于上述,本发明的多芯片封装件可以达到提升多芯片封装件的整体效能。

10.为让本发明的上述特征和优点能更明显易懂,下文特举实施例,并配合所附附图作详细说明如下。

附图说明

11.包含附图以便进一步理解本发明,且附图并入本说明书中并构成本说明书的一部分。附图说明本发明的实施例,并与描述一起用于解释本发明的原理。

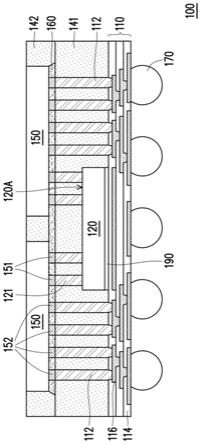

12.图1a至图1i是本发明的一实施例的制造多芯片封装件的制造流程步骤的剖面示意图;

13.图2是本发明的一实施例的多芯片封装件的剖面示意图;

14.图3是本发明的另一实施例的多芯片封装件的剖面示意图;

15.图4是本发明的另一实施例的多芯片封装件的剖面示意图;

16.图5是本发明的另一实施例的多芯片封装件的剖面示意图;

17.图6a至图6j是本发明的一实施例的制造多芯片封装件的制造流程步骤的剖面示意图;

18.图7a到图7h是本发明的第一导体与第一导电柱的连接方法的各种实施例的示意图;

19.图8是本发明的一实施例的多芯片封装件的剖面示意图;

20.图9a至图9i是本发明的一实施例的制造多芯片封装件的制造流程步骤的剖面示意图;

21.图10是本发明的一实施例的多芯片封装件的剖面示意图;

22.图11是本发明的一实施例的堆叠式封装件(package on package,pop)的剖面示意图;

23.图12是本发明的一实施例的堆叠式封装件的剖面示意图;

24.图13a至图13l是本发明的一实施例的制造多芯片封装件的制造流程步骤的剖面示意图;

25.图14a至图14o是本发明的一实施例的制造多芯片封装件800的制造流程步骤的剖面示意图;

26.图15a至图15n是本发明的一实施例的制造多芯片封装件900的制造流程步骤的剖面示意图;

27.图16是本发明的一实施例的堆叠式封装件的剖面示意图;

28.图17是本发明的一实施例的堆叠式封装件的剖面示意图;

29.图18是本发明的一实施例的堆叠式封装件的剖面示意图。

30.附图标号说明

31.100、200、300、400、500、600、700、800、900:多芯片封装件;

32.1000、2000:堆叠式封装件;

33.100a:下部半导体封装件;

34.100b:上部半导体封装件;

35.200b:图像传感器封装件;

36.10:载体;

37.12:基底;

38.13、16、17:半导体芯片;

39.14:焊线;

40.15:包封体;

41.20:离型膜;

42.23:图像传感器芯片;

43.25:透光基板;

44.27:线路层;

45.29:连接导体;

46.110:重配置线路结构;

47.112:第二导电柱;

48.113:第三导电柱;

49.114、274:介电层;

50.116:重配置布线层;

51.120:下部半导体芯片;

52.120a:主动面;

53.121:第一导电柱;

54.121a:保护层;

55.125:接合金属;

56.126:氧化保护层;

57.140:顶部重配置线路结构;

58.141:第一包封体;

59.142、142a、142b:第二包封体;

60.150:上部半导体芯片;

61.151:第一导体;

62.152:第二导体;

63.160、660:底胶;

64.161:第一底胶;

65.165:保护层;

66.170:导电端子;

67.180:中间导电端子;

68.190:黏着剂层;

69.212:导电柱;

70.220:第一下部半导体芯片;

71.220p:第一下部连接导体;

72.230:第二下部半导体芯片;

73.230p:第二下部连接导体;

74.232:导电穿孔结构;

75.240:第一上部半导体芯片;

76.240p:第一上部连接导体;

77.250:第二上部半导体芯片;

78.250p:第二上部连接导体;

79.270:中介连接结构;

80.271:第一导电图案;

81.272:第二导电图案;

82.273:导电通孔图案;

83.280:接合结构;

84.322:传感区;

85.323:微透镜;

86.325:密封结构;

87.330:盖体;

88.350:图像传感器芯片;

89.350a:传感面;

90.420:下部半导体元件;

91.422:第一半导体芯片;

92.422p:第一连接导体;

93.424:第二半导体芯片;

94.424p:第二连接导体;

95.440:图像传感器半导体元件;

96.442:第三半导体芯片;

97.442p:第三连接导体;

98.444:第四半导体芯片;

99.444p:第四连接导体;

100.460:上部半导体元件;

101.462:第五半导体芯片;

102.462p:第五连接导体;

103.464:第六半导体芯片;

104.464p:第六连接导体;

105.610:第一重配置线路结构;

106.613:下部导电柱;

107.614:第一介电层;

108.616:第一重配置布线层;

109.620:下部半导体芯片;

110.620a:第一主动面;

111.620b:第一背面;

112.621:第一导体;

113.622:第二导体;

114.640:第二重配置线路结构;

115.642:第二导电柱;

116.643:第三导电柱;

117.644:第二介电层;

118.646:第二重配置布线层;

119.650:上部半导体芯片;

120.650a:第二主动面;

121.651:第一导电柱;

122.a:部分;

123.db、df、di、dn、do、dt:宽度;

124.114h、614h、o1、o2:开口;

125.s1:顶部表面;

126.α、β:角度。

deposition,cvd)、等离子体增强型化学气相沉积(plasma-enhanced chemical vapor deposition,pecvd)等。介电层114的材料可包括聚酰亚胺、环氧树脂、丙烯酸树脂、酚醛树脂、双马来酰亚胺-三氮杂苯树脂(bismaleimide-trazine resin,bt resin)或任何其他合适的聚合物系介电材料以及氧化硅层、氮化硅层、氮氧化硅层或其他合适的硅介电材料。介电层114可以是包括感光性绝缘树脂的感光性绝缘层。

135.重配置线路结构110可包括多层或单层重配置布线层116。当重配置线路结构110包括多层重配置布线层116时,形成上层的重配置布线层116的工艺包括以下步骤。首先,在介电层114中形成开口114h以暴露出其下的重配置布线层116,其中于介电层114中形成开口114h的方法可取决于介电层114的材料而采用不同的工艺。当介电层114为包括感光性绝缘树脂的感光性绝缘层时,介电层114可通过光刻工艺进行图案化以形成开口114h。当介电层114为非感光性绝缘层时,介电层114可通过光刻/蚀刻工艺、激光钻孔工艺或机械钻孔工艺进行图案化以形成开口114h。参照图1b中的放大图,在介电层114中所形成的开口114h的上部宽度dt可大于下部宽度db。也就是说,开口114h的倾斜侧壁(tapered sidewalls)与介电层114的上表面间的夹角α可大于90

°

。接着以与上述形成重配置布线层116的方法相同的方法形成上层的重配置布线层116以连接到经由介电层114的开口114h所暴露出的重配置布线层116。虽然在附图中,重配置线路结构110绘示为包括三层介电层114与三层重配置布线层116,但本发明不以此为限,重配置线路结构110可包括较附图更多层或更少层的介电层114与重配置布线层116。

136.参照图1c,可在重配置线路结构110上形成第二导电柱112。举例来说,形成第二导电柱112的工艺包括以下步骤。首先,在重配置线路结构110的介电层114中形成开口以暴露出重配置布线层116,其中于介电层114中形成开口的方法可取决于介电层114的材料而采用不同的工艺。当介电层114为包括感光性绝缘树脂的感光性绝缘层时,介电层114可通过光刻工艺进行图案化以形成开口。当介电层114为非感光性绝缘层时,介电层114可通过光刻/蚀刻工艺、激光钻孔工艺或机械钻孔工艺进行图案化以形成开口。开口的上部宽度可大于下部宽度。也就是说,开口的倾斜侧壁与介电层114的上表面间的夹角可大于90

°

。之后,在介电层114以及被开口暴露出的重配置布线层116的表面上形成晶种层。晶种层的材料可例如为钛/铜等导电材料。接着,在晶种层上形成图案化的光致抗蚀剂层。图案化的光致抗蚀剂层可利用光刻以及/或蚀刻工艺来形成。图案化的光致抗蚀剂层的开口暴露出重配置布线层116上的晶种层的表面。接着,可于图案化的光致抗蚀剂层的开口中形成多个导电柱状结构。导电柱状结构的形成方法可例如是印刷、电镀、无电电镀或其组合。之后,移除图案化的光致抗蚀剂层以及部分晶种层而形成第二导电柱112。第二导电柱112的材料可利用电特性优异的金属或其合金形成,例如铜(cu)、银(ag)、钯(pd)、铝(al)、镍(ni)、钛(ti)、金(au)、铂(pt)、钨(w)或其合金。

137.参照图1d(a),可将下部半导体芯片120通过例如芯片黏结薄膜(daf)等黏着剂层190以背面贴附至重配置线路结构110上。下部半导体芯片120可为形成有半导体集成电路的半导体芯片,例如存储器芯片、逻辑芯片、数字芯片、模拟芯片、传感器芯片(sensor chip)、人工智能芯片(ai chip)、无线射频芯片(wireless and radio frequency chip)或电压调节器芯片等。其中传感器芯片可为图像传感器芯片,至少包括电荷耦合元件(ccd)或互补金属氧化物半导体图像传感器(cmos image sensor)。虽然附图中未绘示,但在一些实

施例中,下部半导体芯片120中可具有例如硅穿孔(through silicon via,tsv)或玻璃穿孔(through glass via,tgv)等导电穿孔结构以在下部半导体芯片120中形成垂直连接通路。也就是说,下部半导体芯片120可通过所述导电穿孔结构自主动面120a及/或与主动面120a相对的表面与其它组件电连接。举例来说,下部半导体芯片120也可通过导电穿孔结构电连接至重配置线路结构110。下部半导体芯片120在主动面120a上具有第一导电柱121。第一导电柱121的材料可包括例如铜(cu)、银(ag)、钯(pd)、铝(al)、镍(ni)、钛(ti)、金(au)、铂(pt)、钨(w)或其他电特性优异的金属或其合金。参照图1d(b),在另一实施例中,下部半导体芯片120在主动面120a上可包括保护层121a以保护第一导电柱121。举例来说,第一导电柱121可嵌置于保护层121a中。也就是说,保护层121a可完全包封第一导电柱121。保护层121a的材料可包括模塑化合物、模塑底部填料、树脂或环氧模制化合物(epoxy molding compound,emc)等有机绝缘材料。本发明的保护层121a的材料与配置形式不以此为限。举例来说,保护层121a也可包封第一导电柱121的一部分。视需要,也可省略保护层121a。

138.参照图1e与图1f,形成第一包封体141,所述第一包封体141包覆下部半导体芯片120与第二导电柱112。第一包封体141的材料可包括模塑化合物、模塑底部填料、树脂或环氧模制化合物(epoxy molding compound,emc)等。视需要,第一包封体141中可掺杂有无机填料。形成第一包封体141的方法包括以下步骤。通过合适的工艺(例如模塑工艺或沉积工艺)在载体10之上形成覆盖重配置线路结构110、下部半导体芯片120与第二导电柱112的包封材料层,此后,执行表面研磨抛光工艺(wafer grinding)或者表面平坦化工艺(surface planarization)使得第一导电柱121与第二导电柱112的表面(如图1f所示)暴露出来。也就是说,第一导电柱121与第二导电柱112的上表面位于相同的水平高度上。换句话说第一导电柱121、第二导电柱112及第一包封体141的上表面共面。第一导电柱121及第二导电柱112也可自第一包封体141的上表面略微突出。第一导电柱121及第二导电柱112也可自第一包封体141的上表面略微凹陷。在第一导电柱121与第二导电柱112的上表面自第一包封体141的上表面略微凹陷的情况下,有利于第一导电柱121与第二导电柱112在后续步骤中与上部半导体芯片150对准并接合。

139.在本文中,第一导电柱121的高度是指自下部半导体芯片120的主动面120a到第一导电柱121的上表面的垂直距离,且第二导电柱112的高度是指自重配置线路结构110的与下部半导体芯片120紧邻的表面到第二导电柱112的上表面的垂直距离。第二导电柱112的高度可大于第一导电柱121的高度。第一导电柱121的宽度与第二导电柱112的宽度可彼此相同。或者,第一导电柱121的宽度与第二导电柱112的宽度可彼此不同。举例来说,第一导电柱121的高度可例如为12微米至25微米,且第一导电柱121的高宽比(aspect ratio)可介于0.3至1.2。第二导电柱112的高度可例如为130微米至300微米且第二导电柱112的高宽比可介于1.2至3。

140.参照图1g,提供上部半导体芯片150至第一包封体141上以使上部半导体芯片150的主动面上的第一导体151与第一导电柱121彼此对准并连接,并且使上部半导体芯片150的主动面上的第二导体152与第二导电柱112彼此对准并连接,进而使上部半导体芯片150、下部半导体芯片120以及重配置线路结构110彼此电连接。换言之,上部半导体芯片150的第一导体151与第一导电柱121之间的电连接以及上部半导体芯片150的第二导体152与第二导电柱112之间的电连接不通过重配置线路结构来达成。在此情况下,不但封装工艺可被简

化,且上部半导体芯片150与第一导电柱121以及第二导电柱112之间的电连接路径可有效地缩短,进而提升上部半导体芯片150与下部半导体芯片120之间的沟通效能。

141.上部半导体芯片150的第一导体151在与下部半导体芯片120的主动面120a垂直的方向上与下部半导体芯片120交叠,且上部半导体芯片150的第二导体152在与下部半导体芯片120的主动面120a垂直的方向上不与下部半导体芯片120交叠。第一导体151与第二导体152的材料可包括铜(cu)、银(ag)、钯(pd)、铝(al)、镍(ni)、钛(ti)、金(au)、铂(pt)、钨(w)或其合金等导电材料。第一导体151与第二导体152的形状可包括柱状或图钉状凸块(stud bump)等各种形状。第一导体151与第一导电柱121的连接以及第二导体152与第二导电柱112的连接的方法可例如为通过加热而直接接合或利用接合金属接合。举例来说,可在第一导体151与第一导电柱121之间及第二导体152与第二导电柱112之间配置焊锡合金、铜、金、银、铟、钯、钛、锰、钴、或其合金等接合金属,并对其加热而接合第一导体151与第一导电柱121以及第二导体152与第二导电柱112。第一导体151与第一导电柱121的连接及第二导体152与第二导电柱112的连接也可以不使用焊料。也就是说,第一导体151与第一导电柱121的连接及第二导体152与第二导电柱112的连接可不使用焊锡合金。接合金属可为熔点低于200℃的低温接合金属。举例来说,低温接合金属可包括双晶铜、双晶银或其他纳米双晶材料、铟锡合金、锡铋合金、多孔金或其组合。相对于传统焊球或焊料所需回焊温度多高于或等于250℃,使用低温接合金属可在相对较低的加热温度下(例如,在低于200℃或低于150℃的温度下)使得连接结构达到稳定接合,且满足电连接要求的可靠度要求。

142.继续回到图1g,图1g中绘示多芯片封装件中包括二个上部半导体芯片150,但本发明不限于此。上部半导体芯片150可包括单个上部半导体芯片150或并排设置于第一包封体141上的多个上部半导体芯片150。所述多个上部半导体芯片150的功能可彼此相同。或者,所述多个上部半导体芯片150的功能可彼此不同。上部半导体芯片150可为形成有半导体集成电路的半导体芯片,例如存储器芯片、逻辑芯片、数字芯片、模拟芯片、传感器芯片(sensor chip)、人工智能芯片(ai chip)、无线射频芯片(wireless and radio frequency chip)或电压调节器芯片等。其中传感器芯片可为图像传感器芯片,至少包括电荷耦合元件(ccd)或互补金属氧化物半导体图像传感器(cmos image sensor)。

143.再继续参照图1g,可在第一包封体141上施加底胶160以包封第一导体151与第二导体152。底胶160可填充上部半导体芯片150与第一包封体141之间的空间并包封第一导体151与第二导体152。如图1g所示,底胶160具有倾斜侧壁,且底胶160的上部宽度例如会小于底胶160的下部宽度。在一些实施例中,底胶160的宽度是渐变的,且底胶160的宽度从较靠近第一包封体141的一端朝着较靠近上部半导体芯片150的另一端逐渐缩减。

144.参照图1h,形成第二包封体142,所述第二包封体142包覆上部半导体芯片150。第二包封体142的材料可包括模塑化合物、模塑底部填料、树脂或环氧模制化合物(epoxy molding compound,emc)等。视需要,第二包封体142中可掺杂有无机填料。形成第二包封体142的方法包括以下步骤。通过合适的工艺(例如模塑工艺或沉积工艺)在载体10之上形成覆盖第一包封体141、上部半导体芯片150与底胶160的包封材料层,此后,执行表面研磨抛光工艺(wafer grinding)或者表面平坦化工艺(surface planarization)使得上部半导体芯片150的表面暴露出来。第一包封体141的材料与第二包封体142的材料可彼此相同。或者,第一包封体141的材料与第二包封体142的材料可彼此不同。如图1h中所示,第二包封体

142可包括与第一包封体141直接接触的部分142a以及通过底胶160与第一包封体141彼此隔开的部分142b。

145.参照图1h与图1i,进行一离型工艺,以使图1i中所示的结构与载体10及离型膜20分离。当离型膜20是由紫外线胶所形成时,前述的离型工艺可将紫外光照射于离型膜20上,以使离型膜20丧失或降低其黏性,进而使得载体10以及离型膜20能够与图1h中所示的结构分离。当离型膜20是由光热转换胶所形成时,前述的离型工艺可将适当能量的光照射于离型膜20上,以使离型膜20在光的热能作用下分解而丧失或降低其黏性,进而使得载体10以及离型膜20能够与图1i中所示的结构分离。

146.参照图2,可在重配置线路结构110上形成多个导电端子170而完成本发明的多芯片封装件100。导电端子170例如是焊球,但本发明不限于此。可在大尺寸的芯片上同时形成多个本发明的多芯片封装件100,接着,再通过切割等工艺以分离个别多芯片封装件100。因此本发明的多芯片封装件100中的第一包封体141的侧壁、第二包封体142的侧壁可与重配置线路结构110的侧壁对准。

147.在本发明的多芯片封装件100中,下部半导体芯片120与上部半导体芯片150通过下部半导体芯片120的第一导电柱121与上部半导体芯片150的第一导体151彼此连接。换句话说,下部半导体芯片120与上部半导体芯片150间没有设置重配置线路结构。由于下部半导体芯片120与上部半导体芯片150没有经由重配置线路结构连接而是直接经由下部半导体芯片120的第一导电柱121与上部半导体芯片150的第一导体151连接,因此可缩短下部半导体芯片120与上部半导体芯片150之间的电源及/或信号的传递路径,而提高电源及/或信号的传递速度与品质。

148.在本发明的多芯片封装件100中,多个并排的上部半导体芯片150之间可通过下部半导体芯片120的内部线路结构彼此连接。一般而言,多个并排的半导体芯片使用重配置线路结构或焊线彼此连接。在一般的重配置线路结构中,线宽与线距都大约为2微米、通孔(via)的宽度大约为5微米、连接垫的宽度大约为7微米,且层数一般为3层。而在半导体芯片的内部线路结构中,线宽与线距都大约为0.4微米、通孔(via)的宽度大约为0.4微米、连接垫的宽度大约为0.7微米且层数一般为4层。也就是说,半导体芯片的内部线路结构的线路密度较高且层数较多。在本实施例中,使用具有高密度与多层数联线能力的下部半导体芯片120进行连接,因此相较于使用一般的重配置线路结构进行连接,本实施例的多芯片封装件100可实现高频宽信号连接。

149.在本发明的多芯片封装件100中,重配置线路结构110与上部半导体芯片150可通过第二导电柱112与上部半导体芯片150的第二导体152彼此连接。因此可调整第二导电柱112的宽高比以在重配置线路结构110与上部半导体芯片150之间提供其他信号及大电流(例如接地)的传递路径。

150.在本发明的多芯片封装件100中,下部半导体芯片120的信号传递路径可以是经由第一导电柱121、上部半导体芯片150、第二导电柱112、重配置线路结构110再通过导电端子170与外部信号进行连接,因此,可以省去制作硅穿孔(tsv),进而降低多芯片封装件100的生产成本。

151.图3是绘示依照本发明的另一实施例的多芯片封装件的剖面示意图。

152.参照图3,依照本发明的另一实施例的多芯片封装件200除仅包括一个上部半导体

芯片150外,其余结构关系及配置与图2所示的多芯片封装件100的结构关系及配置相似。也就是说,本发明的多芯片封装件对于上部半导体芯片120与下部半导体芯片150的数量没有特别限制。视需要,本发明的多芯片封装件中可包括一或多个上部半导体芯片120及一或多个下部半导体芯片150。一或多个上部半导体芯片120及一或多个下部半导体芯片150彼此可执行相同功能或不同功能。除非有其他明显矛盾或明显不同的描述,否则多芯片封装件100的相同参考编号的组件的相关描述也适用于多芯片封装件200的相同参考编号的组件,在此不再赘述。

153.图4是绘示依照本发明的另一实施例的多芯片封装件的剖面示意图。

154.参照图4,依照本发明的另一实施例的多芯片封装件300为图像传感器封装件。在本发明的多芯片封装件300中,图像传感器芯片350与其他上部半导体芯片150并排地配置。图像传感器芯片350可为互补式金属氧化物半导体图像传感器芯片(cmos image sensing chip)。然而本发明不对图像传感器芯片350的种类加以限制,其可为其他适当种类的图像传感器芯片。图像传感器芯片350在传感面350a上可具有微透镜(micro lens)323,微透镜323下方为图像传感器芯片350的传感区322。微透镜323上方覆盖有盖体330。盖体330可例如为透明的玻璃基板。盖体330与微透镜323之间形成有例如密封胶(sealant)的密封结构325而使盖体330与微透镜323彼此间隔开,此外,密封结构325可用以定义盖体330与图像传感器芯片350之间的空间。图像传感器芯片350的与传感面350a相对的表面上配置有第一导体151与第二导体152,第一导体151连接到下部半导体芯片120的第一导电柱121以使图像传感器芯片350与下部半导体芯片120彼此电性/信号连接,第二导体152连接到第二导电柱112以使图像传感器芯片350与重配置线路结构110彼此电性/信号连接。在本发明的多芯片封装件300中,图像传感器芯片350与并排的上部半导体芯片150之间可通过下部半导体芯片120的内部线路结构彼此连接,而非通过焊线或重配置线路结构进行连接。因此,本发明的多芯片封装件300可实现高频宽信号连接。除非有其他明显矛盾或明显不同的描述,否则多芯片封装件100、200的相同参考编号的组件的相关描述也适用于多芯片封装件300的相同参考编号的组件,在此不再赘述。

155.图5是绘示依照本发明的另一实施例的多芯片封装件的剖面示意图。

156.参照图5,依照本发明的另一实施例的多芯片封装件400与图4所示的多芯片封装件300相同,不同之处在于在多芯片封装件400中以结合多个芯片的下部半导体元件420、图像传感器半导体元件440及上部半导体元件460分别置换多芯片封装件300中的下部半导体芯片120、图像传感器芯片350及上部半导体芯片150。下部半导体元件420、图像传感器半导体元件440及上部半导体元件460可包括具有相同或不同功能的多个芯片。举例来说,下部半导体元件420可包括上下堆叠的第一半导体芯片422与第二半导体芯片424,图像传感器半导体元件440可包括上下堆叠的第三半导体芯片442与第四半导体芯片444,上部半导体元件460可包括上下堆叠的第五半导体芯片462与第六半导体芯片464。第一半导体芯片422、第二半导体芯片424、第三半导体芯片442、第四半导体芯片444、第五半导体芯片462与第六半导体芯片464可视多芯片封装件400的功能而定可独立地为存储器芯片、逻辑芯片、数字芯片、模拟芯片、传感器芯片(sensor chip)、人工智能芯片(ai chip)、无线射频芯片(wireless and radio frequency chip)或电压调节器芯片等。举例来说,第三半导体芯片442可为图像传感器芯片。第一半导体芯片422与第二半导体芯片424可通过第一半导体芯

片422的第一连接导体422p与第二半导体芯片424的第二连接导体424p彼此连接。第三半导体芯片442与第四半导体芯片444可通过第三半导体芯片442的第三连接导体442p与第四半导体芯片444的第四连接导体444p彼此连接。第五半导体芯片462与第六半导体芯片464可通过第五半导体芯片462的第五连接导体462p与第六半导体芯片464的第六连接导体464p彼此连接。由于第一半导体芯片422与第二半导体芯片424之间、第三半导体芯片442与第四半导体芯片444之间以及第五半导体芯片462与第六半导体芯片464之间的电性路径短,因此可以实现信号的快速传递。同时,由于本发明的多芯片封装件400包括多个芯片,因此本发明的多芯片封装件400可执行更多功能但不显著增加多芯片封装件的体积。虽然图5中绘示了多芯片封装件400将多芯片封装件300中的下部半导体芯片120、图像传感器芯片350及上部半导体芯片150都置换成结合多个芯片的下部半导体元件420、图像传感器半导体元件440及上部半导体元件460,然而本发明不限于此,而是也可仅置换下部半导体芯片120、图像传感器芯片350及上部半导体芯片150中的部分。除非有其他明显矛盾或明显不同的描述,否则多芯片封装件100、200、300的相同参考编号的组件的相关描述也适用于多芯片封装件400的相同参考编号的组件,在此不再赘述。

157.图6a至图6j是依照本发明的一实施例的制造多芯片封装件的制造流程步骤的剖面示意图。图7a到图7f是绘示本发明的第一导体151与第一导电柱121的连接方法的各种实施例的示意图。图8是绘示依照本发明的一实施例的多芯片封装件的剖面示意图。除非有其他明显矛盾或明显不同的描述,否则上述实施例中的相同参考编号的组件的相关描述也适用于本实施例中的相同参考编号的组件,在此不再赘述。

158.参照图6a,将主动面上配置有第一导体151与第二导体152的上部半导体芯片150贴附至具有离型膜20的载体10上。

159.参照图6b及图6c,形成第二包封体142,所述第二包封体142包覆上部半导体芯片150。形成第二包封体142的方法包括以下步骤。通过合适的工艺(例如模塑工艺或沉积工艺)在载体10之上形成覆盖上部半导体芯片150的包封材料层,此后,执行表面研磨抛光工艺(wafer grinding)或者表面平坦化工艺(surface planarization)使得上部半导体芯片150的第一导体151与第二导体152的表面暴露出来。

160.参照图6d,在上部半导体芯片150的第二导体152上形成第二导电柱112。举例来说,形成第二导电柱112的工艺包括以下步骤。首先,在第二包封体142上形成图案化的光致抗蚀剂层。图案化的光致抗蚀剂层可利用光刻以及/或蚀刻工艺来形成。图案化的光致抗蚀剂层的开口暴露出第二导体152的表面。接着,可于图案化的光致抗蚀剂层的开口中形成多个导电柱状结构。导电柱状结构的形成方法可例如是印刷、电镀、无电电镀或其组合。之后,移除图案化的光致抗蚀剂层而形成第二导电柱112。

161.参照图6e,将下部半导体芯片120安装到第二包封体142上以将下部半导体芯片120的第一导电柱121与上部半导体芯片150的第一导体151彼此连接。接着,可在第二包封体142上施加第一底胶161以包封第一导电柱121。第一底胶161可填充下部半导体芯片120与第二包封体142之间的空间并包封第一导电柱121。如图6e所示,第一底胶161具有倾斜侧壁,且第一底胶161的上部宽度例如会小于第一底胶161的下部宽度。在一些实施例中,第一底胶161的宽度是渐变的,且第一底胶161的宽度从较靠近第二包封体142的一端朝着较靠近下部半导体芯片120的另一端逐渐缩减。

162.作为另一选择,第一底胶161在将下部半导体芯片120安装到第二包封体142上之前形成于下部半导体芯片120上。在这种情况下,第一导电柱121可在至少部分被第一底胶161包封的情况下与第一导体151连接。当第一导电柱121在至少部分被第一底胶161包封的情况下与第一导体151连接时,第一底胶161的宽度变化可与图6e所示的相反,也就是说第一底胶161的宽度从较靠近第二包封体142的一端朝着较靠近下部半导体芯片120的另一端逐渐增加(图未示)。图7a到图7h绘示第一导电柱121在至少部分被第一底胶161包封的情况下与第一导体151连接的连接方法的各种实施例的示意图。

163.参照图7a至图7c,可在第一底胶161上形成露出第一导电柱121的下表面的保护层165。保护层165的材料可为例如树脂、非导电性胶膜、介电材料等有机材料。第一导电柱121的形状可如图7a与图7c所示为柱状或如图7b所示为图钉状凸块。第一导体51的形状可如图7a与图7b所示为柱状或如图7c所示为图钉状凸块。在图7a至图7c的实施例中,当将下部半导体芯片120安装到第二包封体142上时,下部半导体芯片120的下表面为平坦表面。也就是说,下部半导体芯片120的保护层165的下表面与第一导电柱121的下表面共面。接着,可使第一导电柱121与第一导体151直接接触并通过加热而连接。由于下部半导体芯片120的第一导电柱121被第一底胶161与保护层165包封而只有表面露出进行连接,因此可避免受到外力冲击而受损,如此一来,可提高半导体工艺的良率。

164.参照图7d及图7e,可在第二包封体142上形成保护层165。保护层165的材料可为例如树脂、非导电性胶膜、介电材料等有机材料。保护层165可不形成在第一导体151的上表面上,因此,第一导体151的上表面会略低于保护层165的上表面。第一导电柱121的形状可如图7d所示为柱状或如图7e所示为图钉状凸块。在图7d与图7e的实施例中,第一导电柱121突出第一底胶161且第一导体151的上表面略低于保护层165的上表面。因此可便于下部半导体芯片120的第一导电柱121与第一导体151彼此对准而接触。第一导电柱121与第一导体151可在直接接触后通过加热而直接接合。

165.参照图7f,图7f所绘示的实施例与图7a所绘示的实施例类似,差别在于第一导电柱121与第一导体151中是通过接合金属125连接。接合金属125可例如为焊锡合金、铜、金、银、铟、钯、钛、锰、钴、或其合金等。可通过使第一导电柱121、第一导体151及/或接合金属125彼此接触并加热而接合第一导电柱121与第一导体151。第一导电柱121与第一导体151的连接也可以不使用焊料。也就是说,第一导电柱121与第一导体151的连接可不使用焊锡合金。接合金属125可为熔点低于200℃的低温接合金属。举例来说,低温接合金属可包括双晶铜、双晶银或其他纳米双晶材料、铟锡合金、锡铋合金、多孔金或其组合。相对于传统焊球或焊料所需回焊温度多高于或等于250℃,使用低温接合金属可在相对较低的加热温度下(例如,在低于200℃或低于150℃的温度下)使得连接结构达到稳定接合,且满足电连接要求的可靠度要求。

166.参照图7g,图7g所绘示的实施例与图7f所绘示的实施例类似,差别在于保护层165同时形成在第二包封体142与第一底胶161上。

167.参照图7h,图7h所绘示的实施例与图7f所绘示的实施例类似,差别在于第一导体上151没有形成接合金属125而是形成氧化保护层126。氧化保护层126的材料例如可为有机保焊膜(organic solderability preservative,osp)。氧化保护层126可在与第一导电柱121接合前使用清洁工艺移除或者通过助焊剂与第一导电柱121接合。

planarization)使得暴露出第二导电柱642及第三导电柱643的表面暴露出来。

181.参照图9h,在第二包封体142上形成包括第二重配置布线层646与第二介电层644的第二重配置线路结构640以与第二导电柱642及第三导电柱643电连接。形成第二重配置线路结构640的材料与方法与前述参照图1b形成重配置线路结构110的材料与方法类似,此处不再予以赘述。

182.参照图9h、图9i与图10,进行例如参照图1h与图1i所描述的离型工艺,以使图9i中所示的结构与载体10及离型膜20分离。接着,可将结构倒置以在最外部的第一介电层614形成开口o2以暴露出至少部分的第一重配置布线层616。参照图9i中的放大图,在最外部的第一介电层614中所形成的开口o2的外部宽度do可大于内部宽度di,而在内部的第一介电层614中所形成的开口614h的较靠近下部半导体芯片120的部分的宽度dn可大于较远离下部半导体芯片120的部分的宽度df,也就是说,开口o2的宽度变化方向与下方的第一介电层614中的开口的宽度变化方向相反。接着,使用拾取装备将导电端子170放至所形成的开口o2中。然后,通过回焊工艺(reflow process)来接合导电端子170与第一重配置布线层616而形成图10的多芯片封装件600。

183.图11绘示依照本发明的一实施例的堆叠式封装件(package on package,pop)的剖面示意图。图11中所示的堆叠式封装件中与前述相同或相似的组件被给定相同的参考编号,且具有相同参考编号的组件的说明与上述说明重复,因此对其不再予以赘述。

184.参照图11,依照本发明的一实施例的堆叠式封装件1000包括下部半导体封装件100a、上部半导体封装件100b以及连接下部半导体封装件100a与上部半导体封装件100b的中间导电端子180。下部半导体封装件100a与前述参照图8所述的多芯片封装件500相同,不同之处在于下部半导体封装件100a还包括第三导电柱113与顶部重配置线路结构140,第三导电柱113贯穿第一包封体141与第二包封体142且连接重配置线路结构110与顶部重配置线路结构140。第三导电柱113的材料包括例如铜(cu)、银(ag)、钯(pd)、铝(al)、镍(ni)、钛(ti)、金(au)、铂(pt)、钨(w)或其合金等导电材料。上部半导体封装件100b包括基底12、半导体芯片13及包封体15。半导体芯片13可以面向上的方式配置在基底12上并通过焊线14与基底12中的线路层(未示出)连接。包封体15配置于基底12上且包封半导体芯片13与焊线。中间导电端子180位于多芯片封装件100a的顶部表面s1上。中间导电端子180例如是焊球,但本发明不限于此。

185.视需要,可省略下部半导体封装件100a的顶部重配置线路结构140。此外,虽然堆叠式封装件1000中的下部半导体封装件100a绘示为具有与参照图8描述的多芯片封装件500类似的结构,但本发明不以此为限,堆叠式封装件1000中的下部半导体封装件100a也可具有与参照图2、图3及图10描述的多芯片封装件100、多芯片封装件200及多芯片封装件600类似的结构。

186.图12绘示依照本发明的一实施例的堆叠式封装件(package on package,pop)的剖面示意图。图12中所示的堆叠式封装件中与前述相同或相似的组件被给定相同的参考编号,且具有相同参考编号的组件的说明与上述说明重复,因此对其不再予以赘述。

187.参照图12,依照本发明的一实施例的堆叠式封装件2000包括多芯片封装件600、图像传感器封装件200b以及连接多芯片封装件600与图像传感器封装件200b的中间导电端子180。图像传感器封装件200b至少包括位于图像传感器封装件200b顶部的透光基板25、透光

基板25下方的图像传感器芯片23、透光基板25上的线路层27以及连接图像传感器芯片23与线路层27的连接导体29。图像传感器芯片23可为互补式金属氧化物半导体图像传感器芯片(cmos image sensing chip)。然而本发明不对图像传感器芯片23的种类加以限制,其可为其他适当种类的图像传感器芯片。图像传感器芯片23可经由连接导体29、线路层27以及中间导电端子180而电连接到多芯片封装件600。

188.除非有其他明显矛盾或明显不同的描述,否则上述实施例中的相同参考编号的组件的相关描述也适用于本实施例中的相同参考编号的组件,在此不再赘述。

189.图13a至图13l是依照本发明的一实施例的制造多芯片封装件的制造流程步骤的剖面示意图。

190.参照图13a,提供载体10。载体10上依序形成有离型膜20与晶种层212s。

191.载体10可为进行半导体芯片封装工艺时所使用的支撑基底。载体10的材料可包括玻璃、陶瓷、半导体等。虽然在附图中显示在载体10上进行单一多芯片封装件的封装,但载体10也可为大尺寸的芯片型态载体。也就是说,可在载体10上同时形成多个多芯片封装件。

192.离型膜20可由黏着剂(例如,紫外线(ultra-violet,uv)胶、光热转换(light-to-heat conversion,lthc)胶等、或者其他类型的黏着剂)形成。以紫外线胶所形成的离型膜20为例,可将紫外光照射于离型膜20上,使离型膜20丧失或降低其黏性,进而使得载体10以及离型膜20能够与后续步骤所形成的结构分离。以光热转换胶为例,可将适当能量的光照射于离型膜20上,使离型膜20在光的热能作用下分解而丧失或降低其黏性,进而使得载体10以及离型膜20能够与后续步骤所形成的结构分离。

193.晶种层212s可通过溅镀或沉积工艺形成于离型膜20上。晶种层212s的材料可例如为钛/铜等导电材料。

194.参照图13b,可在载体10上形成导电柱212。举例来说,形成导电柱212的工艺包括以下步骤。首先,在晶种层212s上形成图案化的光致抗蚀剂层。图案化的光致抗蚀剂层可利用光刻以及/或蚀刻工艺来形成。图案化的光致抗蚀剂层的开口暴露出晶种层212s的表面。接着,可于图案化的光致抗蚀剂层的开口中形成多个导电柱状结构。导电柱状结构的形成方法可例如是印刷、电镀、无电电镀或其组合。之后,移除图案化的光致抗蚀剂层以及部分晶种层而形成导电柱212。导电柱212的材料可利用电特性优异的金属或其合金形成,例如铜(cu)、银(ag)、钯(pd)、铝(al)、镍(ni)、钛(ti)、金(au)、铂(pt)、钨(w)或其合金。之后可通过蚀刻或光刻工艺移除离型膜20上的晶种层212s。

195.参照图13c,可将第一下部半导体芯片220与第二下部半导体芯片230通过例如芯片黏结薄膜(daf)等黏着剂层190以背面贴附至离型膜20上。第一下部半导体芯片220与第二下部半导体芯片230可独立地为形成有半导体集成电路的半导体芯片,例如存储器芯片、逻辑芯片、数字芯片、模拟芯片、传感器芯片(sensor chip)、人工智能芯片(ai chip)、无线射频芯片(wireless and radio frequency chip)或电压调节器芯片等。其中传感器芯片可为图像传感器芯片,至少包括电荷耦合组件(ccd)或互补金属氧化物半导体图像传感器(cmos image sensor)。

196.在本实施例中,第二下部半导体芯片230中可具有例如硅穿孔(through silicon via,tsv)或玻璃穿孔(through glass via,tgv)等导电穿孔结构232以在第二下部半导体芯片230中形成垂直连接通路。也就是说,第二下部半导体芯片230可通过导电穿孔结构232

自配置有第二下部连接导体230p的主动面及/或与所述主动面相对的表面与其它组件电连接。虽然本发明于附图中绘示仅第二下部半导体芯片230具有导电穿孔结构232,但本发明不以此为限。视需要,第一下部半导体芯片220也可具有导电穿孔结构。

197.第一下部半导体芯片220与第二下部半导体芯片230在其主动面上分别具有连接至半导体芯片内部电路的第一下部连接导体220p与第二下部连接导体230p。第一下部连接导体220p与第二下部连接导体230p的材料可包括例如铜(cu)、银(ag)、钯(pd)、铝(al)、镍(ni)、钛(ti)、金(au)、铂(pt)、钨(w)或其他电特性优异的金属或其合金。第一下部半导体芯片220与第二下部半导体芯片230在其主动面上可包括保护层165以包封第一下部连接导体220p与第二下部连接导体230p的至少部分。保护层165的材料可包括模塑化合物、模塑底部填料、树脂或环氧模制化合物(epoxy molding compound,emc)等有机绝缘材料。本发明的保护层165的材料与配置形式不以此为限。视需要,也可省略保护层165。

198.参照图13d与13e,形成第一包封体141,所述第一包封体141包覆第一下部半导体芯片220与第二下部半导体芯片230以及导电柱212。第一包封体141的材料可包括模塑化合物、模塑底部填料、树脂或环氧模制化合物(epoxy molding compound,emc)等。视需要,第一包封体141中可掺杂有无机填料。形成第一包封体141的方法包括以下步骤。通过合适的工艺(例如模塑工艺或沉积工艺)在载体10之上形成覆盖第一下部半导体芯片220与第二下部半导体芯片230以及导电柱212的包封材料层,此后,执行表面研磨抛光工艺(wafer grinding)或者表面平坦化工艺(surface planarization)使得导电柱212的表面以及第一下部连接导体220p与第二下部连接导体230p的表面暴露出来。也就是说,导电柱212的表面以及第一下部连接导体220p与第二下部连接导体230p的表面位于相同的水平高度上。换句话说,导电柱212、第一下部连接导体220p、第二下部连接导体230p以及第一包封体141的上表面共面。

199.参照图13e及图13f,通过薄膜工艺(thin film processes)在图13e所得结构上形成包括介电层274、第一导电图案271、第二导电图案272、贯穿介电层274以连接第一导电图案271与第二导电图案272的导电通孔图案273的中介连接结构270。

200.中介连接结构270可以通过增层法(build-up process)形成。举例而言,形成中介连接结构270的工艺包括以下步骤。首先在图13e所得结构上溅镀或沉积晶种层,其中晶种层的材料可例如为钛/铜等导电材料。接着,在晶种层上形成图案化光致抗蚀剂层以暴露出晶种层。通过电镀工艺于被图案化光致抗蚀剂层所暴露出的晶种层上形成导电材料,所述导电材料可包括铜(cu)、银(ag)、钯(pd)、铝(al)、镍(ni)、钛(ti)、金(au)、铂(pt)、钨(w)或其合金。接着,移除光致抗蚀剂层以及未被导电材料所覆盖的部分晶种层而形成第一导电图案271。

201.第一导电图案271可形成于导电柱212、第一下部连接导体220p、第二下部连接导体230p上并与导电柱212、第一下部半导体芯片220与第二下部半导体芯片230电连接。在一些实施例中,个别第一导电图案271可分别与个别导电柱212、第一下部连接导体220p以及第二下部连接导体230p相应地连接,其中与导电柱212相应连接的第一导电图案271的线宽可大于与第一下部连接导体220p或第二下部连接导体230p相应连接的第一导电图案271的线宽。

202.接着通过例如旋转涂布、化学气相沉积(chemical vapor deposition,cvd)、等离

子体增强型化学气相沉积(plasma-enhanced chemical vapor deposition,pecvd)等方法于第一导电图案271上形成介电层274。介电层274可以是包括感光性绝缘树脂的感光性绝缘层。接着,在介电层274中形成开口以暴露出其下之第一导电图案271,其中于介电层274中形成开口的方法可取决于介电层274的材料而采用不同的工艺。当介电层274为包括感光性绝缘树脂的感光性绝缘层时,介电层274可通过光刻工艺进行图案化以形成开口。当介电层274为非感光性绝缘层时,介电层274可通过光刻/蚀刻工艺、激光钻孔工艺或机械钻孔工艺进行图案化以形成开口。接着,使用例如镀覆工艺在介电层274的开口中填充导电材料以形成导电通孔图案273与第二导电图案272。导电通孔图案273在剖视图中的宽度可变化。举例而言,导电通孔图案273较靠近第二导电图案272处的宽度可大于导电通孔图案273较靠近第一导电图案271处的宽度。

203.参照图13g,将第一上部半导体芯片240与第二上部半导体芯片250并排地安装至中介连接结构270上以使第一上部半导体芯片240的主动面上的第一上部连接导体240p与第二导电图案272电连接,并且使第二上部半导体芯片250的主动面上的第二上部连接导体250p与第二导电图案272电连接。在一些实施例中,个别第二导电图案272可分别与个别第一上部连接导体240p以及第二上部连接导体250p相应地连接。

204.如图13g所绘示,第一上部半导体芯片240可在垂直方向上同时与导电柱212以及第一下部半导体芯片220交叠,而第二上部半导体芯片250可在垂直方向上同时与第一下部半导体芯片220以及第二下部半导体芯片230交叠。此外,第一上部半导体芯片240的第一上部连接导体240p以及第二上部半导体芯片250的第二上部连接导体250p可在垂直方向上与相应的第一下部半导体芯片220的第一下部连接导体220p与第二下部半导体芯片230的第二下部连接导体230p彼此交叠。因此,第一上部半导体芯片240可通过第一下部半导体芯片220与第二上部半导体芯片250进行信号传输。

205.第一上部半导体芯片240与第二上部半导体芯片250可独立地为形成有半导体集成电路的半导体芯片,例如存储器芯片、逻辑芯片、数字芯片、模拟芯片、传感器芯片(sensor chip)、人工智能芯片(ai chip)、无线射频芯片(wireless and radio frequency chip)或电压调节器芯片等。其中传感器芯片可为图像传感器芯片,至少包括电荷耦合组件(ccd)或互补金属氧化物半导体图像传感器(cmos image sensor)。第一下部半导体芯片220、第二下部半导体芯片230、第一上部半导体芯片240及第二上部半导体芯片250可独立地为执行相同或不同功能的半导体芯片,本发明没有特别限制。

206.第一上部半导体芯片240的主动面上的第一上部连接导体240p以及第二上部半导体芯片250的主动面上的第二上部连接导体250p的材料可包括铜(cu)、银(ag)、钯(pd)、铝(al)、镍(ni)、钛(ti)、金(au)、铂(pt)、钨(w)或其合金等导电材料。

207.虽然图中未绘示,但在一些实施例中,第一上部半导体芯片240与第二上部半导体芯片250中可分别具有例如硅穿孔(through silicon via,tsv)等导电穿孔结构以分别在第一上部半导体芯片240与第二上部半导体芯片250中形成垂直连接通路。所述导电穿孔结构可自第一上部半导体芯片240的主动面延伸至第一上部半导体芯片240的与主动面相对的背面。所述导电穿孔结构可与第一上部半导体芯片240的主动面上的第一上部连接导体240p电性及/或实体连接。所述导电穿孔结构可自第一上部半导体芯片240的背面暴露出来以与其它组件电性及/或实体连接。举例而言,例如半导体芯片等其他电子组件可堆叠在第

一上部半导体芯片240上并与自第一上部半导体芯片240的背面暴露出的导电穿孔结构电性及/或实体连接,且所述电子组件可经由所述导电穿孔结构电连接至第一上部半导体芯片240下方的中介连接结构270。类似地,所述导电穿孔结构可自第二上部半导体芯片250的主动面延伸至第二上部半导体芯片250的与主动面相对的背面。所述导电穿孔结构可与第二上部半导体芯片250的主动面上的第二上部连接导体250p电性及/或实体连接。所述导电穿孔结构可自第二上部半导体芯片250的背面暴露出来以与其它组件电性及/或实体连接。举例而言,例如半导体芯片等其他电子组件可堆叠在第二上部半导体芯片250上并与自第二上部半导体芯片250的背面暴露出的导电穿孔结构电性及/或实体连接,且所述电子组件可经由所述导电穿孔结构电连接至第二上部半导体芯片250下方的中介连接结构270。

208.在一些实施例中,在安装第一上部半导体芯片240与第二上部半导体芯片250之前,可在第二导电图案272上形成例如凸块等接合结构280。因此,第一上部半导体芯片240与第二上部半导体芯片250可经由接合结构280与中介连接结构270的第二导电图案272电连接,并经由中介连接结构270与导电柱、第一下部半导体芯片220及第二下部半导体芯片230电连接。

209.接合结构280的材料可例如包括焊锡合金、铜、金、银、铟、钯、钛、锰、钴、或其合金等接合金属。在一些实施例中,接合结构280的材料可为熔点低于200℃的低温接合金属。举例来说,低温接合金属可包括双晶铜、双晶银或其他纳米双晶材料、铟锡合金、锡铋合金、多孔金或其组合。相对于传统焊球或焊料所需回焊温度多高于或等于250℃,使用低温接合金属可在相对较低的加热温度下(例如,在低于200℃或低于150℃的温度下)使得连接结构达到稳定接合,且满足电连接要求的可靠度要求。

210.参照图13h,通过合适的工艺(例如模塑工艺或沉积工艺)在载体10之上形成覆盖中介连接结构270、第一上部半导体芯片240及第二上部半导体芯片250的第二包封体142。第二包封体142的材料可包括模塑化合物、模塑底部填料、树脂或环氧模制化合物(epoxy molding compound,emc)等。视需要,第二包封体142中可掺杂有无机填料。第一包封体141的材料与第二包封体142的材料可彼此相同。或者,第一包封体141的材料与第二包封体142的材料可彼此不同。

211.参照图13h与图13i,进行一离型工艺,以使图13i中所示的结构与载体10及离型膜20分离。当离型膜20是由紫外线胶所形成时,前述的离型工艺可将紫外光照射于离型膜20上,以使离型膜20丧失或降低其黏性,进而使得载体10以及离型膜20能够与图13h中所示的结构分离。当离型膜20是由光热转换胶所形成时,前述的离型工艺可将适当能量的光照射于离型膜20上,以使离型膜20在光的热能作用下分解而丧失或降低其黏性,进而使得载体10以及离型膜20能够与图13i中所示的结构分离。

212.参照图13i与图13j,在离型膜20被移除的表面上执行表面研磨抛光工艺(wafer grinding)或者表面平坦化工艺(surface planarization)使得第二下部半导体芯片230的导电穿孔结构232的表面与导电柱212的表面暴露出来。

213.参照图13k,通过薄膜工艺(thin film processes)在图13j所得的结构上形成包括重配置布线层116与介电层114的重配置线路结构(redistribution circuit structure)110。

214.具体而言,可通过例如旋转涂布、化学气相沉积(chemical vapor deposition,

cvd)、等离子体增强型化学气相沉积(plasma-enhanced chemical vapor deposition,pecvd)等方法于图13j所得的结构上形成介电层114。介电层114的材料可包括聚酰亚胺、环氧树脂、丙烯酸树脂、酚醛树脂、双马来酰亚胺-三氮杂苯树脂(bismaleimide-trazine resin,bt resin)或任何其他合适的聚合物系介电材料以及氧化硅层、氮化硅层、氮氧化硅层或其他合适的硅介电材料。介电层114可以是包括感光性绝缘树脂的感光性绝缘层。

215.接着,在介电层114中形成开口以暴露出其下的导电穿孔结构232及导电柱212。在介电层114中形成开口的方法可取决于介电层114的材料而采用不同的工艺。当介电层114为包括感光性绝缘树脂的感光性绝缘层时,介电层114可通过光刻工艺进行图案化以形成开口。当介电层114为非感光性绝缘层时,介电层114可通过光刻/蚀刻工艺、激光钻孔工艺或机械钻孔工艺进行图案化以形成开口。介电层114的开口在剖视图中的宽度可变化。举例而言,所述开口的上部宽度可大于下部宽度。因此,重配置布线层116的填充于所述开口的部分的上部宽度也可大于下部宽度。

216.接着在介电层114的表面以及介电层114的开口的表面上溅镀或沉积晶种层,其中晶种层的材料可例如为钛/铜等导电材料。接着,于晶种层上形成图案化光致抗蚀剂层以暴露出晶种层。通过电镀工艺于被图案化光致抗蚀剂层所暴露出的晶种层上形成导电材料,所述导电材料可包括铜(cu)、银(ag)、钯(pd)、铝(al)、镍(ni)、钛(ti)、金(au)、铂(pt)、钨(w)或其合金。接着,移除光致抗蚀剂层以及未被导电材料所覆盖的部分晶种层而形成重配置布线层116。

217.参照图13l,可在重配置线路结构110的最外重配置布线层116上形成多个导电端子170而完成本发明的多芯片封装件700。导电端子170例如是焊球,但本发明不限于此。可在大尺寸的芯片上同时形成多个本发明的多芯片封装件700,接着,再通过切割等工艺以分离个别多芯片封装件700。因此本发明的多芯片封装件700中的第一包封体141的侧壁、第二包封体142的侧壁可与重配置线路结构110的侧壁对准。

218.在本发明的多芯片封装件700中,第一上部半导体芯片240与第二上部半导体芯片250与第一下部半导体芯片220与第二下部半导体芯片230之间没有设置重配置线路结构而是通过中介连接结构270彼此连接。相较于重配置线路结构,本发明的中介连接结构270可具有较小的线宽、线距及通孔宽度,因此可缩短第一上部半导体芯片240与第二上部半导体芯片250与第一下部半导体芯片220与第二下部半导体芯片230之间的电源及/或信号的传递路径,而提高电源及/或信号的传递速度与品质。

219.同时,本发明的多芯片封装件700通过在第二下部半导体芯片230中包括可提供高速信号传输的导电穿孔结构232以及与第二下部半导体芯片230并排配置且可提供其他信号或大电流(例如接地)传输的导电柱212,而可同时实现高速信号传输与大电流信号传输。

220.作为另一选择,可例如通过与参照图13a至图13l说明的制造方法相同或类似的制造方法在图13l所示的多芯片封装件700上堆叠更多层半导体芯片。举例而言,可在第一上部半导体芯片240及/或第二上部半导体芯片250上堆叠更多层半导体芯片。详言之,第一上部半导体芯片240及/或第二上部半导体芯片250中可具有例如硅穿孔(through silicon via,tsv)等导电穿孔结构以电性及/或实体连接至堆叠于其上的半导体芯片。

221.图14a至图14o是依照本发明的一实施例的制造多芯片封装件800的制造流程步骤的剖面示意图。图14a至图14o中使用与图13a至图13k相同的符号标示相同或相似的组件,

因此对于具有相同符号的组件的说明可参照上文参照图13a至图13k所提供的说明,重复的内容将不再予以赘述。以下说明将主要针对图14o所示的多芯片封装件800与图13k所示的多芯片封装件700的工艺与结构差异进行说明。

222.图14a与图14b的工艺与参照关于图13a、图13b所说明的工艺相同或相似,因此不再赘述。

223.参照图14c,可将第一下部半导体芯片220与第二下部半导体芯片230通过黏着剂层190以倒装芯片(flip-chip)的方式贴附至离型膜20上。

224.参照图14d与14e,通过合适的工艺(例如模塑工艺或沉积工艺)在载体10之上形成覆盖第一下部半导体芯片220与第二下部半导体芯片230以及导电柱212的包封材料层,此后,执行表面研磨抛光工艺(wafer grinding)或者表面平坦化工艺(surface planarization)使得导电柱212的表面以及第二下部半导体芯片230的导电穿孔结构232的表面暴露出来。也就是说,导电柱212的表面以及第二下部半导体芯片230的背面位于相同的水平高度上。换句话说,导电柱212的上表面、第二下部半导体芯片230的背面以及第一包封体141的上表面共面。同时,第一下部半导体芯片220的背面被第一包封体141完全覆盖,但本发明不以此为限。举例来说,第一下部半导体芯片220的背面也可自第一包封体141暴露出来。

225.参照图14e与图14f,通过薄膜工艺(thin film processes)在图14e所得的结构上形成包括重配置布线层116与介电层114的重配置线路结构(redistribution circuit structure)110。

226.具体而言,可通过例如旋转涂布、化学气相沉积(chemical vapor deposition,cvd)、等离子体增强型化学气相沉积(plasma-enhanced chemical vapor deposition,pecvd)等方法于图14e所得的结构上形成介电层114。接着,在介电层114中形成开口以暴露出其下之导电穿孔结构232及导电柱212。接着在介电层114的表面以及介电层114的开口形成重配置布线层116。介电层114的开口在剖视图中的宽度可变化。举例而言,所述开口的上部宽度可大于下部宽度。因此,重配置布线层116的填充于所述开口的部分的上部宽度也可大于下部宽度。

227.参照图14f~图14i,在图14f所得结构上形成另一离型膜20’与另一载体10’,接着将所得结构上下倒置并通过离型工艺移除离型膜20与载体10而得到图14i所示之结构。

228.参照图14i与图14j,在离型膜20被移除的表面上执行表面研磨抛光工艺(wafer grinding)或者表面平坦化工艺(surface planarization)使得第一下部半导体芯片220的第一下部连接导体220p与第二下部半导体芯片230第二下部连接导体230p的表面与导电柱212的表面暴露出来。

229.参照图14j及图14k,在图14j所得结构上形成包括介电层274、第一导电图案271、第二导电图案272、贯穿介电层274以连接第一导电图案271与第二导电图案272的导电通孔图案273的中介连接结构270。导电通孔图案273在剖视图中的宽度可变化。举例而言,导电通孔图案273较靠近第二导电图案272处的宽度可大于导电通孔图案273较靠近第一导电图案271处的宽度。

230.参照图14l,将第一上部半导体芯片240与第二上部半导体芯片250并排地安装至中介连接结构270上以使第一上部半导体芯片240的主动面上的第一上部连接导体240p与

第二导电图案272电连接,并且使第二上部半导体芯片250的主动面上的第二上部连接导体250p与第二导电图案272电连接。

231.如图14l所绘示,第一上部半导体芯片240可在垂直方向上同时与导电柱212以及第一下部半导体芯片220交叠,而第二上部半导体芯片250可在垂直方向上同时与第一下部半导体芯片220以及第二下部半导体芯片230交叠。此外,第一上部半导体芯片240的个别第一上部连接导体240p以及第二上部半导体芯片250的个别第二上部连接导体250p可在垂直方向上与相应的第一下部半导体芯片220的个别第一下部连接导体220p以及第二下部半导体芯片230的个别第二下部连接导体230p彼此交叠。

232.在一些实施例中,在安装第一上部半导体芯片240与第二上部半导体芯片250之前,可在第二导电图案272上形成例如凸块等接合结构280。因此,第一上部半导体芯片240与第二上部半导体芯片250可经由接合结构280与中介连接结构270的第二导电图案272电连接,并经由中介连接结构270与导电柱、第一下部半导体芯片220及第二下部半导体芯片230电连接

233.再继续参照图14l,可在中介连接结构270的介电层274上施加底胶160以填充第一上部半导体芯片240以及第二上部半导体芯片250与中介连接结构270的介电层274之间的空间并包封第一上部连接导体240p、第二上部连接导体250p、接合结构280以及第二导电图案272。如图14l所示,底胶160具有倾斜侧壁,且底胶160的上部宽度例如会小于底胶160的下部宽度。在一些实施例中,底胶160的宽度是渐变的,且底胶160的宽度从较靠近中介连接结构270的介电层274的一端朝着较靠近第一上部半导体芯片240以及第二上部半导体芯片250的另一端逐渐缩减。

234.参照图14m,通过合适的工艺(例如模塑工艺或沉积工艺)在载体10之上形成覆盖中介连接结构270、第一上部半导体芯片240及第二上部半导体芯片250的第二包封体142。

235.参照图14m与图14n,进行一离型工艺,以使图14m中所示的结构与载体10’及离型膜20’分离并使得重配置线路结构110的最外重配置布线层116暴露出来。

236.参照图14o,可在重配置线路结构110的最外重配置布线层116上形成多个导电端子170而完成本发明的多芯片封装件800。可在大尺寸的芯片上同时形成多个本发明的多芯片封装件800,接着,再通过切割等工艺以分离个别多芯片封装件800。因此本发明的多芯片封装件800中的第一包封体141的侧壁、第二包封体142的侧壁可与重配置线路结构110的侧壁对准。

237.除了底胶160外,图14o所示的多芯片封装件800与图13l所示的芯片封装件700可具有类似的结构,因此图14o所示的多芯片封装件800也可具有上文所述图13l所示的芯片封装件700的优点。此外,由于包括底胶160,因此图14o所示的多芯片封装件800还可具有提高的可靠性。

238.图15a至图15n是依照本发明的一实施例的制造多芯片封装件900的制造流程步骤的剖面示意图。图15a至图15n中使用与图13a至图13k以及图14a至14o相同的符号标示相同或相似的组件,因此对于具有相同符号的组件的说明可参照上文参照图13a至图13k以及图14a至14o所提供的说明,重复的内容将不再予以赘述。以下说明将主要针对图15n所示的多芯片封装件900与图13k所示的多芯片封装件700以及图14o所示的多芯片封装件800的工艺与结构差异进行说明。

239.参照图15a,提供载体10。载体10上依序形成有离型膜20与导电材料层272s。导电材料层272s可通过于离型膜20上溅镀或沉积例如为钛/铜等导电材料而形成晶种层,接着,通过电镀工艺于晶种层上形成导电材料层272s。导电材料层272s可包括铜(cu)、银(ag)、钯(pd)、铝(al)、镍(ni)、钛(ti)、金(au)、铂(pt)、钨(w)或其合金等导电材料。

240.参照图15b,通过例如旋转涂布、化学气相沉积(chemical vapor deposition,cvd)、等离子体增强型化学气相沉积(plasma-enhanced chemical vapor deposition,pecvd)等方法于导电材料层272s上形成介电层274。接着,在介电层274中形成开口以暴露出其下之导电材料层272s。接着,使用例如镀覆工艺在介电层274的开口中填充导电材料以形成导电通孔图案273与第一导电图案271。导电通孔图案273在剖视图中的宽度可变化。举例而言,导电通孔图案273较靠近第一导电图案271处的宽度可大于导电通孔图案273较靠近导电材料层272s处的宽度。接着,在第一导电图案271上形成与第一导电图案271电连接的导电柱212。

241.参照图15c,可将第一下部半导体芯片220与第二下部半导体芯片230通过例如凸块等接合结构280连接到第一导电图案271上。第一下部半导体芯片220与第二下部半导体芯片230可因此与导电柱212电连接。

242.参照图15d与图15e,通过合适的工艺(例如模塑工艺或沉积工艺)在载体10之上形成覆盖第一下部半导体芯片220与第二下部半导体芯片230以及导电柱212的包封材料层,此后,执行表面研磨抛光工艺(wafer grinding)或者表面平坦化工艺(surface planarization)使得导电柱212的表面以及第二下部半导体芯片230的导电穿孔结构232的表面暴露出来。也就是说,导电柱212的表面以及第二下部半导体芯片230的背面位于相同的水平高度上。换句话说,导电柱212的上表面、第二下部半导体芯片230的背面以及第一包封体141的上表面共面。同时,第一下部半导体芯片220的背面被第一包封体141完全覆盖,但本发明不以此为限。举例来说,第一下部半导体芯片220的背面也可自第一包封体141暴露出来。

243.参照图15e及图15f,通过薄膜工艺(thin film processes)在图15e所得的结构上形成包括重配置布线层116与介电层114的重配置线路结构(redistribution circuit structure)110。

244.具体而言,可通过例如旋转涂布、化学气相沉积(chemical vapor deposition,cvd)、等离子体增强型化学气相沉积(plasma-enhanced chemical vapor deposition,pecvd)等方法于15e所得的结构上形成介电层114。接着,在介电层114中形成开口以暴露出其下的导电穿孔结构232及导电柱212。介电层114的开口在剖视图中的宽度可变化。举例而言,所述开口的上部宽度可大于下部宽度。因此,重配置布线层116的填充于所述开口的部分的上部宽度也可大于下部宽度。接着在介电层114的表面以及介电层114的开口的表面上形成重配置布线层116。

245.参照图15f-图15i,在图15f所得结构上形成另一离型膜20’与另一载体10’,接着将所得结构上下倒置并通过离型工艺移除离型膜20与载体10而得到图15i所示之结构。

246.参照图15i及图15j,对导电材料层272s执行图案化工艺而形成包括介电层274、第一导电图案271、第二导电图案272、贯穿介电层274以连接第一导电图案271与第二导电图案272的导电通孔图案273的中介连接结构270。

247.图15k至图15n的工艺与参照关于图14l至图14o所说明的工艺相同或相似,因此不再赘述。

248.参见图15n,图15n所示的多芯片封装件900与图14o所示的多芯片封装件800具有类似的结构,其主要差异在于图15n所示的多芯片封装件900的第一下部半导体芯片220与第二下部半导体芯片230的主动面上没有保护层165,且第一下部半导体芯片220的第一下部连接导体220p与第二下部半导体芯片230的第二下部连接导体230p分别经由接合结构280与相应的第一导电图案272连接。此外,图15n所示的多芯片封装件900中的导电通孔图案273较靠近第二导电图案272处的宽度小于导电通孔图案273较靠近第一导电图案271处的宽度,而图14o所示的多芯片封装件800中的导电通孔图案273较靠近第二导电图案272处的宽度大于导电通孔图案273较靠近第一导电图案271处的宽度(参见图14k)。

249.图16绘示依照本发明的一实施例的堆叠式封装件(package on package,pop)的剖面示意图。图16中所示的堆叠式封装件中与前述相同或相似的组件被给定相同的参考编号,且具有相同参考编号的组件的说明与上述说明重复,因此对其不再予以赘述。

250.参照图16,依照本发明的一实施例的堆叠式封装件包括上文所述的多芯片封装件700、800、900中的任一者以及另一半导体芯片16。半导体芯片16可位于第一上部半导体芯片240以及第二上部半导体芯片250上方且可通过例如接脚(pin)等连接结构连接至中介连接结构270,使得半导体芯片16可通过接脚、中介连接结构270、导电柱212而电连接至重配置线路结构110。

251.图17绘示依照本发明的一实施例的堆叠式封装件(package on package,pop)的剖面示意图。图17所示的堆叠式封装件与图16所示的堆叠式封装件相同或类似,其主要差异在于图17所示的半导体芯片17不同于图16所示的半导体芯片16。半导体芯片17可具有较小的尺寸,且可与第一上部半导体芯片240以及第二上部半导体芯片250并排地安装在中介连接结构270上。

252.图18绘示依照本发明的一实施例的堆叠式封装件(package on package,pop)的剖面示意图。图18中所示的堆叠式封装件中与前述相同或相似的组件被给定相同的参考编号,且具有相同参考编号的组件的说明与上述说明重复,因此对其不再予以赘述。

253.参照图18,依照本发明的一实施例的堆叠式封装件包括上文所述的多芯片封装件700、800、900中的任一者、上部半导体封装件100b以及连接多芯片封装件与上部半导体封装件100b的中间导电端子180。上部半导体封装件100b包括基底12、半导体芯片13及包封体15。半导体芯片13可以面向上的方式配置在基底12上并通过焊线14与基底12中的线路层(未示出)连接。包封体15配置于基底12上且包封半导体芯片13与焊线14。中间导电端子180位于中介连接结构270上且与中介连接结构270电连接。中间导电端子180例如是焊球,但本发明不限于此。

254.除非有其他明显矛盾或明显不同的描述,否则上述实施例中的相同参考编号的组件的相关描述也适用于本实施例中的相同参考编号的组件,在此不再赘述。

255.综上所述,本发明的多芯片封装件能够缩短多芯片封装件中的电源及/或信号的传递路径而提升多芯片封装件的整体效能。

256.最后应说明的是:以上各实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述各实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依

然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1