三维存储器的漏电分析方法及三维存储器与流程

[0001]

本公开实施例涉及半导体技术领域,特别涉及一种三维存储器的漏电分析方法及三维存储器。

背景技术:

[0002]

三维存储器的存储结构包括层叠间隔设置的导电栅极层,相邻的栅极层由绝缘层隔开。存储结构包括核心(core)区和台阶(stair steps,ss)区。台阶区围绕核心区设置,用于向核心区传输控制信息,以实现信息在核心区的读写。在台阶区一般设置有接触孔,在接触孔中填充导电材料形成导电插塞(contact)。导电插塞的一端与栅极层电连接,另一端与后段互连线电连接,从而形成控制信号传输的通路。

[0003]

随着各类电子设备对数据存储密度的需求不断提高,三维存储器的堆叠层数越来越高。在形成接触孔时,为了保证相对靠近衬底的下层台阶中栅极层能够被顺利引出,相对远离衬底的上层台阶中的栅极层容易被过刻蚀(over etch),出现刻蚀穿通(punch through),导致相邻的两层栅极层之间通过导电插塞短接,降低产品良率。

[0004]

现有技术中,对于发生刻蚀穿通的接触孔的分析准确性较低,难以保证制作的三维存储器质量。

技术实现要素:

[0005]

有鉴于此,本公开实施例提供一种三维存储器漏电分析方法及三维存储器。

[0006]

根据本公开实施例的第一方面,提供一种三维存储器的漏电分析方法,所述三维存储器包括栅叠层结构,所述栅叠层结构包括依次交替层叠设置的绝缘层和导电的栅极层,所述方法包括:

[0007]

在所述栅叠层结构的第一台阶区,形成贯穿台阶上表面所述栅极层的绝缘的阻挡结构;其中,所述台阶上表面的所述栅极层包括第一部分和第二部分,所述阻挡结构电隔离所述第一部分和所述第二部分;

[0008]

形成与所述第一部分电连接的第一导电插塞;

[0009]

形成与所述第二部分电连接的第二导电插塞;其中,所述第二导电插塞用于向所述第二部分传输电信号;

[0010]

对所述第一导电插塞进行电性检测,获取检测结果;基于所述检测结果中所述第一导电插塞呈现的图像,对所述三维存储器进行漏电分析。

[0011]

在一些实施例中,所述基于所述检测结果中所述第一导电插塞呈现的图像,对所述三维存储器进行漏电分析,包括:

[0012]

所述检测结果中所述第一导电插塞表面呈现亮色,对应于所述第一导电插塞漏电;

[0013]

所述检测结果中所述第一导电插塞表面呈现暗色,对应于所述第一导电插塞不漏电。

[0014]

在一些实施例中,所述对所述第一导电插塞进行电性检测,包括:

[0015]

对所述第一导电插塞进行电子束检测。

[0016]

在一些实施例中,所述栅叠层结构位于衬底上,所述第一台阶区中至少一个所述台阶包括两层所述栅极层;

[0017]

所述在所述栅叠层结构的第一台阶区,形成贯穿台阶上表面所述栅极层的绝缘的阻挡结构,包括:

[0018]

在所述第一台阶区包括两层所述栅极层的所述台阶中,形成贯穿相对远离所述衬底的一个所述栅极层的所述阻挡结构,所述相对远离所述衬底的一个所述栅极层被所述阻挡结构划分为电隔离的所述第一部分和所述第二部分;

[0019]

其中,所述阻挡结构与相对靠近所述衬底的另一个所述栅极层接触且未贯穿所述另一个所述栅极层;或者,所述阻挡结构与相对靠近所述衬底的另一个所述栅极层之间具有所述绝缘层。

[0020]

在一些实施例中,所述在所述栅叠层结构的第一台阶区,形成贯穿台阶上表面所述栅极层的绝缘的阻挡结构,包括:

[0021]

形成堆叠结构;其中,所述堆叠结构包括依次交替层叠设置的所述绝缘层和牺牲层;

[0022]

在所述堆叠结构对应于所述第一台阶区的第三台阶区,形成贯穿台阶上表面所述牺牲层的第一沟槽;填充所述第一沟槽,形成所述阻挡结构;

[0023]

在形成所述阻挡结构之后,所述方法还包括:去除所述牺牲层,以在相邻所述绝缘层之间形成间隙,填充所述间隙,形成所述栅极层,所述栅极层和所述绝缘层形成所述栅叠层结构。

[0024]

在一些实施例中,所述去除所述牺牲层,以在相邻所述绝缘层之间形成间隙,填充所述间隙,形成所述栅极层,包括:

[0025]

形成贯穿所述堆叠结构的第二沟槽;其中,所述第二沟槽与所述阻挡结构交叉设置;

[0026]

通过所述第二沟槽,去除所述牺牲层,以在相邻所述绝缘层之间形成所述间隙;

[0027]

通过所述第二沟槽,填充所述间隙,形成所述栅极层;

[0028]

在形成所述栅极层之后,所述方法还包括:

[0029]

形成覆盖所述第二沟槽侧壁的绝缘的阻挡层;填充所述第二沟槽,形成覆盖所述阻挡层的导电源极。

[0030]

根据本公开实施例的第二方面,提供一种三维存储器,包括:

[0031]

栅叠层结构,包括:依次交替层叠设置的绝缘层和导电的栅极层;其中,在所述栅叠层结构端部的第一台阶区中,台阶上表面的所述栅极层包括第一部分和第二部分;

[0032]

绝缘的阻挡结构,位于所述第一台阶区,贯穿所述台阶上表面的所述栅极层,且电隔离所述第一部分和所述第二部分;

[0033]

第一导电插塞,垂直于所述栅叠层结构,且与所述第一部分电连接;其中,基于对所述第一导电插塞进行电性分析所获取检测结果中所述第一导电插塞呈现的图像,用于对所述三维存储器进行漏电分析;

[0034]

第二导电插塞,垂直于所述栅叠层结构,且与所述第二部分电连接,用于向所述第

二部分传输电信号。

[0035]

在一些实施例中,所述三维存储器还包括衬底;所述第一台阶区中,至少一个所述台阶包括两层所述栅极层;其中,

[0036]

所述台阶中相对远离所述衬底的一个所述栅极层,包括:被所述阻挡结构划分为电隔离的所述第一部分和所述第二部分;

[0037]

所述台阶中相对靠近所述衬底的另一个所述栅极层,与所述阻挡结构接触,且所述阻挡结构未贯穿所述另一个所述栅极层;或者,所述阻挡结构与所述另一个所述栅极层之间具有所述绝缘层。

[0038]

在一些实施例中,所述三维存储器还包括:

[0039]

导电源极,贯穿所述栅叠层结构,且与所述阻挡结构交叉设置;

[0040]

绝缘的阻挡层,位于所述导电源极的侧壁和所述栅极层之间。

[0041]

在一些实施例中,所述三维存储器包括:

[0042]

虚拟存储块;其中,所述阻挡结构、所述第一导电插塞和所述第二导电插塞形成于所述虚拟存储块的栅叠层结构上。

[0043]

本公开实施例中,当第一导电插塞不漏电时,由于阻挡结构电隔离栅极层的第一部分与第二部分,因此,不漏电的第一导电插塞和第二导电插塞之间断路。当第一导电插塞漏电时,漏电的第一导电插塞穿过台阶上表面的一个栅极层,并与该一个栅极层下方的至少另一个栅极层电连接,因此,漏电的第一导电插塞和第二导电插塞之间短路。

[0044]

需要强调的是,第一导电插塞与第二导电插塞之间断路时第一导电插塞呈现的图像,不同于第一导电插塞与第二导电插塞之间短路时第一导电插塞呈现的图像。因此,根据本公开实施例提供的漏电分析方发,能够直观、高效地进行漏电分析,确定漏电的第一导电插塞,可视性分析效果好。

[0045]

此外,本公开提供的方法在检测过程中不会对三维存储器结构进行物理破坏,无需造成三维存储器产品浪费,可在制造车间(fab,或称洁净室)内直接监测漏电情况,进行产线上监测(inline monitor),相较于通过透射电子显微镜(tem)进行漏电分析,降低了分析成本,缩短了分析时间,进而可加快工艺研发速度。

附图说明

[0046]

图1a是根据一示例性实施例示出的一种包括漏电的导电插塞的三维存储器局部示意图;

[0047]

图1b是一种对图1a示出的三维存储器进行电压对比检测获得的图像;

[0048]

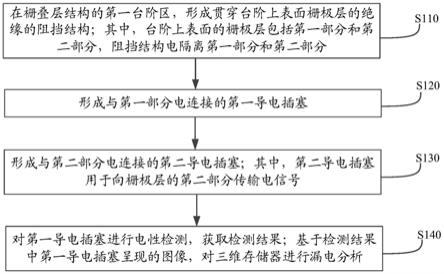

图2是根据一示例性实施例示出的一种三维存储器的漏电分析方法的流程图;

[0049]

图3是根据一示例性实施例示出的一种三维存储器漏电分析的检测结果示意图;

[0050]

图4是根据一示例性实施例示出的一种存储平面的示意图;

[0051]

图5a、图5b、图5c和图5d是根据一示例性实施例示出的一种三维存储器漏电分析方法的示意图;

[0052]

图6a、图6b、图6c和图6d是根据一示例性实施例示出的另一种三维存储器漏电分析方法的示意图;

[0053]

图7a和图7b是根据一示例性实施例示出的一种三维存储器的局部示意图;

[0054]

图8是根据一示例性实施例示出的另一种三维存储器的示意图。

具体实施方式

[0055]

下面将结合附图和实施例对本公开的技术方案进一步详细阐述。虽然附图中显示了本公开的示例性实施方法,然而应当理解,可以以各种形式实现本公开而不应被这里阐述的实施方式所限制。相反,提供这些实施方式是为了能够更透彻的理解本公开,并且能够将本公开的范围完整的传达给本领域的技术人员。

[0056]

在下列段落中参照附图以举例方式更具体的描述本发明。根据下面说明和权利要求书,本公开的优点和特征将更清楚。需说明的是,附图均采用非常简化的形式且均使用非精准的比例,仅用以方便、明晰地辅助说明本公开实施例的目的。

[0057]

在本公开实施例中,术语“a与b相连”包含a、b两者相互接触地a与b相连的情形,或者a、b两者之间还间插有其他部件而a非接触地与b相连的情形。

[0058]

在本公开实施例中,术语“第一”、“第二”等是用于区别类似的对象,而不必用于描述特定的顺序或先后次序。

[0059]

需要说明的是,本发明实施例所记载的技术方案之间,在不冲突的情况下,可以任意组合。

[0060]

在三维存储器的制备过程中,通常会形成包括依次交替层叠设置的若干个绝缘层和若干个牺牲层的堆叠结构,相邻的两个牺牲层通过绝缘层间隔。然后,在堆叠结构呈台阶状的边缘覆盖绝缘的介质层,在该介质层内形成接触孔(ssct)。其中,采用导电的栅极层替换堆叠结构中的牺牲层,以形成三维存储器的栅叠层结构。

[0061]

为了减少接触孔形成过程中栅极层被过刻蚀,在台阶区形成接触孔时,可将堆叠结构分为上部区域及下部区域。上部区域为对应于堆叠结构的台阶状边缘上部的区域,是需要形成的接触孔深度较小的区域;下部区域为对应于堆叠结构的台阶状边缘下部的区域,是需要形成的接触孔深度较大的区域。然后分别采用两张光罩(mask)及两个刻蚀程式(recipe)分别对上部区域和下部区域进行光刻刻蚀。

[0062]

然而,采用两张光罩及两个刻蚀程式分别对堆叠结构的上部区域和下部区域进行光刻刻蚀,会导致生产成本较高的问题。因此,为了降低生产成本,可将上述两张光罩合并为一张光罩,对上述介质层进行光刻后采用一次刻蚀工艺形成所有的接触孔,并在接触孔中形成导电插塞后对导电插塞进行漏电分析,以确定三维存储器的质量是否满足要求。

[0063]

参照图1a所示,在过刻蚀的接触孔中形成的导电插塞为异常导电插塞。该异常导电插塞贯穿第一个栅极层,且与第二个栅极层连接。即该异常导电插塞漏电,使得第一个栅极层和第二个栅极层短接。

[0064]

图1b示出了对图1a示出的存储器进行电压对比(voltage contrast,vc)检测获得的明电压对比(bright voltage contrast,bvc)图像。由于漏电的导电插塞与第一个栅极层及第二个栅极层均电连接,因此,漏电的导电插塞可通过第一栅极层和第二栅极层与存储器中的其他电流通路电连接。

[0065]

可以理解的是,图1b中不漏电的导电插塞通过栅极层与存储器中的其他电流通路电连接。即图1b示出的结构中,漏电的导电插塞和不漏电的导电插塞均与存储器中的其他电流通路电连接,因此,在明电压对比图像中,漏电的导电插塞呈现的图像与不漏电的导电

插塞呈现的图像相同(均为白色或亮色),故无法通过明电压对比图像确定导电插塞是否漏电。

[0066]

并且,随着三维存储器的层数逐渐增加,牺牲层和绝缘层的厚度均会变得更薄,因此,当需要显露目标栅极层的接触孔发生过刻蚀时,通常会穿通目标栅极层与位于目标栅极层下方的绝缘层,以显露位于目标绝缘层下方的相邻的栅极层,从而使得填充过刻蚀的接触孔形成的导电插塞至少电连接相邻的两层栅极层。

[0067]

由此可知,随着栅极层的厚度和绝缘层的厚度变的越来越薄,由于接触孔的过刻蚀导致三维存储器发生漏电问题的情况可能会更加严重,因此,亟需提供一种能够准确、快速对三维存储器进行漏电分析的方法。

[0068]

图2是根据一示例性实施例示出的一种三维存储器漏电分析方法的流程图。所述三维存储器包括栅叠层结构,栅叠层结构包括依次交替层叠设置的绝缘层和导电的栅极层。参照图2所示,所述方法包括以下步骤:

[0069]

s110:在栅叠层结构的第一台阶区,形成贯穿台阶上表面栅极层的绝缘的阻挡结构;其中,台阶上表面的栅极层包括第一部分和第二部分,阻挡结构电隔离第一部分和第二部分;

[0070]

s120:形成与第一部分电连接的第一导电插塞;

[0071]

s130:形成与第二部分电连接的第二导电插塞;其中,第二导电插塞用于向栅极层的第二部分传输电信号;

[0072]

s140:对第一导电插塞进行电性检测,获取检测结果;基于检测结果中第一导电插塞呈现的图像,对三维存储器进行漏电分析。

[0073]

三维存储器可包括三维与非门(3d nand)存储器。三维存储器可为待进行漏电分析的任意一个三维存储器。应当理解的是,本公开实施例中待进行漏电分析的三维存储器不限于完成三维存储器全部制备工艺的器件,还可包括在生产线上完成栅叠层结构制备工艺后的器件结构。

[0074]

三维存储器可包括衬底,用于支撑栅叠层结构。在第一台阶区中,对于相邻的两个台阶,下层台阶沿平行衬底方向凸出于上层台阶,其中,下层台阶为相对靠近上述衬底的台阶,上层台阶为相对远离上述衬底的台阶。

[0075]

台阶上表面为该台阶相对远离上述衬底的表面,台阶下表面为该台阶相对靠近上述衬底的表面。需要指出的是,台阶上表面栅极层的第一部分、第二部分以及阻挡结构,沿平行于衬底方向并列排布。

[0076]

通常,会形成覆盖第一台阶区的绝缘的第一介质层,第一介质层的上表面可与栅叠层结构的上表面平齐,或者第一介质层的上表面可略高于栅叠层结构的上表面。

[0077]

s120可包括:形成贯穿第一介质层的第一接触孔,直至显露对应台阶上表面栅极层的第一部分;填充第一接触孔,形成第一导电插塞。例如,可通过光刻和刻蚀的方式形成垂直于栅叠层结构的第一接触孔。

[0078]

结合图1b所示,当需要形成与第一个栅极层电连接的导电插塞时,形成的第一接触孔需要贯穿覆盖第一个栅极层的第一介质层,直至显露第一个栅极层。若在形成该第一接触孔的过程发生了过刻蚀,使得第一接触孔贯穿第一个栅极层、以及第一个栅极层和第二个栅极层之间的绝缘层,直至显露第二个栅极层时,填充发生过刻蚀的第一接触孔就会

形成漏电的导电插塞,漏电的导电插塞电连接第一个栅极层和第二个栅极层。

[0079]

示例性地,栅叠层结构还包括第二台阶区,第二台阶区和第一台阶区位于栅叠层结构的不同端部,s130可包括:在第二台阶区,形成与栅极层电连接的第二导电插塞;其中,第二导电插塞与第一导电插塞电隔离。

[0080]

通过第二导电插塞向栅极层的第二部分传输的电信号,可包括:用于控制控制三维存储器进行数据存储、擦除或读取的控制信号。

[0081]

第一台阶区和第二台阶区可位于栅叠层结构相对设置的两端。需要指出的是,在第二台阶区中,每个栅极层都与不同的一个第二导电插塞电连接。对于具有第一部分和第二部分的栅极层,该栅极层的第二部分在第二台阶区中与第二导电插塞电连接。

[0082]

上述覆盖第一台阶区的第一介质层,还可覆盖第二台阶区。s130可包括:在第二台阶区,形成贯穿第一介质层的第二接触孔,直至显露对应台阶上表面的栅极层;填充第二接触孔,形成第二导电插塞。

[0083]

示例性地,可通过光刻和刻蚀的方式形成垂直于栅叠层结构的第二接触孔。

[0084]

第一导电插塞和第二导电插塞均为导电插塞。导电插塞是指内部填充有导电材料、可以起到电连接作用的柱状结构。在本领域中,导电插塞也可被称为导电接触(contact)。

[0085]

在一些实施例中,s140包括:对第一导电插塞进行电子束检测(electrons beam inspection,ebi)。

[0086]

电子束检测装置通常用于半导体器件生产过程中的缺陷检测,以聚焦电子束作为检测源,在进行电子束检测时,样品的缺陷区域表现为亮色,无缺陷区域表现为暗色。对应于本公开,缺陷区域即为存在漏电的导电插塞,无缺陷区域即为不漏电的导电插塞。暗色通常呈现为黑色,亮色通常表现为白色。

[0087]

获取的检测结果至少包括:获取电子束检测图像。由于检测结果中既可包括漏电的第一导电插塞呈现的图像,又可包括不漏电的第一导电插塞呈现的图像,因此,上述检测结果也可包括电子束检测对比图像。

[0088]

在一些实施例中,s140包括:

[0089]

检测结果中第一导电插塞表面呈现亮色,对应于第一导电插塞漏电;

[0090]

检测结果中第一导电插塞表面呈现暗色,对应于第一导电插塞不漏电。

[0091]

当第一导电插塞不漏电时,由于阻挡结构电隔离栅极层的第一部分与第二部分,第一导电插塞和第二导电插塞之间断路,当对第一导电插塞进行电子束检测时,得到的图案呈暗色,即电子束检测的图案呈暗色,表明当前第一导电插塞不漏电。

[0092]

当第一导电插塞漏电时,漏电的第一导电插塞穿过台阶上表面的一个栅极层,并与该一个栅极层下方的至少另一个栅极层电连接,第一导电插塞和第二导电插塞之间短路。因此,对漏电的第一导电插塞进行电子束检测时,得到的图案呈亮色,即电子束检测的图案呈亮色,表明当前第一导电插塞漏电。

[0093]

因此,根据本公开实施例中提供的漏电分析方法,能够直观、高效地进行漏电分析,确定漏电的第一导电插塞,可视性分析效果好。

[0094]

此外,本公开提供的方法在检测过程中不会对三维存储器结构进行物理破坏,无需造成三维存储器产品浪费,可在制造车间内直接监测漏电情况,进行产线上监测,相较于

通过透射电子显微镜进行漏电分析,降低了分析成本,缩短了分析时间,进而可加快工艺研发速度。

[0095]

图3是根据一示例性实施例对一种三维存储器漏电分析的检测结果示意图。对于每一个第一导电插塞,当第一导电插塞正常时,即第一导电插塞未发生漏电时,第一导电插塞对应的图像呈现为暗色。

[0096]

参照图3所示,当第一导电插塞漏电时,漏电的第一导电插塞会穿过栅极层的第一部分,与该栅极层下方的另一栅极层电连接。由于另一栅极层也与一个第二导电插塞电连接,因此,漏电的第一导电插塞与第二导电插塞之间短路,第一导电插塞对应的图像呈现为亮色。暗色通常呈现为黑色,亮色通常呈现为白色。

[0097]

通常,在一个三维存储器芯片(die)中,可包括多个存储平面(plane)。每一个存储平面可包括多个虚拟存储块(dummy block)和多个存储块。虚拟存储块不用于执行存储功能,存储块用于执行存储功能。虚拟存储块的结构可与存储块的结构相同。并且,虚拟存储块可与存储块同时进行制备。

[0098]

一个存储平面中,虚拟存储块与存储块位于不同的区域。例如,参照图4所示,虚拟存储块可位于存储平面的边缘区域(即存储平面中未予虚线框内的区域)。

[0099]

在存储平面平行于第一方向上(y方向)的边缘区域,可设置有多个(例如,20个)虚拟存储块。此处,第一方向和第二方向(x方向)所在的平面平行于衬底。本公开提供的上述漏电分析方法可应用于任意一个或多个虚拟存储块中。

[0100]

在一实施例中,在虚拟存储块的栅叠层结构中设置上述第一导电插塞、第二导电插塞和阻挡结构,以对虚拟存储块区域内的栅叠层结构进行漏电分析。

[0101]

可以理解的是,由于虚拟存储块包括的栅叠层结构、阻挡结构以及第一导电插塞,与存储块包括的栅叠层结构、阻挡结构以及第一导电插塞,结构对应相同且可对应同时形成,因此,通过对虚拟存储块的栅叠层结构中第一导电插塞进行漏电分析,可确定存储块中对应的第一导电插塞是否漏电。

[0102]

在一实施例中,在存储块的栅叠层结构中设置上述第一导电插塞、第二导电插塞和阻挡结构,以对存储块区域内的栅叠层结构中的第一导电插塞进行漏电分析。

[0103]

在一实施例中,在虚拟存储块的栅叠层结构中设置上述第一导电插塞、第二导电插塞和阻挡结构,以对虚拟存储块区域内的栅叠层结构中的第一导电插塞进行漏电分析,同时在存储块的栅叠层结构中设置上述第一导电插塞、第二导电插塞和阻挡结构,以对存储块区域内的栅叠层结构中的第一导电插塞进行漏电分析。

[0104]

相较于仅在虚拟存储块或存储块中形成第一导电插塞并进行漏电分析,在本公开实施例中,通过在虚拟存储块和存储块中均形成上述第一导电插塞和阻挡结构,可通过对虚拟存储块中的第一导电插塞和存储块中的第一导电插塞均进行漏电分析,增加了能够用于对该三维存储器进行漏电分析的样品数量,进而能够全面的对制备三维存储器的整片晶圆上导电插塞漏电情况进行检测与分析,有利于缩短形成不漏电的导电插塞的制成研发周期。

[0105]

在一些实施例中,第一台阶区中至少一个台阶包括两层栅极层;s110包括:

[0106]

在第一台阶区包括两层栅极层的台阶中,形成贯穿相对远离衬底的一个栅极层的阻挡结构,相对远离衬底的一个栅极层被阻挡结构划分为电隔离的第一部分和第二部分;

[0107]

其中,阻挡结构与相对靠近衬底的另一个栅极层接触且为贯穿所述另一个栅极层;或者,阻挡结构与相对靠近衬底的另一个栅极层之间具有所述绝缘层。

[0108]

当一个台阶中包括两层栅极层时,在第一台阶区中两侧栅极层的侧表面对齐。可以理解的是,栅极层的侧表面为垂直于衬底所在平面的表面。

[0109]

需要指出的是,当一个台阶中包括两层栅极层时,一个台阶中的每个栅极层在第二台阶区中也与一个第二导电插塞一一对应电连接。对于相对靠近衬底的另一个栅极层,第二导电插塞,还可用于向所述另一个栅极层传输上述电信号。

[0110]

本公开实施例中,通过在第一台阶区中形成包括两层栅极层的台阶,可以减少第一台阶区中台阶的数量,相应减少了形成第一台阶区所需要的曝光与刻蚀次数,降低了工艺成本。

[0111]

需要指出的是,对于存储块中的栅叠层结构,当第一台阶区中的一个台阶包括两层栅极层时,该台阶在的两个栅极层可在第二台阶区中分别与不同的第二导电插塞连接,以接收上述控制信号。

[0112]

在一些实施例中,结合图5a至图5c所示,s110包括:

[0113]

如图5a所示,形成堆叠结构;其中,堆叠结构包括依次交替层叠设置的绝缘层和牺牲层;

[0114]

如图5b所示,在堆叠结构对应于第一台阶区的第三台阶区,形成贯穿台阶上表面牺牲层的第一沟槽;

[0115]

如图5c所示,填充第一沟槽,形成阻挡结构;

[0116]

在形成阻挡结构之后,所述方法还包括:去除牺牲层,以在相邻绝缘层之间形成间隙,填充所述间隙,形成栅极层,所述栅极层和所述绝缘层形成所述栅叠层结构。

[0117]

示例性地,如图5a所示,在第三方向(z方向)上,可通过化学气相沉积的方式,依次形成交替层叠设置的绝缘层和牺牲层,相邻的牺牲层之间间隔有绝缘层。

[0118]

需要指出的是,当堆叠结构中的牺牲层被导电的材料替换,形成栅极层后,堆叠结构即成为上述栅叠层结构,堆叠结构的第三台阶区即成为栅叠层结构的第一台阶区。

[0119]

示例性地,参照图5b所示,在第三台阶区中,当一个台阶包括两个牺牲层和两个绝缘层时,形成的第一沟槽还可贯穿相对远离衬底的一个绝缘层,直至显露相对靠近衬底的另一个牺牲层。此时,在第一沟槽中形成的阻挡结构与上述相对靠近衬底的另一个牺牲层接触。

[0120]

需要指出的是,在形成第一沟槽时,不会对该台阶中上述相对靠近衬底的另一个牺牲层造成损伤。

[0121]

在一些实施例中,参照图5d所示,在第三台阶区中,当一个台阶包括两个牺牲层和两个绝缘层时,第一导电插塞的底部可停留在相对远离衬底的一个绝缘层的上表面。此时,该台阶中相对远离衬底的绝缘层,位于阻挡结构与该台阶中相对靠近衬底的牺牲层之间。

[0122]

在一些实施例中,结合图6a至图6d所示,所述去除牺牲层,以在相邻绝缘层之间形成间隙,填充所述间隙,形成栅极层,包括:

[0123]

如图6a所示,形成贯穿堆叠结构的第二沟槽;其中,第二沟槽与阻挡结构交叉设置;

[0124]

如图6b所示,通过第二沟槽,去除牺牲层,以在相邻绝缘层之间形成间隙;

[0125]

如图6c所示,通过第二沟槽,填充间隙,形成栅极层;

[0126]

在形成所述栅极层之后,所述方法还包括:如图6d所示,形成覆盖第二沟槽侧壁的绝缘的阻挡层;填充第二沟槽,形成覆盖阻挡层的导电源极。

[0127]

可以理解的是,堆叠结构通常设置在衬底上。第二沟槽以及阻挡结构均垂直于该衬底,且交叉设置的第二沟槽和阻挡结构相互垂直。

[0128]

此外,本公开实施例也不排除直接形成依次交替层叠设置的绝缘层和栅极层,即无需采用牺牲层占据后续用于形成栅极层的位置,而是在衬底上直接沉积三维存储器所需的栅极层材料。

[0129]

在一些实施例中,参照图7a所示,s120可包括:在形成栅极层后,形成贯穿第一介质层的第一接触孔,以显露台阶上表面的栅极层的第一部分;填充第一接触孔,形成第一导电插塞。

[0130]

图7b示出了形成有第一导电插塞的三维存储器在平行于衬底所在平面内的截面图。可以理解的是,第一导电插塞为柱状结构,因此,图7b中第一导电插塞呈圆形;阻挡结构为沿着第二方向延伸的条状结构,因此,图7b中阻挡结构呈矩形。

[0131]

图8是根据一示例性实施例示出的一种三维存储器100的示意图。参照图8所示,三维存储器100包括:

[0132]

栅叠层结构110,包括:依次交替层叠设置的绝缘层111和导电的栅极层112;其中,在栅叠层结构110端部的第一台阶区110a中,台阶上表面的栅极层112包括第一部分112a和第二部分112b;

[0133]

绝缘的阻挡结构120,位于第一台阶区110a,贯穿台阶上表面的栅极层112,且电隔离第一部分112a和第二部分112b;

[0134]

第一导电插塞130,垂直于栅叠层结构110,且与第一部分112a电连接;其中,基于对第一导电插塞130进行电性分析所获取检测结果中第一导电插塞130呈现的图像,用于对三维存储器110进行漏电分析;

[0135]

第二导电插塞140,垂直于栅叠层结构110,且与第二部分112b电连接,用于向第二部分112b传输电信号。

[0136]

栅叠层结构110中栅极层112的层数可包括:8层、32层、64层或者128层等。相邻的两个栅极层112之间通过一个绝缘层111隔开。可以理解的是,栅极层112的层数越多,越能提高三维存储器的集成度。

[0137]

栅极层112的组成材料包括:金属、合金或者多晶硅(poly)。例如,钨、镍或者钨镍合金等。

[0138]

绝缘层111的组成材料包括但不限于硅氧化物、硅氮化物或者硅氮氧化物等。示例性地,绝缘层111的组成材料包括氧化硅(sio2)。

[0139]

阻挡结构120的组成材料可与绝缘层111的组成材料相同。

[0140]

第一导电插塞130的组成材料以及第二导电插塞140的组成材料,均可与栅极层112的组成材料相同。

[0141]

在一些实施例中,栅叠层结构110还具有第二台阶区110b;第二台阶区110b与第一台阶区110a位于栅叠层结构110的不同端部。

[0142]

上述电信号可包括:控制三维存储器100进行数据存储、擦除或读取的控制信号。

第二导电插塞140的一端与栅极层112的第二部分112b电连接,第二导电插塞140的另一端可与后段互连金属线连接,从而形成控制信号传输的通路。

[0143]

三维存储器100还包括:衬底,用于支撑栅叠层结构110。衬底可包括:硅片、锗片或者绝缘体上硅(silicon on insulator,soi)等。

[0144]

本公开实施例中,通过设置阻挡结构120,阻挡结构120电隔离台阶上表面栅极层112的第一部分112a和第二部分112b,并设置与该第一部分112a接触的第一导电插塞130,通过第一导电插塞130对三维存储器进行漏电分析,相较于采用透射电子显微镜进行漏电分析,能够直观、高效地进行漏电分析,确定漏电的第一导电插塞130,可视性分析效果好。

[0145]

此外,通过本公开实施例提供的结构进行漏电分析,不会对三维存储器结构进行物理破坏,无需造成三维存储器产品浪费,可在制造车间内直接监测漏电情况,进行产线上监测,相较于通过透射电子显微镜进行漏电分析,降低了分析成本,缩短了分析时间,进而可加快工艺研发速度。

[0146]

阻挡结构120和第一导电插塞130可设置于三维存储器芯片的虚拟存储块内。或者,阻挡结构120和第一导电插塞130可设置于三维存储器芯片中用于执行存储功能的存储块内。

[0147]

在一些实施例中,三维存储器包括存储块;其中,上述第一导电插塞、第二导电插塞和阻挡结构形成于存储块的栅叠层结构上,以对存储块区域内的栅叠层结构中的第一导电插塞进行漏电分析。

[0148]

在一些实施例中,所述三维存储器包括:虚拟存储块;其中,阻挡结构、第一导电插塞和第二导电插塞形成于所述虚拟存储块的栅叠层结构上。

[0149]

在一些实施例中,还可在在虚拟存储块的栅叠层结构中设置上述第一导电插塞、第二导电插塞和阻挡结构,以对虚拟存储块区域内的栅叠层结构中的第一导电插塞进行漏电分析,同时在存储块的栅叠层结构中设置上述第一导电插塞、第二导电插塞和阻挡结构,以对存储块区域内的栅叠层结构中的第一导电插塞进行漏电分析。

[0150]

阻挡结构120和第一导电插塞130可设置于三维存储器芯片的虚拟存储块的栅叠层结构和存储块的栅叠层结构中,并且,虚拟存储块包括的栅叠层结构、阻挡结构以及第一导电插塞,与存储块包括的栅叠层结构、阻挡结构以及第一导电插塞,结构对应相同且可对应同时形成。

[0151]

由于虚拟存储块包括的栅叠层结构、阻挡结构以及第一导电插塞,与存储块包括的栅叠层结构、阻挡结构以及第一导电插塞,结构对应相同且可对应同时形成,因此,通过对虚拟存储块的质量进行检测,可检测存储块的质量。

[0152]

相较于仅在虚拟存储块中形成第一导电插塞并进行漏电分析,本公开实施例提供的三维存储器在虚拟存储块和存储块中均设置上述第一导电插塞和阻挡结构,可通过对虚拟存储块中的第一导电插塞和存储块中的第一导电插塞均进行漏电分析,增加能用于对该三维存储器进行漏电分析的样品数量,进而能够全面的对制备三维存储器的整片晶圆上导电插塞的漏电情况进行检测与分析,有利于缩短形成不漏电的导电插塞的制成研发周期。

[0153]

在一些实施例中,参照图8所示,第一台阶区110a中,至少一个台阶包括两层栅极层112;其中,

[0154]

台阶中相对远离衬底的一个栅极层112,包括:被阻挡结构划分为电隔离的第一部

分112a和第二部分112b;

[0155]

台阶中相对靠近衬底的另一个栅极层112,与阻挡结构120接触,且阻挡结构未贯穿所述另一个栅极层112;或者,阻挡结构120与上述另一个栅极层112之间具有绝缘层111。

[0156]

需要指出的是,在第一台阶区110a中,当一个台阶中包括两层栅极层112时,阻挡结构120贯穿相对远离衬底的一个栅极层112,相对靠近衬底的另一个栅极层112没有被阻挡结构120分割为电隔离的两个部分。

[0157]

需要指出的是,本公开实施例提供的三维存储器中,当第一台阶区110a中每个台阶只包括一个栅极层112时,每个栅极层112均包括第一部分112a和第二部分112b。在第二台阶区110b中,第二导电插塞140与栅极层112的第二部分112b电连接。并且,不同的栅极层112与不同的第一导电插塞130电连接,且不同的栅极层112与不同的第二导电插塞140电连接。

[0158]

当第一台阶区110a中的台阶包括至少两个栅极层112时,每个栅极层在第二台阶区中均与一个第二导电插塞电连接。

[0159]

第一台阶区110a和第二台阶区110b可位于栅叠层结构110相对设置的两端。需要指出的是,在第二台阶区110b中,每个栅极层112都与不同的一个第二导电插塞140电连接。对于具有第一部分112a和第二部分112b的栅极层112,该栅极层112的第二部分112b在第二台阶区110b中与第二导电插塞140电连接。

[0160]

参照图8所示,栅叠层结构还可包括核心区110c。第一台阶区110a、第二台阶区110b和核心区110c沿平行于衬底方向并列设置。在核心区110c中还可设置有垂直贯穿栅叠层结构的存储串。其中,第二导电插塞传输的控制信号,用于控制存储串中电荷的读取和擦除等操作。

[0161]

在一些实施例中,三维存储器100还包括:

[0162]

导电源极,贯穿栅叠层结构110,且与阻挡结构120交叉设置;

[0163]

绝缘的阻挡层,位于导电源极的侧壁和栅极层112之间。

[0164]

在本公开所提供的实施例中,应该理解到,所揭露的装置、系统与方法,可以通过其他的方式实现。以上所述,仅为本公开的具体实施方式,但本公开的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本公开揭露的技术范围内,可轻易想到变化或替换,都应涵盖在本公开的保护范围之内。因此,本公开的保护范围应以所述权利要求的保护范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1