集成电路装置及其形成方法与流程

1.本发明涉及半导体制造技术领域,尤其涉及一种集成电路装置及其形成方法。

背景技术:

2.熔丝是集成电路装置中的一个电阻型结构。在集成电路装置中,通过熔丝的熔断,达到调整集成电路内部电性功能或者电学参数的目的。在具有双层大马士革结构的集成电路装置中,多采用第一金属层、第二金属层以及位于所述第一金属层和第二金属层之间的金属连接层共同作为熔丝,此种熔丝的结构能够有效的避免因对准标记的腐蚀而导致的套刻偏移问题。但是,由于这种熔丝结构复杂,制程工艺繁琐,在后续的熔丝熔断过程中需要较大的熔断能量,且经常会出现熔断不完全的现象,从而导致工艺参数难以控制以及熔断能量的浪费,间接增加了集成电路装置的制造成本。

3.因此,如何简化集成电路装置中的熔丝的结构,降低熔丝的熔断能量,是目前亟待解决的技术问题。

技术实现要素:

4.本发明提供一种集成电路装置及其形成方法,用于解决现有的熔丝结构复杂、制程工艺繁琐的问题,并降低熔丝的熔断能量,实现对集成电路装置制程良率的提高以及制造成本的降低。

5.为了解决上述问题,本发明提供了一种集成电路装置的形成方法,包括如下步骤:

6.提供一衬底,所述衬底包括第一区域和位于所述第一区域外部的第二区域,所述衬底内部具有位于所述第一区域的第一插塞和位于所述第二区域的第二插塞;

7.形成覆盖所述衬底的第一覆盖层;

8.刻蚀所述第一覆盖层,于所述第一区域形成暴露所述第一插塞的第一开口;

9.于所述第一开口内形成第一导电层;

10.形成覆盖所述第一导电层和所述衬底的隔离层;

11.于所述第一区域形成暴露所述第一导电层的接触孔和位于所述接触孔上方且与所述接触孔连通的沟槽、并于所述第二区域形成暴露所述第二插塞的第二开口;

12.于所述接触孔内形成导电连接层、于所述沟槽内形成第二导电层、并于所述第二开口内形成熔丝。

13.可选的,形成覆盖所述第一导电层和所述第一覆盖层的隔离层的具体步骤包括:

14.形成覆盖所述第一导电层和所述第一覆盖层的第一子隔离层;

15.形成覆盖所述第一子隔离层的第二子隔离层,所述第一子隔离层和所述第二子隔离层共同构成隔离层。

16.可选的,于所述第一区域形成暴露所述第一导电层的接触孔和位于所述接触孔上方且与所述接触孔连通的沟槽、并于所述第二区域形成暴露所述第二插塞的第二开口的具体步骤包括:

17.刻蚀位于所述第一区域和所述第二区域的所述第二子隔离层,于所述第一区域形成暴露所述第一子隔离层的初始接触孔、并于所述第二区域形成贯穿所述第二子隔离层的初始第二开口;

18.刻蚀所述初始接触孔侧壁的所述第二子隔离层和所述初始接触孔底部的所述第一子隔离层、并刻蚀所述初始第二开口底部的所述第一子隔离层和所述第一覆盖层,于所述第一区域形成暴露所述第一导电层的接触孔和位于所述接触孔上方且与所述接触孔连通的沟槽、并于所述第二区域形成暴露所述第二插塞的第二开口。

19.可选的,于所述第一区域形成暴露所述第一导电层的接触孔和位于所述接触孔上方且与所述接触孔连通的沟槽、并于所述第二区域形成暴露所述第二插塞的第二开口的具体步骤包括:

20.刻蚀位于所述第一区域和所述第二区域的所述第二子隔离层,于所述第一区域形成未贯穿所述第二子隔离层的初始沟槽、并于所述第二区域形成未贯穿所述第二子隔离层的窗口;

21.刻蚀所述初始沟槽底部的所述第二子隔离层和第一子隔离层、并刻蚀所述窗口底部的所述第二子隔离层、所述第一子隔离层和所述第一覆盖层,于所述第一区域形成暴露所述第一导电层的接触孔和位于所述接触孔上方且与所述接触孔连通的沟槽、并于所述第二区域形成暴露所述第二插塞的第二开口。

22.可选的,于所述接触孔内形成导电连接层、于所述沟槽内形成第二导电层、并于所述第二开口内形成熔丝的具体步骤包括:

23.填充导电材料于所述接触孔、所述沟槽和所述第二开口内,于所述接触孔内形成导电连接层、于所述沟槽内形成第二导电层、并于所述第二开口内形成熔丝。

24.可选的,还包括如下步骤:

25.形成覆盖所述第二导电层、所述熔丝和所述隔离层的第二覆盖层。

26.为了解决上述问题,本发明还提供了一种集成电路装置,包括:

27.衬底,所述衬底包括第一区域和位于所述第一区域外部的第二区域,所述衬底内部具有位于所述第一区域的第一插塞和位于所述第二区域的第二插塞,所述衬底表面具有第一覆盖层和位于所述第一覆盖层表面的隔离层;

28.第一导电层,位于所述第一区域的所述第一覆盖层内,且与所述第一插塞电连接;

29.导电连接层,位于所述第一导电层表面;

30.第二导电层,位于所述导电连接层表面,所述导电连接层的一端电连接所述第一导电层、另一端电连接所述第二导电层;

31.熔丝,位于所述第二区域,所述熔丝呈实心柱状结构、并贯穿所述隔离层和所述第一覆盖层,所述熔丝的底面与所述第二插塞电连接、所述熔丝的顶面与所述第二导电层的顶面平齐。

32.可选的,所述熔丝、所述第二导电层和所述导电连接层的材料相同。

33.可选的,所述隔离层包括:

34.第一子隔离层,覆盖于所述衬底表面;

35.第二子隔离层,覆盖于所述第一子隔离层表面,且所述第二子隔离层的厚度大于所述第一子隔离层。

36.可选的,还包括:

37.第二覆盖层,覆盖于所述第二导电层、所述熔丝和所述隔离层表面。

38.本发明提供的集成电路装置及其形成方法,在形成第一导电层的过程中,不对用于形成熔丝的第二区域进行处理,在形成导电连接层和第二导电层的过程中同时形成熔丝,使得形成的熔丝呈简单的实心柱状结构,与第一导电层和第二导电层的结构无关,不仅简化了熔丝的结构,使得仅仅只需要较低的能量就可以实现熔丝的熔断,而且简化了整个集成电路装置的制造流程,降低了集成电路装置的制程成本,也提高了集成电路装置的良率。

附图说明

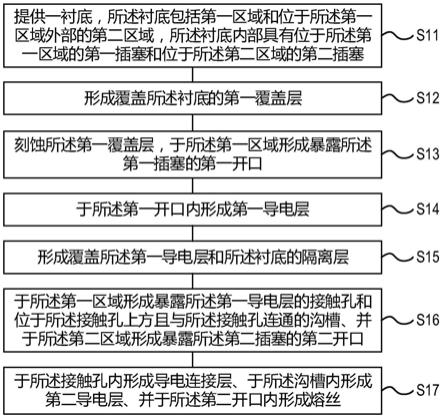

39.附图1是本发明具体实施方式中集成电路装置的形成方法流程图;

40.附图2a-2j是本发明一具体实施方式在形成集成电路装置的过程中主要的工艺截面示意图;

41.附图3a-3b是本发明另一具体实施方式在形成集成电路装置的过程中主要的工艺截面示意图。

具体实施方式

42.下面结合附图对本发明提供的集成电路装置及其形成方法的具体实施方式做详细说明。

43.本具体实施方式提供了一种集成电路装置的形成方法,附图1是本发明具体实施方式中集成电路装置的形成方法流程图,附图2a-2j是本发明一具体实施方式在形成集成电路装置的过程中主要的工艺截面示意图。如图1、图2a-图2i所示,本具体实施方式提供的集成电路装置的形成方法,包括如下步骤:

44.步骤s11,提供一衬底20,所述衬底20包括第一区域ⅰ和位于所述第一区域ⅰ外部的第二区域ⅱ,所述衬底20内部具有位于所述第一区域ⅰ的第一插塞21和位于所述第二区域ⅱ的第二插塞22,如图2a所示。

45.具体来说,所述衬底20可以为单层结构,也可以为由多个半导体层构成的多层结构。本具体实施方式中所述的多层是指两层及两层以上。所述衬底20的具体材料,本领域技术人员可以根据实际需要进行选择,本具体实施方式以所述衬底20的材料为氧化物材料(例如二氧化硅)为例进行说明。所述衬底20的所述第一区域ⅰ上方用于形成双层大马士革结构,并与外界焊盘电连接;所述衬底20的所述第二区域ⅱ的上方用于形成熔丝,通过熔断所述熔丝达到调整所述集成电路装置的电学性能或者电性参数的目的。

46.于所述衬底20内形成所述第一插塞21和所述第二插塞22的具体方法,可以是先对所述衬底20进行刻蚀,于所述第一区域ⅰ形成第一通孔、并于所述第二区域ⅱ形成第二通孔;之后,采用导电材料,例如金属钨或者掺杂多晶硅填充所述第一通孔和所述第二通孔,同时形成所述第一插塞21和所述第二插塞22;最后,可以采用化学机械研磨工艺(cmp)进行平坦化处理,使得所述第一插塞21的顶面、所述第二插塞22的顶面与所述衬底20的顶面平齐。

47.步骤s12,形成覆盖所述衬底20的第一覆盖层23,如图2b所示。

48.具体来说,在对所述第一插塞21和所述第二插塞22进行平坦化处理之后,可以采用化学气相沉积工艺、物理气相沉积工艺或者原子层沉积工艺沉积所述第一覆盖层23,使得所述第一覆盖层23覆盖所述第一插塞21的顶面、所述第二插塞22的顶面和所述衬底20的顶面。其中,所述第一覆盖层23的材料为绝缘材料,其具体类型本领域技术人员可以根据实际需要进行选择。所述第一覆盖层23的厚度可以根据后续所要形成的第一导电层的厚度进行设置。

49.步骤s13,刻蚀所述第一覆盖层23,于所述第一区域ⅰ形成暴露所述第一插塞21的第一开口24,如图2c所示。

50.具体来说,所述第一覆盖层23的材料为绝缘材料。通过对所述衬底20的所述第一区域ⅰ上方的所述第一覆盖层23进行刻蚀,以所述第一插塞21为刻蚀截止层,形成贯穿所述第一覆盖层23且暴露所述衬底20中的所述第一插塞21的所述第一开口24。在本次刻蚀过程中,不对所述衬底20的所述第二区域ⅱ上方的所述第一覆盖层23进行刻蚀,一方面确保后续形成的熔丝中不具有第一导电层结构以及不残留第一导电层的材料;另一方面由于仅对所述第一区域ⅰ上方的所述第一覆盖层23进行刻蚀,可以降低对准难度,从而简化刻蚀工艺。所述第一开口24的内径尺寸,本领域技术人员可以根据所要形成的第一导电层的具体结构进行设置。

51.步骤s14,于所述第一开口24内形成第一导电层25,如图2d所示。

52.具体来说,采用金属铜等导电材料填充满所述第一开口24,形成所述第一导电层25。之后,采用化学机械研磨工艺对所述第一导电层25进行平坦化处理,使得所述第一导电层25的顶面(即所述第一导电层25背离所述衬底20的表面)与所述第一覆盖层23的顶面(即所述第一覆盖层23背离所述衬底20的表面)平齐。

53.步骤s15,形成覆盖所述第一导电层25和所述衬底20的隔离层,如图2e所示。

54.所述隔离层可以为单层结构,也可以为多层结构,本领域技术人员可以根据实际需要进行选择。为了确保后续形成的所述接触孔的形貌,本具体实施方式中,形成覆盖所述第一导电层25和所述第一覆盖层23的隔离层的具体步骤包括:

55.形成覆盖所述第一导电层25和所述第一覆盖层23的第一子隔离层26;

56.形成覆盖所述第一子隔离层26的第二子隔离层27,所述第一子隔离层26和所述第二子隔离层27共同构成隔离层。

57.具体来说,首先,形成覆盖所述第一导电层25顶面和所述第一覆盖层23顶面的所述第一子隔离层26;然后,形成覆盖所述第一子隔离层26的所述第二子隔离层27。通过形成相互层叠的所述第一子隔离层26和所述第二子隔离层27,通过选择合适的材料,使得所述第一子隔离层26与所述第二子隔离层27之间具有一定的刻蚀选择比(例如刻蚀选择比大于3),可以通过选择性刻蚀控制后续所要形成的接触孔、沟槽和第二开口的形貌。在本具体实施方式中,所述第一子隔离层26可以为单层结构,其材料为氮化物材料,例如氮化硅;所述第一子隔离层26也可为由sin/sicn/sion构成的多层结构。所述第二子隔离层27的材料可以为氧化物材料,例如二氧化硅。

58.步骤s16,于所述第一区域ⅰ形成暴露所述第一导电层25的接触孔31和位于所述接触孔31上方且与所述接触孔31连通的沟槽30、并于所述第二区域ⅱ形成暴露所述第二插塞22的第二开口32,如图2g所示。

59.可选的,于所述第一区域ⅰ形成暴露所述第一导电层25的接触孔31和位于所述接触孔31上方且与所述接触孔31连通的沟槽30、并于所述第二区域ⅱ形成暴露所述第二插塞22的第二开口32的具体步骤包括:

60.刻蚀位于所述第一区域ⅰ和所述第二区域ⅱ的所述第二子隔离层27,于所述第一区域ⅰ形成暴露所述第一子隔离层26的初始接触孔28、并于所述第二区域ⅱ形成贯穿所述第二子隔离层27的初始第二开口29,如图2f所示;

61.刻蚀所述初始接触孔28侧壁的所述第二子隔离层27和所述初始接触孔28底部的所述第一子隔离层26、并刻蚀所述初始第二开口29底部的所述第一子隔离层26和所述第一覆盖层23,于所述第一区域ⅰ形成暴露所述第一导电层25的接触孔31和位于所述接触孔31上方且与所述接触孔31连通的沟槽30、并于所述第二区域ⅱ形成暴露所述第二插塞22的第二开口32,如图2g所示。

62.为了简化刻蚀步骤,可选的,所述第二子隔离层27的材料与所述第一覆盖层23的材料相同。

63.具体来说,在形成所述第一子隔离层26和所述第二子隔离层27之后,先以所述第一子隔离层26为刻蚀截止层刻蚀所述第二子隔离层27,于所述第一区域ⅰ上、与所述第一导电层25对应的位置形成贯穿所述第二子隔离层27的所述初始接触孔28,并于所述第二区域ⅱ上、与所述第二插塞22对应的位置形成贯穿所述第二子隔离层27的所述初始第二开口29。接着,沿所述初始接触孔28刻蚀所述初始接触孔28底部的所述第一子隔离层26、暴露所述第一导电层25,并同时沿所述初始第二开口29刻蚀所述第一子隔离层26、暴露位于所述第二区域ⅱ上的所述第一覆盖层23。刻蚀所述初始接触孔28上部的侧壁,扩大所述初始接触孔28上部的开口尺寸,并使得多个所述初始接触孔28的上部连通,形成内径尺寸大于一个所述初始接触孔28的所述沟槽30。在其他具体实施方式中,也可以仅仅扩大所述初始接触孔28的上部的开口宽度,而无需使相邻的所述初始接触孔28连通。之后,沿所述初始第二开口29继续刻蚀所述第一覆盖层23,暴露所述第二插塞23。本具体实施方式将所述第二子隔离层27的材料设置为与所述第一覆盖层23的材料相同,从而在刻蚀形成所述沟槽30的过程中,同时对所述第一覆盖层23进行刻蚀以形成所述第二开口32,能够节省刻蚀步骤,降低刻蚀成本,提高刻蚀效率。

64.本具体实施方式是以在双层大马士革结构中先形成所述接触孔31、再形成所述沟槽为例进行说明。在其他具体实施方式中,可以先形成双层大马士革结构中的沟槽、再形成用于连接相邻两层导电层的接触孔。附图3a-3b是本发明另一具体实施方式在形成集成电路装置的过程中主要的工艺截面示意图。如图3a-3b所示,在其他具体实施方式中,于所述第一区域ⅰ形成暴露所述第一导电层25的接触孔31和位于所述接触孔31上方且与所述接触孔31连通的沟槽30、并于所述第二区域ⅱ形成暴露所述第二插塞22的第二开口32的具体步骤包括:

65.刻蚀位于所述第一区域ⅰ和所述第二区域ⅱ的所述第二子隔离层27,于所述第一区域ⅰ形成未贯穿所述第二子隔离层27的初始沟槽40、并于所述第二区域ⅱ形成未贯穿所述第二子隔离层27的窗口41;

66.刻蚀所述初始沟槽40底部的所述第二子隔离层27和第一子隔离层26、并刻蚀所述窗口41底部的所述第二子隔离层27、所述第一子隔离层26和所述第一覆盖层23,于所述第

一区域ⅰ形成暴露所述第一导电层25的接触孔31和位于所述接触孔31上方且与所述接触孔31连通的沟槽30、并于所述第二区域ⅱ形成暴露所述第二插塞22的第二开口32,如图3b所示。

67.步骤s17,于所述接触孔31内形成导电连接层33、于所述沟槽30内形成第二导电层34、并于所述第二开口32内形成熔丝35。

68.可选的,于所述接触孔31内形成导电连接层33、于所述沟槽30内形成第二导电层34、并于所述第二开口32内形成熔丝35的具体步骤包括:

69.填充导电材料于所述接触孔31、所述沟槽30和所述第二开口32内,于所述接触孔31内形成导电连接层33、于所述沟槽30内形成第二导电层34、并于所述第二开口32内形成熔丝35。

70.具体来说,所述导电连接层33、所述第二导电层34、所述熔丝35的材料可以均与所述第一导电层25的材料相同,例如均为金属铜材料。本领域技术人员也可以根据实际需要将所述导电连接层33、所述第二导电层34、所述熔丝35和所述第一导电层25的材料设置为不同。所述熔丝35的截面形状可以为圆形,也可以为圆角矩形。

71.可选的,所述集成电路装置的形成方法还包括如下步骤:

72.形成覆盖所述第二导电层34、所述熔丝35和所述隔离层的第二覆盖层。

73.具体来说,所述第二覆盖层可以为单层结构,也可以为多层结构。在本具体实施方式中,以所述第二覆盖层为多层结构为例进行说明。如图2i所示,所述第二覆盖层包括第一保护层36和第二保护层37。所述第一保护层36可以为单层结构,其材料为氮化物材料,例如氮化硅;所述第一保护层36也可为由sin/sicn/sion构成的多层结构。所述第二保护层37的材料为氧化物材料,例如二氧化硅。

74.在形成包括所述第一保护层36和所述第二保护层37的所述第二覆盖层之后,可以再在所述第二覆盖层之上依次形成第三覆盖层381和第四覆盖层382,并通过刻蚀位于所述第二区域ⅱ的所述第四覆盖层382、所述第三覆盖层381和所述第二保护层37,形成贯穿所述第四覆盖层382、所述第三覆盖层381和所述第二保护层37、并暴露所述第一保护层36的第三开口39,如图2j所示。后续可以通过所述第三开口39对所述熔丝35进行熔断。其中,所述第三覆盖层381为单层结构(其材料为硬掩模材料,例如氮化硅或者氮氧化硅),也可以为多层结构。所述第四覆盖层382也可以为单层结构(其材料为有机掩模材料,例如无定形碳),也可以为多层结构。

75.不仅如此,本具体实施方式还提供了一种集成电路装置。本具体实施方式提供的集成电路装置可以采用如图1、图2a-图2j或者图3a-图3b所示的方法形成,所述集成电路装置的具体结构可参见图2i和图2j。如图2i、图2j所示,本具体实施方式提供的集成电路装置,包括:

76.衬底20,所述衬底20包括第一区域ⅰ和位于所述第一区域ⅰ外部的第二区域ⅱ,所述衬底20内部具有位于所述第一区域ⅰ的第一插塞21和位于所述第二区域ⅱ的第二插塞22,所述衬底20表面具有第一覆盖层23和位于所述第一覆盖层23表面的隔离层;

77.第一导电层25,位于所述第一区域ⅰ的所述第一覆盖层23内,且与所述第一插塞21电连接;

78.导电连接层33,位于所述第一导电层25表面;

79.第二导电层34,位于所述导电连接层33表面,所述导电连接层33的一端电连接所述第一导电层25、另一端电连接所述第二导电层34;

80.熔丝35,位于所述第二区域ⅱ,所述熔丝35呈实心柱状结构、并贯穿所述隔离层和所述第一覆盖层23,所述熔丝35的底面与所述第二插塞22电连接、所述熔丝35的顶面与所述第二导电层25的顶面平齐。

81.可选的,所述熔丝35、所述第二导电层34和所述导电连接层33的材料相同。

82.可选的,所述隔离层包括:

83.第一子隔离层26,覆盖于所述衬底20表面;

84.第二子隔离层27,覆盖于所述第一子隔离层26表面,且所述第二子隔离层27的厚度大于所述第一子隔离层26。

85.可选的,所述第二子隔离层27的材料与所述第一覆盖层23的材料相同。

86.可选的,所述集成电路装置还包括:

87.第二覆盖层,覆盖于所述第二导电层34、所述熔丝35和所述隔离层表面。

88.本具体实施方式提供的集成电路装置及其形成方法,在形成第一导电层的过程中,不对用于形成熔丝的第二区域进行处理,在形成导电连接层和第二导电层的过程中同时形成熔丝,使得形成的熔丝呈简单的实心柱状结构,与第一导电层和第二导电层的结构无关,不仅简化了熔丝的结构,使得仅仅只需要较低的能量就可以实现熔丝的熔断,而且简化了整个集成电路装置的制造流程,降低了集成电路装置的制程成本,也提高了集成电路装置的良率。

89.以上所述仅是本发明的优选实施方式,应当指出,对于本技术领域的普通技术人员,在不脱离本发明原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也应视为本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1