半导体结构的制造方法与流程

1.本发明涉及半导体技术领域,具体涉及一种半导体结构的制造方法。

背景技术:

2.现有技术的半导体行业中,缩小器件尺寸,在一定面积内增加器件数量是未来发展方向,目前半导体成像制程中阶跃式缩小线宽的方法主要是自对准双重图形化(self-aligned double patterning,sadp)和自对准四重图形化(self-aligned quadruple patterning,saqp),对于更小器件更多的芯片,关键线宽一直是制约下一代半导体的瓶颈。

技术实现要素:

3.本发明的目的在于提供一种半导体结构的制造方法,能够提高图形化的精度,减小图形线宽,提高集成度。

4.根据本发明实施例的半导体结构的制造方法,包括:提供基底;于该基底上形成第一掩膜图案和第一掩膜开口,第一掩膜开口位于相邻的第一掩膜图案之间;于第一掩膜图案和第一掩膜开口上形成第二掩膜图案和第二掩膜开口,第二掩膜开口位于相邻的第二掩膜图案之间,其中,第二掩膜图案在基底上的投影和第一掩膜图案以及第一掩膜开口在基底上的投影至少部分重叠,且第二掩膜开口在基底上的投影和第一掩膜图案以及所述第一掩膜开口在基底上的投影至少部分重叠;基于第一掩膜图案、第一掩膜开口、第二掩膜图案和第二掩膜开口在基底上形成第一图案和第一开口。

5.根据本发明的一些实施例,利用同一光罩形成第一掩膜图案、第一掩膜开口、第二掩膜图案和第二掩膜开口。

6.根据本发明的一些实施例,半导体结构的制造方法还包括:于第一掩膜图案和第一掩膜开口上形成第一介质层,第一介质层填充第一掩膜开口,且第二掩膜图案和第二掩膜开口位于第一介质层上。

7.可选地,基于第二掩膜图案和第二掩膜开口图形化第一介质层以形成倒l型图案,倒l型图案包括倒l型顶部和倒l型侧部。

8.可选地,基于第一掩膜图案、第一掩膜开口、第二掩膜图案和第二掩膜开口在基底上形成第一图案和第一开口的步骤,包括:去除倒l型顶部上方的第二掩膜图案和倒l型侧部周边的第一掩膜图案;去除倒l型顶部,保留倒l型侧部;利用倒l型侧部刻蚀所述基底,在基底上形成第一图案和所述第一开口。

9.可选地,第一掩膜图案和第二掩膜图案的材质相同;去除倒l型顶部上方的第二掩膜图案和倒l型侧部周边的第一掩膜图案的步骤,包括:在同一刻蚀步骤中同时去除第一掩膜图案和第二掩膜图案。

10.根据本发明的一些实施例,该半导体结构的制造方法还包括:在基底上形成第一掩膜层;所基于所述第一掩膜图案、第一掩膜开口、第二掩膜图案和第二掩膜开口在所述基底上刻蚀基底上形成第一图案和第一开口的步骤,包括:基于第一掩膜图案、第一掩膜开

口、第二掩膜图案和所述第二掩膜开口在第一掩膜层上形成初始第一图案和初始第一开口;形成填充初始第一开口的第二介质层;在第二介质层上形成初始第二图案和初始第二开口;基于初始第一图案、初始第一开口、初始第二图案和初始第二开口在所述基底中形成第一图案和第一开口。

11.可选地,在第二介质层上形成初始第二图案和初始第二开口的步骤,包括:于第二介质层上形成第三掩膜图案和第三掩膜开口,第三掩膜开口位于相邻的第三掩膜图案之间;于第三掩膜图案和第三掩膜开口上形成第四掩膜图案和第四掩膜开口,第四掩膜开口位于相邻的第四掩膜图案之间,其中,第四掩膜图案在基底上的投影和所述第三掩膜图案以及第三掩膜开口在基底上的投影至少部分重叠,且第四掩膜开口在基底上的投影和第三掩膜图案以及第三掩膜开口在基底上的投影至少部分重叠;

12.基于第三掩膜图案、第三掩膜开口、第四掩膜图案和所述第四掩膜开口在第二介质层上形成初始第二图案和初始第二开口。

13.可选地,利用同一光罩形成第三掩膜图案、第三掩膜开口、第四掩膜图案和第四掩膜开口。

14.进一步地,利用同一光罩形成第一掩膜图案、第一掩膜开口、第二掩膜图案和第二掩膜开口、第三掩膜图案、第三掩膜开口、第四掩膜图案和第四掩膜开口。

15.可选地,初始第二图案在基底上的投影位于初始第一开口在基底上的投影的内部;初始第一图案在基底上的投影位于初始第二开口在基底上的投影的内部。

16.根据本发明的一些实施例,半导体结构的制造方法还包括:在基底上重复n次形成第一图案和第一开口的步骤,n为大于等于2的正整数。

17.根据本发明的一些实施例,半导体结构的制造方法还包括:在基底上形成第一掩膜层;基于第一掩膜图案、第一掩膜开口、第二掩膜图案和第二掩膜开口在基底上形成第一图案和第一开口的步骤,包括:基于第一掩膜图案、第一掩膜开口、第二掩膜图案和第二掩膜开口在第一掩膜层上形成初始第一图案和初始第一开口;利用初始第一图案和初始第一开口在基底上形成第一图案和第一开口。

18.根据本发明的一些实施例,半导体结构的制造方法还包括:在基底上重复n次形成第一图案和第一开口的步骤,n为大于等于2的正整数。

19.根据本发明的一些实施例,根据第二掩膜图案和第一掩膜开口在基底上的投影重叠部分大小确定重复次数。

20.根据本发明实施例的半导体结构的制备方法,通过形成第一掩膜图案、第一掩膜开口、第二掩膜图案和第二掩膜开口,且第二掩膜图案在基底上的投影和第一掩膜图案以及第一掩膜开口在基底上的投影至少部分重叠,且第二掩膜开口在基底上的投影和第一掩膜图案以及第一掩膜开口在基底上的投影至少部分重叠,由此通过交叠成像,可控制第一掩膜图案与第二掩膜开口的重叠部分以控制图形的关键线宽尺寸,进而能够获得更小线宽尺寸的图形,提高半导体制程中对线宽的精确控制和半导体结构的集成度。

附图说明

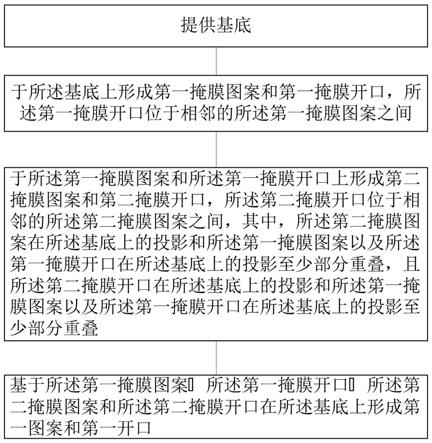

21.图1是根据本发明实施例的半导体结构的制造方法的流程图;

22.图2-图14为根据本发明实施例的半导体结构的制造方法的各步骤的剖面图。

23.附图标记:

24.1:基底,11:第一图案,12:第一开口,13:第一掩膜层,131:初始第一图案,132:初始第一开口;

25.2:第一掩膜图案层,21:第一掩膜图案,22:第一掩膜开口;

26.31:第一光刻胶层,32:第二光刻胶层;

27.4:第二掩膜图案层,41:第二掩膜图案,42:第二掩膜开口;

28.51:第一介质层,52:第二介质层,53:倒l型图案,531:倒l型顶部,532:倒l型侧部;

29.6:第二掩膜层,621:初始第二图案;622:初始第二开口。

具体实施方式

30.以下结合附图和具体实施方式对本发明提出的一种半导体结构的制造方法作进一步详细说明。

31.下面参考附图描述根据本发明实施例的半导体结构的制造方法。

32.如图1所示,根据本发明实施例的半导体结构的制造方法可以包括:提供基底1;于基底1上形成第一掩膜图案21和第一掩膜开口22,第一掩膜开口22位于相邻的第一掩膜图案21之间;于第一掩膜图案21和第一掩膜开口22上形成第二掩膜图案41和第二掩膜开口42,第二掩膜开口42位于相邻的第二掩膜图案41之间,其中,第二掩膜图案41在基底1上的投影和第一掩膜图案21以及第一掩膜开口22在基底1上的投影至少部分重叠,且第二掩膜开口42在基底1上的投影和第一掩膜图案21以及第一掩膜开口22在基底1上的投影至少部分重叠;基于第一掩膜图案21、第一掩膜开口22、第二掩膜图案41和第二掩膜开口42在基底1上形成第一图案11和第一开口12。

33.图2-图13为根据本发明一具体实施例的半导体结构的制造方法的各步骤的工艺流程图。

34.如图2所示,提供基底1,基底1可以为硅(si)基底1、锗(ge)、硅锗(gesi)基底1、或碳化硅基底1(sic);也可以是绝缘体上硅基底1(soi),绝缘体上锗基底1(goi);或者还可以为其它的材料,例如砷化镓等

ⅲ-ⅴ

族化合物。在该基底1上还可设置器件。在基底1上依次形成第一掩膜图案层2和图形化的第一光刻胶层31。具体的,可以采用第一光掩模板进行曝光显影形成图形化的第一光刻胶层31。如图3所示,以图形化的第一光刻胶层31为掩膜对第一掩膜图案层2进行刻蚀,将图形转移到第一掩膜图案层2上,具体可采用干法刻蚀、湿法刻蚀等,通过刻蚀第一掩膜图案层2从而形成第一掩膜图案21和第一掩膜开口22,第一掩膜开口22位于相邻第一掩膜图案21之间,然后去除第一光刻胶层31。

35.可选的,在基底1上还形成第一掩膜层13,所述第一掩膜层13可以为氧化硅、氮化硅或有机碳层等。第一掩膜图案层2和图形化的第一光刻胶层31依次形成在第一掩膜层13上。如图4所示,在第一掩膜图案21和第一掩膜开口22的上方形成第一介质层51,以在第一介质层51上形成第二掩膜图案41和第二掩膜开口42。

36.如图4所示,于第一介质层51上形成第二掩膜图案层4,在第二掩膜图案层4上形成图形化的第二光刻胶层32。以图形化后的第二光刻胶层32为掩膜对第二掩膜图案层4进行刻蚀,将图形转移到第二掩膜图案层4上,具体可采用干法刻蚀、湿法刻蚀等,通过刻蚀第二掩膜图案层4从而形成第二掩膜图案41和第二掩膜开口42,第二掩膜开口42位于相邻第二

掩膜图案41之间,然后去除第二光刻胶层32。

37.如图5所示,在第一掩膜图案21和第一掩膜开口22上形成第二掩膜图案41和第二掩膜开口42,所述第二掩膜开口42位于相邻的所述第二掩膜图案41之间,其中,所述第二掩膜图案41在所述基底1上的投影和所述第一掩膜图案21以及所述第一掩膜开口22在所述基底1上的投影至少部分重叠,且所述第二掩膜开口42在所述基底1上的投影和所述第一掩膜图案21以及所述第一掩膜开口22在所述基底1上的投影至少部分重叠。

38.可选地,可利用同一光罩形成第一掩膜图案21、第一掩膜开口22、第二掩膜图案41和第二掩膜开口42,具体的,可以采用第一光掩模板进行曝光显影形成图形化的第二光刻胶层32。这样第一掩膜图案21的宽度与第二掩膜图案41的宽度相同,第一掩膜开口22的宽度与第二掩膜开口42的宽度相同,其中,第一掩膜图案21和第一掩膜开口22与第二掩膜图案41和第二掩膜开口42并不完全重合,即第二掩膜图案41在基底1上的投影和第一掩膜图案21以及第一掩膜开口22的至少部分重叠,且第二掩膜开口42在基底1上的投影与第一掩膜图案21以及第一掩膜开口22在基底1上的投影至少部分重叠,第二掩膜图案41与第一掩膜图案21重叠的面积或宽度大小可根据实际需要进行设定,采用同一光罩不仅节约成本,也便于对第二掩膜图案41和第二掩膜开口42与第一掩膜图案21和第一掩膜开口22的重叠部分的尺寸进行精确控制。

39.如图6所示,基于第二掩膜图案41和第二掩膜开口42图形化第一介质层51以形成倒l型图案53,该倒l型图案53包括倒l型顶部531和倒l型侧部532。由于第二掩膜图案41与第一掩膜图案21以及第一掩膜开口22在基底1上的投影至少部分重叠,通过第二掩膜图案41和第二掩膜开口42对第一介质层51图形化,剩余的第一介质层51部分位于第一掩膜图案21表面,部分位于第一掩膜开口22内,从而形成倒l型图案53,倒l型顶部531位于第一掩膜图案21的上方,倒l型侧部532位于第一掩膜开口22内。

40.如图7所示,去除倒l型顶部531上方的第二掩膜图案41和倒l型侧部532周边的第一掩膜图案21,即去除第一掩膜图案21和第二掩膜图案41,保留倒l型图案53,具体可采用湿法刻蚀工艺。结合图7和图8所示,对倒l型图案53进行刻蚀,去除倒l型顶部531,保留倒l型侧部532;具体的,可通过控制刻蚀时间仅去除倒l型顶部531而保留倒l型侧部532。由此保留的倒l型侧部532即第二掩膜图案41与第一掩膜开口22的重叠部分。然后可利用倒l型侧部532刻蚀基底1,在基底1上形成第一图案11和第一开口12,即可以倒l型侧部532为掩膜刻蚀基底1,以在基底1上形成第一图案11和第一开口12,具体步骤可以包括:如图7所示,基底1表面形成有第一掩膜层13,以倒l型侧部532为掩膜对第一掩膜层13进行刻蚀,以形成初始第一图案131和初始第一开口132,如图9所示,初始第一图案131和初始第一开口132形成在基底1表面,利用初始第一图案131和初始第一开口132可对基底1进行刻蚀以形成第一图案11和第一开口12。此时第一图案11的宽度即第二掩膜图案41与第一掩膜开口22重叠部分的宽度,通过控制第二掩膜图案41与第一掩膜图案21和第一掩膜开口22的重叠部分的宽度,从而能够精确控制基底1上形成的第一图案11和第一开口12的宽度,进而能够提高图形化的精度,缩小图形线宽,提高集成度。

41.可选地,第一掩膜图案21和第二掩膜图案41的材质相同,由此去除倒l型顶部531上方的第二掩膜图案41和倒l型侧部532周边的第一掩膜图案21的步骤,包括:在同一刻蚀步骤中同时去除第一掩膜图案21和第二掩膜图案41,从而能够简化工艺步骤。

42.进一步地,在基底1上可重复n次形成第一图案11和第一开口12的步骤,n为大于等于2的正整数,从而能够获得线宽更小,集成度更高的半导体结构。

43.结合图9-图14所示为根据本发明一个具体实施例重复上述图形化制程以获的更小线宽半导体结构的剖视图。

44.基于第一掩膜图案21、第一掩膜开口22、第二掩膜图案41和第二掩膜开口42刻蚀基底1形成第一图案11和第一开口12的步骤,包括:基于第一掩膜图案21、第一掩膜开口22、第二掩膜图案41和第二掩膜开口42在第一掩膜层13上形成初始第一图案131和初始第一开口132;形成填充初始第一开口132的第二介质层52;在第二介质层52上形成初始第二图案621和初始第二开口622;基于初始第一图案131、初始第一开口132、初始第二图案621和初始第二开口622在基底1中形成第一图案11和第一开口12。

45.在第二介质层52上形成初始第二图案621和初始第二开口622的步骤可以包括:于第二介质层52上形成第三掩膜图案和第三掩膜开口,第三掩膜开口位于相邻的第三掩膜图案之间;于第三掩膜图案和第三掩膜开口上形成第四掩膜图案和第四掩膜开口,第四掩膜开口位于相邻的第四掩膜图案之间,其中,第四掩膜图案在基底1上的投影和第三掩膜图案以及第三掩膜开口在基底1上的投影至少部分重叠,且第四掩膜开口在基底1上的投影和第三掩膜图案以及第三掩膜开口在基底1上的投影至少部分重叠;基于第三掩膜图案、第三掩膜开口、第四掩膜图案和第四掩膜开口在第二介质层52上形成初始第二图案621和初始第二开口622。

46.其中第三掩膜图案、第三掩膜开口以及第四掩膜图案和第四掩膜开口的形成方法与第一掩膜图案21、第一掩膜开口22以及第二掩膜图案41和第二掩膜开口42的形成方法相同。

47.具体地,如图11所示,在第二介质层52表面形成第二掩膜层6,在第二掩膜层6表面形成第三掩膜图案层和第三光刻胶层,对第三光刻胶层进行图形化,并以图形化后的第三光刻胶层为掩膜以对第三掩膜图案层进行刻蚀,从而形成第三掩膜图案和第三掩膜开口,第三掩膜开口形成在相邻第三掩膜图案之间。

48.于第三掩膜图案表面形成第三介质层,第三介质层覆盖第三掩膜图案表面且填充第三掩膜开口,在第三介质层表面形成第四掩膜图案层和第四光刻胶层,对第四光刻胶层进行图形化,并以图形化后的第四光刻胶层为掩膜以对第四掩膜图案层进行刻蚀,从而形成第四掩膜图案和第四掩膜开口,第四掩膜开口形成在相邻第四掩膜图案之间。

49.如图12所示,基于第三掩膜图案和第三掩膜开口、第四掩膜图案和第四掩膜开口图形化第二掩膜层6,以形成初始第二图案621和初始第二开口622。

50.其中,基于第三掩膜图案和第三掩膜开口以及第四掩膜图案和第四掩膜开口图形化第三介质层的步骤与基于第一掩膜图案21和第一掩膜开口22以及第二掩膜图案41和第二掩膜开口42图形化第一介质层61的步骤相同。

51.具体地,基于第四掩膜图案和第四掩膜开口图形化第三介质层以形成倒l型图案,然后去除第三掩膜图案和第四掩膜图案;去除倒l型顶部,保留倒l型侧部,以倒l型侧部为掩膜图形化第三介质层;然后以图形化后的第三介质层为掩膜刻蚀第二掩膜层6以形成初始第二图案621和初始第二开口622。可选地,为了节约成本,可利用同一光罩形成第三掩膜图案、第三掩膜开口、第四掩膜图案和第四掩膜开口,进一步地,第一掩膜图案、第一掩膜开

口、第二掩膜图案和第二掩膜开口、第三掩膜图案、第三掩膜开口、第四掩膜图案和第四掩膜开口均可采用同一光罩形成。

52.如图13和图14所示,利用初始第二图案621和初始第二开口622刻蚀第二介质层52以形成图形化的第二介质层52,利用初始第一图案131、初始第一开口132以及图形化的第二介质层52在基底1中形成第一图案11和第一开口12。

53.如图13所示,初始第二图案621在基底1上的投影位于初始第一开口132在基底1上的投影的内部;初始第一图案131在基底1上的投影位于初始第二开口622在基底1上的投影的内部,由此可以第一掩膜图案21和第二掩膜图案41为掩膜图形对基底1进行刻蚀,以在基底1形成第一图案11和第一开口12,从而使得第一图案11的线宽和第一开口12的尺寸较小,以达到进一步地缩小第一开口12的目的,实现进一步缩小器件半导体器件尺寸。

54.在基底1上可重复n次上述实施例形成第一图案11和第一开口12的步骤,n为大于等于2的正整数,从而能够获取更小线宽的图形。

55.可选地,根据第二掩膜图案41和第一掩膜开口22在基底1上的投影重叠部分大小确定线宽的大小和重复次数,其中第二掩膜图案41和第一掩膜开口22在基底1上投影的重叠部分的大小即线宽的大小,重复次数越多,最终获得半导体结构的线宽越小,图形化精度更高。

56.以上所述仅是本发明的优选实施方式,应当指出,对于本技术领域的普通技术人员,在不脱离本发明原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也应视为本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1