一种碳化硅MOS器件的制作方法

一种碳化硅mos器件

技术领域

[0001]

本发明涉及半导体技术领域,具体涉及一种碳化硅mos器件。

背景技术:

[0002]

碳化硅mosfet器件是以宽禁带半导体材料碳化硅制造的下一代半导体器件。碳化硅材料诸多吸引人的特性,如10倍于硅材料的临界击穿电场强度、高的热导率、大的禁带宽度以及高电子饱和漂移速度等,使sic材料成为了国际上功率半导体器件的研究热点,并在高功率应用场合,如高速铁路、混合动力汽车、智能高压直流输电等,碳化硅器件均被赋予了很高的期望。同时碳化硅功率器件对功率损耗的降低效果显著,使得碳化硅功率器件被誉为带动“新能源革命”的“绿色能源”器件。然而,因mos沟道的不理想导致mos沟道迁移率过低,极大地限制了碳化硅mosfet通态电流密度。因此,具有更高沟道密度、从而具有更大通态电流密度的碳化硅umosfet受到的广泛关注和研究。尽管碳化硅umosfet具有更低通态电阻以及更紧凑的元胞布局,由于底部栅氧化层电场过高的问题,给碳化硅umosfet长久使用带来可靠性问题,造成器件长期稳定性差。

[0003]

现有技术中在设置栅氧化层的过程中往往采用横向设置的方式,此种设置方式会增长电流流通路径,从而使得导通电阻更大。

技术实现要素:

[0004]

本发明所要解决的问题是:提供一种碳化硅mos器件,将栅氧化层设置为纵向,嵌入到碳化硅体内,导通时,电流纵向流动,电流路径更短,因此导通电阻更低,电流能力更强。另一方面,同时也可以节省器件面积,提高单位面积内的器件个数,降低了生产成本。

[0005]

本发明为解决上述问题所提供的技术方案为:一种碳化硅mos器件,包括金属漏极,所述金属漏极的上端面设有漏电极,所述漏电极的上端面设有n+型碳化硅衬底,所述n+型碳化硅衬底的上端面设置有n型碳化硅漂移区,所述n型碳化硅漂移区的上端面生长有碳化硅n-外延层;所述碳化硅n-外延层左上方和右上方均具有源极沟槽,所述源极沟槽下方自上而下具有碳化硅p+掺杂区以及碳化硅p型掺杂区;所述碳化硅p+掺杂区以及碳化硅p型掺杂区的上端设有肖特基接触金属;所述碳化硅n-外延层的上端面设有源极金属,所述碳化硅n-外延层和源极金属上设有贯穿的槽,所述槽的内壁以及外表面设有栅氧化层,所述槽内设有栅极低阻淀积物;所述槽的顶端自下而上依次设有栅氧化层、栅极低阻淀积物、栅极金属。

[0006]

优选的,所述碳化硅p型掺杂区的深度为0.6μm,掺杂浓度为3

×

1018cm-3。

[0007]

优选的,所述碳化硅p+掺杂区的深度为0.3μm,掺杂浓度为1

×

1019cm-3。

[0008]

优选的,所述金属漏极的总厚度大于1μm,且所述金属漏极为由金属材料为tiniag、vniag、tiniau、vniau中的一种或任意几种组合而成的淀积层。

[0009]

优选的,所述碳化硅n-外延层的电阻率80-200ω*cm,该外延层掺杂元素为氮原子。

[0010]

优选的,所述栅极低阻淀积物为低阻多晶硅、金属钨、金属钛、氧化钛。

[0011]

与现有技术相比,本发明的优点是:

[0012]

1、本发明将栅氧化层设置为纵向,嵌入到碳化硅体内,导通时,电流纵向流动,电流路径更短,因此导通电阻更低,电流能力更强。另一方面,同时也可以节省器件面积,提高单位面积内的器件个数,降低了生产成本。

[0013]

2、由于双深碳化硅p型掺杂区对于器件耐压的提升,使得掺杂能够有效提高,故本发明具有较低的比导通电阻,另外,所集成多子整流器件具有漏电低的特点。

附图说明

[0014]

此处所说明的附图用来提供对本发明的进一步理解,构成本发明的一部分,本发明的示意性实施例及其说明用于解释本发明,并不构成对本发明的不当限定。

[0015]

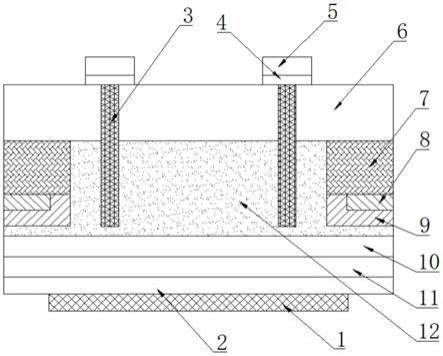

图1是本发明的整体结构示意图;

[0016]

附图标注:1、金属漏极,2、漏电极,3、栅氧化层,4、栅极低阻淀积物,5、栅极金属,6、源极金属,7、肖特基接触金属,8、碳化硅p+掺杂区,9、碳化硅p型掺杂区,10、n型碳化硅漂移区,11、n+型碳化硅衬底,12、碳化硅n-外延层。

具体实施方式

[0017]

以下将配合附图及实施例来详细说明本发明的实施方式,借此对本发明如何应用技术手段来解决技术问题并达成技术功效的实现过程能充分理解并据以实施。

[0018]

本发明的具体实施例如图1所示,一种碳化硅mos器件,包括金属漏极,所述金属漏极的上端面设有漏电极,所述漏电极的上端面设有n+型碳化硅衬底,所述n+型碳化硅衬底的上端面设置有n型碳化硅漂移区,所述n型碳化硅漂移区的上端面生长有碳化硅n-外延层;所述碳化硅n-外延层左上方和右上方均具有源极沟槽,所述源极沟槽下方自上而下具有碳化硅p+掺杂区以及碳化硅p型掺杂区;所述碳化硅p+掺杂区以及碳化硅p型掺杂区的上端设有肖特基接触金属;所述碳化硅n-外延层的上端面设有源极金属,所述碳化硅n-外延层和源极金属上设有贯穿的槽,所述槽的内壁以及外表面设有栅氧化层,所述槽内设有栅极低阻淀积物;所述槽的顶端自下而上依次设有栅氧化层、栅极低阻淀积物、栅极金属。

[0019]

在本实施例中,所述碳化硅p型掺杂区的深度为0.6μm,掺杂浓度为3

×

1018cm-3。

[0020]

在本实施例中,所述碳化硅p+掺杂区的深度为0.3μm,掺杂浓度为1

×

1019cm-3。

[0021]

在本实施例中,所述金属漏极的总厚度大于1μm,且所述金属漏极为由金属材料为tiniag、vniag、tiniau、vniau中的一种或任意几种组合而成的淀积层。

[0022]

在本实施例中,所述碳化硅n-外延层的电阻率80-200ω*cm,该外延层掺杂元素为氮原子。

[0023]

在本实施例中,所述栅极低阻淀积物为低阻多晶硅、金属钨、金属钛、氧化钛。

[0024]

以上仅就本发明的最佳实施例作了说明,但不能理解为是对权利要求的限制。本发明不仅局限于以上实施例,其具体结构允许有变化。凡在本发明独立权利要求的保护范围内所作的各种变化均在本发明保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1