ONO侧墙的工艺方法与流程

ono侧墙的工艺方法

[0001]

技术领域

[0002]

本发明涉及半导体领域,特别是指一种ono侧墙的工艺方法。

背景技术:

[0003]

亚微米集成电路制造中,侧墙工艺定义了源漏轻掺杂区域,其宽度对短沟道器件的阈值电压、漏电流和饱和电流有重要影响。

[0004]

ono 侧墙是一种应用非常广泛的侧墙形成工艺。如图1中左图所示,中间为栅极(gate),栅极外包裹的第一层(靠里层)为一层较薄lpteos(低压teos),约150

å

。第二层为lpsin(lpcvd工艺形成的氮化硅),厚度约为300

å

。第三层(靠外层)为较厚lpteos,厚度范围400~1000

å

。

[0005]

ono 侧墙刻蚀完成后,“l”型sin横向宽度和第一层lpteos在多晶硅侧壁的厚度合起来构成侧墙宽度。如图1中右图所示。其中“l”型sin横向宽度本质上由最上层teos膜层在侧壁上的厚度决定,但由于在这一层teos过刻蚀阶段,会有对teos的横向刻蚀,因此侧墙宽度受过刻蚀时间影响很大。

[0006]

亚微米集成电路中,ono侧墙最外层teos的厚度,已经与多晶硅栅条之间的间距处于同一数量级。在多晶硅栅密集条区和疏区,填充效应开始出现。疏区侧壁toes淀积厚度大于密集区。因而最终侧墙宽度也是疏区宽度大于密集区宽度,如图2所示。

[0007]

栅密集区与疏区的侧墙宽度差异,会降低良率窗口。并且这种差异无法通过opc(光学邻近修正 (optical proximity correction,opc)技术进行补偿。

[0008]

侧墙宽度具有随栅间距减小而减小的趋势,如图3所示。主要在小间距区,侧墙宽度减小很快,与疏区差异比较大。

技术实现要素:

[0009]

本发明所要解决的技术问题在于提供一种ono侧墙的工艺方法,减小多晶硅密集区与疏区侧墙厚度差异的问题。

[0010]

为解决上述问题,本发明所述的ono侧墙的工艺方法,在晶圆上形成晶体管,晶体管的分布不均形成多晶硅栅条的密集区及疏区;在淀积形成栅极的ono侧墙时,淀积完最里层氧化层及中间层氮化层之后,增加最外层氧化层的厚度,然后再进行刻蚀。

[0011]

进一步的改进是,所述最下层氧化层为lpteos工艺形成,中间层为lpcvd工艺形成的氮化硅层,第三层为lpteos工艺形成。

[0012]

进一步的改进是,所述最里层氧化层的厚度为150

å

,中间层氮化层厚度为300

å

,最外层氧化层的厚度为400~1000

å

。

[0013]

进一步的改进是,所述最外层氧化层的厚度,其厚度下限需要至少满足在多晶硅栅条的密集区,保证淀积厚度使多晶硅栅条顶部的最外层氧化物能与相邻的多晶硅栅条上

淀积的最外层氧化物能够连成一体;所述最外层氧化层的厚度上限是最外层氧化物过刻蚀完成之后多晶硅栅条之间最小间距处没有残留的teos。

[0014]

进一步的改进是,所述最外层氧化层厚度增加导致侧墙的宽度增加,需要通过增加teos过刻蚀的时间来进行补偿。

[0015]

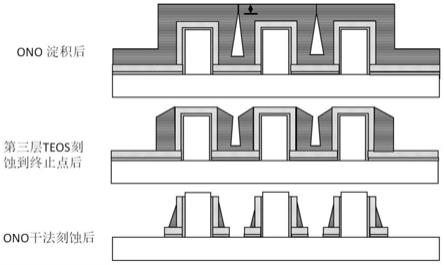

本发明所述的ono侧墙的工艺方法,通过增加第三层,也就是最外层的teos厚度,使得最小硅栅间距处,toes层能够连接起来。刻蚀开始后,疏区的teos正常刻蚀。密集区需要先刻蚀顶部连接起来的teos。刻完顶部teos后,硅栅侧壁的teos才会被刻蚀到,这样疏区多晶硅栅侧壁teos经受横向刻蚀的时间,要多于密集区的teos,从而平衡了疏区横向厚度大于密集区横向厚度的差异,侧墙中间层sin的宽度其实由teos的横向厚度决定,最终减小了密集区和疏区的侧墙宽度差异。

附图说明

[0016]

图1 是常规的ono侧墙膜层淀积之后以及刻蚀之后的示意图。

[0017]

图2 是现有的ono侧墙形成工艺示意图。

[0018]

图3 是栅极间距与侧墙厚度的关系曲线图。

[0019]

图4 是本发明ono侧墙形成工艺示意图。

[0020]

图5 是最外层teos厚度过大导致刻蚀不完全形成侧墙连接的示意图。

具体实施方式

[0021]

本发明用于亚微米集成电路制造中使用ono结构作为侧墙的工艺,所述的ono侧墙的工艺方法,结合附图说明如下:在晶圆上制作形成晶体管后,由于芯片布局的原因,晶体管的分布不均匀,晶体管的多晶硅栅极,以及连接多晶硅栅极形成的多晶硅栅条构成了多晶硅栅条的密集区及疏区。首先使用传统工艺形成第一层,也就是最里层的氧化层,一般基于lpteos工艺形成,淀积厚度为150

å

,再淀积第二层,也就是中间层氮化硅层,采用lpcvd工艺,形成厚度为300

å

。因此,淀积ono侧墙的第一层及中间层与传统工艺无异,在淀积形成栅极的ono侧墙的最外层时,增加最外层氧化层的厚度,然后再进行刻蚀。

[0022]

增加最外层氧化层的厚度需要满足其厚度下限及上限的要求:其厚度下限需要至少满足在多晶硅栅条的密集区,保证淀积厚度使多晶硅栅条顶部的最外层氧化物能与相邻的多晶硅栅条上淀积的最外层氧化物能够连成一体;所述最外层氧化层的厚度上限是最外层氧化物过刻蚀完成之后多晶硅栅条之间最小间距处没有残留的teos。

[0023]

如图3所示,淀积完厚度增加的第三层teos之后,在密集区多晶硅栅条顶部的teos层会形成类似封口的效果,使得相邻的多晶硅栅条顶部的teos层连成一个整体,结合上述的厚度上限,通过控制合适的厚度完成最上层teos的淀积。

[0024]

刻蚀开始后,疏区的teos正常刻蚀。密集区需要先刻蚀顶部连接起来的teos。刻完顶部teos后,硅栅侧壁的teos才会被刻蚀到,这样疏区多晶硅栅侧壁teos经受横向刻蚀的时间,要多于密集区的teos,利用teos填充在密集区多晶硅栅间距顶部

ꢀ“

封口”的特点,造成密集区和疏区侧壁teos经受不同的刻蚀时间,侧墙中间层sin的宽度其实由teos的横向

厚度决定,最终减小了密集区和疏区的侧墙宽度差异。

[0025]

最外层氧化层的厚度增加之后,会导致侧墙的宽度增加,需要通过增加teos过刻蚀的时间来进行补偿。

[0026]

如果最外层teos层淀积厚度过大,会导致过刻蚀无法满足密集区的ono层刻蚀干净,会导致刻蚀后侧墙仍保持相连,如图5所示,因此必须控制最上层teos层淀积的厚度上限。

[0027]

本发明所述的ono侧墙的工艺方法,通过增加最外层的teos厚度,使得最小硅栅间距处,toes层能够连接起来,造成密集区和疏区侧壁teos经受不同的刻蚀时间,平衡密集区和疏区teos侧向厚度的差异。

[0028]

以上仅为本发明的优选实施例,并不用于限定本发明。对于本领域的技术人员来说,本发明可以有各种更改和变化。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1