存储器装置的制作方法

1.本发明是有关于一种存储器装置,且特别是有关于一种三维存储器装置。

背景技术:

2.近年来,存储器装置的尺寸已逐渐缩小。在存储器技术中,特征尺寸的缩小、速度、效能、密度与每单位集成电路的成本的改良皆为相当重要的目标。在实际应用上,装置尺寸缩小的同时,仍须保持装置的电性以符合商业需求。

技术实现要素:

3.本发明有关于一种存储器装置。

4.根据本发明的一方面,提出一种存储器装置。存储器装置包括一叠层结构及至少一个第一元件结构。叠层结构在一存储器阵列区与一阶梯状接触区中,并包括排列在一纵方向上的多个第一导电层与一第二导电层。存储器阵列区与阶梯状接触区排列在一第一横方向上。至少一个第一元件结构沿纵方向穿过这些第一导电层与第二导电层。这些第一导电层环绕至少一个第一元件结构的侧壁表面。第二导电层包括排列在一第二横方向上的多个导电部,这些导电部通过至少一个第一元件结构彼此完全分开。第一横方向不同于第二横方向。

5.为了对本发明的上述及其他方面有更好的了解,下文特举实施例,并配合所附附图详细说明如下:

附图说明

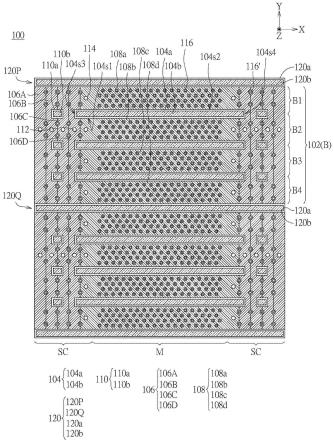

6.图1a绘示根据一实施例的存储器装置的俯视图。

7.图1b绘示图1a的存储器装置的叠层结构的立体示意图。

8.图1c绘示图1a的存储器装置的第一导电层及对应第一导电层的其他元件的横向剖面图。

9.图2绘示一比较例中存储器装置对应一个存储区块部分的俯视图。

10.图3至图7绘示根据一实施例的存储器装置的制造方法。

11.【符号说明】

12.100:存储器装置

13.102:叠层结构

14.104:第一元件结构

15.104a:绝缘墙

16.104b:导电元件

17.104s1:第一侧壁表面

18.104s2:第二侧壁表面

19.104s3:第三侧壁表面

20.104s4:第四侧壁表面

21.106,106a~106d:第一导电层

22.108:第二导电层

23.108a~108d:导电部

24.110:第二元件结构

25.110a:绝缘墙

26.110b:导电元件

27.112:导电柱

28.114:接触柱

29.116,116

′

:柱元件

30.116a:通道柱

31.116b:存储材料层

32.120,120p,120q:第三元件结构

33.120a:绝缘墙

34.120b:导电元件

35.204:介电元件

36.222:导电元件

37.402:叠层结构

38.416,416

′

:柱元件

39.416a:通道柱

40.416b:存储材料层

41.418:绝缘层

42.432:衬底

43.434:绝缘膜

44.438,440,442:开口

45.502:叠层结构

46.536:狭缝

47.606,606a~606d:第一导电层

48.608:第二导电层

49.608a~608d:导电部

50.704a,710a,720a:绝缘墙

51.704c,710c,720c:开口

52.804b,810b,820b:导电元件

53.b:区块

54.b1~b4:次区块

55.gsl:接地选择线

56.ssl:串列选择线

57.wl:字线

58.m:存储器阵列区

59.sc:阶梯状接触区

60.x:第一横方向

61.y:第二横方向

62.z:纵方向

具体实施方式

63.以下系以一些实施例做说明。须注意的是,本发明并非显示出所有可能的实施例,未于本发明提出的其他实施例也可能可以应用。再者,附图上的尺寸比例并非按照实际产品等比例绘制。因此,说明书和图示内容仅作叙述实施例之用,而非作为限缩本发明保护范围之用。另外,实施例中的叙述,例如局部结构、工艺步骤和材料应用等等,仅为举例说明之用,并非对本发明欲保护的范围做限缩。实施例的步骤和结构各自细节可在不脱离本发明的精神和范围内根据实际应用工艺的需要而加以变化与修饰。以下是以相同/类似的符号表示相同/类似的元件做说明。

64.说明书与请求项中所使用的序数例如「第一」、「第二」、「第三」等的用词,以修饰权利要求的元件,其本身并不意含及代表此元件有任何之前的序数,也不代表某一元件与另一元件的顺序、或是制造方法上的顺序,这些序数的使用仅用来使具有某命名的一元件得以和另一具有相同命名的元件能作出清楚区分。

65.图1a绘示根据一实施例的存储器装置100的俯视图。图1b绘示图1a的存储器装置100的叠层结构102的立体示意图。

66.请参照图1a及图1b。存储器装置100可包括叠层结构102及第一元件结构104。举例而言,存储器装置100可包括与非门闪存(nand flash memory)。

67.叠层结构102在一存储器阵列区m与一阶梯状接触区sc中,且存储器阵列区m与阶梯状接触区sc排列在一第一横方向x上。叠层结构102包括在一纵方向z(例如垂直方向)上交错叠层在衬底432(如图1b及图3所示)上的导电层与绝缘层(如图4所示,绝缘层418)。导电层包括第一导电层106(例如第一导电层106a~106d)与一第二导电层108。第二导电层108在第一导电层106上方。举例而言,衬底432可包括半导体材料,例如硅或多晶硅(poly-silicon),但本发明不以此为限。叠层结构102的下阶层(lower level)(或阶梯状接触区sc中叠层结构102的下阶梯阶层(lower stair level))可包括一第一导电层106与一绝缘层418在第一导电层106下方。叠层结构102的上阶层(upper level)(或阶梯状接触区sc中叠层结构102的上阶梯阶层(upper stair level))可包括一第二导电层108与一绝缘层418在第二导电层108下方。

68.第一元件结构104延伸在第一横方向x上。第一元件结构104可包括一绝缘墙104a及一导电元件104b。绝缘墙104a具有封闭的矩形状,且绝缘墙104a环绕导电元件104b。导电元件104b通过绝缘墙104a电性绝缘第一导电层106a~106d与第二导电层108。一实施例中,导电元件104b可用作一共同源极线(csl)。举例而言,导电元件104b可包括导电材料,例如钨(w),但本发明不以此为限。

69.第一元件结构104的绝缘墙104a包括一第一侧壁表面104s1、一第二侧壁表面104s2、一第三侧壁表面104s3及一第四侧壁表面104s4。第二侧壁表面104s2相对于第一侧壁表面104s1。第三侧壁表面104s3在第一侧壁表面104s1与第二侧壁表面104s2之间。第四

侧壁表面104s4相对于第三侧壁表面104s3,且第四侧壁表面104s4在第一侧壁表面104s1与第二侧壁表面104s2之间。

70.绝缘层418(如图4所示)环绕第一元件结构104的侧壁表面。绝缘层418可环绕第一元件结构104的绝缘墙104a的第一侧壁表面104s1、第二侧壁表面104s2、第三侧壁表面104s3及第四侧壁表面104s4。

71.第二导电层108包括排列在第二横方向y上的导电部(例如导电部108a~108d)。导电部108a~108d通过第一元件结构104彼此完全分开。导电部(例如导电部108a~108d)位于第一导电层106(例如第一导电层106a~106d)的上方。第一横方向x可实质上垂直于第二横方向y。

72.第一导电层106包括多个字线(wl)及一接地选择线(gsl)。一实施例中,第一导电层106a用作接地选择线,第一导电层106b~106d用作字线,且第二导电层108的导电部(例如导电部108a~108d)用作串列选择线(ssl)。用作字线的第一导电层106b~106d位于用作接地选择线的第一导电层106a与用作串列选择线的导电部108a~108d之间。附图虽仅显示出3层字线(第一导电层106b~106d),但本发明不限于此,接地选择线(第一导电层106a)与串列选择线(导电部)之间可配置其它更多数目的字线。

73.第一元件结构104沿纵方向z穿过存储器阵列区m的第一导电层106、第二导电层108与绝缘层418。第一元件结构104可延伸至部分的阶梯状接触区sc,在纵方向z上穿过部分的阶梯状接触区sc的第一导电层106与绝缘层418。

74.图1c绘示图1a的存储器装置100的第一导电层106d及对应第一导电层106d的其它元件的横向剖面图。

75.请参照图1a至图1c。第一导电层106环绕第一元件结构104的侧壁表面。第一导电层106可环绕第一元件结构104的第一侧壁表面104s1、第二侧壁表面104s2、第三侧壁表面104s3及第四侧壁表面104s4。第一导电层106(例如第一导电层106a~106d)直接接触绝缘墙104a的第一侧壁表面104s1、第二侧壁表面104s2、第三侧壁表面104s3及第四侧壁表面104s4。

76.第二导电层108的导电部108a、108b分别在第一元件结构104的第二侧壁表面104s2与第一侧壁表面104s1上。

77.请参照图1a及图1b。一实施例中,存储器装置100可选择性地包括第二元件结构110。另一实施例中,存储器装置100可省略第二元件结构110。

78.第二元件结构110可包括一绝缘墙110a及一导电元件110b。第二元件结构110位于阶梯状接触区sc中。第一元件结构104系分离于第二元件结构110。第二元件结构110沿纵方向z穿过阶梯状接触区sc中的第一导电层106a~106c与绝缘层418。绝缘墙110a具有封闭的矩形状,且绝缘墙110a环绕导电元件110b。第二元件结构110的导电元件110b通过绝缘墙110a电性绝缘第一导电层106。举例而言,导电元件110b可包括导电材料,例如钨(w),但本发明不以此为限。

79.请参照图1a及图1b。存储器装置100可还包括导电柱112及接触柱114。

80.导电柱112及接触柱114位于阶梯状接触区sc之中。导电柱112电性连接在第一导电层106上。接触柱114电性连接在第二导电层108的导电部(例如导电部108a~108d)上。导电柱112的纵向尺寸系大于接触柱114的纵向尺寸。电性连接第二导电层108的接触柱114的

数量可不同于导电柱112中电性连接一个第一导电层106(例如第一导电层106a~106d其中一个第一导电层)的部分的数量。一实施例中,电性连接第二导电层108的接触柱114的数量(例如于图1a、图1b所示,数量为4个)可大于电性连接一个第一导电层106的导电柱112的数量(例如于图1a、图1b所示,导电柱数量为1个)。另一实施例中,电性连接一个第一导电层106的导电柱112的数量亦可为其他合适的数量。

81.根据本实施例,由于电性连接一个第一导电层106(例如第一导电层106a~106d其中一个第一导电层)的导电柱112的数量系小于电性连接第二导电层108的接触柱114的数量,可进一步减少导电柱112的数量,从而具有工艺简化、降低制造成本等优点。

82.请参照图1a及图1b。存储器装置100可还包括柱元件116及柱元件116

′

。

83.柱元件116位于存储器阵列区m之中。柱元件116可包括一通道柱116a及一存储材料层116b,且存储材料层116b位于通道柱116a的侧壁表面上。柱元件116可在纵方向z上穿过叠层结构102至最底阶层。通道柱116a的上端可电性连接至位线(bl)。通道柱116a的下端可经过衬底432电性连接至共同源极线(csl)。通道柱116a亦可称为主动柱(active pillar)。通道柱116a位于存储器阵列区m之中,且穿过叠层结构102。多个存储单元定义在用作字线的第一导电层106(例如第一导电层106b~106d)与通道柱116a的交错处的存储材料层116b中。

84.柱元件116

′

位于阶梯状接触区sc之中。柱元件116

′

可包括一通道柱及一存储材料层,且存储材料层位于通道柱的侧壁表面上。柱元件116

′

可在纵方向z上穿过叠层结构102至最底阶梯层。柱元件116

′

(通道柱)可为电性浮接,并用作虚置柱元件(dummy pillar element)。一实施例中,柱元件116

′

的材料组合系相同于柱元件116的材料组合。另一实施例中,柱元件116

′

的材料组合系不同于柱元件116的材料组合。

85.请参照图1a及图1b。存储器装置100可还包括第三元件结构120(例如第三元件结构120p与第三元件结构120q)。

86.第三元件结构120可包括一绝缘墙120a及一导电元件120b。第三元件结构120沿第一横方向x穿过存储器阵列区m与阶梯状接触区sc。绝缘墙120a具有封闭的矩形状,且绝缘墙120a环绕导电元件120b。导电元件120b通过绝缘墙120a电性绝缘第一导电层106a~106d与第二导电层108。

87.一个区块(one block)b(或者,一个存储区块(one memory block))的多个存储单元位于第三元件结构120p与第三元件结构120q之间的存储器阵列区m中的叠层结构102中。一个区块b的存储单元可由对应的一个字线驱动器(未显示)选择或控制,或同时进行擦除。图1a显示两个存储区块。图1b显示一个存储区块。

88.一个区块b包括多个次区块(sub-blocks)(例如4个次区块b1~b4)的多个存储单元。次区块b1~b4的存储单元分别在第一元件结构104的两侧。一个次区块(或者,一个次存储区块)的存储单元可由对应的一个串列选择线(导电部108a~108d其中一个)控制选择/未选择。举例而言,导电元件120b可包括导电材料,例如钨(w),但本发明不以此为限。

89.第一元件结构104在第一横方向x上的长度系小于第三元件结构120在第一横方向x上的长度。第二元件结构110在第一横方向x上的长度系小于第三元件结构120在第一横方向x上的长度。

90.请参照图2,其绘示一比较例中存储器装置对应一个存储区块部分的俯视图。介电

元件204延伸穿过存储器阵列区m与阶梯状接触区sc中叠层结构的接地选择线gsl、字线wl、与对应于次存储区块的串列选择线ssl。通过介电元件204彼此电性绝缘的字线wl与接地选择线gsl上各具有一个导电柱112。电性连接相同阶层的字线wl(或接地选择线gsl)的导电柱112是通过延伸在介电元件204上方的导电元件222(包括例如金属层,例如第零层金属层(ml0))彼此电性连接。如图2所示的比较例中,对应于一个存储区块的相同阶层的字线wl(或接地选择线gsl)上的导电柱112的数量为4个,等于电性连接串列选择线ssl的接触柱114的数量(即4个)。

91.相较于比较例,本发明的实施例中,对应于一个存储区块的存储器装置,其电性连接其中一个第一导电层106(即一个字线或一个接地选择线)上的导电柱112的数量(例如于图1a、图1b所示,数量为1个)少于电性连接第二导电层108(串列选择线)的接触柱114的数量(例如于图1a、图1b所示,数量为4个)。换句话说,对应于一个存储区块的存储器装置可具有较少数量的导电柱112。此外,本发明的实施例中,并不需要如比较例延伸在介电元件204上方、用以电性连接在相同阶层的字线wl的导电元件222。因此,本发明的实施例的存储器装置可具有较简单的工艺、较大的工艺窗(1arger process window)、较低的制造成本。

92.图3至图7绘示根据一实施例的存储器装置的制造方法。

93.请参照图3。在一衬底432上交错叠层绝缘层418与绝缘膜434以形成叠层结构402。举例而言,衬底432可包括半导体材料,例如硅或多晶硅(poly-silicon),但本发明不以此为限。一实施例中,绝缘层418的材质系不同于绝缘膜434的材质。绝缘层418可包括氧化物,例如氧化硅,但本发明不以此为限。绝缘膜434可包括氮化物,例如氮化硅,但本发明不以此为限。绝缘层418与绝缘膜434亦可使用其它绝缘材质。可利用黄光光刻刻蚀方式从叠层结构402的顶表面削减阶梯状接触区sc的厚度。一实施例中,可形成绝缘元件(可包括氧化物,例如氧化硅,未绘示)在叠层结构402的存储器阵列区m与阶梯状接触区sc上。可进行例如化学机械研磨步骤将叠层结构402上的绝缘元件(未绘示)平坦化。

94.一实施例中,形成柱元件416与柱元件416

′

分别穿过叠层结构402的存储器阵列区m与阶梯状接触区sc。柱元件416与柱元件416

′

亦可穿过叠层结构402上的绝缘元件(未绘示)。另一实施例中,柱元件416与柱元件416

′

的形成方法可包括利用黄光光刻刻蚀步骤形成开孔于叠层结构402与绝缘元件(未绘示)中,然后以合适的柱材料填充开孔。柱元件416与柱元件416

′

可同时形成,并可包括通道柱416a与存储材料层416b。存储材料层416b形成在开孔的侧壁表面上。存储材料层416b可包括任意的电荷捕捉结构,例如一氧化物-氮化物-氧化物(ono)结构、onono结构、ononono结构、或一氧化物-氮化物-氧化物-氮化物-氧化物(be-sonos)结构等。举例而言,电荷捕捉层可使用氮化物(例如氮化硅),或是其他类似的高介电常数物质包括金属氧化物,例如三氧化二铝(al2o3)、氧化锆(hfo2)等。通道柱416a形成在开孔中。又一实施例中,柱元件416与柱元件416

′

可使用不同的工艺步骤分开形成。柱元件416与柱元件416

′

可使用不同的材料组合。

95.一实施例中,可利用黄光光刻刻蚀方式在叠层结构402中形成开口438及开口442,并且,在阶梯状接触区sc中的叠层结构402中形成开口440。开口438与开口440的底部可露出衬底432的上表面。

96.请参照图4。可进行选择性刻蚀步骤移除叠层结构502的存储器阵列区m与阶梯状接触区sc的绝缘膜434(可包括氮化物,例如氮化硅),从而形成狭缝536在绝缘层418(可包

括氧化物,例如氧化硅)之间。一实施例中,刻蚀步骤可包含湿法刻蚀方式,例如使用热磷酸等合适的方法。狭缝536露出柱元件416与柱元件416

′

的侧壁表面。露出狭缝536的柱元件416与柱元件416

′

可稳固支撑曝露出的绝缘层418。

97.请参照图5。一实施例中,填充导电材料(可包括例如钨)于狭缝536中,以形成导电层,包括第一导电层606(例如包括第一导电层606a~606d)及第二导电层608(例如包括导电部608a~608d)。另一实施例中,沉积一氧化物(例如是氧化铝(al2o3))于狭缝536中,接着以导电材料(可包括例如钨)填充狭缝536,以形成导电层,包括第一导电层606(例如包括第一导电层606a~606d)及第二导电层608(例如包括导电部608a~608d)。

98.请参照图6。形成绝缘材料于开口438、开口440及开口442的侧壁表面上,以分别形成绝缘墙704a、绝缘墙710a、绝缘墙720a。举例而言,绝缘墙704a、绝缘墙710a及绝缘墙720a可包括氧化物,例如氧化硅,但本发明不以此为限。

99.请参照图7。填充导电材料在绝缘墙704a、绝缘墙710a、绝缘墙720a所环绕的开口704c、开口710c及开口720c内,以分别形成导电元件804b、导电元件810b及导电元件820b。

100.请参照图1a及图1b。形成导电柱112及接触柱114,分别着陆在第一导电层106(例如第一导电层106a~106d)及第二导电层108上。导电柱112及接触柱114可穿过阶梯状接触区sc上方的绝缘元件(未绘示)。导电柱112与接触柱114可利用包含以黄光光刻刻蚀工艺形成孔洞,然后以导电材料填充孔洞的方法形成。

101.至此,已经结合附图对本公开实施例进行了详细描述。

102.以上所述的具体实施例,对本发明的目的、技术方案和有益效果进行了进一步详细说明,所应理解的是,以上所述仅为本发明的具体实施例而已,并不用于限制本发明,凡在本发明的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1