一种双向低压静电浪涌全芯片保护集成电路的制作方法

1.本发明涉及集成电路的静电放电及浪涌防护领域,具体涉及一种双向低压静电浪涌全芯片保护集成电路。

背景技术:

2.静电放电(esd)或浪涌(eos)是造成集成电路内部损坏及电子产品功能失效的主要原因。由于电路(ic)系统集成度日益复杂,ic内部电路的工作电压以及信号传输速率区别较大,尤其伴随集成电路工艺的日益改进,射频ic(rfic)的工作电压变化区间日益缩小,信号传输速度大幅上升,rfic的这些电学特性变化导致其对eos/esd防护要求更高。同时,esd/eos防护电路的性能对工艺制备尺寸非常敏感,这又进一步增大了rfic的esd防护设计难度。

3.通信电子产品的内部电路单元如存储器、显示屏幕和网络接口等都要各自的工作电源,且数据传输速率快,这些电路单元在上电、断电以及状态转变过程中,均可能会受到esd/eos干扰信号的影响。为提高这些电路单元的系统功能稳定性及可靠性,通常需要对风险端口建立合适的esd/eos防护网络。为避免或降低这些esd/eos防护网络对通信电子产品内部电路单元的影响,这些esd/eos防护网络需要具有开启速度快,寄生电容低,esd/eos鲁棒性强等特征。

4.而目前常见的esd/eos的防护网络主要有二极管(diode)、双极型晶体管(bjt)、金属氧化物半导体场效应晶体管(mosfet)、横向与纵向扩散mosfet(ldmos/vdmos)以及可控硅整流器(scr)等电路单元。在低压ic的esd/eos防护应用中,二极管是常用电路单元,但是普通二极管存在鲁棒性差,寄生电容大等问题。二极管辅助scr(dtscr)也是另一种单向esd/eos防护电路单元,又由于它存在仅能对单向esd/eos进行有效防护,在双向信号传输的电路模块中,不能对相反方向的esd/eos进行高效防护。

技术实现要素:

5.鉴于背景技术的不足,本发明是提供了一种双向低压静电浪涌全芯片保护集成电路,所要解决的技术问题是现有技术在对ic进行esd/eos保护时只能进行单方向的esd/eos保护。

6.为解决以上技术问题,本发明提供了如下技术方案:一种双向低压静电浪涌全芯片保护集成电路,包括p型衬底,p型衬底的上表面设有n型隔离区,n型隔离区的上表面从左往右依次设有第一n阱、第一p阱和第二n阱,第一n阱的左侧面与第一p阱的右侧面连接,第一p阱的右侧面与第二n阱的左侧面连接;

7.第一n阱上设有第一p+注入区,第一p+注入区的右侧间隔设有第一n+注入区,第一n+注入区分别在第一n阱和第一p阱上,第二n阱上设有第五p+注入区,第五p+注入区的左侧间隔设有第八n+注入区,第八间隔注入区分别在第一p阱和第二n阱上;

8.第一p阱的中心设有第三n阱,第三n阱上设有第三p+注入区,第三p+注入区的前侧

和后侧分别设有第五n+注入区和第四n+注入区,第五n+注入区分别在第一p阱和第三n阱上,第四n+注入区分别在第一p阱和第三n阱上;

9.第一n+注入区和第四n+注入区之间间隔设有至少两个第二n+注入区,每两个相邻的第二n+注入区之间设有第二p+注入区,第八n+注入区和第四n+注入区之间间隔设有至少两个第六n+注入区,每两个相邻的第六n+注入区之间设有第四p+注入区。

10.作为进一步的技术方案,p型衬底的左侧面、n型隔离区的左侧面和第一n阱的左侧面齐平,p型衬底的右侧面、n型隔离区的右侧面和第二n阱的右侧面齐平。

11.最为进一步的技术方案,该集成电路的整体结构关于p型衬底的中心中心称。

12.作为进一步的技术方案,n型隔离区为高压n阱或者n型埋层。

13.当第一n+注入区和第四n+注入区之间间隔设有两个第二n+注入区、第八n+注入区和第四n+注入区之间间隔设有至少两个第六n+注入区时,第一p+注入区和第二p+注入区左侧的第二n+注入区均与第一金属相连,第一n+注入区、第二p+注入区和第五n+注入区均与第二金属相连,第三p+注入区、第二p+注入区右侧的第二n+注入区和第四p+注入区左侧的第六n+注入区均与第三金属相连,第四p+注入区、第四n+注入区和第八n+注入区均与第四金属相连,第四p+注入区右侧的第六n+注入区和第五p+注入区均与第五金属相连。

14.在实际使用时,可从第一金属引出一电极用作该集成电路的vss端;可从第三金属引出一电极作该集成电路的i/o端;可从第五金属引出一电极用作该集成电路的vdd端。本发明在使用时具有以下六种工作模式:

15.ps模式:i/o接高电位,vss接低电位,vdd浮空;

16.pd模式:i/o接高电位,vdd接低电位,vss浮空:

17.ns模式:i/o接低电位,vss接高电位,vdd浮空;

18.nd模式:i/o接低电位,vdd接高电位,vss浮空;

19.ds模式:vdd接高电位,vss接低电位,i/o浮空;

20.sd模式:vdd接低电位,vss接高电位,i/o浮空。

21.本发明与现有技术相比所具有的有益效果是:首先通过n型隔离区可以降低本发明在工作时的漏电流,削弱衬底寄生效应;其次可以在第二n+注入区和第二p+注入区之间、在第六n+注入区和第四p+注入区之间制备稳压二极管,可以避免i/o端与vss端之间或者vdd与i/o端之间因为距离过短产生esd/eos瞬态击穿现象;另外本发明由于中心对称,因此在ps模式和pd模式下工作的电流泄放路径完全相同,在ns模式与nd模式下工作的电流泄放路径完全相同,在ds模式与sd模式下的电流泄放路径双向完全相同;最后本发明在ps、pd、ns、nd、ds和sd六种工作模式中均有两个正偏二极管辅助scr触发特征,在全芯片esd/eos防护模式下,本发明在i/o、vss与vdd任意两端口之间均有对称正反向esd/eos保护特性,可减小芯片设计面积和寄生电容,降低导通电阻,增强esd/eos鲁棒性,另外任意两端口之间的电流泄放路径包含并联的上下两条scr路径,在不改变触发条件下,亦可有效提高本发明的鲁棒性与维持电压,具有面积小、导通电阻小和寄生电容低的优势。

附图说明

22.本发明有如下附图:

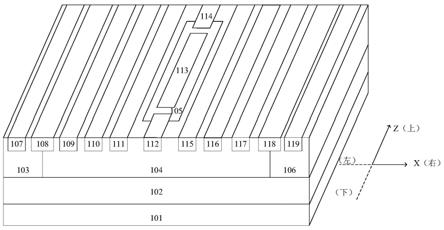

23.图1为本发明的结构图;

24.图2为本发明与第一至第五金属的连线图;

25.图3为本发明在ns模式下的等效电路图;

26.图4为本发明在sd模式下的等效电路图;

27.图5为本发明在pd模式下的等效电路图。

具体实施方式

28.现在结合附图对本发明作进一步详细的说明。这些附图均为简化的示意图,仅以示意方式说明本发明的基本结构,因此其仅显示与本发明有关的构成。

29.如图1

‑

5所示,一种双向低压静电浪涌全芯片保护集成电路包括p型衬底101,p衬底101的表面区域设有n型隔离区102,n型隔离区102的左侧边缘与p型衬底101的左侧边缘相连,n型隔离区102的右侧边缘与p型衬底101右侧边缘相连;

30.n型隔离区102的表面区域从左到右依次设有第一n阱103、第一p阱104和第二n阱106;其中,第一n阱103的左侧边缘与n型隔离区102的左侧边缘相连,第一n阱103的右侧边缘与第一p阱104的左侧边缘相连,第一p阱104的右侧边缘与第二n阱106的左侧边缘相连,第二n阱106的右侧边缘与n型隔离区102右侧边缘相连;

31.第一n阱103上设有第一p+注入区107,第一p+注入区107的右侧间隔设有第一n+注入区108,第一n+注入区108分别在第一n阱103和第一p阱104上,第二n阱106上设有第五p+注入区119,第五p+注入区119的左侧间隔设有第八n+注入区118,第八间隔注入区118分别在第一p阱104和第二n阱106上;

32.第一n阱103的表面设有第一p+注入区107,第一p+注入区107的右侧间隔设有第一n+注入区108,第一n+注入区108横跨在第一n阱103和第一p阱104的表面区域;

33.第一p阱104的中心部分区域设有第三n阱105,第三n阱105上设有第三p+注入区113,第三p+注入区113的前侧和后侧分别设有第五n+注入区114和第四n+注入区112,第五n+注入区114分别在第一p阱104和第三n阱105上,第四n+注入区112分别在第一p阱104和第三n阱105上,第三p+注入区113的左侧边缘与第三n阱105的左侧边缘设有一定间距,第三p+注入区113的右侧边缘与第三n阱105的右侧边缘设有一定间距;

34.第一p阱104的表面区域在第一n+注入区108和第四n+注入区之间从左至右依次按一定间距制备第二n+注入区109、第二p+注入区110、第三n+注入区111、在第四n+注入区和第八n+注入区118之间从左至右依次设有第六n+注入区115、第四p+注入区116和第七n+注入区117,第三n+注入区111的右侧与第三n阱105左侧边缘设有一定间距,第六n+注入区115的左侧与第三n阱105的右侧边缘设有一定间距;

35.如图2所示,第一p+注入区107和第二n+注入区109均与第一金属201相连;第一n+注入区108、第二p+注入区110和第五n+注入区114均与第二金属202相连;第三p+注入区113、第三n+注入区111和第六n+注入区115均与第三金属203相连;第四p+注入区116、第四n+注入区112和第八n+注入区118均与第四金属204相连,第七n+注入区117和第五p+注入区119均与第五金属205相连;

36.具体地,本实施例中,本发明的整体结构关于p型衬底101的中心中心称,n型隔离区102为高压n阱或者n型埋层。

37.在实际使用时,可从第一金属引出一电极用作该集成电路的vss端;可从第三金属

引出一电极作该集成电路的i/o端;可从第五金属引出一电极用作该集成电路的vdd端。本发明在使用时具有以下六种工作模式:

38.ps模式:i/o接高电位,vss接低电位,vdd浮空;

39.pd模式:i/o接高电位,vdd接低电位,vss浮空:

40.ns模式:i/o接低电位,vss接高电位,vdd浮空;

41.nd模式:i/o接低电位,vdd接高电位,vss浮空;

42.ds模式:vdd接高电位,vss接低电位,i/o浮空;

43.sd模式:vdd接低电位,vss接高电位,i/o浮空。

44.在实际使用时在ps模式与ns模式、pd模式与nd模式、pd模式与ps模式、ns模式与nd模式,双向低压静电浪涌全芯片保护ic内部电流泄放路径呈电学双向对称特性。

45.本发明在ns模式下的等效电路图如图3所示,当电流从vss端流向i/o端时,第一p+注入区107、第一n阱103和第一p阱104构成pnp管t1,第一n阱103、第一p阱104和第三n+注入区111构成npn管t2,第一n阱103和所述第一p阱104和第六n+注入区115构成npn管t3,npn管t2与所述npn管t3并联,并与pnp管t1构成scr结构的正反馈网络,提了本发明的鲁棒性;另外第一p+注入区107、第一n+注入区108和第一n阱103构成正偏二极管d1,第二p+注入区110、第一p阱104和第三n+注入区111构成正偏二极管d2,第一p阱104和第六n+注入区115构成正偏二极管d3,正偏二极管d2、d3并联,在esd应力作用下,与正偏二极管d1以及第二金属202形成二极管串正向导通的触发路径,一方面大大降低了本发明的触发电压,切二极管的钳位能力也使得其抗闩锁能力大大提高,另一方面二极管串与scr电流泄放路径并联,降低了本发明的寄生电容和导通电阻;

46.在实际使用时,本发明在sd模式与ds模式的电流泄放路径均呈双向全对称特性。本发明在sd模式下的等效电路图如图4所示,当电流从vss端流到vdd端时,第一n阱103、第一p阱104以及第七n+注入区117构成npn管t4,pnp管t1和npn管t4构成scr结构的正反馈网络,提高了本发明的鲁棒性;另外第一p阱104和第七n+注入区117构成正偏二极管d4,正偏二极管d1、d4组成二极管串正向导通路径,提高双向低压静电浪涌全芯片保护ic的维持电压,降低触发电压。

47.在实际使用时,本发明在pd模式与nd模式的电流泄放路径均呈双向全对称特性,在pd模式下的等效电路图如图5所示,当电流从i/o端流到vdd端时,第三p+注入区113、第三n阱105以及第一p阱104构成pnp管t5,第一p阱104、第三n阱105以及第七n+注入区117构成npn管t6,pnp管t5和npn管t6构成scr结构的正反馈网络,提高双了本发明的鲁棒性,另外第三p+注入区113、第三n阱105和第四n+注入区112构成正偏二极管d5,该正偏二极管d5与第五n+注入区114、第三p+注入区113和第三n阱105构成的正偏二极管并联,由正偏二极管d4、d5组成的二极管串正向导通路径,提高了本发明在pd模式的维持电压,降低触发电压。

48.另外在实际使用时,本发明在pd模式与ps模式、ns模式与nd模式中的内部电流泄放路径呈电学双向对称特性。

49.另外在实际使用时,可根据实际需求在第二n+注入区109与第二p+注入区110之间按工艺设计规则制备稳压二极管、在第二p+注入区110与第三n+注入区111之间根据实际工艺设计规则制备稳压二极管、在第四p+注入区116与第六n+注入区115之间按实际工艺设计规则制备稳压二极管、在将第四p+注入区116与第七n+注入区117之间根据实际工艺设计规

则制备稳压二极管,可避免在i/o端与vss端之间,或在vdd与i/o端之间因为距离过短产生esd/eos瞬态击穿现象。

50.上述依据本发明为启示,通过上述的说明内容,相关工作人员完全可以在不偏离本项发明技术思想的范围内,进行多样的变更以及修改。本项发明的技术性范围并不局限于说明书上的内容,必须要根据权利要求范围来确定其技术性范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1